# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                               |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | ST7                                                                    |

| Core Size                  | 8-Bit                                                                  |

| Speed                      | 8MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                             |

| Peripherals                | LVD, POR, PWM, WDT                                                     |

| Number of I/O              | 48                                                                     |

| Program Memory Size        | 60KB (60K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 2K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                            |

| Data Converters            | A/D 16x10b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 64-LQFP                                                                |

| Supplier Device Package    | -                                                                      |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bar9t3 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

SYSTEM INTEGRITY MANAGEMENT (Cont'd) 6.4.4 Register Description SYSTEM INTEGRITY (SI) CONTROL/STATUS REGISTER (SICSR) Read/Write Reset Value: 000x 000x (00h)

Bit 7 = AVDS Voltage Detection selection This bit is set and cleared by software. Voltage Detection is available only

# **7 INTERRUPTS**

## 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

Hardware interrupts

Software interrupt (TRAP)

Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non maskable events: RESET, TRAP

- 1 maskable Top Level event: TLI

- This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

#### 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of

each interrupt vector (see Table 6). The processing flow is shown in Figure 19

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of

# INTERRUPTS (Cont'd)

| Instruction | New Descripti on                | Function/Example      | 11 | Н | 10 | Ν | Z | С |

|-------------|---------------------------------|-----------------------|----|---|----|---|---|---|

| HALT        | Entering Halt mode              |                       | 1  |   | 0  |   |   |   |

| IRET        | Interrupt routine return        | Pop CC, A, X, PC      | 11 | Н | 10 | Ν | Z | С |

| JRM         | Jump if I1:0=11 (level 3)       | 11:0=11 ?             |    |   |    |   |   |   |

| JRNM        | Jump if I1:0<>11                | 11:0<>11 ?            |    |   |    |   |   |   |

| POP CC      | Pop CC from the Stack           | Mem => CC             | 11 | Н | 10 | Ν | Z | С |

| RIM         | Enable interrupt (level 0 set)  | Load 10 in I1:0 of CC | 1  |   | 0  |   |   |   |

| SIM         | Disable interrupt (level 3 set) | Load 11 in I1:0 of CC | 1  |   | 1  |   |   |   |

| TRAP        | Software trap                   | Software NMI          | 1  |   | 1  |   |   |   |

| WFI         | Wait for interrupt              |                       | 1  |   | 0  |   |   |   |

# Table 7. Dedicated Interrupt Instruction Set

Note: During the execution of an interrupt routine, the HALT, POPCC, RIM, SIM and WFI instructions change the current software priority up to the next IRET instruction or one of the previously mentioned instructions.

## POWER SAVING MODES (Cont'd)

## 8.4.2 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see section 10.2 on page 57 for more details on the MCCSR register).

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 8, "Interrupt Mapping," on page 37) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 30).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b'to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see section 14.1 on page 174 for more details).

Figure 29. HALT Timing Overview

Figure 30. HALT Mode Flow-chart

Notes:

1. WDGHALT is an option bit. See option byte section for more details.

2. Peripheral clocked with an external clock source can still be active.

3. Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 37 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

# 10.2.5 Low Power Modes

| Mode            | Description                                                                                                                                             |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT            | No effect on MCC/RTC peripheral.<br>MCC/RTC interrupt cause the device to exit<br>from WAIT mode.                                                       |

| ACTIVE-<br>HALT | No effect on MCC/RTC counter (OIE bit is<br>set), the registers are frozen.<br>MCC/RTC interrupt cause the device to exit<br>from ACTIVE-HALT mode.     |

| HALT            | MCC/RTC counter and registers are frozen.<br>MCC/RTC operation resumes when the<br>MCU is woken up by an interrupt with "exit<br>from HALT" capability. |

## 10.2.6 Interrupts

The MCC/RTC interrupt event generates an interrupt if the OIE bit of the MCCSR register is set and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event          | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|--------------------------|---------------|--------------------------|----------------------|----------------------|

| Time base overflow event | OIF           | OIE                      | Yes                  | No <sup>1)</sup>     |

Note:

The MCC/RTC interrupt wakes up the MCU from ACTIVE-HALT mode, not from HALT mode.

# 10.2.7 Register Description

MCC CONTROL/STATUS REGISTER (MCCSR) Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| мсо | CP1 | CP0 | SMS | TB1 | TB0 | OIE | OIF |

Bit 7 = MCO Main clock out selection

This bit enables the MCO alternate function on the PF0 I/O port. It is set and cleared by software.

0: MCO alternate function disabled (I/O pin free for general-purpose I/O)

1: MCO alternate function enabled (f<sub>CPU</sub> on I/O port)

Note: To reduce power consumption, the MCO function is not active in ACTIVE-HALT mode.

Bit 6:5 = CP[1:0] CPU clock prescaler These bits select the CPU clock prescaler which is

applied in the different slow modes. Their action is conditioned by the setting of the SMS bit. These two bits are set and cleared by software

| f <sub>CPU</sub> in SLOW mode | CP1 | CP0 |

|-------------------------------|-----|-----|

| f <sub>OSC2</sub> / 2         | 0   | 0   |

| f <sub>OSC2</sub> / 4         | 0   | 1   |

| f <sub>OSC2</sub> / 8         | 1   | 0   |

| f <sub>OSC2</sub> / 16        | 1   | 1   |

Bit 4 = SMS Slow mode select

This bit is set and cleared by software.

0: Normal mode.  $f_{CPU} = f_{OSC2}$

1: Slow mode. f<sub>CPU</sub> is given by CP1, CP0 See Section 8.2 SLOW MODE and Section 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC) for more details.

# Bit 3:2 = TB[1:0] Time base control

These bits select the programmable divider time base. They are set and cleared by software.

| Counter   | Time                                            | TB1  | TB0 |     |  |

|-----------|-------------------------------------------------|------|-----|-----|--|

| Prescaler | f <sub>OSC2</sub> =4MHz f <sub>OSC2</sub> =8MHz |      | TDT | TBU |  |

| 16000     | 4ms                                             | 2ms  | 0   | 0   |  |

| 32000     | 8ms                                             | 4ms  | 0   | 1   |  |

| 80000     | 20ms                                            | 10ms | 1   | 0   |  |

| 200000    | 50ms                                            | 25ms | 1   | 1   |  |

A modification of the time base is taken into account at the end of the current period (previously set) to avoid an unwanted time shift. This allows to use this time base as a real time clock.

Bit 1 = OIE Oscillator interrupt enable

This bit set and cleared by software.

0: Oscillator interrupt disabled

1: Oscillator interrupt enabled

This interrupt can be used to exit from ACTIVE-HALT mode.

When this bit is set, calling the ST7 software HALT instruction enters the ACTIVE-HALT power saving mode.

## SERIAL PERIPHERAL INTERFACE (Cont'd) CONTROL/STATUS REGISTER (SPICSR) Read/Write (some bits Read Only) Reset Value: 0000 0000 (00h)

| 7    |      |     |      |   |     |     | 0   |

|------|------|-----|------|---|-----|-----|-----|

| SPIF | WCOL | OVR | MODF | - | SOD | SSM | SSI |

Bit 7 = SPIF Serial Peripheral Data Transfer Flag (Read only).

This bit is set by hardware when a transfer has been completed. An interrupt is generated if SPIE=1 in the SPICR register. It is cleared by a software sequence (an access to the SPICSR register followed by a write or a read to the SPIDR register).

- 0: Data transfer is in progress or the flag has been cleared.

- 1: Data transfer between the device and an external device has been completed.

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

Bit 6 = WCOL Write Collision status (Read only). This bit is set by hardware when a write to the SPIDR register is done during a transmit sequence. It is cleared by a software sequence (see Figure 59).

0: No write collision occurred

1: A write collision has been detected

Bit 5 = OVR SPI Overrun error (Read only).

This bit is set by hardware when the byte currently being received in the shift register is ready to be transferred into the SPIDR register while SPIF = 1 (See Section 10.5.5.2). An interrupt is generated if SPIE = 1 in SPICR register. The OVR bit is cleared by software reading the SPICSR register.

0: No overrun error

1: Overrun error detected

Bit 4 = MODF Mode Fault flag (Read only).

This bit is set by hardware when the  $\overline{SS}$  pin is pulled low in master mode (see Section 10.5.5.1 Master Mode Fault (MODF)). An SPI interrupt can be generated if SPIE=1 in the SPICSR register. This bit is cleared by a software sequence (An access to the SPICR register while MODF=1 followed by a write to the SPICR register).

0: No master mode fault detected

1: A fault in master mode has been detected

Bit 3 = Reserved, must be kept cleared.

Bit 2 = SOD SPI Output Disable.

This bit is set and cleared by software. When set, it disables the alternate function of the SPI output (MOSI in master mode / MISO in slave mode) 0: SPI output enabled (if SPE=1) 1: SPI output disabled

1: SPI output disabled

Bit 1 = SSM  $\overline{SS}$  Management.

This bit is set and cleared by software. When set, it disables the alternate function of the SPI  $\overline{SS}$  pin and uses the SSI bit value instead. See Section 10.5.3.2 Slave Select Management.

- 0: Hardware management (SS managed by external pin)

- 1: Software management (internal SS signal controlled by SSI bit. External SS pin free for general-purpose I/O)

Bit  $0 = SSI \overline{SS}$  Internal Mode.

This bit is set and cleared by software. It acts as a 'chip select' by controlling the level of the SS slave select signal when the SSM bit is set.

0 : Slave selected

1 : Slave deselected

\_

DATA I/O REGISTER (SPIDR) Read/Write

Reset Value: Undefined

| 1  |    |    |    |    |    |    | 0  |  |

|----|----|----|----|----|----|----|----|--|

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |  |

The SPIDR register is used to transmit and receive data on the serial bus. In a master device, a write to this register will initiate transmission/reception of another byte.

Notes: During the last clock cycle the SPIF bit is set, a copy of the received data byte in the shift register is moved to a buffer. When the user reads the serial peripheral data I/O register, the buffer is actually being read.

While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

Warning: A write to the SPIDR register places data directly into the shift register for transmission.

A read to the SPIDR register returns the value located in the buffer and not the content of the shift register (see Figure 54).

SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

## Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = SCID Disabled for low power consumption When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software. 0: SCI enabled

1: SCI prescaler and outputs disabled

Bit 4 = M Word length. This bit determines the word length. It is set or cleared by software. 0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

Note: The M bit must not be modified during a data transfer (both transmission and reception).

Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

Bit 2 = PCE Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

Bit 1 = PS Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity

1: Odd parity

Bit 0 = PIE Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software. 0: Parity error interrupt disabled

1: Parity error interrupt enabled.

110/187

# SERIAL COMMUNICATION INTERFACE (Cont'd)

| Address<br>(Hex.) | Register<br>Label       | 7        | 6    | 5    | 4    | 3    | 2    | 1    | 0        |

|-------------------|-------------------------|----------|------|------|------|------|------|------|----------|

| 0050h             | SCISR                   | TDRE     | TC   | RDRF | IDLE | OVR  | NF   | FE   | PE       |

|                   | Reset Value             | 1        | 1    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0051h             | SCIDR<br>Reset Value    | MSB<br>x | x    | x    | x    | x    | х    | x    | LSB<br>x |

| 0052h             | SCIBRR                  | SCP1     | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0     |

|                   | Reset Value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0053h             | SCICR1                  | R8       | Т8   | SCID | M    | WAKE | PCE  | PS   | PIE      |

|                   | Reset Value             | x        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0054h             | SCICR2                  | TIE      | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK      |

|                   | Reset Value             | 0        | 0    | 0    | 0    | 0    | 0    | 0    | 0        |

| 0055h             | SCIERPR<br>Reset Value  | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

| 0057h             | SCIPETPR<br>Reset Value | MSB<br>0 | 0    | 0    | 0    | 0    | 0    | 0    | LSB<br>0 |

# Table 23. SCI Register Map and Reset Values

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

Acknowledge may be enabled and disabled by software.

The I<sup>2</sup>C interface address and/or general call address can be selected by software.

The speed of the  $I^2C$  interface may be selected between Standard (up to 100KHz) and Fast  $I^2C$  (up to 400KHz).

## SDA/SCL Line Control

Transmitter mode: the interface holds the clock line low before transmission to wait for the microcontroller to write the byte in the Data Register.

Receiver mode: the interface holds the clock line low after reception to wait for the microcontroller to read the byte in the Data Register. The SCL frequency ( $\rm F_{scl}$ ) is controlled by a programmable clock divider which depends on the  $\rm I^2C$  bus mode.

When the  $I^2C$  cell is enabled, the SDA and SCL ports must be configured as floating inputs. In this case, the value of the external pull-up resistor used depends on the application.

When the I<sup>2</sup>C cell is disabled, the SDA and SCL ports revert to being standard I/O port pins.

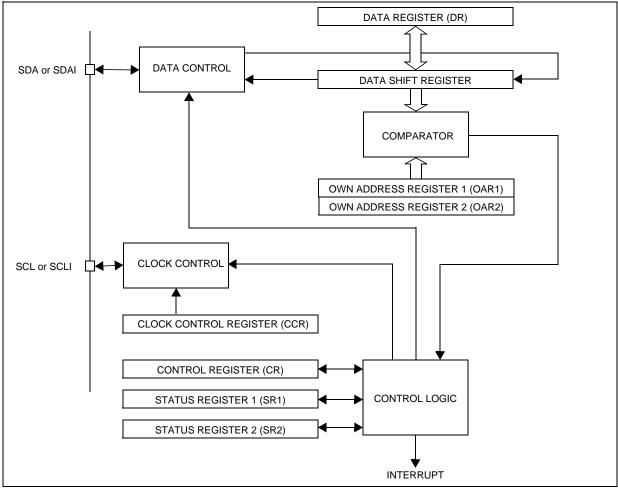

Figure 66. I<sup>2</sup>C Interface Block Diagram

# I<sup>2</sup>C INTERFACE (Cont'd)

How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

## **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

## 10.7.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

## Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, holding the SCL line low (see Figure 67 Transfer sequencing EV5).

## Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, holding the SCL line low (see Figure 67 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

- The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), holding the SCL line low (see Figure 67 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

Note: In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

## Master Receiver

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, holding the SCL line low (see Figure 67 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

Note: In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

# 10-BIT A/D CONVERTER (ADC) (Cont'd)

10.8.6 Register Description

CONTROL/STATUS REGISTER (ADCCSR)

Read/Write (Except bit 7 read only)

Reset Value: 0000 0000 (00h)

| 7   |       |      |   |     |     |     | 0   |

|-----|-------|------|---|-----|-----|-----|-----|

| EOC | SPEED | ADON | 0 | СНЗ | CH2 | CH1 | CH0 |

Bit 7 = EOC End of Conversion This bit is set by hardware. It is cleared by hardware when software reads the ADCDRH register or writes to any bit of the ADCCSR register. 0: Conversion is not complete 1: Conversion complete

Bit 6 = SPEED ADC clock selection

This bit is set and cleared by software. 0:  $f_{ADC} = f_{CPU}/4$

1:  $f_{ADC} = f_{CPU}/2$

Bit 5 = ADON A/D Converter on This bit is set and cleared by software. 0: Disable ADC and stop conversion 1: Enable ADC and start conversion

Bit 4 = Reserved. Must be kept cleared.

Bit 3:0 = CH[3:0] Channel Selection These bits are set and cleared by software. They select the analog input to convert.

| Channel Pin* | CH3 | CH2 | CH1 | CH0 |

|--------------|-----|-----|-----|-----|

| AINO         | 0   | 0   | 0   | 0   |

| AIN1         | 0   | 0   | 0   | 1   |

| AIN2         | 0   | 0   | 1   | 0   |

| AIN3         | 0   | 0   | 1   | 1   |

| AIN4         | 0   | 1   | 0   | 0   |

| AIN5         | 0   | 1   | 0   | 1   |

| AIN6         | 0   | 1   | 1   | 0   |

| AIN7         | 0   | 1   | 1   | 1   |

| AIN8         | 1   | 0   | 0   | 0   |

| AIN9         | 1   | 0   | 0   | 1   |

| AIN10        | 1   | 0   | 1   | 0   |

| AIN11        | 1   | 0   | 1   | 1   |

| AIN12        | 1   | 1   | 0   | 0   |

| AIN13        | 1   | 1   | 0   | 1   |

| AIN14        | 1   | 1   | 1   | 0   |

| AIN15        | 1   | 1   | 1   | 1   |

\*The number of channels is device dependent. Refer to the device pinout description.

## DATA REGISTER (ADCDRH)

Read Only

7

Reset Value: 0000 0000 (00h)

0

| D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 |

|----|----|----|----|----|----|----|----|

|    |    |    |    |    |    |    |    |

Bit 7:0 = D[9:2] MSB of Converted Analog Value

DATA REGISTER (ADCDRL) Read Only Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |    | 0  |

|---|---|---|---|---|---|----|----|

| 0 | 0 | 0 | 0 | 0 | 0 | D1 | D0 |

Bit 7:2 =Reserved. Forced by hardware to 0.

Bit 1:0 = D[1:0] LSB of Converted Analog Value

# **11 INSTRUCTION SET**

## **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

Table 26. CPU Addressing Mode Overview

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 |             |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

## 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                             | Parameter                                                                                                                      | Conditions                                                                                                                                                             | Min                  | Max                  | Unit |

|------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------------------|------|

| f <sub>OSC</sub> (                 | Oscillator Frequency <sup>1)</sup>                                                                                             | LP: Low power oscillator<br>MP: Medium power oscillato                                                                                                                 | r >2                 | 2                    |      |

|                                    |                                                                                                                                | MS: Medium speed oscillator<br>HS: High speed oscillator                                                                                                               |                      | 8<br>16              | MHz  |

| R <sub>F</sub>                     | Feedback resistor <sup>2)</sup>                                                                                                |                                                                                                                                                                        | 20                   | 40                   | k    |

| C <sub>L1</sub><br>C <sub>L2</sub> | Recommended load capacitance ver-<br>sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) | $\begin{array}{ll} R_{S}{=}200 & LP \text{ oscill} \\ R_{S}{=}200 & MP \text{ oscil} \\ R_{S}{=}200 & MS \text{ oscil} \\ R_{S}{=}100 & HS \text{ oscill} \end{array}$ | lator 22<br>lator 18 | 56<br>46<br>33<br>33 | pF   |

| Symbol         | Parameter            | Conditions                                              |                                                                  | Тур                     | Max                      | Unit |

|----------------|----------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------|------|

| i <sub>2</sub> | OSC2 driving current | V <sub>DD</sub> =5V<br>V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA   |

Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

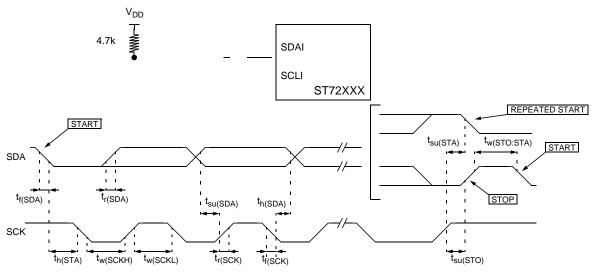

12.11.2 I<sup>2</sup>C - Inter IC Control Interface

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SDAI and SCLI). The ST7 I<sup>2</sup>C interface meets the requirements of the Standard I<sup>2</sup>C communication protocol described in the following table.

| Symbol                                     | Parameter                               | Standard          | mode I <sup>2</sup> C | Fast mo              | de I <sup>2</sup> C <sup>5)</sup> | Unit  |

|--------------------------------------------|-----------------------------------------|-------------------|-----------------------|----------------------|-----------------------------------|-------|

| Symbol                                     | Falameter                               | Min <sup>1)</sup> | Max <sup>1)</sup>     | Min <sup>1)</sup>    | Max <sup>1)</sup>                 | Offic |

| t <sub>w(SCLL)</sub>                       | SCL clock low time                      | 4.7               |                       | 1.3                  |                                   |       |

| t <sub>w(SCLH)</sub>                       | SCL clock high time                     | 4.0               |                       | 0.6                  |                                   | μs    |

| t <sub>su(SDA)</sub>                       | SDA setup time                          | 250               |                       | 100                  |                                   |       |

| t <sub>h(SDA)</sub>                        | SDA data hold time                      | 0 <sup>3)</sup>   |                       | 0 <sup>2)</sup>      | 900 <sup>3)</sup>                 |       |

| t <sub>r(SDA)</sub><br>t <sub>r(SCL)</sub> | SDA and SCL rise time                   |                   | 1000                  | 20+0.1C <sub>b</sub> | 300                               | ns    |

| t <sub>f(SDA)</sub><br>t <sub>f(SCL)</sub> | SDA and SCL fall time                   |                   | 300                   | 20+0.1C <sub>b</sub> | 300                               |       |

| t <sub>h(STA)</sub>                        | START condition hold time               | 4.0               |                       | 0.6                  |                                   |       |

| t <sub>su(STA)</sub>                       | Repeated START condition setup time     | 4.7               |                       | 0.6                  |                                   | μs    |

| t <sub>su(STO)</sub>                       | STOP condition setup time               | 4.0               |                       | 0.6                  |                                   | μs    |

| t <sub>w(STO:STA)</sub>                    | STOP to START condition time (bus free) | 4.7               |                       | 1.3                  |                                   | μs    |

| Cb                                         | Capacitive load for each bus line       |                   | 400                   |                      | 400                               | pF    |

Figure 92. Typical Application with I <sup>2</sup>C Bus and Timing Diagram <sup>4)</sup>

Notes:

1. Data based on standard  $I^2C$  protocol requirement, not tested in production.

2. The device must internally provide a hold time of at least 300ns for the SDA signal in order to bridge the undefined region of the falling edge of SCL.

3. The maximum hold time of the START condition has only to be met if the interface does not stretch the low period of SCL signal.

4. Measurement points are done at CMOS levels:  $0.3xV_{DD}$  and  $0.7xV_{DD}$ .

5. At 4MHz f<sub>CPU</sub>, max.I<sup>2</sup>C speed (400kHz) is not achievable. In this case, max. I<sup>2</sup>C speed will be approximately 260KHz.