Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

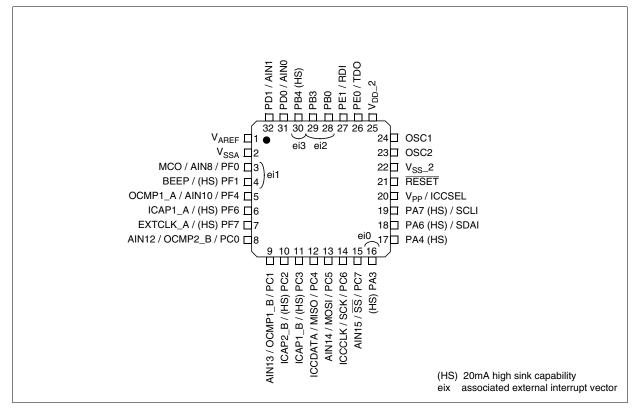

| Product Status             | Not For New Designs                                                   |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | ·                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bj6t3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents ——

|     | 12.2.1 Voltage Characteristics                                                  |     |

|-----|---------------------------------------------------------------------------------|-----|

|     | 12.2.2 Current Characteristics                                                  |     |

|     | 12.2.3 Thermal Characteristics                                                  |     |

|     | 12.3 OPERATING CONDITIONS                                                       |     |

|     | 12.3.1 General Operating Conditions                                             |     |

|     | 12.3.2 Operating Conditions with Low Voltage Detector (LVD)                     |     |

|     | 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds                              |     |

|     | 12.3.4 External Voltage Detector (EVD) Thresholds                               |     |

|     |                                                                                 |     |

|     | 12.4.1 CURRENT CONSUMPTION                                                      |     |

|     | 12.4.2       Supply and Clock Managers         12.4.3       On-Chip Peripherals |     |

|     | 12.5 CLOCK AND TIMING CHARACTERISTICS                                           |     |

|     | 12.5.1 General Timings                                                          |     |

|     | 12.5.2 External Clock Source                                                    |     |

|     | 12.5.3 Crystal and Ceramic Resonator Oscillators                                |     |

|     | 12.5.4 RC Oscillators                                                           |     |

|     | 12.5.5 PLL Characteristics                                                      | 150 |

|     | 12.6 MEMORY CHARACTERISTICS                                                     | 151 |

|     | 12.6.1 RAM and Hardware Registers                                               | 151 |

|     | 12.6.2 FLASH Memory                                                             |     |

|     | 12.7 EMC CHARACTERISTICS                                                        | 152 |

|     | 12.7.1 Functional EMS (Electro Magnetic Susceptibility)                         | 152 |

|     | 12.7.2 Electro Magnetic Interference (EMI)                                      |     |

|     | 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)                        |     |

|     | 12.8 I/O PORT PIN CHARACTERISTICS                                               |     |

|     | 12.8.1 General Characteristics                                                  |     |

|     | 12.8.2 Output Driving Current                                                   |     |

|     | 12.9 CONTROL PIN CHARACTERISTICS                                                |     |

|     | 12.9.1 Asynchronous RESET Pin                                                   |     |

|     | 12.9.2 ICCSEL/VPP Pin                                                           |     |

|     |                                                                                 |     |

|     | 12.10.1 8-Bit PWM-ART Auto-Reload Timer                                         |     |

|     | 12.10.2 16-Bit Timer                                                            |     |

|     |                                                                                 |     |

|     | 12.11.1 SPI - Serial Peripheral Interface                                       |     |

|     | 12.1210-BIT ADC CHARACTERISTICS                                                 |     |

|     | 12.12.1 Analog Power Supply and Reference Pins                                  |     |

|     | 12.12.1 Analog Fower Supply and Reference Fins                                  |     |

|     | 12.12.3 ADC Accuracy                                                            |     |

| 13  | PACKAGE CHARACTERISTICS                                                         |     |

|     | 13.1 PACKAGE MECHANICAL DATA                                                    |     |

|     | 13.2 THERMAL CHARACTERISTICS                                                    | 172 |

|     | 13.3 SOLDERING INFORMATION                                                      |     |

| 14  | ST72321B DEVICE CONFIGURATION AND ORDERING INFORMATION                          |     |

| ••• |                                                                                 |     |

# CENTRAL PROCESSING UNIT (Cont'd)

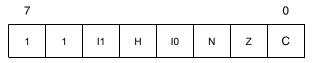

## **Condition Code Register (CC)**

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### **Arithmetic Management Bits**

Bit  $4 = \mathbf{H}$  Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred. 1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 2 = **N** *Negative*.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result 7<sup>th</sup> bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

# Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### Interrupt Management Bits

Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 11 | 10 |

|-------------------------------|----|----|

| Level 0 (main)                | 1  | 0  |

| Level 1                       | 0  | 1  |

| Level 2                       | 0  | 0  |

| Level 3 (= interrupt disable) | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

#### CENTRAL PROCESSING UNIT (Cont'd)

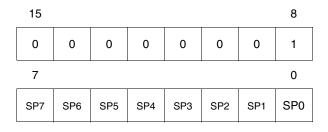

# Stack Pointer (SP)

# Read/Write

**47/**

Reset Value: 01 FFh

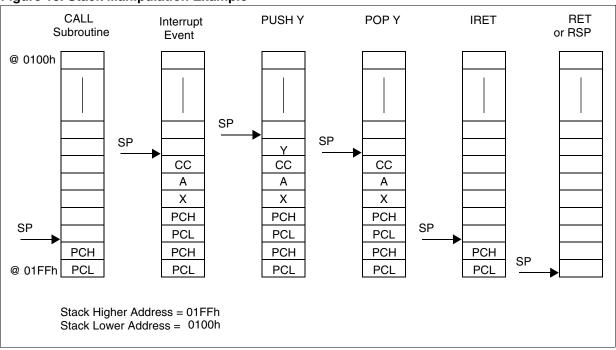

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

#### Figure 10. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

# INTERRUPTS (Cont'd)

# Table 9. Nested Interrupts Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7     | 6       | 5     | 4     | 3     | 2     | 1     | 0     |

|-------------------|-------------------|-------|---------|-------|-------|-------|-------|-------|-------|

|                   |                   | е     | i1      | е     | i0    | M     | CC    | Т     | LI    |

| 0024h             | ISPR0             | l1_3  | 10_3    | l1_2  | 10_2  | l1_1  | 10_1  |       |       |

|                   | Reset Value       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   | S     | PI      |       |       | е     | i3    | е     | i2    |

| 0025h             | ISPR1             | l1_7  | 10_7    | l1_6  | 10_6  | l1_5  | 10_5  | l1_4  | 10_4  |

|                   | Reset Value       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   | A۱    | AVD SCI |       | CI    | TIMI  | ER B  | TIME  | ER A  |

| 0026h             | ISPR2             | 11_11 | I0_11   | l1_10 | l0_10 | l1_9  | 10_9  | l1_8  | 10_8  |

|                   | Reset Value       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1     |

|                   |                   |       |         |       |       | PWN   | IART  | 12    | C     |

| 0027h             | ISPR3             |       |         |       |       | l1_13 | l0_13 | l1_12 | 10_12 |

|                   | Reset Value       | 1     | 1       | 1     | 1     | 1     | 1     | 1     | 1     |

| 0028h             | EICR              | IS11  | IS10    | IPB   | IS21  | IS20  | IPA   | TLIS  | TLIE  |

| 002011            | Reset Value       | 0     | 0       | 0     | 0     | 0     | 0     | 0     | 0     |

## MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

Bit 0 = **OIF** Oscillator interrupt flag

This bit is set by hardware and cleared by software reading the MCCSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).

0: Timeout not reached 1: Timeout reached

T. Timeout reached

<u>ل</u>رک

**CAUTION**: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

## MCC BEEP CONTROL REGISTER (MCCBCR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7 |   |   |   |   |   |     | 0   |  |

|---|---|---|---|---|---|-----|-----|--|

| 0 | 0 | 0 | 0 | 0 | 0 | BC1 | BC0 |  |

Bit 7:2 = Reserved, must be kept cleared.

#### Bit 1:0 = **BC[1:0]** *Beep control*

These 2 bits select the PF1 pin beep capability.

| BC1 | BC0 | Beep mode with f <sub>OSC2</sub> =8MHz |                 |  |  |  |  |  |

|-----|-----|----------------------------------------|-----------------|--|--|--|--|--|

| 0   | 0   | C                                      | Off             |  |  |  |  |  |

| 0   | 1   | ~2-KHz                                 | Output          |  |  |  |  |  |

| 1   | 0   | ~1-KHz                                 | Beep signal     |  |  |  |  |  |

| 1   | 1   | ~500-Hz                                | ~50% duty cycle |  |  |  |  |  |

The beep output signal is available in ACTIVE-HALT mode but has to be disabled to reduce the consumption.

#### Table 15. Main Clock Controller Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6     | 5    | 4     | 3   | 2   | 1   | 0     |

|-------------------|-------------------|------|-------|------|-------|-----|-----|-----|-------|

| 002Bh             | SICSR             | AVDS | AVDIE | AVDF | LVDRF |     |     |     | WDGRF |

| 002011            | Reset Value       | 0    | 0     | 0    | х     | 0   | 0   | 0   | x     |

| 002Ch             | MCCSR             | MCO  | CP1   | CP0  | SMS   | TB1 | TB0 | OIE | OIF   |

| 002011            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

| 002Dh             | MCCBCR            |      |       |      |       |     |     | BC1 | BC0   |

| 002D11            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

## **ON-CHIP PERIPHERALS** (Cont'd)

<u>ل</u>رک

#### **Output compare and Time base interrupt**

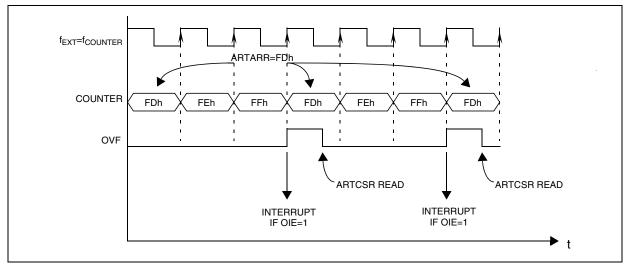

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

#### External clock and event detector mode

Using the  $f_{EXT}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{EVENT}$  number of events to be counted before setting the OVF flag.

# $n_{EVENT} = 256 - ARTARR$

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

Figure 41. External Event Detector Example (3 counts)

## SERIAL PERIPHERAL INTERFACE (Cont'd)

### 10.5.6 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on SPI.<br>SPI interrupt events cause the device to exit<br>from WAIT mode.                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HALT | SPI registers are frozen.<br>In HALT mode, the SPI is inactive. SPI oper-<br>ation resumes when the MCU is woken up by<br>an interrupt with "exit from HALT mode" ca-<br>pability. The data received is subsequently<br>read from the SPIDR register when the soft-<br>ware is running (interrupt vector fetching). If<br>several data are received before the wake-<br>up event, then an overrun error is generated.<br>This error can be detected after the fetch of<br>the interrupt routine that woke up the device. |

# 10.5.6.1 Using the SPI to wakeup the MCU from Halt mode

In slave configuration, the SPI is able to wakeup the ST7 device from HALT mode through a SPIF interrupt. The data received is subsequently read from the SPIDR register when the software is running (interrupt vector fetch). If multiple data transfers have been performed before software clears the SPIF bit, then the OVR bit is set by hardware. **Note:** When waking up from Halt mode, if the SPI remains in Slave mode, it is recommended to perform an extra communications cycle to bring the SPI from Halt mode state to normal state. If the SPI exits from Slave mode, it returns to normal state immediately.

**Caution:** The SPI can wake up the ST7 from Halt mode only if the Slave Select signal (external SS pin or the SSI bit in the SPICSR register) is low when the ST7 enters Halt mode. So if Slave selection is configured as external (see Section 10.5.3.2), make sure the master drives a low level on the SS pin when the slave enters Halt mode.

#### 10.5.7 Interrupts

| Interrupt Event              | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|------------------------------|---------------|--------------------------|----------------------|----------------------|

| SPI End of Transfer<br>Event | SPIF          |                          | Yes                  | Yes                  |

| Master Mode Fault<br>Event   | MODF          | SPIE                     | Yes                  | No                   |

| Overrun Error                | OVR           |                          | Yes                  | No                   |

**Note**: The SPI interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in

<u>/</u>۲

# SERIAL PERIPHERAL INTERFACE (Cont'd)

# Table 20. SPI Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0021h             | SPIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 002111            | Reset Value       | х    | х    | х    | х    | х    | х    | х    | х    |

| 0022h             | SPICR             | SPIE | SPE  | SPR2 | MSTR | CPOL | CPHA | SPR1 | SPR0 |

| 002211            | Reset Value       | 0    | 0    | 0    | 0    | х    | х    | х    | х    |

| 0023h             | SPICSR            | SPIF | WCOL | OVR  | MODF |      | SOD  | SSM  | SSI  |

| 002311            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

# 10.7.4 Functional Description

Refer to the CR, SR1 and SR2 registers in Section 10.7.7. for the bit definitions.

By default the I<sup>2</sup>C interface operates in Slave mode (M/SL bit is cleared) except when it initiates a transmit or receive sequence.

First the interface frequency must be configured using the FRi bits in the OAR2 register.

#### 10.7.4.1 Slave Mode

As soon as a start condition is detected, the address is received from the SDA line and sent to the shift register; then it is compared with the address of the interface or the General Call address (if selected by software).

**Note:** In 10-bit addressing mode, the comparison includes the header sequence (11110xx0) and the two most significant bits of the address.

**Header matched** (10-bit mode only): the interface generates an acknowledge pulse if the ACK bit is set.

Address not matched: the interface ignores it and waits for another Start condition.

Address matched: the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set.

- EVF and ADSL bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV1).

Next, in 7-bit mode read the DR register to determine from the least significant bit (Data Direction Bit) if the slave must enter Receiver or Transmitter mode.

In 10-bit mode, after receiving the address sequence the slave is always in receive mode. It will enter transmit mode on receiving a repeated Start condition followed by the header sequence with matching address bits and the least significant bit set (11110xx1).

#### Slave Receiver

Following the address reception and after SR1 register has been read, the slave receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV2).

## Slave Transmitter

Following the address reception and after SR1 register has been read, the slave sends bytes from the DR register to the SDA line via the internal shift register.

The slave waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV3).

When the acknowledge pulse is received:

The EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

#### Closing slave communication

After the last data byte is transferred a Stop Condition is generated by the master. The interface detects this condition and sets:

EVF and STOPF bits with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR2 register (see Figure 67 Transfer sequencing EV4). Error Cases

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and the BERR bits are set with an interrupt if the ITE bit is set.

If it is a Stop then the interface discards the data, released the lines and waits for another Start condition.

If it is a Start then the interface discards the data and waits for the next slave address on the bus.

- AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set with an interrupt if the ITE bit is set.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

**Note**: In case of errors, SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. While AF=1, the SCL line may be held low due to SB or BTF flags that are set at the same time. It is then necessary to release both lines by software.

57

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Bit 1 = **M/SL** *Master/Slave*.

This bit is set by hardware as soon as the interface is in Master mode (writing START=1). It is cleared by hardware after detecting a Stop condition on the bus or a loss of arbitration (ARLO=1). It is also cleared when the interface is disabled (PE=0). 0: Slave mode

1: Master mode

#### Bit 0 = SB Start bit (Master mode).

This bit is set by hardware as soon as the Start condition is generated (following a write START=1). An interrupt is generated if ITE=1. It is cleared by software reading SR1 register followed by writing the address byte in DR register. It is also cleared by hardware when the interface is disabled (PE=0).

0: No Start condition

1: Start condition generated

# I<sup>2</sup>C STATUS REGISTER 2 (SR2)

Read Only

Reset Value: 0000 0000 (00h)

| 7 |   |   |    |       |      |      | 0    |

|---|---|---|----|-------|------|------|------|

| 0 | 0 | 0 | AF | STOPF | ARLO | BERR | GCAL |

Bit 7:5 = Reserved. Forced to 0 by hardware.

#### Bit 4 = **AF** Acknowledge failure.

This bit is set by hardware when no acknowledge is returned. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while AF=1 but by other flags (SB or BTF) that are set at the same time.

0: No acknowledge failure

1: Acknowledge failure

Note:

– When an AF event occurs, the SCL line is not held low; however, the SDA line can remain low if the last bits transmitted are all 0. It is then necessary to release both lines by software.

Bit 3 =**STOPF** *Stop detection (Slave mode).* This bit is set by hardware when a Stop condition is detected on the bus after an acknowledge (if ACK=1). An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

124/187

The SCL line is not held low while STOPF=1.

- 0: No Stop condition detected

- 1: Stop condition detected

#### Bit 2 = ARLO Arbitration lost.

This bit is set by hardware when the interface loses the arbitration of the bus to another master. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

After an ARLO event the interface switches back automatically to Slave mode (M/SL=0).

The SCL line is not held low while ARLO=1.

0: No arbitration lost detected

1: Arbitration lost detected

Note:

- In a Multimaster environment, when the interface is configured in Master Receive mode it does not perform arbitration during the reception of the Acknowledge Bit. Mishandling of the ARLO bit from the I2CSR2 register may occur when a second master simultaneously requests the same data from the same slave and the I<sup>2</sup>C master does not acknowledge the data. The ARLO bit is then left at 0 instead of being set.

## Bit 1 = **BERR** Bus error.

This bit is set by hardware when the interface detects a misplaced Start or Stop condition. An interrupt is generated if ITE=1. It is cleared by software reading SR2 register or by hardware when the interface is disabled (PE=0).

The SCL line is not held low while BERR=1.

0: No misplaced Start or Stop condition

1: Misplaced Start or Stop condition

Note:

If a Bus Error occurs, a Stop or a repeated Start condition should be generated by the Master to re-synchronize communication, get the transmission acknowledged and the bus released for further communication

Bit 0 = GCAL General Call (Slave mode).

This bit is set by hardware when a general call address is detected on the bus while ENGC=1. It is cleared by hardware detecting a Stop condition (STOPF=1) or when the interface is disabled (PE=0).

- 0: No general call address detected on bus

- 1: general call address detected on bus

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | CC3 | CC2 | CC1 | CC0 |

Bit 7 = **FM/SM** *Fast/Standard I*<sup>2</sup>*C mode.* This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard I<sup>2</sup>C mode 1: Fast I<sup>2</sup>C mode

Bit 6:0 = **CC[6:0]** 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

# I<sup>2</sup>C DATA REGISTER (DR)

# Read / Write

Reset Value: 0000 0000 (00h)

Bit 7:0 = **D**[7:0] *8-bit Data Register.*

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

# **11 INSTRUCTION SET**

# **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

| Table 26. CPU | Addressing | Mode | Overview |

|---------------|------------|------|----------|

|---------------|------------|------|----------|

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 |             |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

# INSTRUCTION SET OVERVIEW (Cont'd)

#### **11.2 INSTRUCTION GROUPS**

The ST7 family devices use an Instruction Set consisting of 63 instructions. The instructions may

be subdivided into 13 main groups as illustrated in the following table:

| Load and Transfer                | LD   | CLR  |      |      |      |       |     |     |

|----------------------------------|------|------|------|------|------|-------|-----|-----|

| Stack operation                  | PUSH | POP  | RSP  |      |      |       |     |     |

| Increment/Decrement              | INC  | DEC  |      |      |      |       |     |     |

| Compare and Tests                | CP   | TNZ  | BCP  |      |      |       |     |     |

| Logical operations               | AND  | OR   | XOR  | CPL  | NEG  |       |     |     |

| Bit Operation                    | BSET | BRES |      |      |      |       |     |     |

| Conditional Bit Test and Branch  | BTJT | BTJF |      |      |      |       |     |     |

| Arithmetic operations            | ADC  | ADD  | SUB  | SBC  | MUL  |       |     |     |

| Shift and Rotates                | SLL  | SRL  | SRA  | RLC  | RRC  | SWAP  | SLA |     |

| Unconditional Jump or Call       | JRA  | JRT  | JRF  | JP   | CALL | CALLR | NOP | RET |

| Conditional Branch               | JRxx |      |      |      |      |       |     |     |

| Interruption management          | TRAP | WFI  | HALT | IRET |      |       |     |     |

| Condition Code Flag modification | SIM  | RIM  | SCF  | RCF  |      |       |     |     |

#### Using a prebyte

The instructions are described with one to four opcodes.

In order to extend the number of available opcodes for an 8-bit CPU (256 opcodes), three different prebyte opcodes are defined. These prebytes modify the meaning of the instruction they precede.

The whole instruction becomes:

| PC-2 | End of | previous instruction |

|------|--------|----------------------|

|------|--------|----------------------|

| PC-1 | Prebyte |

|------|---------|

|------|---------|

PC Opcode

PC+1 Additional word (0 to 2) according to the number of bytes required to compute the effective address These prebytes enable instruction in Y as well as indirect addressing modes to be implemented. They precede the opcode of the instruction in X or the instruction using direct addressing mode. The prebytes are:

PDY 90 Replace an X based instruction using immediate, direct, indexed, or inherent addressing mode by a Y one.

PIX 92 Replace an instruction using direct, direct bit, or direct relative addressing mode to an instruction using the corresponding indirect addressing mode.

It also changes an instruction using X indexed addressing mode to an instruction using indirect X indexed addressing mode.

PIY 91 Replace an instruction using X indirect indexed addressing mode by a Y one.

**/**

| INSTRUCTION SET OVER | /IEW (Cont'd) |

|----------------------|---------------|

|----------------------|---------------|

| Mnemo | Description               | Function/Example    | Dst    | Src | 11 | н | 10 | Ν | Z | С |

|-------|---------------------------|---------------------|--------|-----|----|---|----|---|---|---|

| ADC   | Add with Carry            | A=A+M+C             | А      | М   |    | Н |    | Ν | Ζ | С |

| ADD   | Addition                  | A = A + M           | А      | М   |    | н |    | Ν | Z | С |

| AND   | Logical And               | A = A . M           | А      | М   |    |   |    | Ν | Ζ |   |

| BCP   | Bit compare A, Memory     | tst (A . M)         | А      | М   |    |   |    | Ν | Z |   |

| BRES  | Bit Reset                 | bres Byte, #3       | М      |     |    |   |    |   |   |   |

| BSET  | Bit Set                   | bset Byte, #3       | М      |     |    |   |    |   |   |   |

| BTJF  | Jump if bit is false (0)  | btjf Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| BTJT  | Jump if bit is true (1)   | btjt Byte, #3, Jmp1 | М      |     |    |   |    |   |   | С |

| CALL  | Call subroutine           |                     |        |     |    |   |    |   |   |   |

| CALLR | Call subroutine relative  |                     |        |     |    |   |    |   |   |   |

| CLR   | Clear                     |                     | reg, M |     |    |   |    | 0 | 1 |   |

| СР    | Arithmetic Compare        | tst(Reg - M)        | reg    | М   |    |   |    | Ν | Ζ | С |

| CPL   | One Complement            | A = FFH-A           | reg, M |     |    |   |    | Ν | Ζ | 1 |

| DEC   | Decrement                 | dec Y               | reg, M |     |    |   |    | Ν | Z |   |

| HALT  | Halt                      |                     |        |     | 1  |   | 0  |   |   |   |

| IRET  | Interrupt routine return  | Pop CC, A, X, PC    |        |     | 11 | Н | 10 | Ν | Z | С |

| INC   | Increment                 | inc X               | reg, M |     |    |   |    | Ν | Z |   |

| JP    | Absolute Jump             | jp [TBL.w]          |        |     |    |   |    |   |   |   |

| JRA   | Jump relative always      |                     |        |     |    |   |    |   |   |   |

| JRT   | Jump relative             |                     |        |     |    |   |    |   |   |   |

| JRF   | Never jump                | jrf *               |        |     |    |   |    |   |   |   |

| JRIH  | Jump if ext. INT pin = 1  | (ext. INT pin high) |        |     |    |   |    |   |   |   |

| JRIL  | Jump if ext. INT pin = 0  | (ext. INT pin low)  |        |     |    |   |    |   |   |   |

| JRH   | Jump if H = 1             | H = 1 ?             |        |     |    |   |    |   |   |   |

| JRNH  | Jump if H = 0             | H = 0 ?             |        |     |    |   |    |   |   |   |

| JRM   | Jump if I1:0 = 11         | l1:0 = 11 ?         |        |     |    |   |    |   |   |   |

| JRNM  | Jump if I1:0 <> 11        | 11:0 <> 11 ?        |        |     |    |   |    |   |   |   |

| JRMI  | Jump if N = 1 (minus)     | N = 1 ?             |        |     |    |   |    |   |   |   |

| JRPL  | Jump if N = 0 (plus)      | N = 0 ?             |        |     |    |   |    |   |   |   |

| JREQ  | Jump if Z = 1 (equal)     | Z = 1 ?             |        |     |    |   |    |   |   |   |

| JRNE  | Jump if Z = 0 (not equal) | Z = 0 ?             |        |     |    |   |    |   |   |   |

| JRC   | Jump if C = 1             | C = 1 ?             |        |     |    |   |    |   |   |   |

| JRNC  | Jump if C = 0             | C = 0 ?             |        |     |    |   |    |   |   |   |

| JRULT | Jump if C = 1             | Unsigned <          |        |     |    |   |    |   |   |   |

| JRUGE | Jump if C = 0             | Jmp if unsigned >=  |        |     |    |   |    |   |   |   |

| JRUGT | Jump if $(C + Z = 0)$     | Unsigned >          |        |     |    |   |    |   |   |   |

## **12.4 SUPPLY CURRENT CHARACTERISTICS**

The following current consumption specified for the ST7 functional operating modes over temperature range does not take into account the clock source current consumption. To get the total device consumption, the two current values must be added (except for HALT mode for which the clock is stopped).

#### **12.4.1 CURRENT CONSUMPTION**

| Symbol          | Parameter                                                                                                                                                                                   | Conditions                                                                                                                                                 | Flash I                   | Devices                      | ROM                      | Devices                  | Unit |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------------------|--------------------------|--------------------------|------|

| Symbol          | Parameter                                                                                                                                                                                   | Conditions                                                                                                                                                 | Тур                       | Max <sup>1)</sup>            | Тур                      | Max <sup>1)</sup>        | Unit |

|                 | Supply current in RUN mode <sup>2)</sup>                                                                                                                                                    | $\begin{array}{l} f_{OSC}=2MHz, \ f_{CPU}=1MHz\\ f_{OSC}=4MHz, \ f_{CPU}=2MHz\\ f_{OSC}=8MHz, \ f_{CPU}=4MHz\\ f_{OSC}=16MHz, \ f_{CPU}=8MHz \end{array}$  | 1.3<br>2.0<br>3.6<br>7.1  | 3.0<br>5.0<br>8.0<br>15.0    | 0.5<br>1.2<br>2.2<br>4.8 | 1.0<br>2.0<br>4.0<br>8.0 | mA   |

| I <sub>DD</sub> | Supply current in SLOW mode $ \begin{array}{c} f_{OSC}=2MHz, f_{CPU}=62.5kHz \\ f_{OSC}=4MHz, f_{CPU}=125kHz \\ f_{OSC}=8MHz, f_{CPU}=250kHz \\ f_{OSC}=16MHz, f_{CPU}=500kHz \end{array} $ |                                                                                                                                                            | 600<br>700<br>800<br>1100 | 2700<br>3000<br>3600<br>4000 | 100<br>200<br>300<br>500 | 600<br>700<br>800<br>950 | μΑ   |

|                 | Supply current in WAIT mode 2)                                                                                                                                                              | $\begin{array}{l} f_{OSC}=2MHz, \ f_{CPU}=1MHz\\ f_{OSC}=4MHz, \ f_{CPU}=2MHz\\ f_{OSC}=8MHz, \ f_{CPU}=4MHz\\ f_{OSC}=16MHz, \ f_{CPU}=8MHz \end{array}$  | 0.8<br>1.2<br>2.0<br>3.5  | 3.0<br>4.0<br>5.0<br>7.0     | 0.5<br>0.8<br>1.5<br>3.0 | 1.0<br>1.3<br>2.2<br>4.0 | mA   |

|                 | Supply current in SLOW WAIT mode <sup>2)</sup>                                                                                                                                              | $\begin{array}{l} f_{OSC}=2MHz, f_{CPU}=62.5kHz\\ f_{OSC}=4MHz, f_{CPU}=125kHz\\ f_{OSC}=8MHz, f_{CPU}=250kHz\\ f_{OSC}=16MHz, f_{CPU}=500kHz \end{array}$ | 580<br>650<br>770<br>1050 | 1200<br>1300<br>1800<br>2000 | 50<br>90<br>180<br>350   | 100<br>150<br>300<br>600 | μΑ   |

|                 | Supply current in HALT mode                                                                                                                                                                 | -40°C ≤T <sub>A</sub> ≤+85°C<br>-40°C ≤T <sub>A</sub> ≤+125°C                                                                                              | <1<br>5                   | 10<br>50                     | <1<br><1                 | 10<br>50                 | μA   |

| I <sub>DD</sub> | Supply current in ACTIVE-<br>HALT mode <sup>4)</sup>                                                                                                                                        | $f_{OSC}=2MHz$ $f_{OSC}=4MHz$ $f_{OSC}=4MHz$ $f_{OSC}=16MHz$                                                                                               | 450<br>465<br>530<br>650  | No max.<br>guaran-<br>teed   | 15<br>30<br>60<br>120    | 25<br>50<br>100<br>200   | μΑ   |

Notes:

1. Data based on characterization results, tested in production at  $V_{\text{DD}}$  max. and  $f_{\text{CPU}}$  max.

2. Measurements are done in the following conditions:

- Program executed from RAM, CPU running with RAM access.

- All I/O pins in input mode with a static value at  $V_{\text{DD}}$  or  $V_{\text{SS}}$  (no load)

- All peripherals in reset state.

- LVD disabled.

- Clock input (OSC1) driven by external square wave.

- In SLOW and SLOW WAIT mode,  $\rm f_{CPU}$  is based on  $\rm f_{OSC}$  divided by 32.

To obtain the total current consumption of the device, add the clock source (Section 12.4.2) and the peripheral power consumption (Section 12.4.3).

3. All I/O pins in push-pull 0 mode (when applicable) with a static value at  $V_{DD}$  or VSS (no load), LVD disabled. Data based on characterization results, tested in production at  $V_{DD}$  max. and  $f_{CPU}$  max.

4. Data based on characterisation results, not tested in production. All I/O pins in push-pull 0 mode (when applicable) with a static value at V<sub>DD</sub> or V<sub>SS</sub> (no load); clock input (OSC1) driven by external square wave, LVD disabled. To obtain the total current consumption of the device, add the clock source consumption (Section 12.4.2).

# CLOCK AND TIMING CHARACTERISTICS (Cont'd)

## 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol                                                                                       | Parameter                                      | Сог                  | Conditions      |     |    | Unit  |

|----------------------------------------------------------------------------------------------|------------------------------------------------|----------------------|-----------------|-----|----|-------|

|                                                                                              |                                                | LP: Low powe         | r oscillator    | 1   | 2  |       |

| f <sub>OSC</sub> Oscillator Frequency <sup>1)</sup>                                          | Oppillator Fragmanau 1)                        | MP: Medium p         | ower oscillator | >2  | 4  | N411- |

|                                                                                              | MS: Medium s                                   | >4                   | 8               | MHz |    |       |

|                                                                                              |                                                | HS: High spee        | >8              | 16  | 16 |       |

| R <sub>F</sub>                                                                               | Feedback resistor <sup>2)</sup>                |                      |                 | 20  | 40 | kΩ    |

|                                                                                              | Decomposed of load compatitudes and            | R <sub>S</sub> =200Ω | LP oscillator   | 22  | 56 |       |

| C <sub>L1</sub>                                                                              | Recommended load capacitance ver-              | R <sub>S</sub> =200Ω | MP oscillator   | 22  | 46 |       |

| CL1sus equivalent serial resistance of the<br>crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =200Ω                           | MS oscillator        | 18              | 33  | pF |       |

|                                                                                              | crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =100Ω | HS oscillator   | 15  | 33 |       |

| Symbol         | Parameter            |                                                         | Тур                                                              | Max                     | Unit                     |    |

|----------------|----------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------|----|

| i <sub>2</sub> | OSC2 driving current | V <sub>DD</sub> =5V<br>V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA |

#### Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

# **12.9 CONTROL PIN CHARACTERISTICS**

# 12.9.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                              | Conditions               |                       | Min                             | Тур | Max                 | Unit |

|-------------------------|----------------------------------------|--------------------------|-----------------------|---------------------------------|-----|---------------------|------|

| V <sub>IL</sub>         | Input low level voltage 1)             |                          |                       |                                 |     | 0.3xV <sub>DD</sub> | V    |

| V <sub>IH</sub>         | Input high level voltage <sup>1)</sup> |                          |                       | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                     |      |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 2)  |                          |                       |                                 | 2.5 |                     | V    |

| V <sub>OL</sub>         | Output low level voltage 3)            | V <sub>DD</sub> =5V      | I <sub>IO</sub> =+2mA |                                 | 0.2 | 0.5                 | v    |

| I <sub>IO</sub>         | Input current on RESET pin             |                          |                       |                                 | 2   |                     | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor       |                          |                       | 20                              | 30  | 120                 | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Stretch ap<br>external p |                       | 0                               |     | 42 <sup>6)</sup>    | μs   |

| ( - ,                   |                                        | Internal re              | eset sources          | 20                              | 30  | 42 <sup>6)</sup>    | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                          |                       | 2.5                             |     |                     | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup> |                          |                       |                                 | 200 |                     | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $I_{VSS}$ .

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overrightarrow{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

# **12.11 COMMUNICATION INTERFACE CHARACTERISTICS**

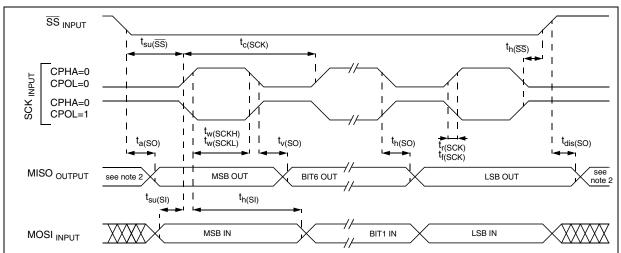

#### 12.11.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{CPU},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                    | Conditions                       | Min                             | Max                      | Unit               |

|----------------------------------------------|------------------------------|----------------------------------|---------------------------------|--------------------------|--------------------|

| f <sub>SCK</sub><br>1/t <sub>c(SCK)</sub>    | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128<br>0.0625 | f <sub>CPU</sub> /4<br>2 | MHz                |

|                                              |                              | Slave<br>f <sub>CPU</sub> =8MHz  | 0                               | f <sub>CPU</sub> /2<br>4 |                    |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time |                                  | see I/O port pin description    |                          |                    |

| t <sub>su(SS)</sub>                          | SS setup time <sup>4)</sup>  | Slave                            | t <sub>CPU</sub> + 50           |                          |                    |

| t <sub>h(SS)</sub>                           | SS hold time                 | Slave                            | 120                             |                          |                    |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time        | Master<br>Slave                  | 100<br>90                       |                          |                    |

| t <sub>su(MI)</sub><br>t <sub>su(SI)</sub>   | Data input setup time        | Master<br>Slave                  | 100<br>100                      |                          |                    |

| t <sub>h(MI)</sub><br>t <sub>h(SI)</sub>     | Data input hold time         | Master<br>Slave                  | 100<br>100                      |                          | ns                 |

| t <sub>a(SO)</sub>                           | Data output access time      | Slave                            | 0                               | 120                      |                    |

| t <sub>dis(SO)</sub>                         | Data output disable time     | Slave                            |                                 | 240                      |                    |

| t <sub>v(SO)</sub>                           | Data output valid time       | Slave (after enable edge)        |                                 | 120                      |                    |

| t <sub>h(SO)</sub>                           | Data output hold time        | Slave (after enable edge)        | 0                               |                          |                    |

| t <sub>v(MO)</sub>                           | Data output valid time       | Master (after enable edge)       |                                 | 120                      | - t <sub>CPU</sub> |

| t <sub>h(MO)</sub>                           | Data output hold time        |                                  | 0                               |                          |                    |

# Figure 89. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

1. Data based on design simulation and/or characterisation results, not tested in production.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

- 3. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

- 4. Depends on f<sub>CPU</sub>. For example, if f<sub>CPU</sub> = 8 MHz, then t<sub>CPU</sub> = 1 / f<sub>CPU</sub> = 125 ns and t<sub>su(SS)</sub> = 175 ns.

# DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

#### Table 30. Suggested List of Socket Types

| Device        | Socket (supplied with ST7MDT20M-<br>EMU3) | Emulator Adapter (supplied with<br>ST7MDT20M-EMU3) |

|---------------|-------------------------------------------|----------------------------------------------------|

| LQFP64 14 x14 | CAB 3303262                               | CAB 3303351                                        |

| LQFP64 10 x10 | YAMAICHI IC149-064-*75-*5                 | YAMAICHI ICP-064-6                                 |

| LQFP44 10 X10 | YAMAICHI IC149-044-*52-*5                 | YAMAICHI ICP-044-5                                 |

| LQFP32 7 X 7  | IRONWOOD SF-QFE32SA-L-01                  | IRONWOOD SK-UGA06/32A-01                           |

# 14.3.4 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 30.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet.

#### **Related Documentation**

AN 978: ST7 Visual Develop Software Key Debugging Features

AN 1938: ST7 Visual Develop for ST7 Cosmic C toolset users

AN 1940: ST7 Visual Develop for ST7 Assembler Linker toolset users