Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 32KB (32K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bj6t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Table of Contents ——

\_\_\_\_\_

| 14.1 FLASH OPTION BYTES 12                                        | 74 |

|-------------------------------------------------------------------|----|

| 14.2 DEVICE ORDERING INFORMATION AND TRANSFER OF CUSTOMER CODE 17 | 76 |

| 14.3 DEVELOPMENT TOOLS                                            | 78 |

| 14.3.1 Starter kits 1                                             | 78 |

| 14.3.2 Development and debugging tools 1                          | 78 |

| 14.3.3 Programming tools 1                                        |    |

| 14.3.4 Socket and Emulator Adapter Information                    |    |

| 14.4 ST7 APPLICATION NOTES                                        | 80 |

| 15 KNOWN LIMITATIONS                                              | 83 |

| 15.1 ALL DEVICES                                                  | 83 |

| 15.1.1 Unexpected Reset Fetch 18                                  | 83 |

| 15.1.2 External interrupt missed 18                               |    |

| 15.1.3 Clearing active interrupts outside interrupt routine       | 84 |

| 15.1.4 SCI Wrong Break duration                                   | 85 |

| 15.1.5 16-bit Timer PWM Mode 18                                   |    |

| 15.1.6 TIMD set simultaneously with OC interrupt 18               | 85 |

| 15.1.7 I2C Multimaster 18                                         | 85 |

| 15.1.8 Pull-up always active on PE2 18                            |    |

| 15.1.9 ADC accuracy 32K Flash devices 18                          |    |

| 16 REVISION HISTORY                                               | 86 |

57

# CENTRAL PROCESSING UNIT (Cont'd)

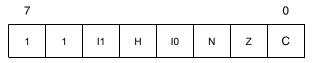

### **Condition Code Register (CC)**

Read/Write

Reset Value: 111x1xxx

The 8-bit Condition Code register contains the interrupt masks and four flags representative of the result of the instruction just executed. This register can also be handled by the PUSH and POP instructions.

These bits can be individually tested and/or controlled by specific instructions.

#### **Arithmetic Management Bits**

Bit  $4 = \mathbf{H}$  Half carry.

This bit is set by hardware when a carry occurs between bits 3 and 4 of the ALU during an ADD or ADC instructions. It is reset by hardware during the same instructions.

0: No half carry has occurred. 1: A half carry has occurred.

This bit is tested using the JRH or JRNH instruction. The H bit is useful in BCD arithmetic subroutines.

#### Bit 2 = **N** *Negative*.

This bit is set and cleared by hardware. It is representative of the result sign of the last arithmetic, logical or data manipulation. It's a copy of the result 7<sup>th</sup> bit.

0: The result of the last operation is positive or null.

1: The result of the last operation is negative

(that is, the most significant bit is a logic 1).

This bit is accessed by the JRMI and JRPL instructions.

# Bit 1 = **Z** Zero.

This bit is set and cleared by hardware. This bit indicates that the result of the last arithmetic, logical or data manipulation is zero.

- 0: The result of the last operation is different from zero.

- 1: The result of the last operation is zero.

This bit is accessed by the JREQ and JRNE test instructions.

#### Bit 0 = C Carry/borrow.

This bit is set and cleared by hardware and software. It indicates an overflow or an underflow has occurred during the last arithmetic operation.

0: No overflow or underflow has occurred.

1: An overflow or underflow has occurred.

This bit is driven by the SCF and RCF instructions and tested by the JRC and JRNC instructions. It is also affected by the "bit test and branch", shift and rotate instructions.

#### Interrupt Management Bits

Bit 5,3 = 11, 10 Interrupt

The combination of the I1 and I0 bits gives the current interrupt software priority.

| Interrupt Software Priority   | 11 | 10 |

|-------------------------------|----|----|

| Level 0 (main)                | 1  | 0  |

| Level 1                       | 0  | 1  |

| Level 2                       | 0  | 0  |

| Level 3 (= interrupt disable) | 1  | 1  |

These two bits are set/cleared by hardware when entering in interrupt. The loaded value is given by the corresponding bits in the interrupt software priority registers (IxSPR). They can be also set/ cleared by software with the RIM, SIM, IRET, HALT, WFI and PUSH/POP instructions.

See the interrupt management chapter for more details.

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

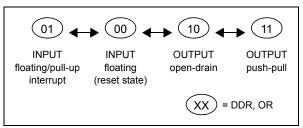

#### 9.3 I/O PORT IMPLEMENTATION

**ل ح**ک

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 2 on page 4. Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 32. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode Description |                                                                                      |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|

| WAIT             | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |  |  |  |  |  |  |

| HALT             | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |  |  |  |  |  |  |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| External interrupt on selected external event | -             | DDRx<br>ORx              | Yes                  |                      |

49/187

# I/O PORTS (Cont'd)

# Table 13. I/O Port Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label        | 7   | 6 | 5 | 4 | 3 | 2 | 1 | 0   |

|-------------------|--------------------------|-----|---|---|---|---|---|---|-----|

|                   | t Value<br>ort registers | 0   | 0 | 0 | 0 | 0 | 0 | 0 | 0   |

| 0000h             | PADR                     |     |   |   |   |   |   |   |     |

| 0001h             | PADDR                    | MSB |   |   |   |   |   |   | LSB |

| 0002h             | PAOR                     |     |   |   |   |   |   |   |     |

| 0003h             | PBDR                     |     |   |   |   |   |   |   |     |

| 0004h             | PBDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0005h             | PBOR                     |     |   |   |   |   |   |   |     |

| 0006h             | PCDR                     |     |   |   |   |   |   |   |     |

| 0007h             | PCDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0008h             | PCOR                     |     |   |   |   |   |   |   |     |

| 0009h             | PDDR                     |     |   |   |   |   |   |   |     |

| 000Ah             | PDDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Bh             | PDOR                     |     |   |   |   |   |   |   |     |

| 000Ch             | PEDR                     |     |   |   |   |   |   |   |     |

| 000Dh             | PEDDR                    | MSB |   |   |   |   |   |   | LSB |

| 000Eh             | PEOR                     |     |   |   |   |   |   |   |     |

| 000Fh             | PFDR                     |     |   |   |   |   |   |   |     |

| 0010h             | PFDDR                    | MSB |   |   |   |   |   |   | LSB |

| 0011h             | PFOR                     |     |   |   |   |   |   |   |     |

# **Related Documentation**

AN 970: SPI Communication between ST7 and EEPROM

AN1045: S/W implementation of I2C bus master AN1048: Software LCD driver

57

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | Т0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

# Table 14. Watchdog Timer Register Map and Reset Values

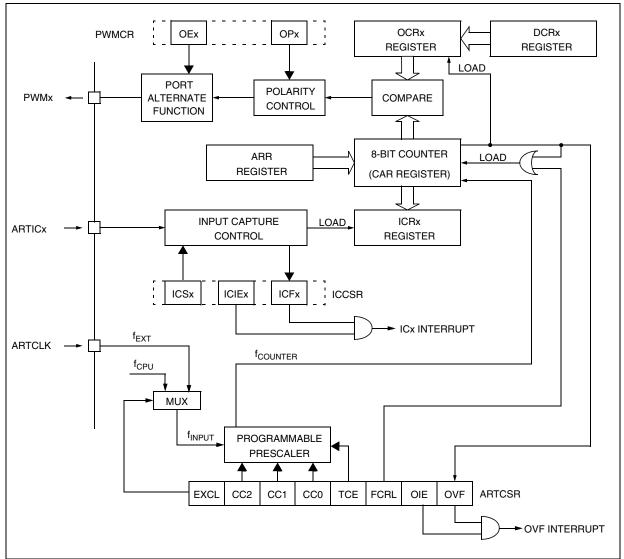

# **10.3 PWM AUTO-RELOAD TIMER (ART)**

#### **10.3.1 Introduction**

The Pulse Width Modulated Auto-Reload Timer on-chip peripheral consists of an 8-bit auto reload counter with compare/capture capabilities and of a 7-bit prescaler clock source.

These resources allow five possible operating modes:

- Generation of up to 4 independent PWM signals

- Output compare and Time base interrupt

- Up to two input capture functions

- External event detector

- Up to two external interrupt sources

The three first modes can be used together with a single counter frequency.

The timer can be used to wake up the MCU from WAIT and HALT modes.

# **ON-CHIP PERIPHERALS** (Cont'd)

### 10.3.3 Register Description

# **CONTROL / STATUS REGISTER (ARTCSR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7    |     |     |     |     |      |     | 0   |

|------|-----|-----|-----|-----|------|-----|-----|

| EXCL | CC2 | CC1 | CC0 | TCE | FCRL | OIE | OVF |

#### Bit 7 = **EXCL** External Clock

This bit is set and cleared by software. It selects the input clock for the 7-bit prescaler.

0: CPU clock. 1: External clock.

Bit 6:4 = **CC[2:0]** Counter Clock Control These bits are set and cleared by software. They determine the prescaler division ratio from  $f_{INPUT}$ .

| fCOUNTER                 | With f <sub>INPUT</sub> =8 MHz | CC2 | CC1 | CC0 |

|--------------------------|--------------------------------|-----|-----|-----|

| f <sub>INPUT</sub>       | 8 MHz                          | 0   | 0   | 0   |

| f <sub>INPUT</sub> / 2   | 4 MHz                          | 0   | 0   | 1   |

| f <sub>INPUT</sub> / 4   | 2 MHz                          | 0   | 1   | 0   |

| f <sub>INPUT</sub> / 8   | 1 MHz                          | 0   | 1   | 1   |

| f <sub>INPUT</sub> / 16  | 500 kHz                        | 1   | 0   | 0   |

| f <sub>INPUT</sub> / 32  | 250 kHz                        | 1   | 0   | 1   |

| f <sub>INPUT</sub> / 64  | 125 kHz                        | 1   | 1   | 0   |

| f <sub>INPUT</sub> / 128 | 62.5 kHz                       | 1   | 1   | 1   |

# Bit 3 = **TCE** *Timer Counter Enable*

This bit is set and cleared by software. It puts the timer in the lowest power consumption mode.

0: Counter stopped (prescaler and counter frozen).1: Counter running.

# Bit 2 = **FCRL** Force Counter Re-Load

This bit is write-only and any attempt to read it will yield a logical zero. When set, it causes the contents of ARTARR register to be loaded into the counter, and the content of the prescaler register to be cleared in order to initialize the timer before starting to count.

#### Bit 1 = **OIE** Overflow Interrupt Enable

This bit is set and cleared by software. It allows to enable/disable the interrupt which is generated when the OVF bit is set.

0: Overflow Interrupt disable.

1: Overflow Interrupt enable.

# Bit 0 = **OVF** Overflow Flag

This bit is set by hardware and cleared by software reading the ARTCSR register. It indicates the transition of the counter from FFh to the ARTARR value.

#### 0: New transition not yet reached 1: Transition reached

# COUNTER ACCESS REGISTER (ARTCAR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| CA7 | CA6 | CA5 | CA4 | CA3 | CA2 | CA1 | CA0 |

#### Bit 7:0 = CA[7:0] Counter Access Data

These bits can be set and cleared either by hardware or by software. The ARTCAR register is used to read or write the auto-reload counter "on the fly" (while it is counting).

### AUTO-RELOAD REGISTER (ARTARR)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| AR7 | AR6 | AR5 | AR4 | AR3 | AR2 | AR1 | AR0 |

#### Bit 7:0 = AR[7:0] Counter Auto-Reload Data

These bits are set and cleared by software. They are used to hold the auto-reload value which is automatically loaded in the counter when an overflow occurs. At the same time, the PWM output levels are changed according to the corresponding OPx bit in the PWMCR register.

This register has two PWM management functions:

- Adjusting the PWM frequency

- Setting the PWM duty cycle resolution

#### PWM Frequency vs Resolution:

| ARTARR     | Resolution | f <sub>₽₩M</sub> |           |  |  |

|------------|------------|------------------|-----------|--|--|

| value      | Resolution | Min              | Max       |  |  |

| 0          | 8-bit      | ~0.244 kHz       | 31.25 kHz |  |  |

| [ 0127 ]   | > 7-bit    | ~0.244 kHz       | 62.5 kHz  |  |  |

| [ 128191 ] | > 6-bit    | ~0.488 kHz       | 125 kHz   |  |  |

| [ 192223 ] | > 5-bit    | ~0.977 kHz       | 250 kHz   |  |  |

| [ 224239 ] | > 4-bit    | ~1.953 kHz       | 500 kHz   |  |  |

# 16-BIT TIMER (Cont'd)

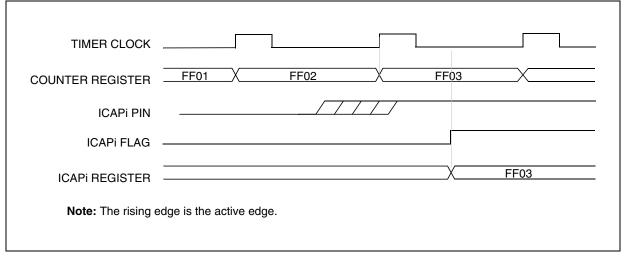

# Figure 47. Input Capture Block Diagram

# Figure 48. Input Capture Timing Diagram

**لركم**

### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

# 10.6.7 Register Description

### STATUS REGISTER (SCISR)

Read Only

Reset Value: 1100 0000 (C0h)

| 7    |    |      |      |    |    |    | 0  |  |

|------|----|------|------|----|----|----|----|--|

| TDRE | тс | RDRF | IDLE | OR | NF | FE | PE |  |

Bit 7 = **TDRE** *Transmit data register empty.*

This bit is set by hardware when the content of the TDR register has been transferred into the shift register. An interrupt is generated if the TIE bit = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Data is not transferred to the shift register 1: Data is transferred to the shift register

**Note:** Data is not transferred to the shift register unless the TDRE bit is cleared.

#### Bit 6 = **TC** *Transmission complete.*

This bit is set by hardware when transmission of a frame containing Data is complete. An interrupt is generated if TCIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a write to the SCIDR register).

0: Transmission is not complete

1: Transmission is complete

**Note:** TC is not set after the transmission of a Preamble or a Break.

#### Bit 5 = **RDRF** Received data ready flag.

This bit is set by hardware when the content of the RDR register has been transferred to the SCIDR register. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: Data is not received

1: Received data is ready to be read

#### Bit 4 = **IDLE** *Idle line detect.*

This bit is set by hardware when a Idle Line is detected. An interrupt is generated if the ILIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register). 0: No Idle Line is detected

1: Idle Line is detected

1. Idle Lille is delected

**Note:** The IDLE bit is not set again until the RDRF bit has been set itself (that is, a new idle line occurs).

#### Bit 3 = **OR** Overrun error.

This bit is set by hardware when the word currently being received in the shift register is ready to be transferred into the RDR register while RDRF = 1. An interrupt is generated if RIE = 1 in the SCICR2 register. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Overrun error

1: Overrun error is detected

**Note:** When this bit is set RDR register content is not lost but the shift register is overwritten.

#### Bit 2 = NF Noise flag.

This bit is set by hardware when noise is detected on a received frame. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register). 0: No noise is detected

1: Noise is detected

1. Noise is delected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt.

#### Bit 1 = **FE** Framing error.

This bit is set by hardware when a de-synchronization, excessive noise or a break character is detected. It is cleared by a software sequence (an access to the SCISR register followed by a read to the SCIDR register).

0: No Framing error is detected

1: Framing error or break character is detected

**Note:** This bit does not generate interrupt as it appears at the same time as the RDRF bit which itself generates an interrupt. If the word currently being transferred causes both frame error and overrun error, it will be transferred and only the OR bit will be set.

#### Bit 0 = PE Parity error.

This bit is set by hardware when a parity error occurs in receiver mode. It is cleared by a software sequence (a read to the status register followed by an access to the SCIDR data register). An interrupt is generated if PIE = 1 in the SCICR1 register. 0: No parity error

1: Parity error

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

#### Master Transmitter

Following the address transmission and after SR1 register has been read, the master sends bytes from the DR register to the SDA line via the internal shift register.

The master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV8).

When the acknowledge bit is received, the interface sets:

EVF and BTF bits with an interrupt if the ITE bit is set.

To close the communication: after writing the last byte to the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

#### **Error Cases**

**ل ح**ک

BERR: Detection of a Stop or a Start condition during a byte transfer. In this case, the EVF and BERR bits are set by hardware with an interrupt if ITE is set.

Note that BERR will not be set if an error is detected during the first or second pulse of each 9bit transaction:

Single Master Mode

If a Start or Stop is issued during the first or second pulse of a 9-bit transaction, the BERR flag will not be set and transfer will continue however the BUSY flag will be reset. To work around this, slave devices should issue a NACK when they receive a misplaced Start or Stop. The reception of a NACK or BUSY by the master in the middle of communication gives the possibility to reinitiate transmission.

Multimaster Mode

Normally the BERR bit would be set whenever unauthorized transmission takes place while transfer is already in progress. However, an issue will arise if an external master generates an unauthorized Start or Stop while the I<sup>2</sup>C master is on the first or second pulse of a 9-bit transaction. It is possible to work around this by polling the BUSY bit during I<sup>2</sup>C master mode transmission. The resetting of the BUSY bit can then be handled in a similar manner as the BERR flag being set.

- AF: Detection of a non-acknowledge bit. In this case, the EVF and AF bits are set by hardware with an interrupt if the ITE bit is set. To resume, set the Start or Stop bit.

The AF bit is cleared by reading the I2CSR2 register. However, if read before the completion of the transmission, the AF flag will be set again, thus possibly generating a new interrupt. Software must ensure either that the SCL line is back at 0 before reading the SR2 register, or be able to correctly handle a second interrupt during the 9th pulse of a transmitted byte.

- ARLO: Detection of an arbitration lost condition. In this case the ARLO bit is set by hardware (with an interrupt if the ITE bit is set and the interface goes automatically back to slave mode (the M/SL bit is cleared).

**Note:** In all these cases, the SCL line is not held low; however, the SDA line can remain low due to possible «0» bits transmitted last. It is then necessary to release both lines by software.

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

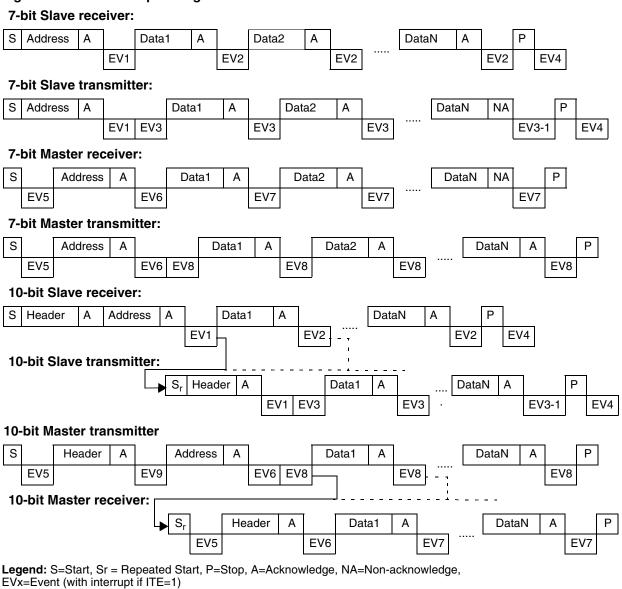

### Figure 67. Transfer Sequencing

EV1: EVF=1, ADSL=1, cleared by reading SR1 register.

EV2: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

EV3: EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

EV3-1: EVF=1, AF=1, BTF=1; AF is cleared by reading SR1 register. BTF is cleared by releasing the

lines (STOP=1, STOP=0) or by writing DR register (DR=FFh). Note: If lines are released by

STOP=1, STOP=0, the subsequent EV4 is not seen.

EV4: EVF=1, STOPF=1, cleared by reading SR2 register.

EV5: EVF=1, SB=1, cleared by reading SR1 register followed by writing DR register.

EV6: EVF=1, cleared by reading SR1 register followed by writing CR register (for example PE=1).

EV7: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

EV8: EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

EV9: EVF=1, ADD10=1, cleared by reading SR1 register followed by writing DR register.

# I<sup>2</sup>C BUS INTERFACE (Cont'd)

# 10.7.5 Low Power Modes

| Mode | Description                                                                                                                                                                                                                                                                      |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WAIT | No effect on I <sup>2</sup> C interface.<br>I <sup>2</sup> C interrupts cause the device to exit from WAIT mode.                                                                                                                                                                 |

| HALT | I <sup>2</sup> C registers are frozen.<br>In HALT mode, the I <sup>2</sup> C interface is inactive and does not acknowledge data on the bus. The I <sup>2</sup> C interface<br>resumes operation when the MCU is woken up by an interrupt with "exit from HALT mode" capability. |

### 10.7.6 Interrupts

57

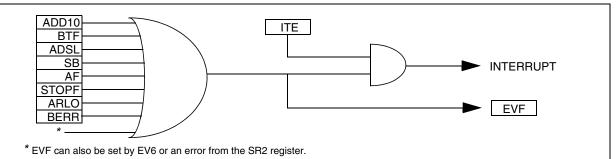

# Figure 68. Event Flags and Interrupt Generation

| Interrupt Event                                    | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|----------------------------------------------------|---------------|--------------------------|----------------------|----------------------|

| 10-bit Address Sent Event (Master mode)            | ADD10         |                          | Yes                  | No                   |

| End of Byte Transfer Event                         | BTF           |                          | Yes                  | No                   |

| Address Matched Event (Slave mode)                 | ADSEL         |                          | Yes                  | No                   |

| Start Bit Generation Event (Master mode)           | SB            | ITE                      | Yes                  | No                   |

| Acknowledge Failure Event                          | AF            |                          | Yes                  | No                   |

| Stop Detection Event (Slave mode)                  | STOPF         |                          | Yes                  | No                   |

| Arbitration Lost Event (Multimaster configuration) | ARLO          |                          | Yes                  | No                   |

| Bus Error Event                                    | BERR          |                          | Yes                  | No                   |

**Note**: The  $I^2C$  interrupt events are connected to the same interrupt vector (see Interrupts chapter). They generate an interrupt if the corresponding Enable Control Bit is set and the I-bit in the CC register is reset (RIM instruction).

121/187

# I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C OWN ADDRESS REGISTER (OAR1)

Read / Write Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

#### 7-bit Addressing Mode

Bit 7:1 = ADD[7:1] Interface address.

These bits define the  $l^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

Bit 0 = **ADD0** Address direction bit.

This bit is don't care, the interface acknowledges either 0 or 1. It is not cleared when the interface is disabled (PE=0).

Note: Address 01h is always ignored.

#### **10-bit Addressing Mode**

Bit 7:0 = **ADD**[7:0] Interface address. These are the least significant bits of the  $I^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

# I<sup>2</sup>C OWN ADDRESS REGISTER (OAR2)

#### Read / Write

Reset Value: 0100 0000 (40h)

| 7   |     |   |   |   |      |      | 0 |

|-----|-----|---|---|---|------|------|---|

| FR1 | FR0 | 0 | 0 | 0 | ADD9 | ADD8 | 0 |

#### Bit 7:6 = **FR[1:0]** Frequency bits.

These bits are set by software only when the interface is disabled (PE=0). To configure the interface to  $I^2C$  specified delays select the value corresponding to the microcontroller frequency  $F_{CPU}$ .

| f <sub>CPU</sub> | FR1 | FR0 |

|------------------|-----|-----|

| < 6 MHz          | 0   | 0   |

| 6 to 8 MHz       | 0   | 1   |

Bit 5:3 = Reserved

#### Bit 2:1 = ADD[9:8] Interface address.

These are the most significant bits of the  $I^2C$  bus address of the interface (10-bit mode only). They are not cleared when the interface is disabled (PE=0).

### Bit 0 = Reserved.

# **OPERATING CONDITIONS** (Cont'd)

# 12.3.2 Operating Conditions with Low Voltage Detector (LVD)

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                    | Conditions                                   | Min                | Тур  | Max                 | Unit |

|-----------------------|--------------------------------------------------------------|----------------------------------------------|--------------------|------|---------------------|------|

|                       | Reset release threshold                                      | VD level = High in option byte               | 4.0 <sup>1)</sup>  | 4.2  | 4.5                 |      |

| V <sub>IT+(LVD)</sub> | (V <sub>DD</sub> rise)                                       | VD level = Med. in option byte <sup>2)</sup> | 3.55 <sup>1)</sup> | 3.75 | 4.0 <sup>1)</sup>   |      |

|                       |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.95 <sup>1)</sup> | 3.15 | 3.35 <sup>1)</sup>  | V    |

|                       | Reset generation threshold                                   | VD level = High in option byte               | 3.8                | 4.0  | 4.25 <sup>1)</sup>  | v    |

| V <sub>IT-(LVD)</sub> | (V <sub>DD</sub> fall)                                       | VD level = Med. in option byte <sup>2)</sup> | 3.35 <sup>1)</sup> | 3.55 | 3.75 <sup>1))</sup> |      |

|                       |                                                              | VD level = Low in option byte <sup>2)</sup>  | 2.8 <sup>1)</sup>  | 3.0  | 3.15 <sup>1)</sup>  |      |

| V <sub>hys(LVD)</sub> | LVD voltage threshold hysteresis                             | V <sub>IT+(LVD)</sub> -V <sub>IT-(LVD)</sub> |                    | 200  |                     | mV   |

| Vt <sub>POR</sub>     | V <sub>DD</sub> rise time <sup>3)2)</sup>                    | LVD enabled                                  | 6µs/V              |      | 100ms/V             |      |

| t <sub>g(VDD)</sub>   | $V_{DD}$ glitches filtered (not detected) by LVD $^{\rm 3)}$ |                                              |                    |      | 40                  | ns   |

Notes:

1. Data based on characterization results, tested in production for ROM devices only.

2. If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

3. Data based on characterization results, not tested in production.

3. When Vt<sub>POR</sub> is faster than 100  $\mu$ s/V, the Reset signal is released after a delay of max. 42 $\mu$ s after V<sub>DD</sub> crosses the V<sub>IT+(LVD)</sub> threshold.

# 12.3.3 Auxiliary Voltage Detector (AVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                    | Conditions                                                      | Min                                     | Тур         | Max                                    | Unit |

|-----------------------|--------------------------------------------------------------|-----------------------------------------------------------------|-----------------------------------------|-------------|----------------------------------------|------|

|                       | 1 $\Rightarrow$ 0 AVDF flag toggle threshold                 | VD level = High in option byte                                  | 4.4 <sup>1)</sup>                       | 4.6         | 4.9 <sup>1)</sup>                      |      |

| V <sub>IT+(AVD)</sub> | $(V_{DD} rise)$                                              | VD level = Med. in option byte<br>VD level = Low in option byte | 3.95 <sup>1)</sup><br>3.4 <sup>1)</sup> | 4.15<br>3.6 | 4.4 <sup>1)</sup><br>3.8 <sup>1)</sup> | V    |

|                       | $0 \Rightarrow 1 \text{ AVDF flag toggle threshold}$         | VD level = High in option byte                                  | 4.2 <sup>1)</sup>                       | 4.4         | 4.65 <sup>1)</sup>                     | v    |

| V <sub>IT-(AVD)</sub> | $(V_{DD} \text{ fall})$                                      | VD level = Med. in option byte<br>VD level = Low in option byte | 3.75 <sup>1)</sup><br>3.2 <sup>1)</sup> | 4.0<br>3.4  | 4.2 <sup>1)</sup><br>3.6 <sup>1)</sup> |      |

| V <sub>hys(AVD)</sub> | AVD voltage threshold hysteresis                             | V <sub>IT+(AVD)</sub> -V <sub>IT-(AVD)</sub>                    |                                         | 200         |                                        | mV   |

| $\Delta V_{IT-}$      | Voltage drop between AVD flag set<br>and LVD reset activated | V <sub>IT-(AVD)</sub> -V <sub>IT-(LVD)</sub>                    |                                         | 450         |                                        | mV   |

1. Data based on characterization results, tested in production for ROM devices only.

#### 12.3.4 External Voltage Detector (EVD) Thresholds

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$ .

| Symbol                | Parameter                                                                            | Conditions                                   | Min  | Тур  | Max  | Unit |

|-----------------------|--------------------------------------------------------------------------------------|----------------------------------------------|------|------|------|------|

| V <sub>IT+(EVD)</sub> | 1 $\Rightarrow$ 0 AVDF flag toggle threshold $(V_{DD} rise)^{1)}$                    |                                              | 1.15 | 1.26 | 1.35 | V    |

| V <sub>IT-(EVD)</sub> | $0 \Rightarrow 1 \text{ AVDF flag toggle threshold}$<br>$(V_{DD} \text{ fall})^{1)}$ |                                              | 1.1  | 1.2  | 1.3  | v    |

| V <sub>hys(EVD)</sub> | EVD voltage threshold hysteresis                                                     | V <sub>IT+(EVD)</sub> -V <sub>IT-(EVD)</sub> |      | 200  |      | mV   |

1. Data based on characterization results, not tested in production.

<u>ل</u>رک

# CLOCK CHARACTERISTICS (Cont'd)

Note:

1. Data based on characterization results.

### **12.5.5 PLL Characteristics**

| Symbol                             | Parameter                              | Conditions                | Min | Тур | Max | Unit |

|------------------------------------|----------------------------------------|---------------------------|-----|-----|-----|------|

| f <sub>OSC</sub>                   | PLL input frequency range              |                           | 2   |     | 4   | MHz  |

| $\Delta f_{\rm CPU} / f_{\rm CPU}$ | Instantaneous PLL jitter <sup>1)</sup> | f <sub>OSC</sub> = 4 MHz. |     | 0.7 | 2   | %    |

Note:

1. Data characterized but not tested.

The user must take the PLL jitter into account in the application (for example in serial communication or sampling of high frequency signals). The PLL jitter is a periodic effect, which is integrated over several CPU cycles. Therefore the longer the period of the application signal, the less it will be impacted by the PLL jitter.

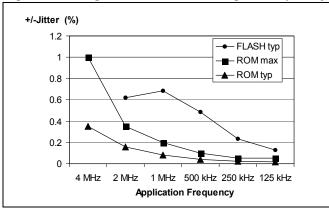

Figure 77 shows the PLL jitter integrated on application signals in the range 125kHz to 4MHz. At frequencies of less than 125KHz, the jitter is negligible.

Figure 77. Integrated PLL Jitter vs signal frequency<sup>1</sup>

Note 1: Measurement conditions: f<sub>CPU</sub> = 8MHz.

# **12.6 MEMORY CHARACTERISTICS**

#### 12.6.1 RAM and Hardware Registers

| Symbol          | Parameter                         | Conditions           | Min | Тур | Max | Unit |

|-----------------|-----------------------------------|----------------------|-----|-----|-----|------|

| V <sub>RM</sub> | Data retention mode <sup>1)</sup> | HALT mode (or RESET) | 1.6 |     |     | V    |

#### 12.6.2 FLASH Memory

| DUAL VOL                                | TAGE HDFLASH MEMORY                           |                                    |                   |     |                   |        |

|-----------------------------------------|-----------------------------------------------|------------------------------------|-------------------|-----|-------------------|--------|

| Symbol                                  | Parameter                                     | Conditions                         | Min <sup>2)</sup> | Тур | Max <sup>2)</sup> | Unit   |

| £                                       | Operating frequency                           | Read mode                          | 0                 |     | 8                 | MHz    |

| f <sub>CPU</sub>                        | Operating frequency                           | Write / Erase mode                 | 1                 |     | 8                 |        |

| V <sub>PP</sub>                         | Programming voltage <sup>3)</sup>             | $4.5V \leq V_{DD} \leq 5.5V$       | 11.4              |     | 12.6              | V      |

|                                         |                                               | RUN mode (f <sub>CPU</sub> = 4MHz) |                   |     | 3                 | mA     |

| I <sub>DD</sub>                         | Supply current <sup>4)</sup>                  | Write / Erase                      |                   | 0   |                   | ma     |

|                                         |                                               | Power down mode / HALT             |                   | 1   | 10                | μA     |

| 1                                       | VPP current <sup>4)</sup>                     | Read (V <sub>PP</sub> =12V)        |                   |     | 200               | μΑ     |

| I <sub>PP</sub>                         |                                               | Write / Erase                      |                   |     | 30                | mA     |

| t <sub>VPP</sub>                        | Internal V <sub>PP</sub> stabilization time   |                                    |                   | 10  |                   | μs     |

|                                         |                                               | T <sub>A</sub> =85°C               | 40                |     |                   |        |

| t <sub>RET</sub>                        | Data retention                                | T <sub>A</sub> =105°C              | 15                |     |                   | years  |

|                                         |                                               | T <sub>A</sub> =125°C              | 7                 |     |                   |        |

| N                                       | Write erase cycles                            | T <sub>A</sub> = 55°C              | 1000              |     |                   | cycles |

| N <sub>RW</sub>                         | while erase cycles                            | T <sub>A</sub> = 85°C              | 100               |     |                   | cycles |

| T <sub>PROG</sub><br>T <sub>ERASE</sub> | Programming or erasing tempera-<br>ture range |                                    | -40               | 25  | 85                | °C     |

Notes:

1. Minimum  $V_{DD}$  supply voltage without losing data stored in RAM (in HALT mode or under RESET) or in hardware registers (only in HALT mode). Not tested in production.

2. Data based on characterization results, not tested in production.

3. V<sub>PP</sub> must be applied only during the programming or erasing operation and not permanently for reliability reasons.

4. Data based on simulation results, not tested in production.

Warning: Do not connect 12V to  $V_{PP}$  before  $V_{DD}$  is powered on, as this may damage the device.

151/187

57

# I/O PORT PIN CHARACTERISTICS (Cont'd)

57

# **12.9 CONTROL PIN CHARACTERISTICS**

# 12.9.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                  | Parameter                              | Conditions                        |                       | Min                             | Тур | Max                 | Unit |

|-------------------------|----------------------------------------|-----------------------------------|-----------------------|---------------------------------|-----|---------------------|------|

| V <sub>IL</sub>         | Input low level voltage 1)             |                                   |                       |                                 |     | 0.3xV <sub>DD</sub> | V    |

| V <sub>IH</sub>         | Input high level voltage <sup>1)</sup> |                                   |                       | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                     |      |

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 2)  |                                   |                       |                                 | 2.5 |                     | V    |

| V <sub>OL</sub>         | Output low level voltage 3)            | V <sub>DD</sub> =5V               | I <sub>IO</sub> =+2mA |                                 | 0.2 | 0.5                 | v    |

| I <sub>IO</sub>         | Input current on RESET pin             |                                   |                       |                                 | 2   |                     | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor       |                                   |                       | 20                              | 30  | 120                 | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Stretch applied on external pulse |                       | 0                               |     | 42 <sup>6)</sup>    | μs   |

|                         |                                        | Internal reset sources            |                       | 20                              | 30  | 42 <sup>6)</sup>    | μs   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                                   |                       | 2.5                             |     |                     | μs   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup> |                                   |                       |                                 | 200 |                     | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed  $I_{VSS}$ .

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overrightarrow{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

# **12.11 COMMUNICATION INTERFACE CHARACTERISTICS**

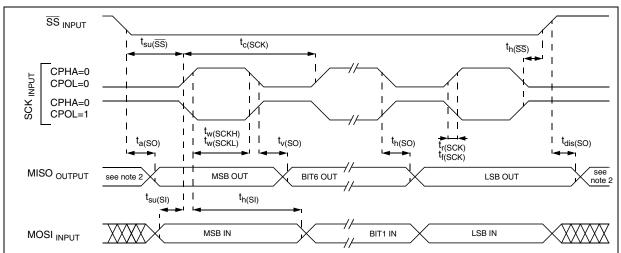

#### 12.11.1 SPI - Serial Peripheral Interface

Subject to general operating conditions for  $V_{DD}, f_{CPU},$  and  $T_A$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (SS, SCK, MOSI, MISO).

| Symbol                                       | Parameter                    | Conditions                       | Min                             | Max                      | Unit             |  |

|----------------------------------------------|------------------------------|----------------------------------|---------------------------------|--------------------------|------------------|--|

| f <sub>SCK</sub>                             | SPI clock frequency          | Master<br>f <sub>CPU</sub> =8MHz | f <sub>CPU</sub> /128<br>0.0625 | f <sub>CPU</sub> /4<br>2 | MHz              |  |

| 1/t <sub>c(SCK)</sub>                        |                              | Slave<br>f <sub>CPU</sub> =8MHz  | 0                               | f <sub>CPU</sub> /2<br>4 |                  |  |

| t <sub>r(SCK)</sub><br>t <sub>f(SCK)</sub>   | SPI clock rise and fall time |                                  | see I/O port pin description    |                          |                  |  |

| t <sub>su(SS)</sub>                          | SS setup time <sup>4)</sup>  | Slave                            | t <sub>CPU</sub> + 50           |                          |                  |  |

| t <sub>h(SS)</sub>                           | SS hold time                 | Slave                            | 120                             |                          |                  |  |

| t <sub>w(SCKH)</sub><br>t <sub>w(SCKL)</sub> | SCK high and low time        | Master<br>Slave                  | 100<br>90                       |                          |                  |  |

| t <sub>su(MI)</sub><br>t <sub>su(SI)</sub>   | Data input setup time        | Master<br>Slave                  | 100<br>100                      |                          | ns               |  |

| t <sub>h(MI)</sub><br>t <sub>h(SI)</sub>     | Data input hold time         | Master<br>Slave                  | 100<br>100                      |                          |                  |  |

| t <sub>a(SO)</sub>                           | Data output access time      | Slave                            | 0                               | 120                      | 120              |  |

| t <sub>dis(SO)</sub>                         | Data output disable time     | Slave                            |                                 | 240                      |                  |  |

| t <sub>v(SO)</sub>                           | Data output valid time       | Slave (after enable edge)        |                                 | 120                      | -                |  |

| t <sub>h(SO)</sub>                           | Data output hold time        | Slave (after enable edge)        | 0                               |                          |                  |  |

| t <sub>v(MO)</sub>                           | Data output valid time       | Master (after enable edge)       |                                 | 120                      | t <sub>CPU</sub> |  |

| t <sub>h(MO)</sub>                           | Data output hold time        |                                  | 0                               |                          |                  |  |

# Figure 89. SPI Slave Timing Diagram with CPHA=0<sup>3)</sup>

#### Notes:

1. Data based on design simulation and/or characterisation results, not tested in production.

2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends on the I/O port configuration.

- 3. Measurement points are done at CMOS levels:  $0.3 x V_{\text{DD}}$  and  $0.7 x V_{\text{DD}}.$

- 4. Depends on f<sub>CPU</sub>. For example, if f<sub>CPU</sub> = 8 MHz, then t<sub>CPU</sub> = 1 / f<sub>CPU</sub> = 125 ns and t<sub>su(SS)</sub> = 175 ns.

## **13.3 SOLDERING INFORMATION**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.