Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

|                            |                                                                       |

| Product Status             | Not For New Designs                                                   |

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1.5K x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    |                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bj7t6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIN DESCRIPTION (Cont'd)

For external pin connection guidelines, refer to See "ELECTRICAL CHARACTERISTICS" on page 138.

## Legend / Abbreviations for Table 2:

Type: I = input, O = output, S = supplyInput level: A = Dedicated analog inputIn/Output level:  $C = CMOS = 3V_{PP}/0.7V_{PP}$

In/Output level:  $C = CMOS~0.3V_{DD}/0.7V_{DD}$   $C_{T} = CMOS~0.3V_{DD}/0.7V_{DD}$  with input trigger  $T_{T} = TTL~0.8V~/~2V$  with Schmitt trigger

Output level: HS = 20mA high sink (on N-buffer only)

Port and control configuration:

Input: float = floating, wpu = weak pull-up, int = interrupt <sup>1)</sup>, ana = analog

- Output: OD = open drain  $^{2)}$ , PP = push-pull

Refer to "I/O PORTS" on page 46 for more details on the software configuration of the I/O ports.

The RESET configuration of each pin is shown in bold. This configuration is valid as long as the device is in reset state.

**Table 2. Device Pin Description**

| F      | Pin n  | 0      |                   |      | Le      | evel   |       |     | P   | ort |     |     | Main               |                          |

|--------|--------|--------|-------------------|------|---------|--------|-------|-----|-----|-----|-----|-----|--------------------|--------------------------|

| P64    | P44    | P32    | Pin Name          | Type | ut      | put    |       | Inp | out |     | Out | put | function<br>(after | Alternate function       |

| LQFP64 | LQFP44 | LQFP32 |                   |      | Input   | Output | float | ndw | int | ana | ОО  | ЬР  | reset)             |                          |

| 1      | -      | -      | PE4 (HS)          | I/O  | $C_{T}$ | HS     | X     | Χ   |     |     | Х   | Х   | Port E4            |                          |

| 2      | -      | -      | PE5 (HS)          | I/O  | $C_{T}$ | HS     | X     | Χ   |     |     | Х   | Х   | Port E5            |                          |

| 3      | -      | -      | PE6 (HS)          | I/O  | $C_{T}$ | HS     | X     | Χ   |     |     | Х   | Х   | Port E6            |                          |

| 4      | -      | -      | PE7 (HS)          | I/O  | $C_{T}$ | HS     | X     | Χ   |     |     | Χ   | Χ   | Port E7            |                          |

| 5      | 2      | 28     | PB0/PWM3          | I/O  | $C_{T}$ |        | X     | е   | i2  |     | Χ   | Χ   | Port B0            | PWM Output 3             |

| 6      | 3      | •      | PB1/PWM2          | I/O  | $C_{T}$ |        | X     | е   | i2  |     | Х   | Χ   | Port B1            | PWM Output 2             |

| 7      | 4      | •      | PB2/PWM1          | I/O  | $C_T$   |        | X     | е   | i2  |     | Χ   | Χ   | Port B2            | PWM Output 1             |

| 8      | 5      | 29     | PB3/PWM0          | I/O  | $C_{T}$ |        | X     |     | ei2 |     | Х   | Χ   | Port B3            | PWM Output 0             |

| 9      | 6      | 30     | PB4 (HS)/ARTCLK   | I/O  | $C_T$   | HS     | X     | е   | i3  |     | Χ   | Χ   | Port B4            | PWM-ART External Clock   |

| 10     | -      |        | PB5 / ARTIC1      | I/O  | $C_{T}$ |        | X     | е   | i3  |     | Х   | Χ   | Port B5            | PWM-ART Input Capture 1  |

| 11     | -      |        | PB6 / ARTIC2      | I/O  | $C_T$   |        | X     | е   | i3  |     | Χ   | Χ   | Port B6            | PWM-ART Input Capture 2  |

| 12     | -      | •      | PB7               | I/O  | $C_T$   |        | X     |     | ei3 |     | Χ   | Χ   | Port B7            |                          |

| 13     | 7      | 31     | PD0/AIN0          | I/O  | $C_T$   |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D0            | ADC Analog Input 0       |

| 14     | 8      | 32     | PD1/AIN1          | I/O  | $C_{T}$ |        | X     | Χ   |     | Χ   | Х   | Χ   | Port D1            | ADC Analog Input 1       |

| 15     | 9      |        | PD2/AIN2          | I/O  | $C_T$   |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D2            | ADC Analog Input 2       |

| 16     | 10     | •      | PD3/AIN3          | I/O  | $C_T$   |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D3            | ADC Analog Input 3       |

| 17     | 11     | -      | PD4/AIN4          | I/O  | $C_T$   |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D4            | ADC Analog Input 4       |

| 18     | 12     | -      | PD5/AIN5          | I/O  | $C_T$   |        | Х     | Χ   |     | Χ   | Χ   | Χ   | Port D5            | ADC Analog Input 5       |

| 19     | -      | -      | PD6/AIN6          | I/O  | $C_{T}$ |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D6            | ADC Analog Input 6       |

| 20     | -      | -      | PD7/AIN7          | I/O  | $C_T$   |        | X     | Χ   |     | Χ   | Χ   | Χ   | Port D7            | ADC Analog Input 7       |

| 21     | 13     | 1      | V <sub>AREF</sub> | I    |         |        |       |     |     |     |     |     | Analog R           | eference Voltage for ADC |

| 22     | 14     | 2      | V <sub>SSA</sub>  | S    |         |        |       |     |     |     |     |     | Analog G           | iround Voltage           |

| Address                                                                                | Block   | Register<br>Label                                                                    | Register Name                                                                                                                                                                                                                                                                                                                                                                                                         | Reset<br>Status                                             | Remarks                                                                        |

|----------------------------------------------------------------------------------------|---------|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------|

| 0058h<br>to<br>006Fh                                                                   |         |                                                                                      | Reserved Area (24 Bytes)                                                                                                                                                                                                                                                                                                                                                                                              |                                                             |                                                                                |

| 0070h<br>0071h<br>0072h                                                                | ADC     | ADCCSR<br>ADCDRH<br>ADCDRL                                                           | Control/Status Register Data High Register Data Low Register                                                                                                                                                                                                                                                                                                                                                          | 00h<br>00h<br>00h                                           | R/W<br>Read Only<br>Read Only                                                  |

| 0073h<br>0074h<br>0075h<br>0076h<br>0077h<br>0078h<br>0079h<br>007Ah<br>007Bh<br>007Ch | PWM ART | PWMDCR3 PWMDCR1 PWMDCR0 PWMCR ARTCSR ARTCAR ARTARR ARTICCSR ARTICCSR ARTICR1 ARTICR2 | PWM AR Timer Duty Cycle Register 3 PWM AR Timer Duty Cycle Register 2 PWM AR Timer Duty Cycle Register 1 PWM AR Timer Duty Cycle Register 0 PWM AR Timer Control Register 0 Auto-Reload Timer Control/Status Register Auto-Reload Timer Counter Access Register Auto-Reload Timer Auto-Reload Register AR Timer Input Capture Control/Status Reg. AR Timer Input Capture Register 1 AR Timer Input Capture Register 1 | 00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h<br>00h | R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>R/W<br>Read Only<br>Read Only |

| 007Eh<br>007Fh                                                                         |         |                                                                                      | Reserved Area (2 Bytes)                                                                                                                                                                                                                                                                                                                                                                                               |                                                             |                                                                                |

**Legend**: x=undefined, R/W=read/write

# Notes:

1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

2. The bits associated with unavailable pins must always keep their reset value.

## 4 FLASH PROGRAM MEMORY

#### 4.1 Introduction

The ST7 dual voltage High Density Flash (HDFlash) is a non-volatile memory that can be electrically erased as a single block or by individual sectors and programmed on a Byte-by-Byte basis using an external V<sub>PP</sub> supply.

The HDFlash devices can be programmed and erased off-board (plugged in a programming tool) or on-board using ICP (In-Circuit Programming) or IAP (In-Application Programming).

The array matrix organisation allows each sector to be erased and reprogrammed without affecting other sectors.

### 4.2 Main Features

- Three Flash programming modes:

- Insertion in a programming tool. In this mode, all sectors including option bytes can be programmed or erased.

- ICP (In-Circuit Programming). In this mode, all sectors including option bytes can be programmed or erased without removing the device from the application board.

- IAP (In-Application Programming) In this mode, all sectors except Sector 0, can be programmed or erased without removing the device from the application board and while the application is running.

- ICT (In-Circuit Testing) for downloading and executing user application test patterns in RAM

- Read-out protection

- Register Access Security System (RASS) to prevent accidental programming or erasing

### 4.3 Structure

The Flash memory is organised in sectors and can be used for both code and data storage.

Depending on the overall Flash memory size in the microcontroller device, there are up to three user sectors (see Table 4). Each of these sectors can be erased independently to avoid unnecessary erasing of the whole Flash memory when only a partial erasing is required.

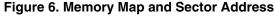

The first two sectors have a fixed size of 4 Kbytes (see Figure 6). They are mapped in the upper part of the ST7 addressing space so the reset and interrupt vectors are located in Sector 0 (F000h-FFFFh).

Table 4. Sectors available in Flash devices

| Flash Size (bytes) | Available Sectors |

|--------------------|-------------------|

| 4K                 | Sector 0          |

| 8K                 | Sectors 0,1       |

| > 8K               | Sectors 0,1, 2    |

#### 4.3.1 Read-out Protection

Read-out protection, when selected, provides a protection against Program Memory content extraction and against write access to Flash memory. Even if no protection can be considered as totally unbreakable, the feature provides a very high level of protection for a general purpose microcontroller.

In flash devices, this protection is removed by reprogramming the option. In this case, the entire program memory is first automatically erased and the device can be reprogrammed.

Read-out protection selection depends on the device type:

- In Flash devices it is enabled and removed through the FMP\_R bit in the option byte.

- In ROM devices it is enabled by mask option specified in the Option List.

## FLASH PROGRAM MEMORY (Cont'd)

### 4.4 ICC Interface

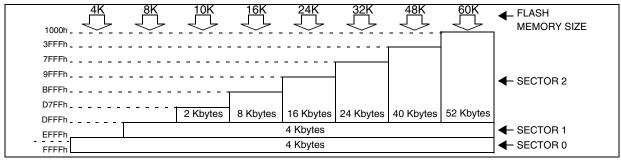

ICC needs a minimum of 4 and up to 6 pins to be connected to the programming tool (see Figure 7). These pins are:

- RESET: device reset

- V<sub>SS</sub>: device power supply ground

- ICCCLK: ICC output serial clock pin

- ICCDATA: ICC input/output serial data pin

- ICCSEL/V<sub>PP</sub>: programming voltage

- OSC1(or OSCIN): main clock input for external source (optional)

- V<sub>DD</sub>: application board power supply (optional, see Figure 7, Note 3)

Figure 7. Typical ICC Interface

### Notes:

- 1. If the ICCCLK or ICCDATA pins are only used as outputs in the application, no signal isolation is necessary. As soon as the Programming Tool is plugged to the board, even if an ICC session is not in progress, the ICCCLK and ICCDATA pins are not available for the application. If they are used as inputs by the application, isolation such as a serial resistor has to implemented in case another device forces the signal. Refer to the Programming Tool documentation for recommended resistor values.

- 2. During the ICC session, the programming tool must control the RESET pin. This can lead to conflicts between the programming tool and the application reset circuit if it drives more than 5mA at high level (push pull output or pull-up resistor<1K). A schottky diode can be used to isolate the application RESET circuit in this case. When using a classical RC network with R>1K or a reset man-

- agement IC with open drain output and pull-up resistor>1K, no additional components are needed. In all cases the user must ensure that no external reset is generated by the application during the ICC session.

- 3. The use of Pin 7 of the ICC connector depends on the Programming Tool architecture. This pin must be connected when using most ST Programming Tools (it is used to monitor the application power supply). Please refer to the Programming Tool manual.

- 4. Pin 9 has to be connected to the OSC1 or OSCIN pin of the ST7 when the clock is not available in the application or if the selected clock option is not programmed in the option byte. ST7 devices with multi-oscillator capability need to have OSC2 grounded in this case.

<u> 577</u>

## **CENTRAL PROCESSING UNIT (Cont'd)**

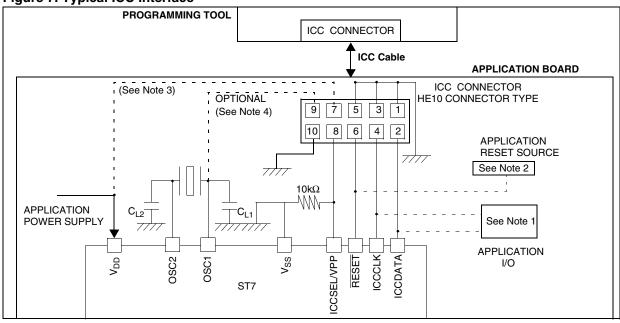

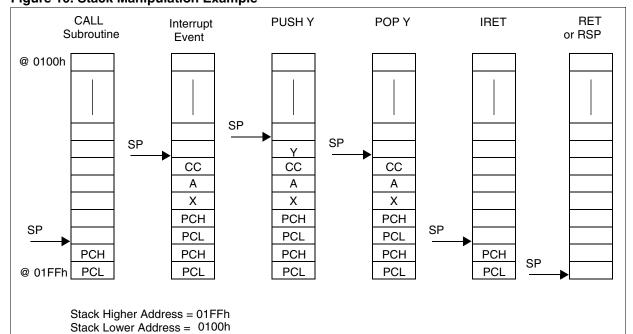

## Stack Pointer (SP)

Read/Write

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

Figure 10. Stack Manipulation Example

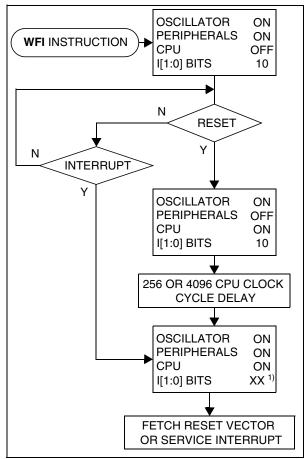

## POWER SAVING MODES (Cont'd)

### 8.3 WAIT MODE

WAIT mode places the MCU in a low power consumption mode by stopping the CPU.

This power saving mode is selected by calling the 'WFI' instruction.

All peripherals remain active. During WAIT mode, the I[1:0] bits of the CC register are forced to '10', to enable all interrupts. All other registers and memory remain unchanged. The MCU remains in WAIT mode until an interrupt or RESET occurs, whereupon the Program Counter branches to the starting address of the interrupt or Reset service routine.

The MCU will remain in WAIT mode until a Reset or an Interrupt occurs, causing it to wake up.

Refer to Figure 26.

Figure 26. WAIT Mode Flow-chart

## Note:

1. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

# MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK (Cont'd)

Bit 0 = **OIF** Oscillator interrupt flag

This bit is set by hardware and cleared by software reading the MCCSR register. It indicates when set that the main oscillator has reached the selected elapsed time (TB1:0).

0: Timeout not reached

1: Timeout reached

**CAUTION**: The BRES and BSET instructions must not be used on the MCCSR register to avoid unintentionally clearing the OIF bit.

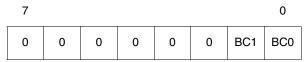

# MCC BEEP CONTROL REGISTER (MCCBCR)

Read/Write

Reset Value: 0000 0000 (00h)

Bit 7:2 = Reserved, must be kept cleared.

Bit 1:0 = **BC[1:0]** Beep control These 2 bits select the PF1 pin beep capability.

| BC1 | BC0 | Beep mode wi | th f <sub>OSC2</sub> =8MHz |

|-----|-----|--------------|----------------------------|

| 0   | 0   | C            | Off                        |

| 0   | 1   | ~2-KHz       | Output                     |

| 1   | 0   | ~1-KHz       | Beep signal                |

| 1   | 1   | ~500-Hz      | ~50% duty cycle            |

The beep output signal is available in ACTIVE-HALT mode but has to be disabled to reduce the consumption.

Table 15. Main Clock Controller Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6     | 5    | 4     | 3   | 2   | 1   | 0     |

|-------------------|-------------------|------|-------|------|-------|-----|-----|-----|-------|

| 002Bh             | SICSR             | AVDS | AVDIE | AVDF | LVDRF |     |     |     | WDGRF |

| 002611            | Reset Value       | 0    | 0     | 0    | х     | 0   | 0   | 0   | х     |

| 002Ch             | MCCSR             | MCO  | CP1   | CP0  | SMS   | TB1 | TB0 | OIE | OIF   |

| 002011            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

| 002Dh             | MCCBCR            |      |       |      |       |     |     | BC1 | BC0   |

| 002011            | Reset Value       | 0    | 0     | 0    | 0     | 0   | 0   | 0   | 0     |

# **ON-CHIP PERIPHERALS** (Cont'd)

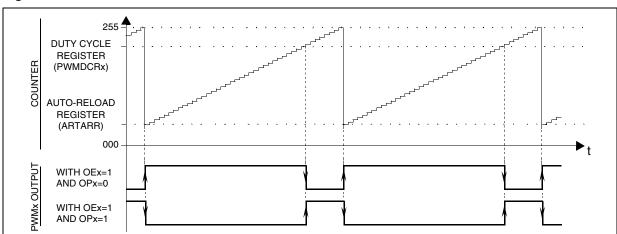

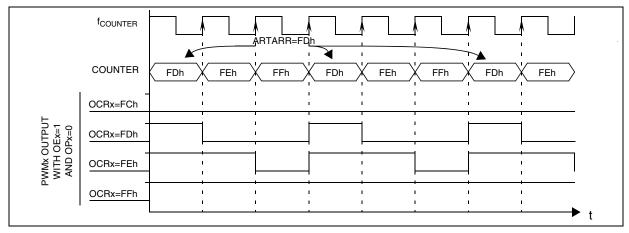

### **Independent PWM signal generation**

This mode allows up to four Pulse Width Modulated signals to be generated on the PWMx output pins with minimum core processing overhead. This function is stopped during HALT mode.

Each PWMx output signal can be selected independently using the corresponding OEx bit in the PWM Control register (PWMCR). When this bit is set, the corresponding I/O pin is configured as output push-pull alternate function.

The PWM signals all have the same frequency which is controlled by the counter period and the ARTARR register value.

$$f_{PWM} = f_{COUNTER} / (256 - ARTARR)$$

When a counter overflow occurs, the PWMx pin level is changed depending on the corresponding OPx (output polarity) bit in the PWMCR register.

When the counter reaches the value contained in one of the output compare register (OCRx) the corresponding PWMx pin level is restored.

It should be noted that the reload values will also affect the value and the resolution of the duty cycle of the PWM output signal. To obtain a signal on a PWMx pin, the contents of the OCRx register must be greater than the contents of the ARTARR register

The maximum available resolution for the PWMx duty cycle is:

**Note**: To get the maximum resolution (1/256), the ARTARR register must be 0. With this maximum resolution, 0% and 100% can be obtained by changing the polarity.

Figure 39. PWM Auto-reload Timer Function

Figure 40. PWM Signal from 0% to 100% Duty Cycle

# **ON-CHIP PERIPHERALS** (Cont'd)

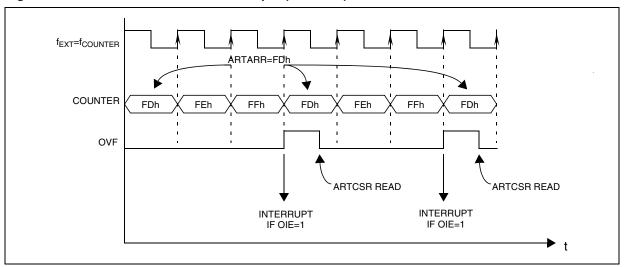

## Output compare and Time base interrupt

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

### External clock and event detector mode

Using the  $f_{\text{EXT}}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{\text{EVENT}}$  number of events to be counted before setting the OVF flag.

$$n_{EVENT} = 256 - ARTARR$$

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

Figure 41. External Event Detector Example (3 counts)

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

# PWM AUTO-RELOAD TIMER (Cont'd)

Table 16. PWM Auto-Reload Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label       | 7    | 6   | 5        | 4        | 3         | 2         | 1        | 0        |

|-------------------|-------------------------|------|-----|----------|----------|-----------|-----------|----------|----------|

| 0073h             | PWMDCR3                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0074h             | PWMDCR2                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0075h             | PWMDCR1                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0076h             | PWMDCR0                 | DC7  | DC6 | DC5      | DC4      | DC3       | DC2       | DC1      | DC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0077h             | PWMCR                   | OE3  | OE2 | OE1      | OE0      | OP3       | OP2       | OP1      | OP0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0078h             | ARTCSR                  | EXCL | CC2 | CC1      | CC0      | TCE       | FCRL      | RIE      | OVF      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 0079h             | ARTCAR                  | CA7  | CA6 | CA5      | CA4      | CA3       | CA2       | CA1      | CA0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Ah             | ARTARR                  | AR7  | AR6 | AR5      | AR4      | AR3       | AR2       | AR1      | AR0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Bh             | ARTICCSR<br>Reset Value | 0    | 0   | CS2<br>0 | CS1<br>0 | CIE2<br>0 | CIE1<br>0 | CF2<br>0 | CF1<br>0 |

| 007Ch             | ARTICR1                 | IC7  | IC6 | IC5      | IC4      | IC3       | IC2       | IC1      | IC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

| 007Dh             | ARTICR2                 | IC7  | IC6 | IC5      | IC4      | IC3       | IC2       | IC1      | IC0      |

|                   | Reset Value             | 0    | 0   | 0        | 0        | 0         | 0         | 0        | 0        |

### **16-BIT TIMER** (Cont'd)

**16-bit read sequence:** (from either the Counter Register or the Alternate Counter Register).

Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

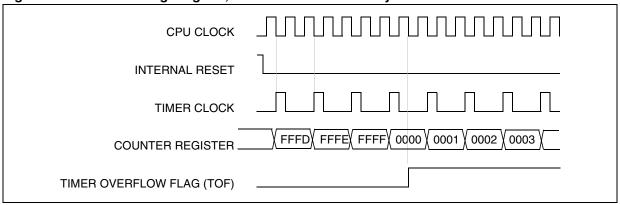

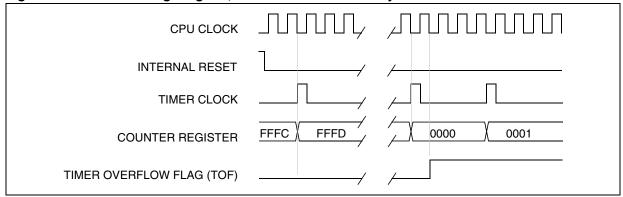

Whatever the timer mode used (input capture, output compare, One Pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true.

Clearing the overflow interrupt request is done in two steps:

- 1. Reading the SR register while the TOF bit is set.

- 2. An access (read or write) to the CLR register.

**Notes:** The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

## 10.4.3.2 External Clock

The external clock (where available) is selected if CC0 = 1 and CC1 = 1 in the CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronized with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

# 16-BIT TIMER (Cont'd)

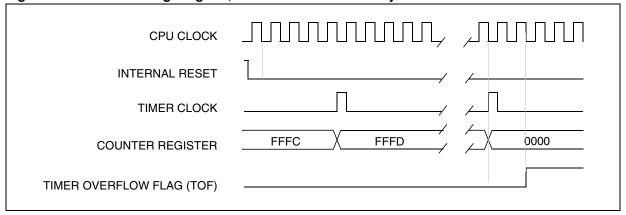

Figure 44. Counter Timing Diagram, Internal Clock Divided by 2

Figure 45. Counter Timing Diagram, Internal Clock Divided by 4

Figure 46. Counter Timing Diagram, Internal Clock Divided By 8

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

# 16-BIT TIMER (Cont'd)

Table 18. 16-Bit Timer Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4     | 3     | 2     | 1     | 0     |

|-------------------|-------------------|------|------|------|-------|-------|-------|-------|-------|

| Timer A: 32       | CR1               | ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

| Timer B: 42       | Reset Value       | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 31       | CR2               | OC1E | OC2E | OPM  | PWM   | CC1   | CC0   | IEDG2 | EXEDG |

| Timer B: 41       | Reset Value       | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 33       | CSR               | ICF1 | OCF1 | TOF  | ICF2  | OCF2  | TIMD  | -     | -     |

| Timer B: 43       | Reset Value       | Х    | Х    | Х    | Х     | Х     | 0     | Х     | x     |

| Timer A: 34       | IC1HR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 44       | Reset Value       | Х    | Х    | Х    | Х     | Х     | Х     | Х     | х     |

| Timer A: 35       | IC1LR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 45       | Reset Value       | Х    | Х    | Х    | Х     | Х     | Х     | Х     | х     |

| Timer A: 36       | OC1HR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 46       | Reset Value       | 1    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 37       | OC1LR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 47       | Reset Value       | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 3E       | OC2HR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4E       | Reset Value       | 1    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 3F       | OC2LR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4F       | Reset Value       | 0    | 0    | 0    | 0     | 0     | 0     | 0     | 0     |

| Timer A: 38       | CHR               | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 48       | Reset Value       | 1    | 1    | 1    | 1     | 1     | 1     | 1     | 1     |

| Timer A: 39       | CLR               | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 49       | Reset Value       | 1    | 1    | 1    | 1     | 1     | 1     | 0     | 0     |

| Timer A: 3A       | ACHR              | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4A       | Reset Value       | 1    | 1    | 1    | 1     | 1     | 1     | 1     | 1     |

| Timer A: 3B       | ACLR              | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4B       | Reset Value       | 1    | 1    | 1    | 1     | 1     | 1     | 0     | 0     |

| Timer A: 3C       | IC2HR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4C       | Reset Value       | Х    | Х    | Х    | х     | х     | х     | Х     | х     |

| Timer A: 3D       | IC2LR             | MSB  |      |      |       |       |       |       | LSB   |

| Timer B: 4D       | Reset Value       | Х    | Х    | Х    | Х     | Х     | Х     | Х     | Х     |

# **Related Documentation**

AN 973: SCI software communications using 16-bit timer

AN 974: Real Time Clock with ST7 Timer Output Compare

AN 976: Driving a buzzer through the ST7 Timer PWM function

AN1041: Using ST7 PWM signal to generate analog input (sinusoid)

AN1046: UART emulation software

AN1078: PWM duty cycle switch implementing

true 0 or 100 per cent duty cycle

AN1504: Starting a PWM signal directly at high

level using the ST7 16-Bit timer

<u> 577</u>

# SERIAL PERIPHERAL INTERFACE (Cont'd)

- SS: Slave select:

This input signal acts as a 'chip select' to let the SPI master communicate with slaves individually and to avoid contention on the data lines. Slave SS inputs can be driven by standard I/O ports on the master MCU.

## 10.5.3.1 Functional Description

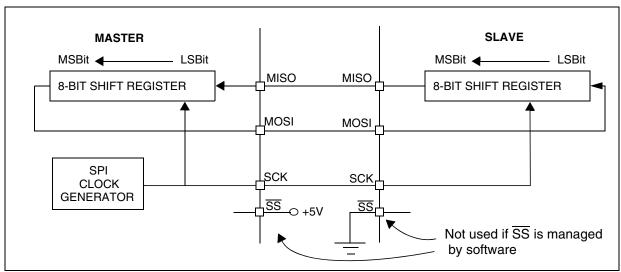

A basic example of interconnections between a single master and a single slave is illustrated in Figure 55.

The MOSI pins are connected together and the MISO pins are connected together. In this way data is transferred serially between master and slave (most significant bit first).

The communication is always initiated by the master. When the master device transmits data to a slave device via MOSI pin, the slave device responds by sending data to the master device via the MISO pin. This implies full duplex communication with both data out and data in synchronized with the same clock signal (which is provided by the master device via the SCK pin).

To use a single data line, the MISO and MOSI pins must be connected at each node (in this case only simplex communication is possible).

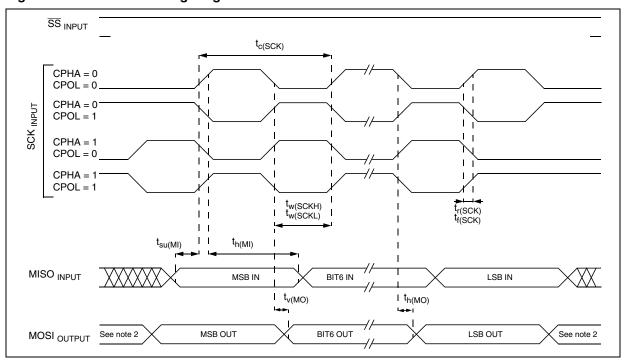

Four possible data/clock timing relationships may be chosen (see Figure 58) but master and slave must be programmed with the same timing mode.

Figure 55. Single Master/ Single Slave Application

## SERIAL PERIPHERAL INTERFACE (Cont'd)

### 10.5.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

To operate the SPI in master mode, perform the following steps in order (if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account):

- Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 58 shows the four possible configurations.

Note: The slave must have the same CPOL and CPHA settings as the master.

- 2. Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- 3. Write to the SPICR register:

- Set the MSTR and SPE bits

Note: MSTR and SPE bits remain set only if SS is high).

The transmit sequence begins when software writes a byte in the SPIDR register.

### 10.5.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register.

**Note:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

### 10.5.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see Figure 58).

- **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Manage the SS pin as described in Section 10.5.3.2 and Figure 56. If CPHA=1 SS must be held low continuously. If CPHA=0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

### 10.5.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared

Clearing the SPIF bit is performed by the following software sequence:

- An access to the SPICSR register while the SPIF bit is set.

- 2. A write or a read to the SPIDR register.

**Notes:** While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.5.5.2).

# ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

# SERIAL COMMUNICATION INTERFACE (Cont'd)

**Table 23. SCI Register Map and Reset Values**

| Address<br>(Hex.) | Register<br>Label | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------------------|-------------------|------|------|------|------|------|------|------|------|

| 0050h             | SCISR             | TDRE | TC   | RDRF | IDLE | OVR  | NF   | FE   | PE   |

| 005011            | Reset Value       | 1    | 1    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0051h             | SCIDR             | MSB  |      |      |      |      |      |      | LSB  |

| 003111            | Reset Value       | Х    | Х    | х    | Х    | х    | Х    | х    | х    |

| 0052h             | SCIBRR            | SCP1 | SCP0 | SCT2 | SCT1 | SCT0 | SCR2 | SCR1 | SCR0 |

| 003211            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0053h             | SCICR1            | R8   | T8   | SCID | М    | WAKE | PCE  | PS   | PIE  |

| 005311            | Reset Value       | Х    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0054h             | SCICR2            | TIE  | TCIE | RIE  | ILIE | TE   | RE   | RWU  | SBK  |

| 005411            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0055h             | SCIERPR           | MSB  |      |      |      |      |      |      | LSB  |

| 000011            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| 0057h             | SCIPETPR          | MSB  |      |      |      |      |      |      | LSB  |

| 005711            | Reset Value       | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

# INSTRUCTION SET OVERVIEW (Cont'd)

| Mnemo | Description            | Function/Example    | Dst     | Src     | I1 | Н | 10 | N | Z | С |

|-------|------------------------|---------------------|---------|---------|----|---|----|---|---|---|

| JRULE | Jump if $(C + Z = 1)$  | Unsigned <=         |         |         |    |   |    |   |   |   |

| LD    | Load                   | dst <= src          | reg, M  | M, reg  |    |   |    | N | Z |   |

| MUL   | Multiply               | X,A = X * A         | A, X, Y | X, Y, A |    | 0 |    |   |   | 0 |

| NEG   | Negate (2's compl)     | neg \$10            | reg, M  |         |    |   |    | N | Z | С |

| NOP   | No Operation           |                     |         |         |    |   |    |   |   |   |

| OR    | OR operation           | A = A + M           | Α       | М       |    |   |    | N | Z |   |

| POP   | Pop from the Stack     | pop reg             | reg     | М       |    |   |    |   |   |   |

| FOF   | Pop Irom the Stack     | pop CC              | CC      | М       | I1 | Н | 10 | N | Z | С |

| PUSH  | Push onto the Stack    | push Y              | М       | reg, CC |    |   |    |   |   |   |

| RCF   | Reset carry flag       | C = 0               |         |         |    |   |    |   |   | 0 |

| RET   | Subroutine Return      |                     |         |         |    |   |    |   |   |   |

| RIM   | Enable Interrupts      | I1:0 = 10 (level 0) |         |         | 1  |   | 0  |   |   |   |

| RLC   | Rotate left true C     | C <= A <= C         | reg, M  |         |    |   |    | Ν | Z | С |

| RRC   | Rotate right true C    | C => A => C         | reg, M  |         |    |   |    | N | Z | С |

| RSP   | Reset Stack Pointer    | S = Max allowed     |         |         |    |   |    |   |   |   |

| SBC   | Substract with Carry   | A = A - M - C       | Α       | М       |    |   |    | N | Z | С |

| SCF   | Set carry flag         | C = 1               |         |         |    |   |    |   |   | 1 |

| SIM   | Disable Interrupts     | I1:0 = 11 (level 3) |         |         | 1  |   | 1  |   |   |   |

| SLA   | Shift left Arithmetic  | C <= A <= 0         | reg, M  |         |    |   |    | Ν | Z | С |

| SLL   | Shift left Logic       | C <= A <= 0         | reg, M  |         |    |   |    | N | Z | O |

| SRL   | Shift right Logic      | 0 => A => C         | reg, M  |         |    |   |    | 0 | Z | С |

| SRA   | Shift right Arithmetic | A7 => A => C        | reg, M  |         |    |   |    | N | Z | С |

| SUB   | Substraction           | A = A - M           | Α       | М       |    |   |    | N | Z | O |

| SWAP  | SWAP nibbles           | A7-A4 <=> A3-A0     | reg, M  |         |    |   |    | N | Z |   |

| TNZ   | Test for Neg & Zero    | tnz lbl1            |         |         |    |   |    | N | Z |   |

| TRAP  | S/W trap               | S/W interrupt       |         |         | 1  |   | 1  |   |   |   |

| WFI   | Wait for Interrupt     |                     |         |         | 1  |   | 0  |   |   |   |

| XOR   | Exclusive OR           | A = A XOR M         | Α       | М       |    |   |    | N | Z |   |

# **COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)**

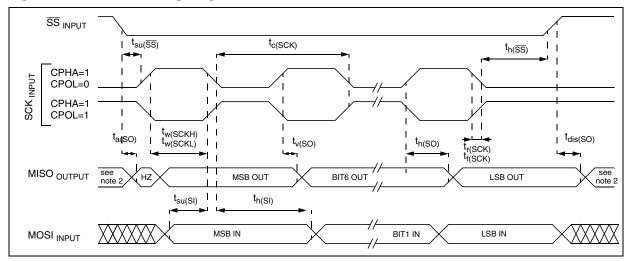

Figure 90. SPI Slave Timing Diagram with CPHA=11)

Figure 91. SPI Master Timing Diagram 1)

### Notes:

- 1. Measurement points are done at CMOS levels:  $0.3 \mathrm{xV}_{\mathrm{DD}}$  and  $0.7 \mathrm{xV}_{\mathrm{DD}}$ .

- 2. When no communication is on-going the data output line of the SPI (MOSI in master mode, MISO in slave mode) has its alternate function capability released. In this case, the pin status depends of the I/O port configuration.

## 14 ST72321B DEVICE CONFIGURATION AND ORDERING INFORMATION

Each device is available for production in user programmable versions (FLASH) as well as in factory coded versions (ROM/FASTROM).

ST72321B devices are ROM versions. ST72P321B devices are Factory Advanced Service Technique ROM (FASTROM) versions: they factory-programmed HDFlash devices.

FLASH devices are shipped to customers with a default content, while ROM/FASTROM factory coded parts contain the code supplied by the customer. This implies that FLASH devices have to be configured by the customer using the Option Bytes while the ROM/FASTROM devices are factoryconfigured.

## 14.1 FLASH OPTION BYTES

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | STATI | С ОРТ | ION B | YTE 0 |    |     | STATIC OPTION BYTE |      |    |       |    |     |   |     |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-------|-------|-------|-------|----|-----|--------------------|------|----|-------|----|-----|---|-----|

|         | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |       |       |       |       |    | 0   | <b>1</b> 7         |      |    |       |    |     |   | 0   |

|         | WDG Sserved Sserved Swerved Sw |    |       |       |       |       | G1 | тс  | osc                | TYPE | 05 | SCRAN | GE | OFF |   |     |

|         | HALT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SW | Resel | 1     | 0     | Resei | Ā  | FMP | PKG                | RS   | 1  | 0     | 2  | 1   | 0 | PLL |

| Default | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1  | 1     | 0     | 0     | 1     | 1  | 1   | 1                  | 1    | 1  | 0     | 1  | 1   | 1 | 1   |

The option bytes allow the hardware configuration of the microcontroller to be selected. They have no address in the memory map and can be accessed only in programming mode (for example using a standard ST7 programming tool). The default content of the FLASH is fixed to FFh. To program the FLASH devices directly using ICP, FLASH devices are shipped to customers with the internal RC clock source enabled. In masked ROM devices, the option bytes are fixed in hardware by the ROM code (see option list).

### **OPTION BYTE 0**

OPT7= WDG HALT Watchdog and HALT mode This option bit determines if a RESET is generated when entering HALT mode while the Watchdog is active.

- 0: No Reset generation when entering Halt mode

- 1: Reset generation when entering Halt mode

OPT6= WDG SW Hardware or software watchdog This option bit selects the watchdog type.

- 0: Hardware (watchdog always enabled)

- 1: Software (watchdog to be enabled by software)

OPT5 = Reserved, must be kept at default value.

OPT4:3= VD[1:0] Voltage detection These option bits enable the voltage detection

block (LVD, and AVD) with a selected threshold for the LVD and AVD (EVD+AVD).

| Selected Low Voltage Detector           | VD1 | VD0 |

|-----------------------------------------|-----|-----|

| LVD and AVD Off                         | 1   | 1   |

| Lowest Threshold: (V <sub>DD</sub> ~3V) | 1   | 0   |

| Med. Threshold (V <sub>DD</sub> ~3.5V)  | 0   | 1   |

| Highest Threshold (V <sub>DD</sub> ~4V) | 0   | 0   |

Caution: If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed. For details on the AVD and LVD threshold levels refer to section 12.3.2 on page 141

OPT2 = Reserved, must be kept at default value.

OPT1= PKG0 Package selection bit 0 This option bit is not used.

**Table 31. ST7 Application Notes**

| IDENTIFICATION      | DESCRIPTION                                                                     |

|---------------------|---------------------------------------------------------------------------------|

| AN1071              | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER          |

| AN1106              | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                      |

| AN1179              | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PROGRAMMING) |

| AN1446              | USING THE ST72521 EMULATOR TO DEBUG AN ST72324 TARGET APPLICATION               |

| AN1477              | EMULATED DATA EEPROM WITH XFLASH MEMORY                                         |

| AN1527              | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                   |

| AN1575              | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                    |

| AN1576              | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS         |

| AN1577              | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS           |

| AN1601              | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                        |

| AN1603              | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)              |

| AN1635              | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                       |

| AN1754              | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                       |

| AN1796              | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT             |

| AN1900              | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                        |

| AN1904              | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                   |

| AN1905              | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                           |

| SYSTEM OPTIMIZATION |                                                                                 |

| AN1711              | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                             |

| AN1827              | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                            |

| AN2009              | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                   |

| AN2030              | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                  |