Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | 60KB (60K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 44-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321bj9t3 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 6.2 MULTI-OSCILLATOR (MO)

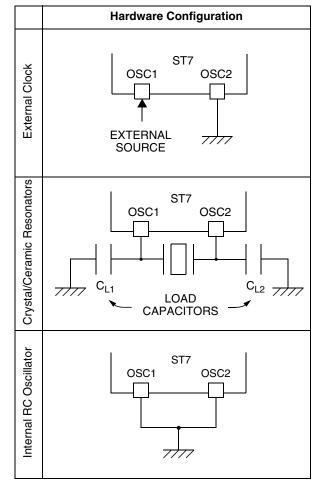

The main clock of the ST7 can be generated by three different source types coming from the multioscillator block:

- an external source

- 4 crystal or ceramic resonator oscillators

- an internal high frequency RC oscillator

Each oscillator is optimized for a given frequency range in terms of consumption and is selectable through the option byte. The associated hardware configurations are shown in Table 5. Refer to the electrical characteristics section for more details.

**Caution:** The OSC1 and/or OSC2 pins must not be left unconnected. For the purposes of Failure Mode and Effect Analysis, it should be noted that if the OSC1 and/or OSC2 pins are left unconnected, the ST7 main oscillator may start and, in this configuration, could generate an  $f_{OSC}$  clock frequency in excess of the allowed maximum (>16MHz.), putting the ST7 in an unsafe/undefined state. The product behaviour must therefore be considered undefined when the OSC pins are left unconnected.

#### **External Clock Source**

In this external clock mode, a clock signal (square, sinus or triangle) with ~50% duty cycle has to drive the OSC1 pin while the OSC2 pin is tied to ground.

#### **Crystal/Ceramic Oscillators**

This family of oscillators has the advantage of producing a very accurate rate on the main clock of the ST7. The selection within a list of 4 oscillators with different frequency ranges has to be done by option byte in order to reduce consumption (refer to section 14.1 on page 174 for more details on the frequency ranges). In this mode of the multi-oscillator, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. The loading capacitance values must be adjusted according to the selected oscillator.

These oscillators are not stopped during the RESET phase to avoid losing time in the oscillator start-up phase.

#### Internal RC Oscillator

This oscillator allows a low cost solution for the main clock of the ST7 using only an internal resistor and capacitor. Internal RC oscillator mode has the drawback of a lower frequency accuracy and should not be used in applications that require accurate timing.

In this mode, the two oscillator pins have to be tied to ground.

#### Table 5. ST7 Clock Sources

#### 6.3 RESET SEQUENCE MANAGER (RSM)

#### 6.3.1 Introduction

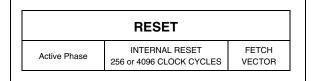

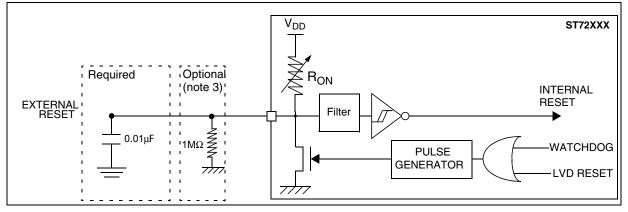

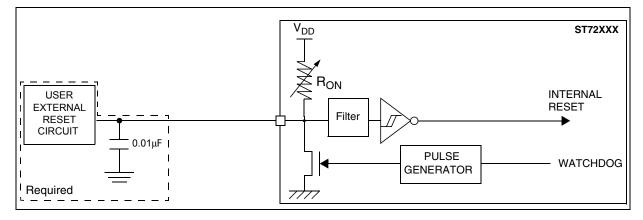

The reset sequence manager includes three RE-SET sources as shown in Figure 14:

- External RESET source pulse

- Internal LVD RESET (Low Voltage Detection)

- Internal WATCHDOG RESET

These sources act on the RESET pin and it is always kept low during the delay phase.

The RESET service routine vector is fixed at addresses FFFEh-FFFFh in the ST7 memory map.

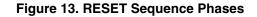

The basic RESET sequence consists of 3 phases as shown in Figure 13:

- Active Phase depending on the RESET source

- 256 or 4096 CPU clock cycle delay (selected by option byte)

- RESET vector fetch

The 256 or 4096 CPU clock cycle delay allows the oscillator to stabilise and ensures that recovery has taken place from the Reset state. The shorter or longer clock cycle delay should be selected by option byte to correspond to the stabilization time of the external oscillator used in the application (see section 14.1 on page 174).

The RESET vector fetch phase duration is 2 clock cycles.

**Caution:** When the ST7 is unprogrammed or fully erased, the Flash is blank and the RESET vector is not programmed.

For this reason, it is recommended to keep the RESET pin in low state until programming mode is entered, in order to avoid unwanted behavior.

#### 6.3.2 Asynchronous External RESET pin

The  $\overrightarrow{\text{RESET}}$  pin is both an input and an open-drain output with integrated  $\overrightarrow{\text{R}}_{ON}$  weak pull-up resistor. This pull-up has no fixed value but varies in accordance with the input voltage. It can be pulled low by external circuitry to reset the device. See "CONTROL PIN CHARACTERISTICS" on page 158 for more details.

A RESET signal originating from an external source must have a duration of at least  $t_{h(RSTL)in}$  in order to be recognized (see Figure 15). This detection is asynchronous and therefore the MCU can enter reset state even in HALT mode.

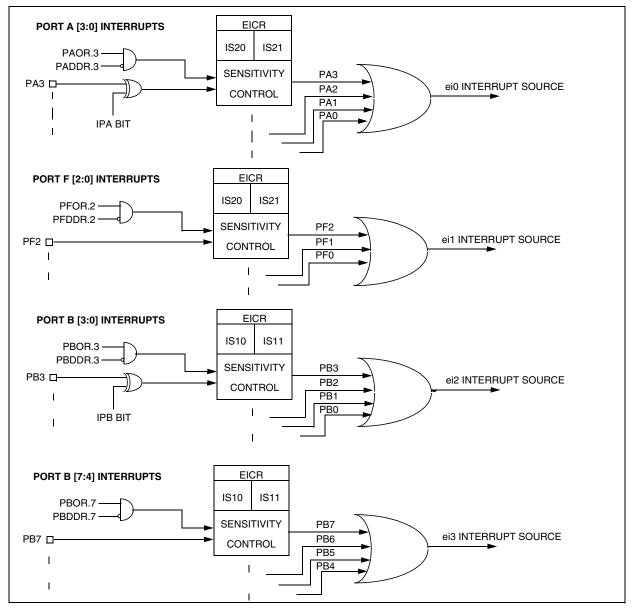

#### INTERRUPTS (Cont'd)

#### Figure 23. External Interrupt Control bits

<u>ل</u>حک

#### POWER SAVING MODES (Cont'd)

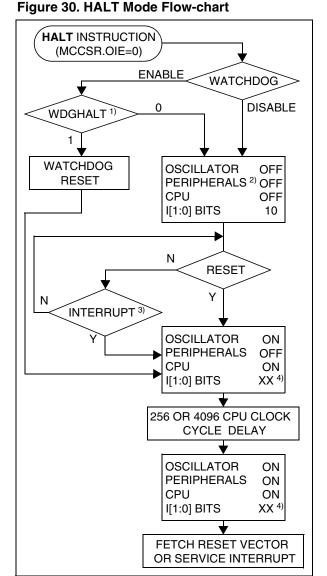

#### 8.4.2 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see section 10.2 on page 57 for more details on the MCCSR register).

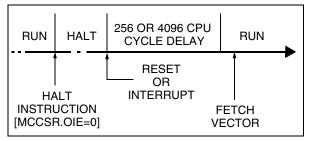

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 8, "Interrupt Mapping," on page 37) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 30).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b'to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see section 14.1 on page 174 for more details).

| Figure 2 | 9. HALT | Timing | Overview |

|----------|---------|--------|----------|

|----------|---------|--------|----------|

#### Notes:

1. WDGHALT is an option bit. See option byte section for more details.

2. Peripheral clocked with an external clock source can still be active.

3. Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 37 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

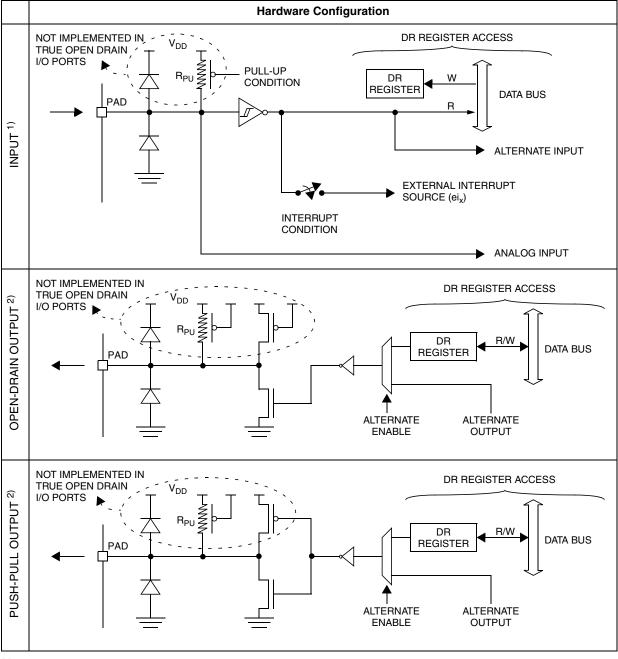

#### I/O PORTS (Cont'd)

#### Table 11. I/O Port Configurations

#### Notes:

- 1. When the I/O port is in input configuration and the associated alternate function is enabled as an output, reading the DR register will read the alternate function output status.

- When the I/O port is in output configuration and the associated alternate function is enabled as an input, the alternate function reads the pin status given by the DR register content.

#### I/O PORTS (Cont'd)

#### 9.5.1 I/O Port Implementation

The I/O port register configurations are summarised as follows.

#### **Standard Ports**

PA5:4, PC7:0, PD7:0, PE7:3, PE1:0, PF7:3,

| MODE              | DDR | OR |

|-------------------|-----|----|

| floating input    | 0   | 0  |

| pull-up input     | 0   | 1  |

| open drain output | 1   | 0  |

| push-pull output  | 1   | 1  |

#### Interrupt Ports

PA2:0, PB6:5, PB4, PB2:0, PF1:0 (with pull-up)

| MODE                    | DDR | OR |

|-------------------------|-----|----|

| floating input          | 0   | 0  |

| pull-up interrupt input | 0   | 1  |

| open drain output       | 1   | 0  |

| push-pull output        | 1   | 1  |

| MODE                     | DDR | OR |

|--------------------------|-----|----|

| floating input           | 0   | 0  |

| floating interrupt input | 0   | 1  |

| open drain output        | 1   | 0  |

| push-pull output         | 1   | 1  |

# True Open Drain Ports PA7:6

| MODE                         | DDR |

|------------------------------|-----|

| floating input               | 0   |

| open drain (high sink ports) | 1   |

#### Pull-Up Input Port PE2

| MODE               | DDR | OR |

|--------------------|-----|----|

| pull-up input      | 0   | х  |

| open drain output* | 1   | 0  |

| push-pull output*  | 1   | 1  |

**/**

#### Table 12. Port Configuration

| Port   | Pin name             | lı                 | nput               | Out         | tput       |

|--------|----------------------|--------------------|--------------------|-------------|------------|

| Port   | Fin name             | OR = 0             | OR = 1             | OR = 0      | OR = 1     |

|        | PA7:6                | flo                | pating             | true ope    | en-drain   |

| Port A | PA5:4                | floating           | pull-up            | open drain  | push-pull  |

| FOILA  | PA3                  | floating           | floating interrupt | open drain  | push-pull  |

|        | PA2:0                | floating           | pull-up interrupt  | open drain  | push-pull  |

|        | PB7, PB3             | floating           | floating interrupt | open drain  | push-pull  |

| Port B | PB6:5, PB4,<br>PB2:0 | floating           | pull-up interrupt  | open drain  | push-pull  |

| Port C | PC7:0                | floating           | pull-up            | open drain  | push-pull  |

| Port D | PD7:0                | floating           | pull-up            | open drain  | push-pull  |

| Port E | PE7:3, PE1:0         | floating           | pull-up            | open drain  | push-pull  |

| FOILE  | PE2                  | pull-up input only |                    | open drain* | push-pull* |

|        | PF7:3                | floating           | pull-up            | open drain  | push-pull  |

| Port F | PF2                  | floating           | floating interrupt | open drain  | push-pull  |

|        | PF1:0                | floating           | pull-up interrupt  | open drain  | push-pull  |

\*Pull-up always activated on PE2.

## ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | Т0 |

| UUZAII            | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## Table 14. Watchdog Timer Register Map and Reset Values

#### **ON-CHIP PERIPHERALS** (Cont'd)

#### **PWM CONTROL REGISTER (PWMCR)**

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| OE3 | OE2 | OE1 | OE0 | OP3 | OP2 | OP1 | OP0 |

Bit 7:4 = **OE[3:0]** *PWM Output Enable*

These bits are set and cleared by software. They enable or disable the PWM output channels independently acting on the corresponding I/O pin. 0: PWM output disabled.

1: PWM output enabled.

#### Bit 3:0 = OP[3:0] PWM Output Polarity

These bits are set and cleared by software. They independently select the polarity of the four PWM output signals.

| PWMx ou         | itput level | OPx |

|-----------------|-------------|-----|

| Counter <= OCRx | UFX         |     |

| 1               | 0           | 0   |

| 0               | 1           | 1   |

**Note**: When an OPx bit is modified, the PWMx output signal polarity is immediately reversed.

#### DUTY CYCLE REGISTERS (PWMDCRx)

Read/Write

Reset Value: 0000 0000 (00h)

| 7   |     |     |     |     |     |     | 0   |

|-----|-----|-----|-----|-----|-----|-----|-----|

| DC7 | DC6 | DC5 | DC4 | DC3 | DC2 | DC1 | DC0 |

#### Bit 7:0 = DC[7:0] Duty Cycle Data

These bits are set and cleared by software.

A PWMDCRx register is associated with the OCRx register of each PWM channel to determine the second edge location of the PWM signal (the first edge location is common to all channels and given by the ARTARR register). These PWMDCR registers allow the duty cycle to be set independently for each PWM channel.

## 16-BIT TIMER (Cont'd) **INPUT CAPTURE 1 HIGH REGISTER (IC1HR)**

Read Only

**Reset Value: Undefined**

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

7

<u>ل</u>رک

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **OUTPUT COMPARE 1 HIGH REGISTER** (OC1HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

-

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 1   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

85/187

^

#### SERIAL PERIPHERAL INTERFACE (Cont'd)

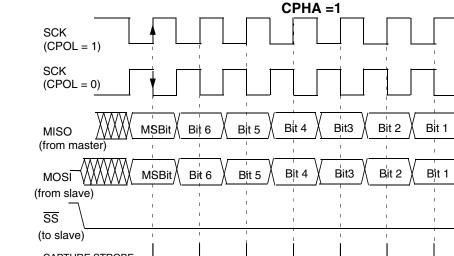

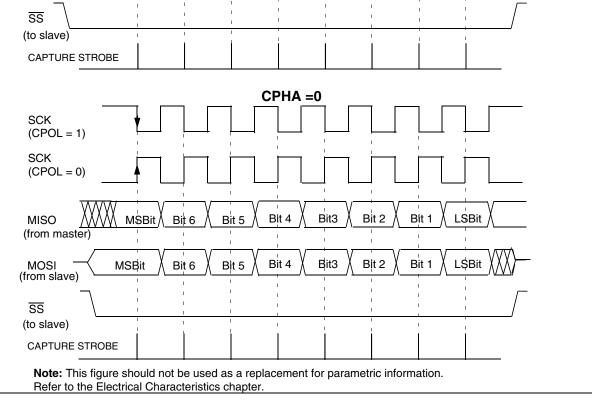

#### 10.5.4 Clock Phase and Clock Polarity

Four possible timing relationships may be chosen by software, using the CPOL and CPHA bits (See Figure 58).

**Note:** The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

The combination of the CPOL clock polarity and CPHA (clock phase) bits selects the data capture clock edge

Figure 58, shows an SPI transfer with the four combinations of the CPHA and CPOL bits. The diagram may be interpreted as a master or slave timing diagram where the SCK pin, the MISO pin, the MOSI pin are directly connected between the master and the slave device.

**Note**: If CPOL is changed at the communication byte boundaries, the SPI must be disabled by resetting the SPE bit.

LSBit

L\$Bit

**/۲**۸

#### Figure 58. Data Clock Timing Diagram

#### SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### **10.6.4 Functional Description**

The block diagram of the Serial Control Interface, is shown in Figure 1. It contains six dedicated registers:

- Two control registers (SCICR1 & SCICR2)

- A status register (SCISR)

**/رک**

- A baud rate register (SCIBRR)

- An extended prescaler receiver register (SCIER-PR)

- An extended prescaler transmitter register (SCI-ETPR)

Refer to the register descriptions in Section 0.1.7 for the definitions of each bit.

#### 10.6.4.1 Serial Data Format

Word length may be selected as being either 8 or 9 bits by programming the M bit in the SCICR1 register (see Figure 1.).

The TDO pin is in low state during the start bit.

The TDO pin is in high state during the stop bit.

An Idle character is interpreted as an entire frame of "1"s followed by the start bit of the next frame which contains data.

A Break character is interpreted on receiving "0"s for some multiple of the frame period. At the end of the last break frame the transmitter inserts an extra "1" bit to acknowledge the start bit.

Transmission and reception are driven by their own baud rate generator.

# Figure 62. Word Length Programming

|   | 9-bit Word length (M bit is set) Data Frame                    |      |       |         |       |       |       |                 | Possible<br>Parity<br>Bit |                 |             | Next Data Frame<br>Next |  |

|---|----------------------------------------------------------------|------|-------|---------|-------|-------|-------|-----------------|---------------------------|-----------------|-------------|-------------------------|--|

|   | Start<br>Bit                                                   | Bit0 | Bit1  | Bit2    | Bit3  | Bit4  | Bit5  | Bit6            | Bit7                      | Bit8            | Stop<br>Bit | Start<br>Bit            |  |

|   | Idle Frame                                                     |      |       |         |       |       |       |                 | Start<br>Bit              |                 |             |                         |  |

|   |                                                                |      | E     | Break F | rame  |       |       |                 |                           |                 |             | Extra Start<br>'1' Bit  |  |

|   | <b>8-bit Word length (M bit is reset)</b><br>Data Frame<br>Bit |      |       |         |       |       | Ne    | Next Data Frame |                           |                 |             |                         |  |

|   | Start<br>Bit                                                   | Bit  | ) Bit | 1 Bitź  | 2 Bit | 3 Bit | 4 Bit | 5 Bit           | 6 Bit                     | t7 Sto<br>Bit   |             | t                       |  |

| _ | Idle Frame                                                     |      |       |         |       |       |       | Sta<br>Bi       | art                       |                 |             |                         |  |

|   | Break Frame                                                    |      |       |         |       |       |       |                 | Ext                       | ra Start<br>Bit |             |                         |  |

|   |                                                                |      |       |         |       |       |       |                 |                           |                 | <u> </u>    |                         |  |

# I<sup>2</sup>C INTERFACE (Cont'd)

## How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

#### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

#### 10.7.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 67 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

- The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 67 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

#### **Master Receiver**

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

## I<sup>2</sup>C BUS INTERFACE (Cont'd)

**57**

## Table 24. I<sup>2</sup>C Register Map and Reset Values

| Address<br>(Hex.) | Register<br>Label      | 7          | 6          | 5         | 4         | 3          | 2         | 1         | 0         |

|-------------------|------------------------|------------|------------|-----------|-----------|------------|-----------|-----------|-----------|

| 0018h             | I2CCR<br>Reset Value   | 0          | 0          | PE<br>0   | ENGC<br>0 | START<br>0 | ACK<br>0  | STOP<br>0 | ITE<br>0  |

| 0019h             | I2CSR1<br>Reset Value  | EVF<br>0   | ADD10<br>0 | TRA<br>0  | BUSY<br>0 | BTF<br>0   | ADSL<br>0 | M/SL<br>0 | SB<br>0   |

| 001Ah             | I2CSR2<br>Reset Value  | 0          | 0          | 0         | AF<br>0   | STOPF<br>0 | ARLO<br>0 | BERR<br>0 | GCAL<br>0 |

| 001Bh             | I2CCCR<br>Reset Value  | FM/SM<br>0 | CC6<br>0   | CC5<br>0  | CC4<br>0  | CC3<br>0   | CC2<br>0  | CC1<br>0  | CC0<br>0  |

| 001Ch             | I2COAR1<br>Reset Value | ADD7<br>0  | ADD6<br>0  | ADD5<br>0 | ADD4<br>0 | ADD3<br>0  | ADD2<br>0 | ADD1<br>0 | ADD0<br>0 |

| 001Dh             | I2COAR2<br>Reset Value | FR1<br>0   | FR0<br>1   | 0         | 0         | 0          | ADD9<br>0 | ADD8<br>0 | 0         |

| 001Eh             | I2CDR<br>Reset Value   | MSB<br>0   | 0          | 0         | 0         | 0          | 0         | 0         | LSB<br>0  |

# **11 INSTRUCTION SET**

#### **11.1 CPU ADDRESSING MODES**

The CPU features 17 different addressing modes which can be classified in seven main groups:

| Addressing Mode | Example         |

|-----------------|-----------------|

| Inherent        | nop             |

| Immediate       | ld A,#\$55      |

| Direct          | ld A,\$55       |

| Indexed         | ld A,(\$55,X)   |

| Indirect        | ld A,([\$55],X) |

| Relative        | jrne loop       |

| Bit operation   | bset byte,#5    |

The CPU Instruction set is designed to minimize the number of bytes required per instruction: To do

| Table 26. CPU | Addressing | Mode | Overview |

|---------------|------------|------|----------|

|---------------|------------|------|----------|

so, most of the addressing modes may be subdivided in two submodes called long and short:

- Long addressing mode is more powerful because it can use the full 64 Kbyte address space, however it uses more bytes and more CPU cycles.

- Short addressing mode is less powerful because it can generally only access page zero (0000h -00FFh range), but the instruction size is more compact, and faster. All memory to memory instructions use short addressing modes only (CLR, CPL, NEG, BSET, BRES, BTJT, BTJF, INC, DEC, RLC, RRC, SLL, SRL, SRA, SWAP)

The ST7 Assembler optimizes the use of long and short addressing modes.

|           | Mode     |          | Syntax              | Destination | Pointer<br>Address<br>(Hex.) | Pointer Size<br>(Hex.) | Length<br>(Bytes) |

|-----------|----------|----------|---------------------|-------------|------------------------------|------------------------|-------------------|

| Inherent  |          |          | nop                 |             |                              |                        | + 0               |

| Immediate |          |          | ld A,#\$55          |             |                              |                        | + 1               |

| Short     | Direct   |          | ld A,\$10           | 00FF        |                              |                        | + 1               |

| Long      | Direct   |          | ld A,\$1000         | 0000FFFF    |                              |                        | + 2               |

| No Offset | Direct   | Indexed  | ld A,(X)            | 00FF        |                              |                        | + 0               |

| Short     | Direct   | Indexed  | ld A,(\$10,X)       | 001FE       |                              |                        | + 1               |

| Long      | Direct   | Indexed  | ld A,(\$1000,X)     | 0000FFFF    |                              |                        | + 2               |

| Short     | Indirect |          | ld A,[\$10]         | 00FF        | 00FF                         | byte                   | + 2               |

| Long      | Indirect |          | ld A,[\$10.w]       | 0000FFFF    | 00FF                         | word                   | + 2               |

| Short     | Indirect | Indexed  | ld A,([\$10],X)     | 001FE       | 00FF                         | byte                   | + 2               |

| Long      | Indirect | Indexed  | ld A,([\$10.w],X)   | 0000FFFF    | 00FF                         | word                   | + 2               |

| Relative  | Direct   |          | jrne loop           | PC+/-127    |                              |                        | + 1               |

| Relative  | Indirect |          | jrne [\$10]         | PC+/-127    | 00FF                         | byte                   | + 2               |

| Bit       | Direct   |          | bset \$10,#7        | 00FF        |                              |                        | + 1               |

| Bit       | Indirect |          | bset [\$10],#7      | 00FF        | 00FF                         | byte                   | + 2               |

| Bit       | Direct   | Relative | btjt \$10,#7,skip   | 00FF        |                              |                        | + 2               |

| Bit       | Indirect | Relative | btjt [\$10],#7,skip | 00FF        | 00FF                         | byte                   | + 3               |

#### INSTRUCTION SET OVERVIEW (Cont'd)

#### 11.1.6 Indirect Indexed (Short, Long)

This is a combination of indirect and short indexed addressing modes. The operand is referenced by its memory address, which is defined by the unsigned addition of an index register value (X or Y) with a pointer value located in memory. The pointer address follows the opcode.

The indirect indexed addressing mode consists of two submodes:

#### Indirect Indexed (Short)

The pointer address is a byte, the pointer size is a byte, thus allowing 00 - 1FE addressing space, and requires 1 byte after the opcode.

#### Indirect Indexed (Long)

The pointer address is a byte, the pointer size is a word, thus allowing 64 Kbyte addressing space, and requires 1 byte after the opcode.

# Table27.InstructionsSupportingDirect,Indexed,IndirectandIndirectIndexedAddressingModes

| Long and Short<br>Instructions | Function                                           |

|--------------------------------|----------------------------------------------------|

| LD                             | Load                                               |

| CP                             | Compare                                            |

| AND, OR, XOR                   | Logical Operations                                 |

| ADC, ADD, SUB, SBC             | Arithmetic Additions/Sub-<br>stractions operations |

| BCP                            | Bit Compare                                        |

| Short Instructions Only    | Function                          |

|----------------------------|-----------------------------------|

| CLR                        | Clear                             |

| INC, DEC                   | Increment/Decrement               |

| TNZ                        | Test Negative or Zero             |

| CPL, NEG                   | 1 or 2 Complement                 |

| BSET, BRES                 | Bit Operations                    |

| BTJT, BTJF                 | Bit Test and Jump Opera-<br>tions |

| SLL, SRL, SRA, RLC,<br>RRC | Shift and Rotate Operations       |

| SWAP                       | Swap Nibbles                      |

| CALL, JP                   | Call or Jump subroutine           |

#### 11.1.7 Relative mode (Direct, Indirect)

This addressing mode is used to modify the PC register value, by adding an 8-bit signed offset to it.

| Available Relative<br>Direct/Indirect<br>Instructions | Function         |

|-------------------------------------------------------|------------------|

| JRxx                                                  | Conditional Jump |

| CALLR                                                 | Call Relative    |

The relative addressing mode consists of two submodes:

#### **Relative (Direct)**

The offset is following the opcode.

#### **Relative (Indirect)**

The offset is defined in memory, which address follows the opcode.

#### CLOCK AND TIMING CHARACTERISTICS (Cont'd)

| Supplier | f <sub>OSC</sub><br>(MHz) | Typical Ceramic Resonators <sup>1)</sup> |                                                  |

|----------|---------------------------|------------------------------------------|--------------------------------------------------|

|          |                           | Reference <sup>2)</sup>                  | Recommended OSCRANGE<br>Option bit configuration |

| Murata   | 2                         | CSTCC2M00G56A-R0                         | MP Mode <sup>3)</sup>                            |

|          | 4                         | CSTCR4M00G55B-R0                         | MS Mode                                          |

|          | 8                         | CSTCE8M00G55A-R0                         | HS Mode                                          |

|          | 16                        | CSTCE16M0G53A-R0                         | HS Mode                                          |

Notes:

1. Resonator characteristics given by the ceramic resonator manufacturer.

SMD = [-R0: Plastic tape package (Ø =180mm), -B0: Bulk] LEAD = [-A0: Flat pack package (Radial taping Ho= 18mm), -B0: Bulk]

3. LP mode is not recommended for 2 MHz resonator because the peak to peak amplitude is too small (>0.8V) For more information on these resonators, please consult www.murata.com

#### **12.7 EMC CHARACTERISTICS**

Susceptibility tests are performed on a sample basis during product characterization.

# 12.7.1 Functional EMS (Electro Magnetic Susceptibility)

Based on a simple running application on the product (toggling 2 LEDs through I/O ports), the product is stressed by two electro magnetic events until a failure occurs (indicated by the LEDs).

- ESD: Electro-Static Discharge (positive and negative) is applied on all pins of the device until a functional disturbance occurs. This test conforms with the IEC 1000-4-2 standard.

- FTB: A Burst of Fast Transient voltage (positive and negative) is applied to V<sub>DD</sub> and V<sub>SS</sub> through a 100pF capacitor, until a functional disturbance occurs. This test conforms with the IEC 1000-4-4 standard.

A device reset allows normal operations to be resumed. The test results are given in the table below based on the EMS levels and classes defined in application note AN1709.

# 12.7.1.1 Designing hardened software to avoid noise problems

EMC characterization and optimization are performed at component level with a typical application environment and simplified MCU software. It should be noted that good EMC performance is highly dependent on the user application and the software in particular.

Therefore it is recommended that the user applies EMC software optimization and prequalification tests in relation with the EMC level requested for his application.

#### Software recommendations:

The software flowchart must include the management of runaway conditions such as:

- Corrupted program counter

- Unexpected reset

- Critical Data corruption (control registers...)

#### Prequalification trials:

Most of the common failures (unexpected reset and program counter corruption) can be reproduced by manually forcing a low state on the RE-SET pin or the Oscillator pins for 1 second.

To complete these trials, ESD stress can be applied directly on the device, over the range of specification values. When unexpected behaviour is detected, the software can be hardened to prevent unrecoverable errors occurring (see application note AN1015).

| Symbol            | Parameter                                                                                                                                | Conditions                                                                                                               | Level/<br>Class |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------------|

| V <sub>FESD</sub> | Voltage limits to be applied on any I/O pin to induce a functional disturbance                                                           | All Flash and ROM devices, $V_{DD}$ =5V,<br>T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8 MHz, conforms to IEC<br>1000-4-2  | ЗB              |

| V <sub>FFTB</sub> | Fast transient voltage burst limits to be applied through 100pF on $V_{\rm DD}$ and $V_{\rm DD}$ pins to induce a functional disturbance | 32K Flash device LQFP44/LQFP32, : $V_{DD}$ =5V, T <sub>A</sub> =+25°C, f <sub>OSC</sub> =8 MHz, conforms to IEC 1000-4-4 | ЗB              |

|                   |                                                                                                                                          | 48/60K Flash and all ROM devices, $V_{DD}$ =5V, $T_A$ =+25°C, $f_{OSC}$ =8 MHz, conforms to IEC 1000-4-4                 | 4A              |

57

#### CONTROL PIN CHARACTERISTICS (Cont'd)

#### Figure 86. RESET pin protection when LVD is enabled.<sup>1)2)3)4)</sup>

Figure 87. RESET pin protection when LVD is disabled.<sup>1)</sup>

#### Note 1:

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 12.9.1 on page 158. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 12.2.2 on page 139.

**Note 2:** When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a  $1M\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add 5µA to the power consumption of the MCU).

Note 4: Tips when using the LVD:

- 1. Check that all recommendations related to reset circuit have been applied (see notes above).

- 2. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality. <u>In most cases</u>, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor.

#### **13.3 SOLDERING INFORMATION**

In order to meet environmental requirements, ST offers these devices in ECOPACK® packages. These packages have a lead-free second level interconnect. The category of second level interconnect is marked on the package and on the inner box label, in compliance with JEDEC Standard JESD97. The maximum ratings related to soldering conditions are also marked on the inner box label.

ECOPACK is an ST trademark. ECOPACK® specifications are available at www.st.com.

#### DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

#### Table 30. Suggested List of Socket Types

| Device        | Socket (supplied with ST7MDT20M-<br>EMU3) | Emulator Adapter (supplied with<br>ST7MDT20M-EMU3) |

|---------------|-------------------------------------------|----------------------------------------------------|

| LQFP64 14 x14 | CAB 3303262                               | CAB 3303351                                        |

| LQFP64 10 x10 | YAMAICHI IC149-064-*75-*5                 | YAMAICHI ICP-064-6                                 |

| LQFP44 10 X10 | YAMAICHI IC149-044-*52-*5                 | YAMAICHI ICP-044-5                                 |

| LQFP32 7 X 7  | IRONWOOD SF-QFE32SA-L-01                  | IRONWOOD SK-UGA06/32A-01                           |

# 14.3.4 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 30.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet.

#### **Related Documentation**

AN 978: ST7 Visual Develop Software Key Debugging Features

AN 1938: ST7 Visual Develop for ST7 Cosmic C toolset users

AN 1940: ST7 Visual Develop for ST7 Assembler Linker toolset users