Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                              |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | ST7                                                                   |

| Core Size                  | 8-Bit                                                                 |

| Speed                      | 8MHz                                                                  |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                    |

| Number of I/O              | 48                                                                    |

| Program Memory Size        | 48KB (48K x 8)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1.5К х 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                           |

| Data Converters            | A/D 16x10b                                                            |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 64-LQFP                                                               |

| Supplier Device Package    | -                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321br7t6 |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### CENTRAL PROCESSING UNIT (Cont'd)

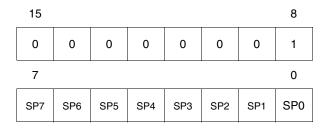

## Stack Pointer (SP)

## Read/Write

**47/**

Reset Value: 01 FFh

The Stack Pointer is a 16-bit register which is always pointing to the next free location in the stack. It is then decremented after data has been pushed onto the stack and incremented before data is popped from the stack (see Figure 2).

Since the stack is 256 bytes deep, the 8 most significant bits are forced by hardware. Following an MCU Reset, or after a Reset Stack Pointer instruction (RSP), the Stack Pointer contains its reset value (the SP7 to SP0 bits are set) which is the stack higher address.

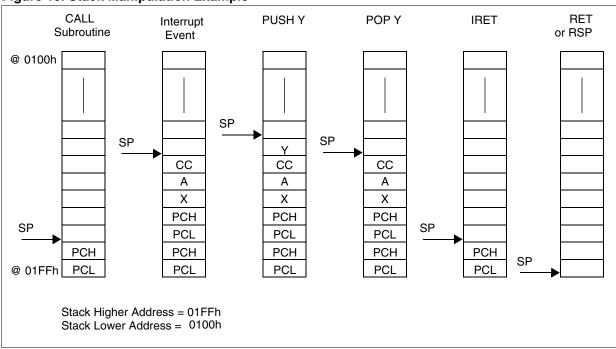

#### Figure 10. Stack Manipulation Example

The least significant byte of the Stack Pointer (called S) can be directly accessed by a LD instruction.

**Note:** When the lower limit is exceeded, the Stack Pointer wraps around to the stack upper limit, without indicating the stack overflow. The previously stored information is then overwritten and therefore lost. The stack also wraps in case of an underflow.

The stack is used to save the return address during a subroutine call and the CPU context during an interrupt. The user may also directly manipulate the stack by means of the PUSH and POP instructions. In the case of an interrupt, the PCL is stored at the first location pointed to by the SP. Then the other registers are stored in the next locations as shown in Figure 2.

- When an interrupt is received, the SP is decremented and the context is pushed on the stack.

- On return from interrupt, the SP is incremented and the context is popped from the stack.

A subroutine call occupies two locations and an interrupt five locations in the stack area.

## **7 INTERRUPTS**

### 7.1 INTRODUCTION

The ST7 enhanced interrupt management provides the following features:

- Hardware interrupts

- Software interrupt (TRAP)

- Nested or concurrent interrupt management with flexible interrupt priority and level management:

- Up to 4 software programmable nesting levels

- Up to 16 interrupt vectors fixed by hardware

- 2 non maskable events: RESET, TRAP

- 1 maskable Top Level event: TLI

- This interrupt management is based on:

- Bit 5 and bit 3 of the CPU CC register (I1:0),

- Interrupt software priority registers (ISPRx),

- Fixed interrupt vector addresses located at the high addresses of the memory map (FFE0h to FFFFh) sorted by hardware priority order.

This enhanced interrupt controller guarantees full upward compatibility with the standard (not nested) ST7 interrupt controller.

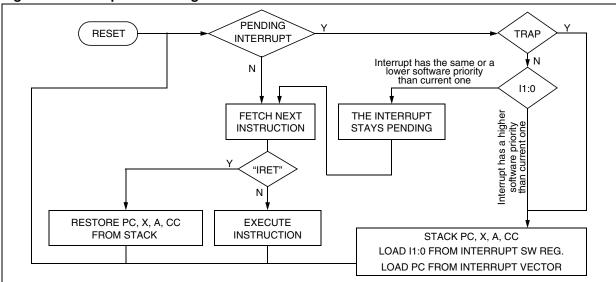

## 7.2 MASKING AND PROCESSING FLOW

The interrupt masking is managed by the I1 and I0 bits of the CC register and the ISPRx registers which give the interrupt software priority level of

**Figure 19. Interrupt Processing Flowchart**

each interrupt vector (see Table 6). The processing flow is shown in Figure 19

When an interrupt request has to be serviced:

- Normal processing is suspended at the end of the current instruction execution.

- The PC, X, A and CC registers are saved onto the stack.

- I1 and I0 bits of CC register are set according to the corresponding values in the ISPRx registers of the serviced interrupt vector.

- The PC is then loaded with the interrupt vector of the interrupt to service and the first instruction of the interrupt service routine is fetched (refer to "Interrupt Mapping" table for vector addresses).

The interrupt service routine should end with the IRET instruction which causes the contents of the saved registers to be recovered from the stack.

**Note**: As a consequence of the IRET instruction, the I1 and I0 bits will be restored from the stack and the program in the previous level will resume.

#### **Table 6. Interrupt Software Priority Levels**

| Interrupt software priority   | Level | 11 | 10 |

|-------------------------------|-------|----|----|

| Level 0 (main)                | Low   | 1  | 0  |

| Level 1                       |       | 0  | 1  |

| Level 2                       | 🔸     | 0  | 0  |

| Level 3 (= interrupt disable) | High  | 1  | 1  |

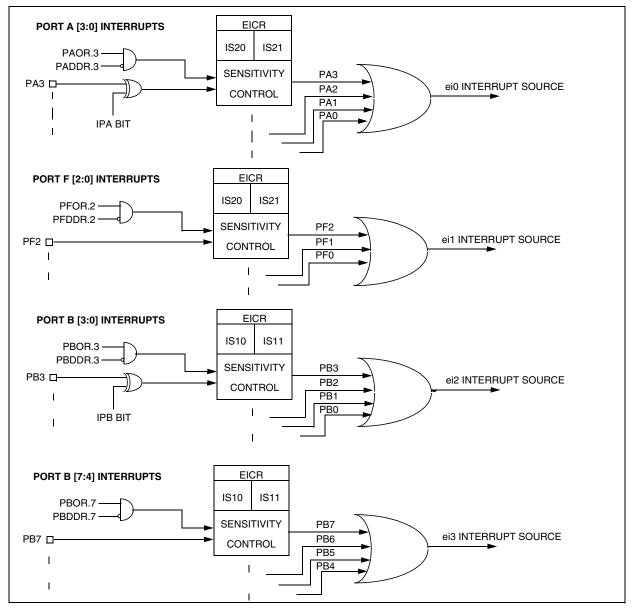

## INTERRUPTS (Cont'd)

## Figure 23. External Interrupt Control bits

<u>ل</u>حک

38/187

## 16-BIT TIMER (Cont'd)

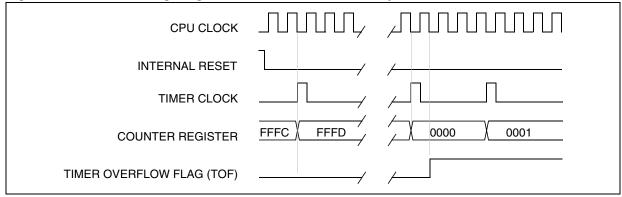

### Figure 44. Counter Timing Diagram, Internal Clock Divided by 2

| CPU CLOCK                 |                                                 |

|---------------------------|-------------------------------------------------|

| INTERNAL RESET            |                                                 |

| TIMER CLOCK               |                                                 |

| –<br>COUNTER REGISTER –   | \ FFFD\ FFFE\ FFFF\ 0000 \ 0001 \ 0002 \ 0003 \ |

| TIMER OVERFLOW FLAG (TOF) |                                                 |

## Figure 45. Counter Timing Diagram, Internal Clock Divided by 4

## Figure 46. Counter Timing Diagram, Internal Clock Divided By 8

| CPU CLOCK                 |                |

|---------------------------|----------------|

| INTERNAL RESET            | 1              |

| TIMER CLOCK               |                |

| COUNTER REGISTER          | FFFC FFFD 0000 |

| TIMER OVERFLOW FLAG (TOF) |                |

Note: The MCU is in reset state when the internal reset signal is high, when it is low the MCU is running.

#### 16-BIT TIMER (Cont'd)

## OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

## OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **COUNTER HIGH REGISTER (CHR)**

Read Only

7

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER HIGH REGISTER (ACHR)

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 HIGH REGISTER (IC2HR)**

Read Only

Λ

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

### SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 10.5.3.3 Master Mode Operation

In master mode, the serial clock is output on the SCK pin. The clock frequency, polarity and phase are configured by software (refer to the description of the SPICSR register).

Note: The idle state of SCK must correspond to the polarity selected in the SPICSR register (by pulling up SCK if CPOL=1 or pulling down SCK if CPOL=0).

To operate the SPI in master mode, perform the following steps in order (if the SPICSR register is not written first, the SPICR register setting (MSTR bit) may be not taken into account):

1. Write to the SPICR register:

- Select the clock frequency by configuring the SPR[2:0] bits.

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits. Figure 58 shows the four possible configurations. **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Write to the SPICSR register:

- Either set the SSM bit and set the SSI bit or clear the SSM bit and tie the SS pin high for the complete byte transmit sequence.

- Write to the SPICR register:

- Set the MSTR and SPE bits

MSTR and SPE bits remain set only if SS is high).

The transmit sequence begins when software writes a byte in the SPIDR register.

#### 10.5.3.4 Master Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MOSI pin most significant bit first.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if the SPIE bit is set and the interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set

- 2. A read to the SPIDR register.

Note: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

#### 10.5.3.5 Slave Mode Operation

In slave mode, the serial clock is received on the SCK pin from the master device.

To operate the SPI in slave mode:

- 1. Write to the SPICSR register to perform the following actions:

- Select the clock polarity and clock phase by configuring the CPOL and CPHA bits (see **Note:** The slave must have the same CPOL and CPHA settings as the master.

- Manage the SS pin as described in Section 10.5.3.2 and Figure 56. If CPHA=1 SS must be held low continuously. If CPHA=0 SS must be held low during byte transmission and pulled up between each byte to let the slave write in the shift register.

- 2. Write to the SPICR register to clear the MSTR bit and set the SPE bit to enable the SPI I/O functions.

#### 10.5.3.6 Slave Mode Transmit Sequence

When software writes to the SPIDR register, the data byte is loaded into the 8-bit shift register and then shifted out serially to the MISO pin most significant bit first.

The transmit sequence begins when the slave device receives the clock signal and the most significant bit of the data on its MOSI pin.

When data transfer is complete:

- The SPIF bit is set by hardware

- An interrupt request is generated if SPIE bit is set and interrupt mask in the CCR register is cleared.

Clearing the SPIF bit is performed by the following software sequence:

- 1. An access to the SPICSR register while the SPIF bit is set.

- A write or a read to the SPIDR register.

Notes: While the SPIF bit is set, all writes to the SPIDR register are inhibited until the SPICSR register is read.

The SPIF bit can be cleared during a second transmission; however, it must be cleared before the second SPIF bit in order to prevent an Overrun condition (see Section 10.5.5.2).

<u>لرک</u>

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.6.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### Character Transmission

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 1.).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

2. A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 2.).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### Idle Characters

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set, that is, before writing the next byte in the SCIDR.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 1 (SCICR1)

#### Read/Write

Reset Value: x000 0000 (x0h)

| 7  |    |      |   |      |     |    | 0   |

|----|----|------|---|------|-----|----|-----|

| R8 | Т8 | SCID | М | WAKE | PCE | PS | PIE |

Bit 7 = R8 Receive data bit 8.

This bit is used to store the 9th bit of the received word when M = 1.

#### Bit 6 = T8 Transmit data bit 8.

This bit is used to store the 9th bit of the transmitted word when M = 1.

Bit 5 = **SCID** *Disabled for low power consumption* When this bit is set the SCI prescalers and outputs are stopped and the end of the current byte transfer in order to reduce power consumption. This bit is set and cleared by software. 0: SCI enabled

1: SCI prescaler and outputs disabled

Bit  $4 = \mathbf{M}$  Word length. This bit determines the word length. It is set or cleared by software. 0: 1 Start bit, 8 Data bits, 1 Stop bit

1: 1 Start bit, 9 Data bits, 1 Stop bit

**Note**: The M bit must not be modified during a data transfer (both transmission and reception).

#### Bit 3 = WAKE Wake-Up method.

This bit determines the SCI Wake-Up method, it is set or cleared by software. 0: Idle Line 1: Address Mark

### Bit 2 = **PCE** Parity control enable.

This bit selects the hardware parity control (generation and detection). When the parity control is enabled, the computed parity is inserted at the MSB position (9th bit if M = 1; 8th bit if M = 0) and parity is checked on the received data. This bit is set and cleared by software. Once it is set, PCE is active after the current byte (in reception and in transmission).

0: Parity control disabled

1: Parity control enabled

#### Bit 1 = **PS** Parity selection.

This bit selects the odd or even parity when the parity generation/detection is enabled (PCE bit set). It is set and cleared by software. The parity is selected after the current byte.

0: Even parity 1: Odd parity

r. Odd panty

#### Bit 0 = **PIE** Parity interrupt enable.

This bit enables the interrupt capability of the hardware parity control when a parity error is detected (PE bit set). It is set and cleared by software. 0: Parity error interrupt disabled

1: Parity error interrupt enabled.

110/187

## I<sup>2</sup>C INTERFACE (Cont'd)

## How to release the SDA / SCL lines

Set and subsequently clear the STOP bit while BTF is set. The SDA/SCL lines are released after the transfer of the current byte.

#### **SMBus Compatibility**

ST7 I<sup>2</sup>C is compatible with SMBus V1.1 protocol. It supports all SMBus adressing modes, SMBus bus protocols and CRC-8 packet error checking. Refer to AN1713: SMBus Slave Driver For ST7 I<sup>2</sup>C Peripheral.

### 10.7.4.2 Master Mode

To switch from default Slave mode to Master mode a Start condition generation is needed.

#### Start condition

Setting the START bit while the BUSY bit is cleared causes the interface to switch to Master mode (M/SL bit set) and generates a Start condition.

Once the Start condition is sent:

The EVF and SB bits are set by hardware with an interrupt if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register with the Slave address, **holding the SCL line low** (see Figure 67 Transfer sequencing EV5).

#### Slave address transmission

Then the slave address is sent to the SDA line via the internal shift register.

In 7-bit addressing mode, one address byte is sent.

In 10-bit addressing mode, sending the first byte including the header sequence causes the following event:

The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV9). Then the second address byte is sent by the interface.

After completion of this transfer (and acknowledge from the slave if the ACK bit is set):

- The EVF bit is set by hardware with interrupt generation if the ITE bit is set.

Then the master waits for a read of the SR1 register followed by a write in the CR register (for example set PE bit), **holding the SCL line low** (see Figure 67 Transfer sequencing EV6).

Next the master must enter Receiver or Transmitter mode.

**Note:** In 10-bit addressing mode, to switch the master to Receiver mode, software must generate a repeated Start condition and resend the header sequence with the least significant bit set (11110xx1).

#### **Master Receiver**

Following the address transmission and after SR1 and CR registers have been accessed, the master receives bytes from the SDA line into the DR register via the internal shift register. After each byte the interface generates in sequence:

- Acknowledge pulse if the ACK bit is set

- EVF and BTF bits are set by hardware with an interrupt if the ITE bit is set.

Then the interface waits for a read of the SR1 register followed by a read of the DR register, **holding the SCL line low** (see Figure 67 Transfer sequencing EV7).

To close the communication: before reading the last byte from the DR register, set the STOP bit to generate the Stop condition. The interface goes automatically back to slave mode (M/SL bit cleared).

**Note:** In order to generate the non-acknowledge pulse after the last received data byte, the ACK bit must be cleared just before reading the second last data byte.

## I<sup>2</sup>C BUS INTERFACE (Cont'd)

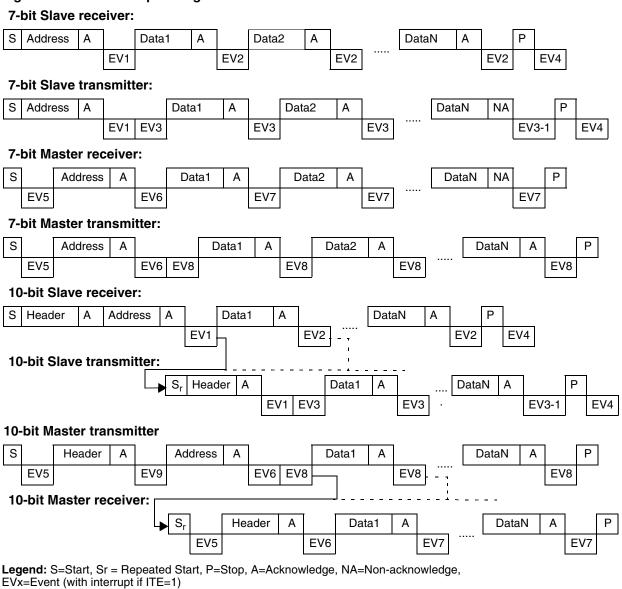

## Figure 67. Transfer Sequencing

EV1: EVF=1, ADSL=1, cleared by reading SR1 register.

EV2: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

EV3: EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

EV3-1: EVF=1, AF=1, BTF=1; AF is cleared by reading SR1 register. BTF is cleared by releasing the

lines (STOP=1, STOP=0) or by writing DR register (DR=FFh). Note: If lines are released by

STOP=1, STOP=0, the subsequent EV4 is not seen.

EV4: EVF=1, STOPF=1, cleared by reading SR2 register.

EV5: EVF=1, SB=1, cleared by reading SR1 register followed by writing DR register.

EV6: EVF=1, cleared by reading SR1 register followed by writing CR register (for example PE=1).

EV7: EVF=1, BTF=1, cleared by reading SR1 register followed by reading DR register.

EV8: EVF=1, BTF=1, cleared by reading SR1 register followed by writing DR register.

EV9: EVF=1, ADD10=1, cleared by reading SR1 register followed by writing DR register.

## ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

## I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C CLOCK CONTROL REGISTER (CCR)

Read / Write Reset Value: 0000 0000 (00h)

| 7     |     |     |     |     |     |     | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|

| FM/SM | CC6 | CC5 | CC4 | CC3 | CC2 | CC1 | CC0 |

Bit 7 = **FM/SM** *Fast/Standard I*<sup>2</sup>*C mode.* This bit is set and cleared by software. It is not cleared when the interface is disabled (PE=0). 0: Standard I<sup>2</sup>C mode 1: Fast I<sup>2</sup>C mode

Bit 6:0 = **CC[6:0]** 7-bit clock divider.

These bits select the speed of the bus ( $F_{SCL}$ ) depending on the I<sup>2</sup>C mode. They are not cleared when the interface is disabled (PE=0).

Refer to the Electrical Characteristics section for the table of values.

Note: The programmed  $\mathrm{F}_{\mathrm{SCL}}$  assumes no load on SCL and SDA lines.

## I<sup>2</sup>C DATA REGISTER (DR)

## Read / Write

Reset Value: 0000 0000 (00h)

Bit 7:0 = **D**[7:0] *8-bit Data Register.*

These bits contain the byte to be received or transmitted on the bus.

- Transmitter mode: Byte transmission start automatically when the software writes in the DR register.

- Receiver mode: the first data byte is received automatically in the DR register using the least significant bit of the address.

Then, the following data bytes are received one by one after reading the DR register.

## CLOCK AND TIMING CHARACTERISTICS (Cont'd)

## 12.5.3 Crystal and Ceramic Resonator Oscillators

The ST7 internal clock can be supplied with four different Crystal/Ceramic resonator oscillators. All the information given in this paragraph is based on characterization results with specified typical external components. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and start-up stabilization time. Refer to the crystal/ceramic resonator manufacturer for more details (frequency, package, accuracy...).

| Symbol           | Parameter                                      | Сог                  | nditions      | Min | Max   | Unit |

|------------------|------------------------------------------------|----------------------|---------------|-----|-------|------|

|                  |                                                | LP: Low powe         | r oscillator  | 1   | 2     |      |

| 4                | Oppillator Fragmanau 1)                        | MP: Medium p         | >2            | 4   | N411- |      |

| f <sub>OSC</sub> | Oscillator Frequency <sup>1)</sup>             | MS: Medium s         | >4            | 8   | MHz   |      |

|                  |                                                | HS: High spee        | >8            | 16  |       |      |

| R <sub>F</sub>   | Feedback resistor <sup>2)</sup>                |                      |               | 20  | 40    | kΩ   |

|                  | Decomposed of load compatitudes and            | R <sub>S</sub> =200Ω | LP oscillator | 22  | 56    |      |

| C <sub>L1</sub>  | Recommended load capacitance ver-              | R <sub>S</sub> =200Ω | MP oscillator | 22  | 46    |      |

| C <sub>L2</sub>  | sus equivalent serial resistance of the        | R <sub>S</sub> =200Ω | MS oscillator | 18  | 33    | pF   |

| - L2             | crystal or ceramic resonator (R <sub>S</sub> ) | R <sub>S</sub> =100Ω | HS oscillator | 15  | 33    |      |

| Symbol         | Parameter            |                                                         | Conditions                                                       |                         |                          | Unit |

|----------------|----------------------|---------------------------------------------------------|------------------------------------------------------------------|-------------------------|--------------------------|------|

| i <sub>2</sub> | OSC2 driving current | V <sub>DD</sub> =5V<br>V <sub>IN</sub> =V <sub>SS</sub> | LP oscillator<br>MP oscillator<br>MS oscillator<br>HS oscillator | 80<br>160<br>310<br>610 | 150<br>250<br>460<br>910 | μA   |

#### Notes:

1. The oscillator selection can be optimized in terms of supply current using an high quality resonator with small R<sub>S</sub> value. Refer to crystal/ceramic resonator manufacturer for more details.

2. Data based on characterisation results, not tested in production.

## EMC CHARACTERISTICS (Cont'd)

## 12.7.2 Electro Magnetic Interference (EMI)

Based on a simple application running on the product (toggling 2 LEDs through the I/O ports), the product is monitored in terms of emission. This emission test is in line with the norm SAE J 1752/3 which specifies the board and the loading of each pin.

| Symbol           | Parameter  | Conditions                                                                                                      | Monitored       | Max vs. [f | osc/f <sub>CPU</sub> ] <sup>1</sup> | Unit |

|------------------|------------|-----------------------------------------------------------------------------------------------------------------|-----------------|------------|-------------------------------------|------|

| Symbol           | Farameter  | anameter conditions                                                                                             |                 | 8/4MHz     | 16/8MHz                             |      |

|                  |            | 48/60K Flash Devices:                                                                                           | 0.1MHz to 30MHz | 15         | 20                                  |      |

| · ·              | Peak level | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,                                                                     | 30MHz to 130MHz | 20         | 27                                  | dBµV |

| S <sub>EMI</sub> | Feak level | LQFP64 10x10 package                                                                                            | 130MHz to 1GHz  | 7          | 12                                  |      |

|                  |            | conforming to SAE J 1752/3                                                                                      | SAE EMI Level   | 2.5        | 3                                   | -    |

|                  |            | 32K/Flash Devices:                                                                                              | 0.1MHz to 30MHz | 13         | 14                                  | dBμV |

| · ·              | Peak level | V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,<br>LQFP44 10x10 package<br>conforming to SAE J 1752/3               | 30MHz to 130MHz | 20         | 25                                  |      |

| S <sub>EMI</sub> |            |                                                                                                                 | 130MHz to 1GHz  | 16         | 21                                  |      |

|                  |            |                                                                                                                 | SAE EMI Level   | 3          | 3.5                                 | -    |

|                  |            | 60K ROM Devices:<br>V <sub>DD</sub> =5V, T <sub>A</sub> =+25°C,<br>LQFP64 package<br>conforming to SAE J 1752/3 | 0.1MHz to 30MHz | 15         | 20                                  |      |

| · ·              | Peak level |                                                                                                                 | 30MHz to 130MHz | 20         | 27                                  | dBμV |

| S <sub>EMI</sub> | Peaklevel  |                                                                                                                 | 130MHz to 1GHz  | 7          | 12                                  |      |

|                  |            |                                                                                                                 | SAE EMI Level   | 2.5        | 3                                   | -    |

|                  |            | 32K ROM devices: V <sub>DD</sub> =5V,                                                                           | 0.1MHz to 30MHz | 17         | 21                                  |      |

| · ·              | Dealstand  | T <sub>A</sub> =+25°C,                                                                                          | 30MHz to 130MHz | 24         | 30                                  | dBμV |

| S <sub>EMI</sub> | Peak level | LQFP44 10x10 package                                                                                            | 130MHz to 1GHz  | 18         | 23                                  |      |

|                  |            | conforming to SAE J 1752/3                                                                                      | SAE EMI Level   | 3          | 3.5                                 | -    |

Notes:

1. Data based on characterization results, not tested in production.

2. Refer to Application Note AN1709 for data on other package types.

## CONTROL PIN CHARACTERISTICS (Cont'd)

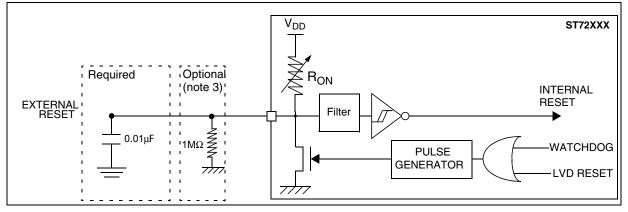

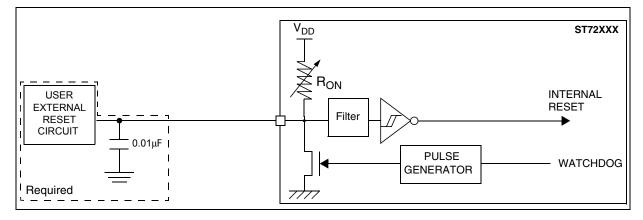

#### Figure 86. RESET pin protection when LVD is enabled.<sup>1)2)3)4)</sup>

Figure 87. RESET pin protection when LVD is disabled.<sup>1)</sup>

#### Note 1:

- The reset network protects the device against parasitic resets.

- The output of the external reset circuit must have an open-drain output to drive the ST7 reset pad. Otherwise the device can be damaged when the ST7 generates an internal reset (LVD or watchdog).

- Whatever the reset source is (internal or external), the user must ensure that the level on the RESET pin can go below the V<sub>IL</sub> max. level specified in section 12.9.1 on page 158. Otherwise the reset will not be taken into account internally.

- Because the reset circuit is designed to allow the internal RESET to be output in the RESET pin, the user must ensure that the current sunk on the RESET pin is less than the absolute maximum value specified for I<sub>INJ(RESET)</sub> in section 12.2.2 on page 139.

**Note 2:** When the LVD is enabled, it is recommended not to connect a pull-up resistor or capacitor. A 10nF pull-down capacitor is required to filter noise on the reset line.

**Note 3:** In case a capacitive power supply is used, it is recommended to connect a  $1M\Omega$  pull-down resistor to the RESET pin to discharge any residual voltage induced by the capacitive effect of the power supply (this will add 5µA to the power consumption of the MCU).

Note 4: Tips when using the LVD:

- 1. Check that all recommendations related to reset circuit have been applied (see notes above).

- 2. Check that the power supply is properly decoupled (100nF + 10 $\mu$ F close to the MCU). Refer to AN1709 and AN2017. If this cannot be done, it is recommended to put a 100nF + 1M $\Omega$  pull-down on the RESET pin.

- 3. The capacitors connected on the RESET pin and also the power supply are key to avoid any start-up marginality. <u>In most cases</u>, steps 1 and 2 above are sufficient for a robust solution. Otherwise: replace 10nF pull-down on the RESET pin with a 5µF to 20µF capacitor.

## COMMUNICATION INTERFACE CHARACTERISTICS (Cont'd)

The following table gives the values to be written in the I2CCCR register to obtain the required  $I^2C$  SCL line frequency.

## Table 28. SCL Frequency Table

|                  |                                                   |                  |                       | I2CCCF       | R Value                 |                             |                       |                             |  |

|------------------|---------------------------------------------------|------------------|-----------------------|--------------|-------------------------|-----------------------------|-----------------------|-----------------------------|--|

| f <sub>SCL</sub> | f <sub>CPU</sub> =4 MHz. f <sub>CPU</sub> =8 MHz. |                  |                       |              |                         |                             |                       |                             |  |

| (kHz)            | V <sub>DD</sub> = 4.1 V                           |                  | V <sub>DD</sub> = 5 V |              | V <sub>DD</sub> = 4.1 V |                             | V <sub>DD</sub> = 5 V |                             |  |

|                  | $R_P=3.3k\Omega$                                  | $R_P=4.7k\Omega$ | $R_P=3.3k\Omega$      | $R_P$ =4.7kΩ | $R_P=3.3k\Omega$        | <b>R<sub>P</sub>=4.7k</b> Ω | $R_P=3.3k\Omega$      | <b>R<sub>P</sub>=4.7k</b> Ω |  |

| 400              | NA                                                | NA               | NA                    | NA           | 83h                     | 83                          | 83h                   | 83h                         |  |

| 300              | NA                                                | NA               | NA                    | NA           | 85h                     | 85h                         | 85h                   | 85h                         |  |

| 200              | 83h                                               | 83h              | 83h                   | 83h          | 8Ah                     | 89h                         | 8Ah                   | 8Ah                         |  |

| 100              | 10h                                               | 10h              | 10h                   | 10h          | 24h                     | 23h                         | 24h                   | 23h                         |  |

| 50               | 24h                                               | 24h              | 24h                   | 24h          | 4Ch                     | 4Ch                         | 4Ch                   | 4Ch                         |  |

| 20               | 5Fh                                               | 5Fh              | 5Fh                   | 5Fh          | FFh                     | FFh                         | FFh                   | FFh                         |  |

## Legend:

$R_P$  = External pull-up resistance  $f_{SCL}$  = I<sup>2</sup>C speed NA = Not achievable

## Note:

– For speeds around 200 kHz, achieved speed can have  $\pm 5\%$  tolerance

- For other speed ranges, achieved speed can have ±2% tolerance

The above variations depend on the accuracy of the external components used.

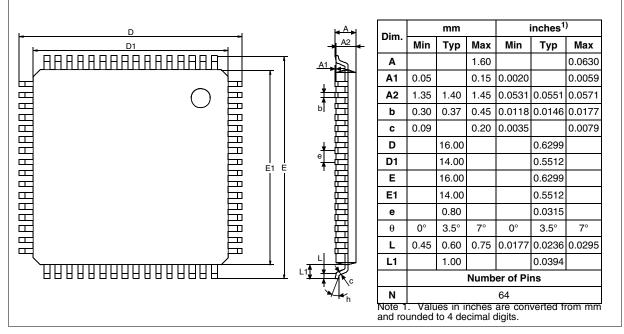

## **13 PACKAGE CHARACTERISTICS**

## **13.1 PACKAGE MECHANICAL DATA**

## Figure 98. 64-Pin Low Profile Quad Flat Package (14x14)

<u>لرکم</u>

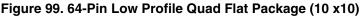

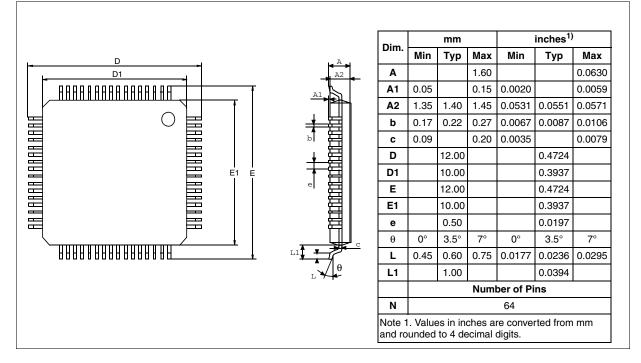

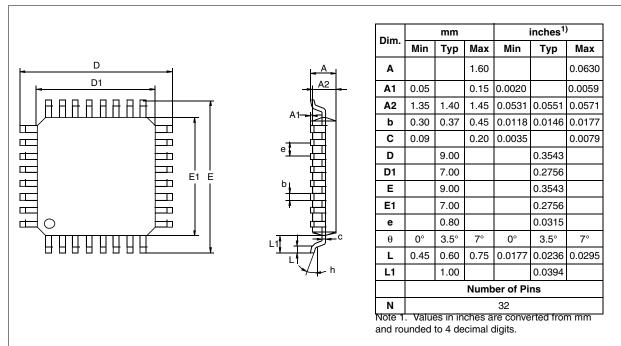

## PACKAGE MECHANICAL DATA (Cont'd)

## Figure 100. 44-Pin Low Profile Quad Flat Package

| D:   |      | mm    |      | inches <sup>1)</sup> |        |        |  |

|------|------|-------|------|----------------------|--------|--------|--|

| Dim. | Min  | Тур   | Max  | Min                  | Тур    | Max    |  |

| Α    |      |       | 1.60 |                      |        | 0.0630 |  |

| A1   | 0.05 |       | 0.15 | 0.0020               |        | 0.0059 |  |

| A2   | 1.35 | 1.40  | 1.45 | 0.0531               | 0.0551 | 0.0571 |  |

| b    | 0.30 | 0.37  | 0.45 | 0.0118               | 0.0146 | 0.0177 |  |

| С    | 0.09 |       | 0.20 | 0.0035               |        | 0.0079 |  |

| D    |      | 12.00 |      |                      | 0.4724 |        |  |

| D1   |      | 10.00 |      |                      | 0.3937 |        |  |

| Е    |      | 12.00 |      |                      | 0.4724 |        |  |

| E1   |      | 10.00 |      |                      | 0.3937 |        |  |

| е    |      | 0.80  |      |                      | 0.0315 |        |  |

| θ    | 0°   | 3.5°  | 7°   | 0°                   | 3.5°   | 7°     |  |

| L    | 0.45 | 0.60  | 0.75 | 0.0177               | 0.0236 | 0.0295 |  |

| L1   |      | 1.00  |      |                      | 0.0394 |        |  |

|      |      |       | Numb | per of Pi            | ns     |        |  |

| Ν    | 44   |       |      |                      |        |        |  |

and rounded to 4 decimal digits.

## Figure 101. 32-Pin Low Profile Quad Flat Package

57

| IDENTIFICATION | DESCRIPTION                                                                          |

|----------------|--------------------------------------------------------------------------------------|

| AN1071         | HALF DUPLEX USB-TO-SERIAL BRIDGE USING THE ST72611 USB MICROCONTROLLER               |

| AN1106         | TRANSLATING ASSEMBLY CODE FROM HC05 TO ST7                                           |

| AN1179         | PROGRAMMING ST7 FLASH MICROCONTROLLERS IN REMOTE ISP MODE (IN-SITU PRO-<br>GRAMMING) |

| AN1446         | USING THE ST72521 EMULATOR TO DEBUG AN ST72324 TARGET APPLICATION                    |

| AN1477         | EMULATED DATA EEPROM WITH XFLASH MEMORY                                              |

| AN1527         | DEVELOPING A USB SMARTCARD READER WITH ST7SCR                                        |

| AN1575         | ON-BOARD PROGRAMMING METHODS FOR XFLASH AND HDFLASH ST7 MCUS                         |

| AN1576         | IN-APPLICATION PROGRAMMING (IAP) DRIVERS FOR ST7 HDFLASH OR XFLASH MCUS              |

| AN1577         | DEVICE FIRMWARE UPGRADE (DFU) IMPLEMENTATION FOR ST7 USB APPLICATIONS                |

| AN1601         | SOFTWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |

| AN1603         | USING THE ST7 USB DEVICE FIRMWARE UPGRADE DEVELOPMENT KIT (DFU-DK)                   |

| AN1635         | ST7 CUSTOMER ROM CODE RELEASE INFORMATION                                            |

| AN1754         | DATA LOGGING PROGRAM FOR TESTING ST7 APPLICATIONS VIA ICC                            |

| AN1796         | FIELD UPDATES FOR FLASH BASED ST7 APPLICATIONS USING A PC COMM PORT                  |

| AN1900         | HARDWARE IMPLEMENTATION FOR ST7DALI-EVAL                                             |

| AN1904         | ST7MC THREE-PHASE AC INDUCTION MOTOR CONTROL SOFTWARE LIBRARY                        |

| AN1905         | ST7MC THREE-PHASE BLDC MOTOR CONTROL SOFTWARE LIBRARY                                |

| SYSTEM OPTIMIZ | ATION                                                                                |

| AN1711         | SOFTWARE TECHNIQUES FOR COMPENSATING ST7 ADC ERRORS                                  |

| AN1827         | IMPLEMENTATION OF SIGMA-DELTA ADC WITH ST7FLITE05/09                                 |

| AN2009         | PWM MANAGEMENT FOR 3-PHASE BLDC MOTOR DRIVES USING THE ST7FMC                        |

| AN2030         | BACK EMF DETECTION DURING PWM ON TIME BY ST7MC                                       |

## Table 31. ST7 Application Notes

LD sema,A IRET Case 2: Writing to PxOR or PxDDR with Global Interrupts Disabled: SIM ; set the interrupt mask LD A.PFDR AND A,#\$02 LD X,A ; store the level before writing to PxOR/PxDDR LD A.#\$90 LD PFDDR,A; Write into PFDDR LD A,#\$ff LD PFOR,A ; Write to PFOR LD A, PFDR AND A,#\$02 LD Y,A ; store the level after writing to PxOR/ **PxDDR** LD A,X ; check for falling edge cp A,#\$02 jrne OUT TNZ Y jrne OUT LD A,#\$01 LD sema, A ; set the semaphore to '1' if edge is detected RIM ; reset the interrupt mask LD A, sema ; check the semaphore status CP A,#\$01 irne OUT call call\_routine; call the interrupt routine RIM OUT: RIM JP while\_loop .call\_routine ; entry to call\_routine PUSH A PUSH X PUSH CC .ext1 rt ; entry to interrupt routine LD A,#\$00 LD sema,A IRET

## 15.1.3 Clearing active interrupts outside interrupt routine

When an active interrupt request occurs at the same time as the related flag is being cleared, an unwanted reset may occur.

**Note:** clearing the related interrupt mask will not generate an unwanted reset

#### **Concurrent interrupt context**

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

Perform SIM and RIM operation before and after resetting an active interrupt request.

Example:

SIM

reset interrupt flag

RIM

#### Nested interrupt context:

The symptom does not occur when the interrupts are handled normally, i.e.

when:

- The interrupt flag is cleared within its own interrupt routine

- The interrupt flag is cleared within any interrupt routine with higher or identical priority level

- The interrupt flag is cleared in any part of the code while this interrupt is disabled

If these conditions are not met, the symptom can be avoided by implementing the following sequence:

PUSH CC SIM reset interrupt flag POP CC

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2008 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan -Malaysia - Malta - Morocco - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

57