Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014.10                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                |

| Core Processor             | ST7                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 8MHz                                                                    |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                              |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 48                                                                      |

| Program Memory Size        | 48KB (48K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 1.5K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                             |

| Data Converters            | A/D 16x10b                                                              |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f321br7t6tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table of Contents ——

\_\_\_\_\_

| 1 DESC  | CRIPTION                                                  | 7  |

|---------|-----------------------------------------------------------|----|

| 2 PIN D | DESCRIPTION                                               | 8  |

|         | STER & MEMORY MAP                                         |    |

| 4 FLAS  |                                                           | 18 |

| 4.1     |                                                           | 18 |

| 4.2     | MAIN FEATURES                                             | 18 |

| 4.3     | STRUCTURE                                                 | 18 |

|         | 4.3.1 Read-out Protection                                 | 18 |

| 4.4     | ICC INTERFACE                                             | 19 |

| 4.5     | ICP (IN-CIRCUIT PROGRAMMING)                              | 20 |

| 4.6     | IAP (IN-APPLICATION PROGRAMMING)                          | 20 |

| 4.7     | RELATED DOCUMENTATION                                     | 20 |

|         | 4.7.1 Register Description                                | 20 |

| 5 CEN   | TRAL PROČESSING UNIT                                      |    |

| 5.1     | INTRODUCTION                                              | 21 |

| 5.2     | MAIN FEATURES                                             | 21 |

| 5.3     | CPU REGISTERS                                             | 21 |

| 6 SUPF  | PLY, RESET AND CLOCK MANAGEMENT                           | 24 |

|         | PHASE LOCKED LOOP                                         |    |

| 6.2     | MULTI-OSCILLATOR (MO)                                     | 25 |

|         | RESET SEQUENCE MANAGER (RSM)                              |    |

|         | 6.3.1 Introduction                                        |    |

|         | 6.3.2 Asynchronous External RESET pin                     |    |

|         | 6.3.3 External Power-On RESET                             |    |

|         | 6.3.4 Internal Low Voltage Detector (LVD) RESET           | 27 |

|         | 6.3.5 Internal Watchdog RESET                             |    |

| 6.4     | SYSTEM INTEGRITY MANAGEMENT (SI)                          |    |

|         | 6.4.1 Low Voltage Detector (LVD)                          |    |

|         | 6.4.2Auxiliary Voltage Detector (AVD)6.4.3Low Power Modes |    |

|         | 6.4.4 Register Description                                |    |

| 7 INTE  | RRUPTS                                                    |    |

| 7.1     |                                                           | 32 |

| 7.2     | MASKING AND PROCESSING FLOW                               | 32 |

| 7.3     | INTERRUPTS AND LOW POWER MODES                            | 34 |

| 7.4     | CONCURRENT & NESTED MANAGEMENT                            | 34 |

| 7.5     | INTERRUPT REGISTER DESCRIPTION                            | 35 |

|         | EXTERNAL INTERRUPTS                                       |    |

|         | 7.6.1 I/O Port Interrupt Sensitivity                      | -  |

| 7.7     | EXTERNAL INTERRUPT CONTROL REGISTER (EICR)                | 39 |

|         | ER SAVING MODES                                           |    |

|         |                                                           |    |

|         | SLOW MODE                                                 |    |

|         | WAIT MODE                                                 |    |

57

#### **6.4 SYSTEM INTEGRITY MANAGEMENT (SI)**

The System Integrity Management block contains the Low Voltage Detector (LVD), Auxiliary Voltage Detector (AVD) functions. It is managed by the SICSR register.

#### 6.4.1 Low Voltage Detector (LVD)

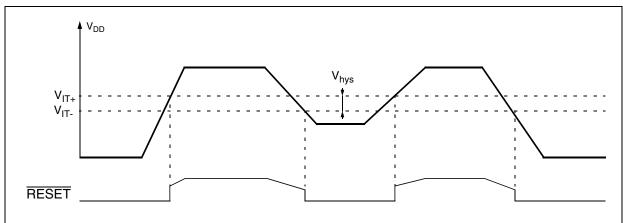

The Low Voltage Detector function (LVD) generates a static reset when the  $V_{DD}$  supply voltage is below a  $V_{IT}$  reference value. This means that it secures the power-up as well as the power-down keeping the ST7 in reset.

The V<sub>IT</sub> reference value for a voltage drop is lower than the V<sub>IT</sub> reference value for power-on in order to avoid a parasitic reset when the MCU starts running and sinks current on the supply (hysteresis).

The LVD Reset circuitry generates a reset when  $V_{DD}$  is below:

- $V_{IT+}$  when  $V_{DD}$  is rising

- $-V_{IT}$  when  $V_{DD}$  is falling

- The LVD function is illustrated in Figure 16.

The voltage threshold can be configured by option byte to be low, medium or high.

Provided the minimum  $V_{DD}$  value (guaranteed for the oscillator frequency) is above  $V_{IT-}$ , the MCU can only be in two modes:

Figure 16. Low Voltage Detector vs Reset

- under full software control

- in static safe reset

In these conditions, secure operation is always ensured for the application without the need for external reset hardware.

During a Low Voltage Detector Reset, the RESET pin is held low, thus permitting the MCU to reset other devices.

#### Notes:

The LVD allows the device to be used without any external RESET circuitry.

If the medium or low thresholds are selected, the detection may occur outside the specified operating voltage range. Below 3.8V, device operation is not guaranteed.

The LVD is an optional function which can be selected by option byte.

It is recommended to make sure that the  $V_{DD}$  supply voltage rises monotonously when the device is exiting from Reset, to ensure the application functions properly.

**/رک**ا

## INTERRUPTS (Cont'd)

## Table 8. Interrupt Mapping

| N° | Source<br>Block | Description                               | Register<br>Label | Priority<br>Order | Exit<br>from<br>HALT/<br>ACTIVE<br>HALT | Address<br>Vector |

|----|-----------------|-------------------------------------------|-------------------|-------------------|-----------------------------------------|-------------------|

|    | RESET           | Reset                                     | N/A               |                   | yes                                     | FFFEh-FFFFh       |

|    | TRAP            | Software interrupt                        |                   |                   | no                                      | FFFCh-FFFDh       |

| 0  | TLI             | External top level interrupt              | EICR              |                   | yes                                     | FFFAh-FFFBh       |

| 1  | MCC/RTC         | Main clock controller time base interrupt | MCCSR             | Higher            | yes                                     | FFF8h-FFF9h       |

| 2  | ei0             | External interrupt port A30               |                   | Priority          | yes                                     | FFF6h-FFF7h       |

| 3  | ei1             | External interrupt port F20               | N/A               |                   | yes                                     | FFF4h-FFF5h       |

| 4  | ei2             | External interrupt port B30               | IN/A              |                   | yes                                     | FFF2h-FFF3h       |

| 5  | ei3             | External interrupt port B74               |                   |                   | yes                                     | FFF0h-FFF1h       |

| 6  |                 | Not used                                  |                   |                   |                                         | FFEEh-FFEFh       |

| 7  | SPI             | SPI peripheral interrupts                 | SPICSR            |                   | yes <sup>1</sup>                        | FFECh-FFEDh       |

| 8  | TIMER A         | TIMER A peripheral interrupts             | TASR              | •                 | no                                      | FFEAh-FFEBh       |

| 9  | TIMER B         | TIMER B peripheral interrupts             | TBSR              |                   | no                                      | FFE8h-FFE9h       |

| 10 | SCI             | SCI Peripheral interrupts                 | SCISR             | Lower             | no                                      | FFE6h-FFE7h       |

| 11 | AVD             | Auxiliary Voltage detector interrupt      | SICSR             | Priority          | no                                      | FFE4h-FFE5h       |

| 12 | I2C             | I2C Peripheral interrupts                 | (see periph)      |                   | no                                      | FFE2h-FFE3h       |

| 13 | PWM ART         | PWM ART interrupt                         | ARTCSR            |                   | yes <sup>2</sup>                        | FFE0h-FFE1h       |

## Notes:

- 1. Exit from HALT possible when SPI is in slave mode.

- 2. Exit from HALT possible when PWM ART is in external clock mode.

## **7.6 EXTERNAL INTERRUPTS**

#### 7.6.1 I/O Port Interrupt Sensitivity

The external interrupt sensitivity is controlled by the IPA, IPB and ISxx bits of the EICR register (Figure 23). This control allows to have up to 4 fully independent external interrupt source sensitivities.

Each external interrupt source can be generated on four (or five) different events on the pin:

- Falling edge

- Rising edge

- Falling and rising edge

- Falling edge and low level

- Rising edge and high level (only for ei0 and ei2)

To guarantee correct functionality, the sensitivity bits in the EICR register can be modified only when the I1 and I0 bits of the CC register are both set to 1 (level 3). This means that interrupts must be disabled before changing sensitivity.

The pending interrupts are cleared by writing a different value in the ISx[1:0], IPA or IPB bits of the EICR.

57

## POWER SAVING MODES (Cont'd)

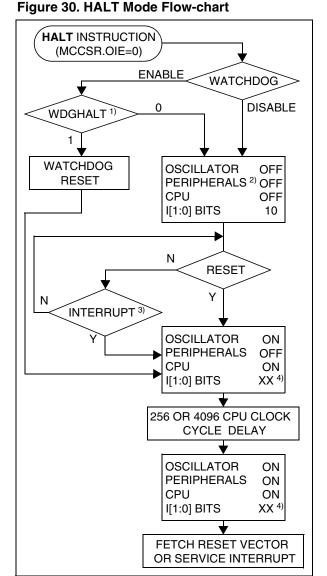

#### 8.4.2 HALT MODE

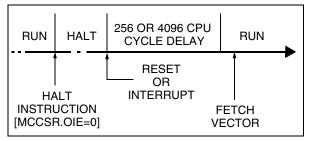

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see section 10.2 on page 57 for more details on the MCCSR register).

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 8, "Interrupt Mapping," on page 37) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 30).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b'to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see section 14.1 on page 174 for more details).

| Figure 2 | 9. HALT | Timing | Overview |

|----------|---------|--------|----------|

|----------|---------|--------|----------|

#### Notes:

1. WDGHALT is an option bit. See option byte section for more details.

2. Peripheral clocked with an external clock source can still be active.

3. Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 37 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

#### 44/187

## **ON-CHIP PERIPHERALS** (Cont'd)

<u>ل</u>رک

#### **Output compare and Time base interrupt**

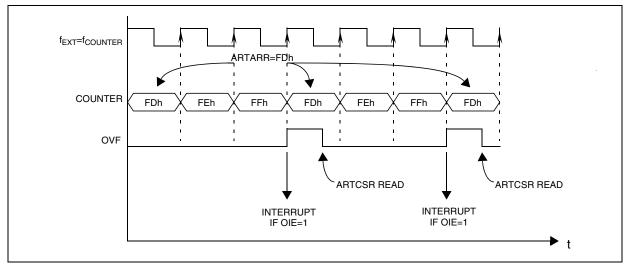

On overflow, the OVF flag of the ARTCSR register is set and an overflow interrupt request is generated if the overflow interrupt enable bit, OIE, in the ARTCSR register, is set. The OVF flag must be reset by the user software. This interrupt can be used as a time base in the application.

#### External clock and event detector mode

Using the  $f_{EXT}$  external prescaler input clock, the auto-reload timer can be used as an external clock event detector. In this mode, the ARTARR register is used to select the  $n_{EVENT}$  number of events to be counted before setting the OVF flag.

## $n_{EVENT} = 256 - ARTARR$

**Caution:** The external clock function is not available in HALT mode. If HALT mode is used in the application, prior to executing the HALT instruction, the counter must be disabled by clearing the TCE bit in the ARTCSR register to avoid spurious counter increments.

Figure 41. External Event Detector Example (3 counts)

#### 16-BIT TIMER (Cont'd)

#### 10.4.3.4 Output Compare

In this section, the index, *i*, may be 1 or 2 because there are two output compare functions in the 16-bit timer.

This function can be used to control an output waveform or indicate when a period of time has elapsed.

When a match is found between the Output Compare register and the free running counter, the output compare function:

- Assigns pins with a programmable value if the OC*i*E bit is set

- Sets a flag in the status register

- Generates an interrupt if enabled

Two 16-bit registers Output Compare Register 1 (OC1R) and Output Compare Register 2 (OC2R) contain the value to be compared to the counter register each timer clock cycle.

|               | MS Byte        | LS Byte        |

|---------------|----------------|----------------|

| OC <i>i</i> R | OC <i>i</i> HR | OC <i>i</i> LR |

These registers are readable and writable and are not affected by the timer hardware. A reset event changes the OC*i*R value to 8000h.

Timing resolution is one count of the free running counter:  $(f_{CPU/CC[1:0]})$ .

#### **Procedure:**

To use the output compare function, select the following in the CR2 register:

- Set the OC*i*E bit if an output is needed then the OCMP*i* pin is dedicated to the output compare *i* signal.

- Select the timer clock (CC[1:0]) (see Table 1).

And select the following in the CR1 register:

- Select the OLVL*i* bit to applied to the OCMP*i* pins after the match occurs.

- Set the OCIE bit to generate an interrupt if it is needed.

When a match is found between OC*i*R register and CR register:

OCF*i* bit is set.

- The OCMP*i* pin takes OLVL*i* bit value (OCMP*i* pin latch is forced low during reset).

- A timer interrupt is generated if the OCIE bit is set in the CR1 register and the I bit is cleared in the CC register (CC).

The OC*i*R register value required for a specific timing application can be calculated using the following formula:

$$\Delta \text{ OC} i \text{R} = \frac{\Delta t * f_{\text{CPU}}}{\text{PRESC}}$$

Where:

$\Delta t$  = Output compare period (in seconds)

$f_{CPU} = CPU \operatorname{clock} \operatorname{frequency} (\operatorname{in} \operatorname{hertz})$

PRESC = Timer prescaler factor (2, 4 or 8 depending on CC[1:0] bits, see Table 1)

If the timer clock is an external clock, the formula is:

$$\Delta OC R = \Delta t * f_{EXT}$$

Where:

$\Delta t$  = Output compare period (in seconds)

f<sub>EXT</sub> = External timer clock frequency (in hertz)

Clearing the output compare interrupt request (that is, clearing the OCF*i* bit) is done by:

1. Reading the SR register while the OCF*i* bit is set.

2. An access (read or write) to the OCiLR register.

The following procedure is recommended to prevent the OCFi bit from being set between the time it is read and the write to the OCiR register:

- Write to the OC*i*HR register (further compares are inhibited).

- Read the SR register (first step of the clearance of the OCF*i* bit, which may be already set).

- Write to the OC*i*LR register (enables the output compare function and clears the OCF*i* bit).

57

#### 16-BIT TIMER (Cont'd)

#### **10.4.7 Register Description**

Each Timer is associated with three control and status registers, and with six pairs of data registers (16-bit values) relating to the two input captures, the two output compares, the counter and the alternate counter.

#### **CONTROL REGISTER 1 (CR1)**

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |      |       |       |       |       | 0     |

|------|------|------|-------|-------|-------|-------|-------|

| ICIE | OCIE | TOIE | FOLV2 | FOLV1 | OLVL2 | IEDG1 | OLVL1 |

Bit 7 = **ICIE** *Input Capture Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the ICF1 or ICF2 bit of the SR register is set.

Bit 6 = **OCIE** *Output Compare Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is generated whenever the OCF1 or OCF2 bit of the SR register is set.

## Bit 5 = **TOIE** *Timer Overflow Interrupt Enable.* 0: Interrupt is inhibited.

1: A timer interrupt is enabled whenever the TOF bit of the SR register is set.

#### Bit 4 = FOLV2 Forced Output Compare 2.

- This bit is set and cleared by software.

- 0: No effect on the OCMP2 pin.

- 1: Forces the OLVL2 bit to be copied to the OCMP2 pin, if the OC2E bit is set and even if there is no successful comparison.

Bit 3 = FOLV1 Forced Output Compare 1.

- This bit is set and cleared by software.

- 0: No effect on the OCMP1 pin.

- 1: Forces OLVL1 to be copied to the OCMP1 pin, if the OC1E bit is set and even if there is no successful comparison.

#### Bit 2 = OLVL2 Output Level 2.

This bit is copied to the OCMP2 pin whenever a successful comparison occurs with the OC2R register and OCxE is set in the CR2 register. This value is copied to the OCMP1 pin in One Pulse mode and Pulse Width Modulation mode.

## Bit 1 = IEDG1 Input Edge 1.

This bit determines which type of level transition on the ICAP1 pin will trigger the capture.0: A falling edge triggers the capture.1: A rising edge triggers the capture.

#### Bit 0 = OLVL1 Output Level 1.

The OLVL1 bit is copied to the OCMP1 pin whenever a successful comparison occurs with the OC1R register and the OC1E bit is set in the CR2 register.

## 16-BIT TIMER (Cont'd) **INPUT CAPTURE 1 HIGH REGISTER (IC1HR)**

Read Only

**Reset Value: Undefined**

This is an 8-bit read only register that contains the high part of the counter value (transferred by the input capture 1 event).

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **INPUT CAPTURE 1 LOW REGISTER (IC1LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the input capture 1 event).

7

<u>ل</u>رک

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### **OUTPUT COMPARE 1 HIGH REGISTER** (OC1HR)

#### Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

#### OUTPUT COMPARE 1 LOW REGISTER (OC1LR)

Read/Write

\_

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 1   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

85/187

^

#### 16-BIT TIMER (Cont'd)

# OUTPUT COMPARE 2 HIGH REGISTER (OC2HR)

Read/Write

Reset Value: 1000 0000 (80h)

This is an 8-bit register that contains the high part of the value to be compared to the CHR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# OUTPUT COMPARE 2 LOW REGISTER (OC2LR)

#### Read/Write

Reset Value: 0000 0000 (00h)

This is an 8-bit register that contains the low part of the value to be compared to the CLR register.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

#### **COUNTER HIGH REGISTER (CHR)**

Read Only

7

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **COUNTER LOW REGISTER (CLR)**

#### Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after accessing the CSR register clears the TOF bit.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## ALTERNATE COUNTER HIGH REGISTER (ACHR)

Read Only

Reset Value: 1111 1111 (FFh)

This is an 8-bit register that contains the high part of the counter value.

| 7   |  |  |  | 0   |  |

|-----|--|--|--|-----|--|

| MSB |  |  |  | LSB |  |

# ALTERNATE COUNTER LOW REGISTER (ACLR)

Read Only

Reset Value: 1111 1100 (FCh)

This is an 8-bit register that contains the low part of the counter value. A write to this register resets the counter. An access to this register after an access to CSR register does not clear the TOF bit in the CSR register.

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 HIGH REGISTER (IC2HR)**

Read Only

Λ

Reset Value: Undefined

This is an 8-bit read only register that contains the high part of the counter value (transferred by the Input Capture 2 event).

| 7   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## **INPUT CAPTURE 2 LOW REGISTER (IC2LR)**

Read Only

Reset Value: Undefined

This is an 8-bit read only register that contains the low part of the counter value (transferred by the Input Capture 2 event).

| 1   |  |  |  | 0   |

|-----|--|--|--|-----|

| MSB |  |  |  | LSB |

## SERIAL PERIPHERAL INTERFACE (Cont'd)

#### 10.5.3.2 Slave Select Management

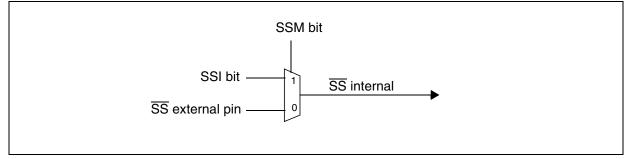

As an alternative to using the  $\overline{SS}$  pin to control the Slave Select signal, the application can choose to manage the Slave Select signal by software. This is configured by the SSM bit in the SPICSR register (see Figure 57)

In software management, the external SS pin is free for other application uses and the internal SS signal level is driven by writing to the SSI bit in the SPICSR register.

#### In Master mode:

- SS internal must be held high continuously

#### In Slave Mode:

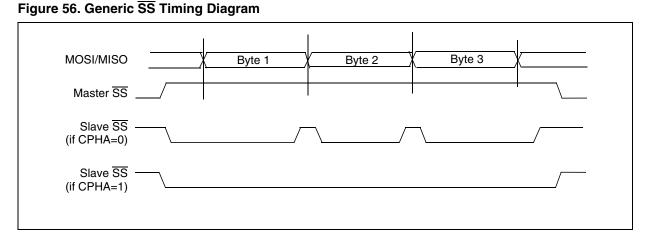

There are two cases depending on the data/clock timing relationship (see Figure 56):

If CPHA=1 (data latched on 2nd clock edge):

SS internal must be held low during the entire transmission. This implies that in single slave applications the SS pin either can be tied to V<sub>SS</sub>, or made free for standard I/O by managing the SS function by software (SSM= 1 and SSI=0 in the in the SPICSR register)

If CPHA=0 (data latched on 1st clock edge):

$-\overline{SS}$  internal must be held low during byte transmission and pulled high between each byte to allow the slave to write to the shift register. If SS is not pulled high, a Write Collision error will occur when the slave writes to the shift register (see Section 10.5.5.3).

Figure 57. Hardware/Software Slave Select Management

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

## **Framing Error**

A framing error is detected when:

- The stop bit is not recognized on reception at the expected time, following either a de-synchronization or excessive noise.

- A break is received.

- When the framing error is detected:

- the FE bit is set by hardware

- Data is transferred from the Shift register to the SCIDR register.

- No interrupt is generated. However this bit rises at the same time as the RDRF bit which itself generates an interrupt.

The FE bit is reset by a SCISR register read operation followed by a SCIDR register read operation.

#### 10.6.4.4 Conventional Baud Rate Generation

The baud rate for the receiver and transmitter (Rx and Tx) are set independently and calculated as follows:

$$Tx = \frac{f_{CPU}}{(16*PR)*TR} \qquad Rx = \frac{f_{CPU}}{(16*PR)*RR}$$

with:

PR = 1, 3, 4 or 13 (see SCP[1:0] bits)

TR = 1, 2, 4, 8, 16, 32, 64,128

(see SCT[2:0] bits)

RR = 1, 2, 4, 8, 16, 32, 64,128

(see SCR[2:0] bits)

All these bits are in the SCIBRR register.

**Example:** If  $f_{CPU}$  is 8 MHz (normal mode) and if PR = 13 and TR = RR = 1, the transmit and receive baud rates are 38400 baud.

**Note:** The baud rate registers MUST NOT be changed while the transmitter or the receiver is enabled.

#### 10.6.4.5 Extended Baud Rate Generation

The extended prescaler option gives a very fine tuning on the baud rate, using a 255 value prescaler, whereas the conventional Baud Rate Generator retains industry standard software compatibility.

The extended baud rate generator block diagram is described in the Figure 3.

The output clock rate sent to the transmitter or to the receiver is the output from the 16 divider divided by a factor ranging from 1 to 255 set in the SCI-ERPR or the SCIETPR register. **Note:** the extended prescaler is activated by setting the SCIETPR or SCIERPR register to a value other than zero. The baud rates are calculated as follows:

$$Tx = \frac{f_{CPU}}{16 \cdot ETPR^*(PR^*TR)} \quad Rx = \frac{f_{CPU}}{16 \cdot ERPR^*(PR^*RR)}$$

with:

ETPR = 1,..,255 (see SCIETPR register)

ERPR = 1,.. 255 (see SCIERPR register)

#### 10.6.4.6 Receiver Muting and Wake-up Feature

In multiprocessor configurations it is often desirable that only the intended message recipient should actively receive the full message contents, thus reducing redundant SCI service overhead for all non addressed receivers.

The non addressed devices may be placed in sleep mode by means of the muting function.

Setting the RWU bit by software puts the SCI in sleep mode:

All the reception status bits can not be set.

All the receive interrupts are inhibited.

A muted receiver may be awakened by one of the following two ways:

by Idle Line detection if the WAKE bit is reset,

- by Address Mark detection if the WAKE bit is set.

Receiver wakes-up by Idle Line detection when the Receive line has recognized an Idle Frame. Then the RWU bit is reset by hardware but the IDLE bit is not set.

Receiver wakes-up by Address Mark detection when it received a "1" as the most significant bit of a word, thus indicating that the message is an address. The reception of this particular word wakes up the receiver, resets the RWU bit and sets the RDRF bit, which allows the receiver to receive this word normally and to use it as an address word.

**CAUTION:** In Mute mode, do not write to the SCICR2 register. If the SCI is in Mute mode during the read operation (RWU = 1) and a address mark wake up event occurs (RWU is reset) before the write operation, the RWU bit is set again by this write operation. Consequently the address byte is lost and the SCI is not woken up from Mute mode.

57

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.6.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 1.

#### Table 21. Frame Formats

| M bit | PCE bit | SCI frame                  |  |  |

|-------|---------|----------------------------|--|--|

| 0     | 0       | SB   8 bit data   STB      |  |  |

| 0     | 1       | SB   7-bit data   PB   STB |  |  |

| 1     | 0       | SB   9-bit data   STB      |  |  |

| 1 1   |         | SB   8-bit data PB   STB   |  |  |

Legend: SB = Start Bit, STB = Stop Bit, PB = Parity Bit

Note: In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

Even parity: the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 0 if even parity is selected (PS bit = 0).

Odd parity: the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Example: data = 00110101; 4 bits set => parity bit is 1 if odd parity is selected (PS bit = 1).

Transmission mode: If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

Reception mode: If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS = 0) or an odd number of "1s" if odd parity is selected (PS = 1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

#### 10.6.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: If the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value is "1", but the Noise Flag bit is set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

Note: The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 Kbaud (bit length is 64µs), then the 8th, 9th and 10th samples are at 28µs, 32µs and 36µs respectively (the first sample starting ideally at Ous). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

## ST72321BRx, ST72321BARx ST72321BJx, ST72321BKx

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) 10.6.5 Low Power Modes

| Mode | Description                                                                        |

|------|------------------------------------------------------------------------------------|

|      | No effect on SCI.                                                                  |

| WAIT | SCI interrupts cause the device to exit from Wait mode.                            |

|      | SCI registers are frozen.                                                          |

| HALT | In Halt mode, the SCI stops transmitting/re-<br>ceiving until Halt mode is exited. |

#### 10.6.6 Interrupts

The SCI interrupt events are connected to the same interrupt vector.

These events generate an interrupt if the corresponding Enable Control Bit is set and the interrupt mask in the CC register is reset (RIM instruction).

| Interrupt Event                 | Event<br>Flag | Enable<br>Control<br>Bit | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|---------------------------------|---------------|--------------------------|----------------------|----------------------|

| Transmit Data Register<br>Empty | TDRE          | TIE                      | Yes                  | No                   |

| Transmission Com-<br>plete      | тс            | TCIE                     | Yes                  | No                   |

| Received Data Ready to be Read  |               |                          | Yes                  | No                   |

| Overrun Error Detect-<br>ed     | OR            | RIE                      | Yes                  | No                   |

| Idle Line Detected              | IDLE          | ILIE                     | Yes                  | No                   |

| Parity Error                    | PE            | PIE                      | Yes                  | No                   |

## I<sup>2</sup>C BUS INTERFACE (Cont'd) I<sup>2</sup>C OWN ADDRESS REGISTER (OAR1)

Read / Write Reset Value: 0000 0000 (00h)

| 7    |      |      |      |      |      |      | 0    |

|------|------|------|------|------|------|------|------|

| ADD7 | ADD6 | ADD5 | ADD4 | ADD3 | ADD2 | ADD1 | ADD0 |

#### 7-bit Addressing Mode

Bit 7:1 = ADD[7:1] Interface address.

These bits define the  $l^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

Bit 0 = **ADD0** Address direction bit.

This bit is don't care, the interface acknowledges either 0 or 1. It is not cleared when the interface is disabled (PE=0).

Note: Address 01h is always ignored.

#### **10-bit Addressing Mode**

Bit 7:0 = **ADD**[7:0] Interface address. These are the least significant bits of the  $I^2C$  bus address of the interface. They are not cleared when the interface is disabled (PE=0).

## I<sup>2</sup>C OWN ADDRESS REGISTER (OAR2)

#### Read / Write

Reset Value: 0100 0000 (40h)

| 7   |     |   |   |   |      |      | 0 |

|-----|-----|---|---|---|------|------|---|

| FR1 | FR0 | 0 | 0 | 0 | ADD9 | ADD8 | 0 |

#### Bit 7:6 = **FR[1:0]** Frequency bits.

These bits are set by software only when the interface is disabled (PE=0). To configure the interface to  $I^2C$  specified delays select the value corresponding to the microcontroller frequency  $F_{CPU}$ .

| f <sub>CPU</sub> | FR1 | FR0 |

|------------------|-----|-----|

| < 6 MHz          | 0   | 0   |

| 6 to 8 MHz       | 0   | 1   |

Bit 5:3 = Reserved

#### Bit 2:1 = ADD[9:8] Interface address.

These are the most significant bits of the  $I^2C$  bus address of the interface (10-bit mode only). They are not cleared when the interface is disabled (PE=0).

## Bit 0 = Reserved.

## **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                    | ymbol Ratings                                                                             |                                | Unit    |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------|---------|--|

| V <sub>DD</sub> - V <sub>SS</sub>         | V <sub>DD</sub> - V <sub>SS</sub> Supply voltage                                          |                                |         |  |

| V <sub>PP</sub> - V <sub>SS</sub>         | Programming Voltage                                                                       | 13                             | V       |  |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>    | Input Voltage on true open drain pin                                                      | V <sub>SS</sub> -0.3 to 6.5    | v       |  |

| VIN                                       | Input voltage on any other pin                                                            | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 |         |  |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ | $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $ Variations between different digital power pins |                                | mV      |  |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I    | IV <sub>SSA</sub> - V <sub>SSx</sub> I Variations between digital and analog ground pins  |                                | IIIV    |  |

| V <sub>ESD(HBM)</sub>                     | Electro-static discharge voltage (Human Body Model)                                       | soo soction 1273 on n          | 200 154 |  |

| V <sub>ESD(MM)</sub>                      | Electro-static discharge voltage (Machine Model)                                          | see section 12.7.3 on page 154 |         |  |

#### 12.2.2 Current Characteristics

| Symbol                               | Ratings                                                                                 | Maximum value | Unit |

|--------------------------------------|-----------------------------------------------------------------------------------------|---------------|------|

| I <sub>VDD</sub>                     | I <sub>VDD</sub> Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup>  |               | mA   |

| I <sub>VSS</sub>                     | I <sub>VSS</sub> Total current out of V <sub>SS</sub> ground lines (sink) <sup>3)</sup> |               |      |

|                                      | Output current sunk by any standard I/O and control pin                                 | 25            |      |

| I <sub>IO</sub>                      | Output current sunk by any high sink I/O pin                                            | 50            |      |

|                                      | Output current source by any I/Os and control pin                                       | - 25          |      |

|                                      | Injected current on V <sub>PP</sub> pin                                                 | ± 5           |      |

|                                      | Injected current on RESET pin                                                           | ± 5           | mA   |

| I <sub>INJ(PIN)</sub> 2) & 4)        | Injected current on OSC1 and OSC2 pins                                                  | ± 5           |      |

|                                      | Injected current on PB0 (Flash devices only)                                            | + 5           |      |

|                                      | Injected current on any other pin 5) & 6)                                               | ± 5           | 1    |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup> | Total injected current (sum of all I/O and control pins) <sup>5)</sup>                  | ± 25          |      |

#### Notes:

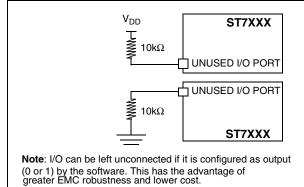

1. Directly connecting the  $\overrightarrow{\text{RESET}}$  and I/O pins to  $V_{\text{DD}}$  or  $V_{\text{SS}}$  could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7k $\Omega$  for RESET, 10k $\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected.

3. All power  $(V_{DD})$  and ground  $(V_{SS})$  lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 169. For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum mum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

**لركم**

## **12.8 I/O PORT PIN CHARACTERISTICS**

#### 12.8.1 General Characteristics

Subject to general operating conditions for  $V_{DD}$ ,  $f_{OSC}$ , and  $T_A$  unless otherwise specified.

| Symbol                              | Parameter                                                | Conc                                                               | litions               | Min                             | Тур | Max                             | Unit             |

|-------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------|-----------------------|---------------------------------|-----|---------------------------------|------------------|

| V <sub>IL</sub>                     | Input low level voltage 1)                               |                                                                    |                       |                                 |     | $0.3 \mathrm{xV}_{\mathrm{DD}}$ |                  |

| V <sub>IH</sub>                     | Input high level voltage 1)                              | CMOS ports                                                         |                       | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                                 | V                |

| V <sub>hys</sub>                    | Schmitt trigger voltage hysteresis 2)                    | •                                                                  |                       |                                 | 0.7 |                                 |                  |

| I <sub>INJ(PIN)</sub> <sup>3)</sup> | Injected Current on PC6 (Flash de-<br>vices only)        |                                                                    |                       | 0                               |     | +4                              |                  |

|                                     | Injected Current on an I/O pin V <sub>DD</sub> =5V       |                                                                    |                       |                                 |     | ± 4                             | mA               |

| $\Sigma I_{\rm INJ(PIN)}^{3)}$      | Total injected current (sum of all I/O and control pins) |                                                                    |                       |                                 |     | ± 25                            |                  |

| ١L                                  | Input leakage current                                    | $V_{SS} \leq V_{IN} \leq V_{IN}$                                   | DD                    |                                 |     | ±1                              |                  |

| ا <sub>S</sub>                      | Static current consumption                               | Floating inpu                                                      | ut mode <sup>4)</sup> |                                 | 400 |                                 | μA               |

| R <sub>PU</sub>                     | Weak pull-up equivalent resistor 5)                      | V <sub>IN</sub> =V <sub>SS</sub>                                   | V <sub>DD</sub> =5V   | 50                              | 120 | 250                             | kΩ               |

| C <sub>IO</sub>                     | I/O pin capacitance                                      |                                                                    |                       |                                 | 5   |                                 | pF               |

| t <sub>f(IO)out</sub>               | Output high to low level fall time <sup>1)</sup>         | put high to low level fall time <sup>1)</sup> C <sub>L</sub> =50pF |                       |                                 | 25  |                                 | ns               |

| t <sub>r(IO)out</sub>               | Output low to high level rise time <sup>1)</sup>         | Between 10% and 90%                                                |                       |                                 | 25  |                                 | 115              |

| t <sub>w(IT)in</sub>                | External interrupt pulse time 6)                         |                                                                    |                       | 1                               |     |                                 | t <sub>CPU</sub> |

Figure 78. Unused I/Os configured as input

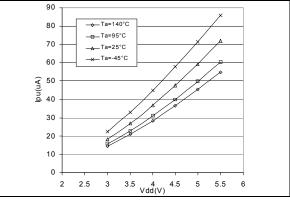

## Figure 79. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

3. When the current limitation is not possible, the V<sub>IN</sub> maximum must be respected, otherwise refer to  $I_{INJ(PIN)}$  specification. A positive injection is induced by  $V_{IN}$ >V<sub>DD</sub> while a negative injection is induced by  $V_{IN}$ <V<sub>SS</sub>. Refer to section 12.2.2 on page 139 for more details.

4. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example and leaving the I/O unconnected on the board or an external pull-up or pull-down resistor (see Figure 78). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

5. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding I<sub>PU</sub> current characteristics described in Figure 79).

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

<u>ل</u>رک

## I/O PORT PIN CHARACTERISTICS (Cont'd)

## 12.8.2 Output Driving Current

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol                        | Parameter                                                                                                                       | Conditions          |                                                                     | Min                  | Max | Unit |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------------------------------------------------------|----------------------|-----|------|

|                               | Output low level voltage for a standard I/O pin                                                                                 |                     | I <sub>IO</sub> =+5mA                                               |                      | 1.2 |      |

| 1)                            | when 8 pins are sunk at same time (see Figure 80)                                                                               |                     | I <sub>IO</sub> =+2mA                                               |                      | 0.5 |      |

| V <sub>OL</sub> <sup>1)</sup> | Output low level voltage for a high sink I/O pin                                                                                |                     | I <sub>IO</sub> =+20mA, T <sub>A</sub> ≤85°C                        |                      | 1.3 |      |

|                               | when 4 pins are sunk at same time                                                                                               | / <sub>DD</sub> =5V | T <sub>A</sub> ≥85°C                                                |                      | 1.5 | V    |

|                               | (see Figure 81 and Figure 83)                                                                                                   |                     | I <sub>IO</sub> =+8mA                                               |                      | 0.6 |      |

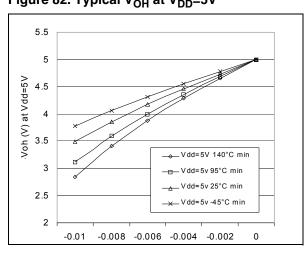

| V <sub>OH</sub> <sup>2)</sup> | <sup>2)</sup> Output high level voltage for an I/O pin<br>when 4 pins are sourced at same time<br>(see Figure 82 and Figure 85) |                     | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°C<br>T <sub>A</sub> ≥85°C |                      |     |      |

| - 01                          |                                                                                                                                 |                     | I <sub>IO</sub> =-2mA                                               | V <sub>DD</sub> -0.7 |     |      |

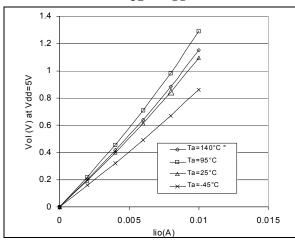

Figure 80. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (standard)

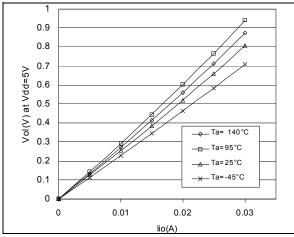

Figure 81. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink)

Figure 82. Typical V<sub>OH</sub> at V<sub>DD</sub>=5V

#### Notes:

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins do not have V<sub>OH</sub>.

## CONTROL PIN CHARACTERISTICS (Cont'd)

## 12.9.2 ICCSEL/V<sub>PP</sub> Pin

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{CPU}},$  and  $T_{\text{A}}$  unless otherwise specified.

| Symbol          | Parameter                             | Conditions                       | Min                             | Max <sup>1</sup>                | Unit |

|-----------------|---------------------------------------|----------------------------------|---------------------------------|---------------------------------|------|

| V <sub>IL</sub> | Input low level voltage <sup>1)</sup> |                                  | V <sub>SS</sub>                 | $0.3 \mathrm{xV}_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub> | Input high level voltage 1)           |                                  | $0.7 \mathrm{xV}_{\mathrm{DD}}$ | V <sub>DD</sub>                 |      |

| ١L              | Input leakage current                 | V <sub>IN</sub> =V <sub>SS</sub> |                                 | ±1                              | μA   |

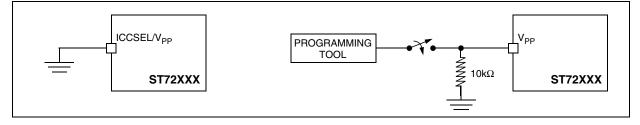

## Figure 88. Two typical Applications with ICCSEL/V\_{PP} Pin $^{\rm 2)}$

#### Notes:

1. Data based on design simulation and/or technology characteristics, not tested in production.

2. When ICC mode is not required by the application ICCSEL/V<sub>PP</sub> pin must be tied to  $V_{SS}$ .

## **12.10 TIMER PERIPHERAL CHARACTERISTICS**

Subject to general operating conditions for  $V_{\text{DD}},\,f_{\text{OSC}},$  and  $T_{\text{A}}$  unless otherwise specified.

Refer to I/O port characteristics for more details on the input/output alternate function characteristics (output compare, input capture, external clock, PWM output...).

## 12.10.1 8-Bit PWM-ART Auto-Reload Timer

| Symbol                        | Parameter                                 | Conditions                      | Min | Тур | Max                 | Unit             |

|-------------------------------|-------------------------------------------|---------------------------------|-----|-----|---------------------|------------------|

| tros(RMM) PWM resolution time |                                           |                                 | 1   |     |                     | t <sub>CPU</sub> |

| <sup>t</sup> res(PWM)         | t <sub>res(PWM)</sub> PWW resolution time | f <sub>CPU</sub> =8MHz          | 125 |     |                     | ns               |

| f <sub>EXT</sub>              | ART external clock frequency              |                                 | 0   |     | f <sub>CPU</sub> /2 | MHz              |

| f <sub>PWM</sub>              | PWM repetition rate                       |                                 | 0   |     | f <sub>CPU</sub> /2 |                  |

| Res <sub>PWM</sub>            | PWM resolution                            |                                 |     |     | 8                   | bit              |

| V <sub>OS</sub>               | PWM/DAC output step voltage               | V <sub>DD</sub> =5V, Res=8-bits |     | 20  |                     | mV               |

## 12.10.2 16-Bit Timer

| Symbol                                    | Parameter                      | Conditions             | Min | Тур | Max                 | Unit             |

|-------------------------------------------|--------------------------------|------------------------|-----|-----|---------------------|------------------|

| t <sub>w(ICAP)in</sub>                    | Input capture pulse time       |                        | 1   |     |                     | t <sub>CPU</sub> |

| t <sub>res(PWM)</sub> PWM resolution time |                                | 2                      |     |     | t <sub>CPU</sub>    |                  |

|                                           | r www.resolution.time          | f <sub>CPU</sub> =8MHz | 250 |     |                     | ns               |

| f <sub>EXT</sub>                          | Timer external clock frequency |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| f <sub>PWM</sub>                          | PWM repetition rate            |                        | 0   |     | f <sub>CPU</sub> /4 | MHz              |

| Res <sub>PWM</sub>                        | PWM resolution                 |                        |     |     | 16                  | bit              |

## DEVICE CONFIGURATION AND ORDERING INFORMATION (Cont'd)

#### Table 30. Suggested List of Socket Types

| Device        | Socket (supplied with ST7MDT20M-<br>EMU3) | Emulator Adapter (supplied with<br>ST7MDT20M-EMU3) |

|---------------|-------------------------------------------|----------------------------------------------------|

| LQFP64 14 x14 | CAB 3303262                               | CAB 3303351                                        |

| LQFP64 10 x10 | YAMAICHI IC149-064-*75-*5                 | YAMAICHI ICP-064-6                                 |

| LQFP44 10 X10 | YAMAICHI IC149-044-*52-*5                 | YAMAICHI ICP-044-5                                 |

| LQFP32 7 X 7  | IRONWOOD SF-QFE32SA-L-01                  | IRONWOOD SK-UGA06/32A-01                           |

## 14.3.4 Socket and Emulator Adapter Information

For information on the type of socket that is supplied with the emulator, refer to the suggested list of sockets in Table 30.

**Note:** Before designing the board layout, it is recommended to check the overall dimensions of the socket as they may be greater than the dimensions of the device.

For footprint and other mechanical information about these sockets and adapters, refer to the manufacturer's datasheet.

#### **Related Documentation**

AN 978: ST7 Visual Develop Software Key Debugging Features

AN 1938: ST7 Visual Develop for ST7 Cosmic C toolset users

AN 1940: ST7 Visual Develop for ST7 Assembler Linker toolset users