Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 64 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f610-e-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Table of Contents**

| 1.0   | Device Overview                                                                                 | 9   |

|-------|-------------------------------------------------------------------------------------------------|-----|

| 2.0   | Memory Organization                                                                             | 13  |

| 3.0   | Oscillator Module                                                                               |     |

| 4.0   | I/O Ports                                                                                       | 33  |

| 5.0   | Timer0 Module                                                                                   |     |

| 6.0   | Timer1 Module with Gate Control                                                                 | 49  |

| 7.0   | Timer2 Module (PIC16F616/16HV616 only)                                                          | 55  |

| 8.0   | Comparator Module                                                                               |     |

| 9.0   | Analog-to-Digital Converter (ADC) Module (PIC16F616/16HV616 only)                               | 73  |

| 10.0  | Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC16F616/16HV616 Only) | 85  |

| 11.0  | Voltage Regulator                                                                               |     |

|       | Special Features of the CPU                                                                     |     |

| 13.0  | Instruction Set Summary                                                                         | 129 |

| 14.0  | Development Support                                                                             | 139 |

| 15.0  | Electrical Specifications                                                                       | 143 |

| 16.0  | DC and AC Characteristics Graphs and Tables                                                     | 173 |

|       | Packaging Information                                                                           |     |

|       | ndix A:Data Sheet Revision History                                                              |     |

| Appe  | ndix B: Migrating from other PIC <sup>®</sup> Devices                                           | 206 |

| Index | · · · · · · · · · · · · · · · · · · ·                                                           | 207 |

|       | Aicrochip Web Site                                                                              |     |

| Custo | omer Change Notification Service                                                                | 211 |

| Custo | omer Support                                                                                    | 211 |

| Read  | er Response                                                                                     | 212 |

| Produ | uct Identification System                                                                       | 213 |

| World | dwide Sales and Service                                                                         | 214 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

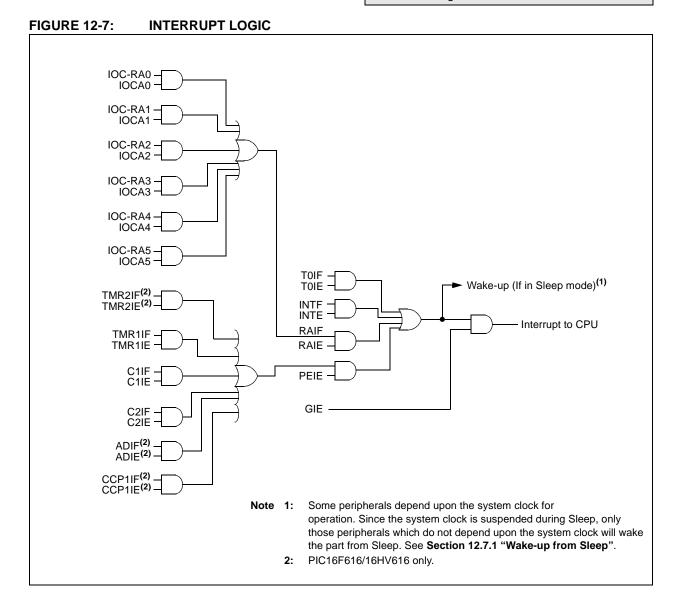

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the peripheral interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | R/W-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-------|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE  | C1IE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |       |       |     |                       | bit 0  |

| Legend:    |                 |                                                   |                               |                    |

|------------|-----------------|---------------------------------------------------|-------------------------------|--------------------|

| R = Read   | able bit        | W = Writable bit                                  | U = Unimplemented bit,        | read as '0'        |

| -n = Value | e at POR        | '1' = Bit is set                                  | '0' = Bit is cleared          | x = Bit is unknown |

|            |                 |                                                   |                               |                    |

| bit 7      | •               | mented: Read as '0'                               |                               |                    |

| bit 6      | ADIE: A/        | D Converter (ADC) Interrupt                       | Enable bit <sup>(1)</sup>     |                    |

|            |                 | les the ADC interrupt<br>bles the ADC interrupt   |                               |                    |

| bit 5      | CCP1IE:         | CCP1 Interrupt Enable bit <sup>(1)</sup>          |                               |                    |

|            |                 | les the CCP1 interrupt<br>bles the CCP1 interrupt |                               |                    |

| bit 4      | <b>C2IE:</b> Co | mparator C2 Interrupt Enabl                       | e bit                         |                    |

|            | 1 = Enab        | les the Comparator C2 interr                      | rupt                          |                    |

|            | 0 = Disat       | oles the Comparator C2 inter                      | rupt                          |                    |

| bit 3      | <b>C1IE:</b> Co | mparator C1 Interrupt Enabl                       | e bit                         |                    |

|            | 1 = Enab        | les the Comparator C1 interr                      | rupt                          |                    |

|            | 0 = Disat       | oles the Comparator C1 inter                      | rupt                          |                    |

| bit 2      | Unimple         | mented: Read as '0'                               |                               |                    |

| bit 1      | TMR2IE:         | Timer2 to PR2 Match Interru                       | upt Enable bit <sup>(1)</sup> |                    |

|            | 1 = Enab        | les the Timer2 to PR2 match                       | n interrupt                   |                    |

|            | 0 = Disat       | oles the Timer2 to PR2 matcl                      | h interrupt                   |                    |

| bit 0      | TMR1IE:         | Timer1 Overflow Interrupt E                       | nable bit                     |                    |

|            | 1 = Enab        | les the Timer1 overflow inter                     | rupt                          |                    |

|            | 0 = Disat       | oles the Timer1 overflow inte                     | rrupt                         |                    |

| Note 1:    | PIC16F616/16    | 6HV616 only. PIC16F610/16                         | HV610 unimplemented, read a   | as '0'.            |

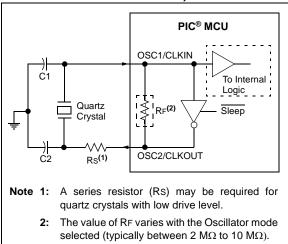

### 3.3.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

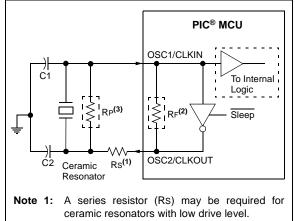

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 3-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- **2:** The value of RF varies with the Oscillator mode selected (typically between 2 MΩ to 10 MΩ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

### 6.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of TCY as determined by the Timer1 prescaler.

#### 6.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge.                    |

### 6.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

#### 6.4 Timer1 Oscillator

A low-power 32.768 kHz crystal oscillator is built-in between pins OSC1 (input) and OSC2 (output). The oscillator is enabled by setting the T1OSCEN control bit of the T1CON register. The oscillator will continue to run during Sleep.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is derived from the internal oscillator or when the oscillator is in the LP Oscillator mode. The user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 bits read as '0' and TRISA5 and TRISA4 bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

### 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

- Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

- Note: In asynchronous counter mode or when using the internal oscillator and T1ACS=1, Timer1 can not be used as a time base for the capture or compare modes of the ECCP module (for PIC16F616/HV616 only).

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

### 6.6 Timer1 Gate

Timer1 gate source is software configurable to be the T1G pin or the output of Comparator C2. This allows the device to directly time external events using T1G or analog events using Comparator C2. See the CM2CON1 register (Register 8-3) for selecting the Timer1 gate source. This feature can simplify the software for a Delta-Sigma A/D converter and many

#### **TABLE 8-2:** SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND **VOLTAGE REFERENCE MODULES**

| Name    | Bit 7  | Bit 6               | Bit 5                 | Bit 4  | Bit 3               | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|---------------------|-----------------------|--------|---------------------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ANSEL   | ANS7   | ANS6                | ANS5                  | ANS4   | ANS3 <sup>(1)</sup> | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | 1111 1111            | 1111 1111                       |

| CM1CON0 | C1ON   | C1OUT               | C1OE                  | C1POL  | C1SP                | C1R                 | C1CH1                 | C1CH0   | 0000 0000            | 0000 0000                       |

| CM2CON0 | C2ON   | C2OUT               | C2OE                  | C2POL  | C2SP                | C2R                 | C2CH1                 | C2CH0   | 0000 0000            | 0000 0000                       |

| CM2CON1 | MC10UT | MC2OUT              | _                     | T1ACS  | C1HYS               | C2HYS               | T1GSS                 | C2SYNC  | 00-0 0010            | 00-0 0010                       |

| INTCON  | GIE    | PEIE                | TOIE                  | INTE   | RAIE                | T0IF                | INTF                  | RAIF    | 0000 000x            | 0000 000x                       |

| PIE1    | —      | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE   | C1IE                | _                   | TMR2IE <sup>(1)</sup> | TMR1IE  | -000 0-00            | -000 0-00                       |

| PIR1    | —      | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF   | C1IF                | _                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -000 0-00            | -000 0-00                       |

| PORTA   | —      | -                   | RA5                   | RA4    | RA3                 | RA2                 | RA1                   | RA0     | x0 x000              | x0 x000                         |

| PORTC   | —      | -                   | RC5                   | RC4    | RC3                 | RC2                 | RC1                   | RC0     | xx 00xx              | uu 00uu                         |

| SRCON0  | SR1    | SR0                 | C1SEN                 | C2REN  | PULSS               | PULSR               | _                     | SRCLKEN | 0000 00-0            | 0000 00-0                       |

| SRCON1  | SRCS1  | SRCS0               | _                     | _      | _                   | _                   | _                     | _       | 00                   | 00                              |

| TRISA   | _      | _                   | TRISA5                | TRISA4 | TRISA3              | TRISA2              | TRISA1                | TRISA0  | 11 1111              | 11 1111                         |

| TRISC   |        |                     | TRISC5                | TRISC4 | TRISC3              | TRISC2              | TRISC1                | TRISC0  | 1111 1111            | 1111 1111                       |

| VRCON   | C1VREN | C2VREN              | VRR                   | FVREN  | VR3                 | VR2                 | VR1                   | VR0     | 0000 0000            | 0000 0000                       |

Legend:

x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

Note

1:

PIC16F616/16HV616 only.

| U-0              | R/W-0                                                                                                                                                                                                                                                        | R/W-0            | R/W-0 | U-0                | U-0                | U-0               | U-0 |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|--------------------|--------------------|-------------------|-----|--|--|

| _                | ADCS2                                                                                                                                                                                                                                                        | ADCS1            | ADCS0 | —                  | —                  | —                 | _   |  |  |

| bit 7            |                                                                                                                                                                                                                                                              |                  |       |                    |                    |                   | bit |  |  |

| Legend:          |                                                                                                                                                                                                                                                              |                  |       |                    |                    |                   |     |  |  |

| R = Readable bi  | t                                                                                                                                                                                                                                                            | W = Writable b   | it    | U = Unimpleme      | ented bit, read as | s '0'             |     |  |  |

| -n = Value at PO | R                                                                                                                                                                                                                                                            | '1' = Bit is set |       | '0' = Bit is clear | ed                 | x = Bit is unknow | /n  |  |  |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32<br>x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64 |                  |       |                    |                    |                   |     |  |  |

| bit 3-0          | Unimplement                                                                                                                                                                                                                                                  | ed: Read as '0'  |       |                    |                    |                   |     |  |  |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

### 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 9-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =  $50^{\circ}C$  and external impedance of  $10k\Omega 5.0V VDD$  TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF $= 5\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-T_{C}}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} \qquad (1 - e^{\frac{-T_{C}}{RC}}) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}$$

$$V_{APPLIED}\left(1 - e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \quad \text{; combining [1] and [2]}$$

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

**3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

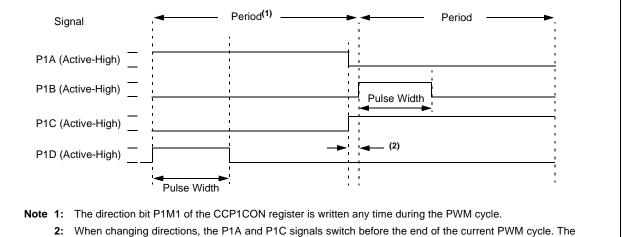

# 10.4.2.1 Direction Change in Full-Bridge Mode

In the Full-Bridge mode, the P1M1 bit in the CCP1CON register allows users to control the forward/reverse direction. When the application firmware changes this direction control bit, the module will change to the new direction on the next PWM cycle.

A direction change is initiated in software by changing the P1M1 bit of the CCP1CON register. The following sequence occurs four Timer2 cycles prior to the end of the current PWM period:

- The modulated outputs (P1B and P1D) are placed in their inactive state.

- The associated unmodulated outputs (P1A and P1C) are switched to drive in the opposite direction.

- PWM modulation resumes at the beginning of the next period.

See Figure 10-12 for an illustration of this sequence.

The Full-Bridge mode does not provide dead-band delay. As one output is modulated at a time, dead-band delay is generally not required. There is a situation where dead-band delay is required. This situation occurs when both of the following conditions are true:

- 1. The direction of the PWM output changes when the duty cycle of the output is at or near 100%.

- 2. The turn off time of the power switch, including the power device and driver circuit, is greater than the turn on time.

Figure 10-13 shows an example of the PWM direction changing from forward to reverse, at a near 100% duty cycle. In this example, at time t1, the output P1A and P1D become inactive, while output P1C becomes active. Since the turn off time of the power devices is longer than the turn on time, a shoot-through current will flow through power devices QC and QD (see Figure 10-10) for the duration of 't'. The same phenomenon will occur to power devices QA and QB for PWM direction change from reverse to forward.

If changing PWM direction at high duty cycle is required for an application, two possible solutions for eliminating the shoot-through current are:

- 1. Reduce PWM duty cycle for one PWM period before changing directions.

- 2. Use switch drivers that can drive the switches off faster than they can drive them on.

Other options to prevent shoot-through current may exist.

#### FIGURE 10-12: EXAMPLE OF PWM DIRECTION CHANGE

When changing directions, the P1A and P1C signals switch before the end of the current PWM cycle.

modulated P1B and P1D signals are inactive at this time. The length of this time is four Timer2 counts.

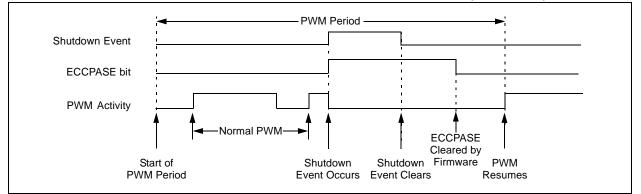

- Note 1: The auto-shutdown condition is a levelbased signal, not an edge-based signal. As long as the level is present, the autoshutdown will persist.

- 2: Writing to the ECCPASE bit is disabled while an auto-shutdown condition persists.

- 3: Once the auto-shutdown condition has been removed and the PWM restarted (either through firmware or auto-restart), the PWM signal will always restart at the beginning of the next PWM period.

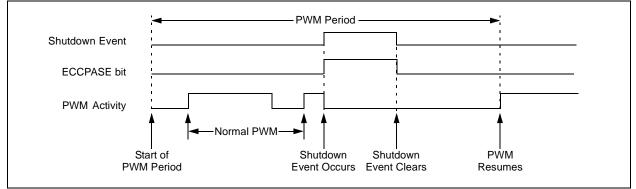

#### FIGURE 10-14: PWM AUTO-SHUTDOWN WITH FIRMWARE RESTART (PRSEN = 0)

#### 10.4.5 AUTO-RESTART MODE

The Enhanced PWM can be configured to automatically restart the PWM signal once the auto-shutdown condition has been removed. Auto-restart is enabled by setting the PRSEN bit in the PWM1CON register.

If auto-restart is enabled, the ECCPASE bit will remain set as long as the auto-shutdown condition is active. When the auto-shutdown condition is removed, the ECCPASE bit will be cleared via hardware and normal operation will resume.

#### FIGURE 10-15: PWM AUTO-SHUTDOWN WITH AUTO-RESTART ENABLED (PRSEN = 1)

#### 12.4.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF bit of the INTCON register. The interrupt can be enabled/disabled by setting/clearing T0IE bit of the INTCON register. See **Section 5.0 "Timer0 Module"** for operation of the Timer0 module.

#### 12.4.3 PORTA INTERRUPT-ON-CHANGE

An input change on PORTA sets the RAIF bit of the INTCON register. The interrupt can be enabled/ disabled by setting/clearing the RAIE bit of the INTCON register. Plus, individual pins can be configured through the IOCA register.

Note: If a change on the I/O pin should occur when any PORTA operation is being executed, then the RAIF interrupt flag may not get set.

NOTES:

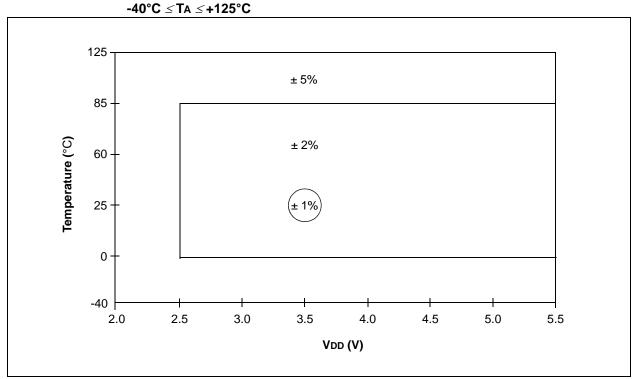

FIGURE 15-3: PIC16F610/616 FREQUENCY TOLERANCE GRAPH,

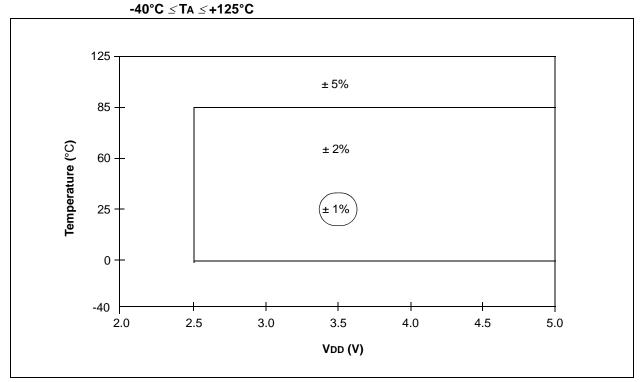

FIGURE 15-4: PIC16HV610/616 FREQUENCY TOLERANCE GRAPH,

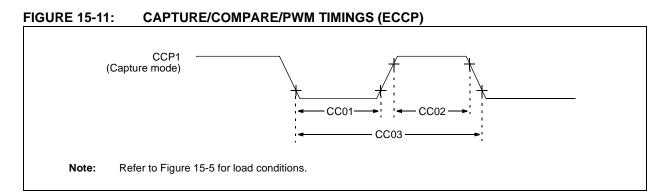

### TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

|              | Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature -40°C ≤ TA ≤ +125°C |                      |                |                       |   |   |       |                                       |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|---|---|-------|---------------------------------------|--|--|--|

| Param<br>No. | Sym                                                                                                  | Character            | Characteristic |                       |   |   | Units | Conditions                            |  |  |  |

| CC01*        | TccL                                                                                                 | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | — | _ | ns    |                                       |  |  |  |

|              |                                                                                                      |                      | With Prescaler | 20                    | — | _ | ns    |                                       |  |  |  |

| CC02*        | ТссН                                                                                                 | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | — | _ | ns    |                                       |  |  |  |

|              |                                                                                                      |                      | With Prescaler | 20                    | — |   | ns    |                                       |  |  |  |

| CC03*        | TccP                                                                                                 | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | — | — | ns    | N = prescale<br>value (1, 4 or<br>16) |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### TABLE 15-12: PIC16F616/16HV616 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                                        | Min | Тур†         | Max | Units | Conditions                                                                                                                                      |

|--------------|------|-----------------------------------------------------------------------|-----|--------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| AD130*       | TAD  | A/D Clock Period                                                      | 1.6 |              | 9.0 | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                    |

|              |      |                                                                       | 3.0 | —            | 9.0 | μS    | Tosc-based, VREF full range                                                                                                                     |

|              |      | A/D Internal RC<br>Oscillator Period                                  | 3.0 | 6.0          | 9.0 | μs    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                     |

|              |      |                                                                       | 1.6 | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                   |

| AD131        | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _   | 11           |     | Tad   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                           |

| AD132*       | TACQ | Acquisition Time                                                      |     | 11.5         | _   | μS    |                                                                                                                                                 |

| AD133*       | TAMP | Amplifier Settling Time                                               | _   | —            | 5   | μS    |                                                                                                                                                 |

| AD134        | Tgo  | Q4 to A/D Clock Start                                                 | _   | Tosc/2       |     | —     |                                                                                                                                                 |

|              |      |                                                                       | _   | Tosc/2 + Tcy |     | _     | If the A/D clock source is selected as RC, a time of TCY is added before the A/D clock starts. This allows the SLEE instruction to be executed. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Section 9.3 "A/D Acquisition Requirements" for minimum conditions.

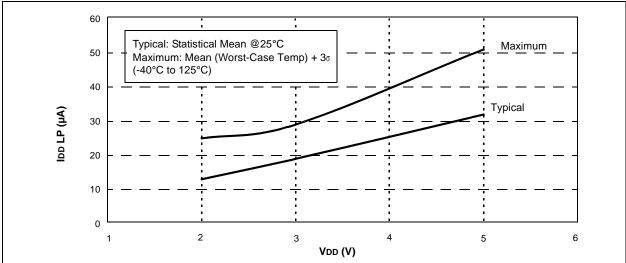

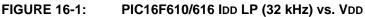

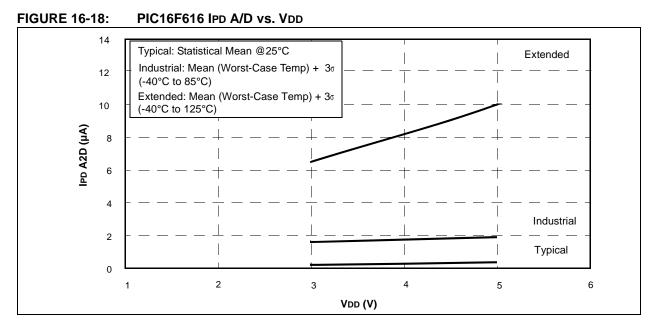

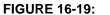

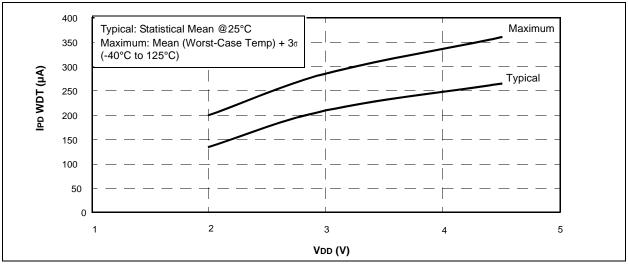

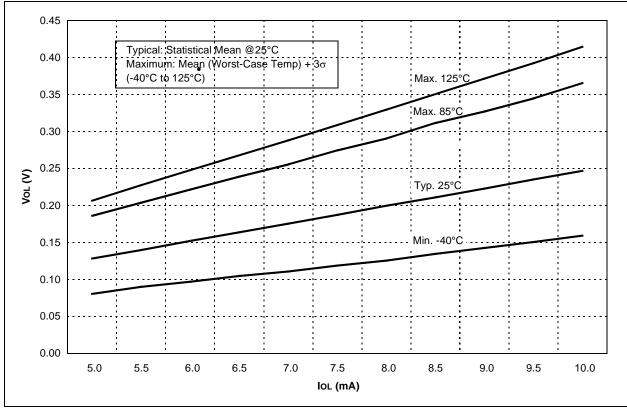

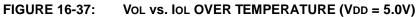

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

#### FIGURE 16-2: PIC16F610/616 IDD EC (1 MHz) vs. VDD

PIC16HV610/616 IDD LP (32 kHz) vs. VDD

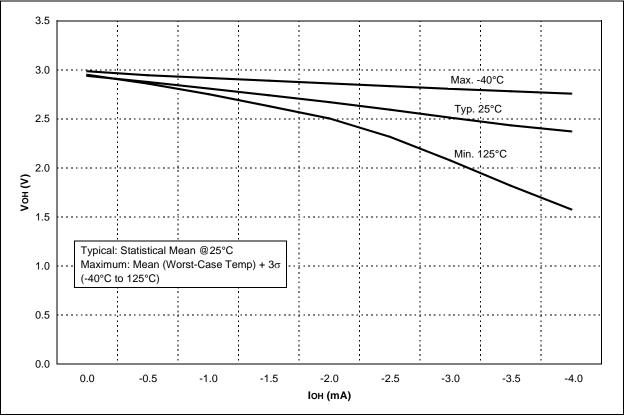

14-Lead Plastic Small Outline (SL) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                       | Units  | N        | MILLIMETERS |      |  |  |

|-----------------------|--------|----------|-------------|------|--|--|

| Dimension             | Limits | MIN      | NOM         | MAX  |  |  |

| Contact Pitch         |        | 1.27 BSC |             |      |  |  |

| Contact Pad Spacing   | С      |          | 5.40        |      |  |  |

| Contact Pad Width     | Х      |          |             | 0.60 |  |  |

| Contact Pad Length    | Y      |          |             | 1.50 |  |  |

| Distance Between Pads | Gx     | 0.67     |             |      |  |  |

| Distance Between Pads | G      | 3.90     |             |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2065A

NOTES: