Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Supplier Device Package    | 14-TSSOP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f610t-i-st |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Addr   | Name                    | Bit 7              | Bit 6               | Bit 5                 | Bit 4          | Bit 3          | Bit 2           | Bit 1                 | Bit 0    | Value on<br>POR, BOR | Page     |

|--------|-------------------------|--------------------|---------------------|-----------------------|----------------|----------------|-----------------|-----------------------|----------|----------------------|----------|

| Bank 0 |                         |                    |                     |                       |                |                |                 |                       |          |                      |          |

| 00h    | INDF                    | Addressing         | this location       | uses conten           | ts of FSR to a | address data   | memory (no      | t a physical r        | egister) | xxxx xxxx            | 24, 116  |

| 01h    | TMR0                    | Timer0 Mod         | lule's Registe      | er                    |                |                |                 |                       |          | xxxx xxxx            | 45, 116  |

| 02h    | PCL                     | Program Co         | ounter's (PC)       | Least Signif          | icant Byte     |                |                 |                       |          | 0000 0000            | 24, 116  |

| 03h    | STATUS                  | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>  | RP0                   | TO             | PD             | Z               | DC                    | С        | 0001 1xxx            | 18, 116  |

| 04h    | FSR                     | Indirect Dat       | a Memory Ad         | ddress Pointe         | er             |                |                 |                       |          | XXXX XXXX            | 24, 116  |

| 05h    | PORTA                   | _                  | _                   | RA5                   | RA4            | RA3            | RA2             | RA1                   | RA0      | x0 x000              | 33, 116  |

| 06h    | _                       | Unimpleme          | nted                |                       |                |                |                 |                       |          | _                    | _        |

| 07h    | PORTC                   | _                  | _                   | RC5                   | RC4            | RC3            | RC2             | RC1                   | RC0      | xx 00xx              | 42, 116  |

| 08h    | _                       | Unimpleme          | nted                |                       |                |                |                 |                       |          | _                    | _        |

| 09h    | _                       | Unimpleme          | nted                |                       |                |                |                 |                       |          | _                    | _        |

| 0Ah    | PCLATH                  | _                  | —                   | —                     | Write          | Buffer for up  | oper 5 bits of  | Program Co            | unter    | 0 0000               | 24, 116  |

| 0Bh    | INTCON                  | GIE                | PEIE                | TOIE                  | INTE           | RAIE           | T0IF            | INTF                  | RAIF     | 0000 0000            | 20, 116  |

| 0Ch    | PIR1                    | _                  | ADIF <sup>(2)</sup> | CCP1IF <sup>(2)</sup> | C2IF           | C1IF           | —               | TMR2IF <sup>(2)</sup> | TMR1IF   | -000 0-00            | 22, 116  |

| 0Dh    | _                       | Unimpleme          | nted                |                       |                |                |                 |                       |          | _                    | _        |

| 0Eh    | TMR1L                   | Holding Reg        | gister for the      | Least Signifi         | cant Byte of t | he 16-bit TM   | IR1 Register    |                       |          | xxxx xxxx            | 49, 116  |

| 0Fh    | TMR1H                   | Holding Reg        | gister for the      | Most Signific         | ant Byte of t  | ne 16-bit TMI  | R1 Register     |                       |          | xxxx xxxx            | 49, 116  |

| 10h    | T1CON                   | T1GINV             | TMR1GE              | T1CKPS1               | T1CKPS0        | T1OSCEN        | T1SYNC          | TMR1CS                | TMR10N   | 0000 0000            | 52, 116  |

| 11h    | TMR2 <sup>(2)</sup>     | Timer2 Mod         | lule Register       |                       |                |                |                 |                       |          | 0000 0000            | 55, 116  |

| 12h    | T2CON <sup>(2)</sup>    | _                  | TOUTPS3             | TOUTPS2               | TOUTPS1        | TOUTPS0        | TMR2ON          | T2CKPS1               | T2CKPS0  | -000 0000            | 56, 116  |

| 13h    | CCPR1L <sup>(2)</sup>   | Capture/Co         | mpare/PWM           | Register 1 L          | ow Byte        |                | •               | •                     | •        | XXXX XXXX            | 86, 116  |

| 14h    | CCPR1H <sup>(2)</sup>   | Capture/Co         | mpare/PWM           | Register 1 H          | ligh Byte      |                |                 |                       |          | XXXX XXXX            | 86, 116  |

| 15h    | CCP1CON <sup>(2)</sup>  | P1M1               | P1M0                | DC1B1                 | DC1B0          | CCP1M3         | CCP1M2          | CCP1M1                | CCP1M0   | 0000 0000            | 85, 116  |

| 16h    | PWM1CON <sup>(2)</sup>  | PRSEN              | PDC6                | PDC5                  | PDC4           | PDC3           | PDC2            | PDC1                  | PDC0     | 0000 0000            | 85, 116  |

| 17h    | ECCPAS <sup>(2)</sup>   | ECCPASE            | ECCPAS2             | ECCPAS1               | ECCPAS0        | PSSAC1         | PSSAC0          | PSSBD1                | PSSBD0   | 0000 0000            | 102, 116 |

| 18h    | _                       | Unimpleme          | nted                |                       |                |                |                 |                       |          | _                    | _        |

| 19h    | VRCON                   | C1VREN             | C2VREN              | VRR                   | FVREN          | VR3            | VR2             | VR1                   | VR0      | 0000 0000            | 72, 116  |

| 1Ah    | CM1CON0                 | C1ON               | C1OUT               | C10E                  | C1POL          | —              | C1R             | C1CH1                 | C1CH0    | 0000 -000            | 62, 116  |

| 1Bh    | CM2CON0                 | C2ON               | C2OUT               | C2OE                  | C2POL          | _              | C2R             | C2CH1                 | C2CH0    | 0000 -000            | 63, 116  |

| 1Ch    | CM2CON1                 | MC1OUT             | MC2OUT              | —                     | T1ACS          | C1HYS          | C2HYS           | T1GSS                 | C2SYNC   | 00-0 0010            | 65, 116  |

| 1Dh    | _                       | Unimpleme          | nted                |                       | •              |                | •               | •                     | •        | _                    | —        |

| 1Eh    | ADRESH <sup>(2,3)</sup> | Most Signifi       | cant 8 bits of      | the left shift        | ed A/D result  | or 2 bits of r | ight shifted re | esult                 |          | xxxx xxxx            | 80, 116  |

| 1Fh    | ADCON0(2)               | ADFM               | VCFG                | CHS3                  | CHS2           | CHS1           | CHS0            | GO/DONE               | ADON     | 0000 0000            | 78, 116  |

#### **TABLE 2-1:** PIC16F610/616/16HV610/616 SPECIAL FUNCTION REGISTERS SUMMARY BANK 0

- = Unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented IRP and RP1 bits are reserved, always maintain these bits clear. Legend:

Note 1:

2: PIC16F616/16HV616 only.

3: Read-only register.

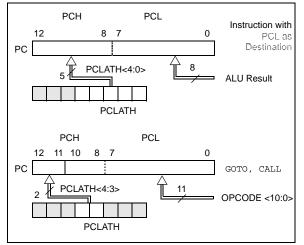

### 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in Figure 2-5 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-5 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

### 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, "Implementing a Table Read" (DS00556).

### 2.3.2 STACK

The PIC16F610/616/16HV610/616 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

### 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-7.

A simple program to clear RAM location 40h-4Fh using indirect addressing is shown in Example 2-1.

|       | MOVLW    | 0x40   | ;initialize pointer  |

|-------|----------|--------|----------------------|

|       | MOVWF    | FSR    | ;to RAM              |

| NEXT  | CLRF     | INDF   | ;clear INDF register |

|       | INCF     | FSR, F | ;inc pointer         |

|       | BTFSS    | FSR,4  | ;all done?           |

|       | GOTO     | NEXT   | ;no clear next       |

| CONTI | CONTINUE |        | ;yes continue        |

| 1     |          |        |                      |

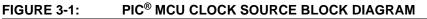

### 3.0 OSCILLATOR MODULE

### 3.1 Overview

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured with a choice of two selectable speeds: internal or external system clock source.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The Internal Oscillator module provides a selectable system clock mode of either 4 MHz (Postscaler) or 8 MHz (INTOSC).

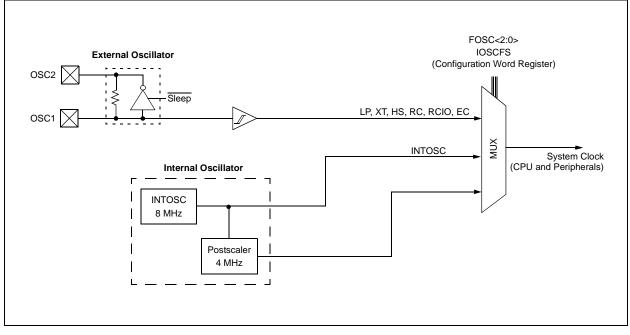

### 3.3.3 LP, XT, HS MODES

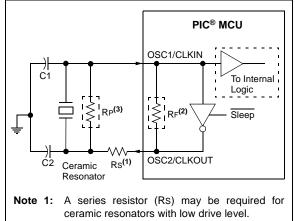

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

### FIGURE 3-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- **2:** The value of RF varies with the Oscillator mode selected (typically between 2 MΩ to 10 MΩ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

### 4.2 Additional Pin Functions

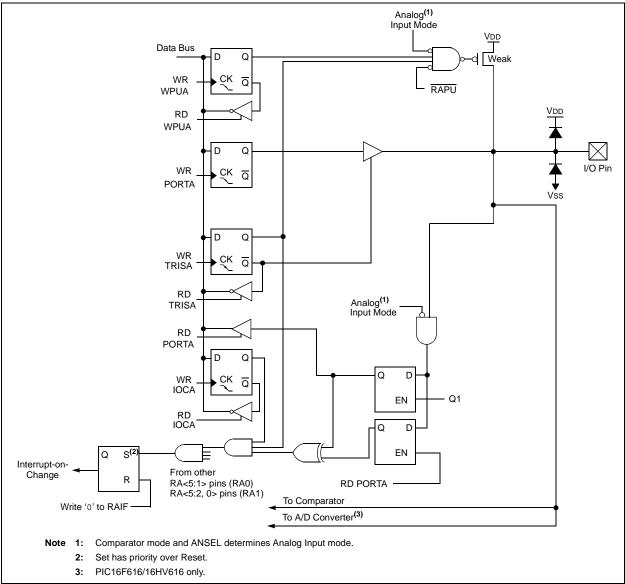

Every PORTA pin on the PIC16F610/616/16HV610/ 616 has an interrupt-on-change option and a weak pullup option. The next three sections describe these functions.

### 4.2.1 ANSEL REGISTER

The ANSEL register is used to configure the Input mode of an I/O pin to analog. Setting the appropriate ANSEL bit high will cause all digital reads on the pin to be read as '0' and allow analog functions on the pin to operate correctly.

The state of the ANSEL bits has no affect on digital output functions. A pin with TRIS clear and ANSEL set will still operate as a digital output, but the Input mode will be analog. This can cause unexpected behavior when executing read-modify-write instructions on the affected port.

### 4.2.2 WEAK PULL-UPS

Each of the PORTA pins, except RA3, has an individually configurable internal weak pull-up. Control bits WPUAx enable or disable each pull-up. Refer to Register 4-4. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the RAPU bit of the OPTION register). A weak pull-up is automatically enabled for RA3 when configured as MCLR and disabled when RA3 is an input. There is no software control of the MCLR pull-up.

### 4.2.3 INTERRUPT-ON-CHANGE

Each PORTA pin is individually configurable as an interrupt-on-change pin. Control bits IOCAx enable or disable the interrupt function for each pin. Refer to Register 4-5. The interrupt-on-change is disabled on a Power-on Reset.

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of PORTA. The 'mismatch' outputs of the last read are OR'd together to set the PORTA Change Interrupt Flag bit (RAIF) in the INTCON register (Register 2-3).

This interrupt can wake the device from Sleep. The user, in the Interrupt Service Routine, clears the interrupt by:

- a) Any read or write of PORTA. This will end the mismatch condition, then,

- b) Clear the flag bit RAIF.

A mismatch condition will continue to set flag bit RAIF. Reading PORTA will end the mismatch condition and allow flag bit RAIF to be cleared. The <u>latch</u> holding the last read value is not affected by a MCLR nor BOR Reset. After these resets, the RAIF flag will continue to be set if a mismatch is present.

Note: If a change on the I/O pin should occur when any PORTA operation is being executed, then the RAIF interrupt flag may not get set.

### REGISTER 4-3: ANSEL: ANALOG SELECT REGISTER

| R/W-1                          | R/W-1 | R/W-1        | R/W-1 | R/W-1               | R/W-1               | R/W-1    | R/W-1 |

|--------------------------------|-------|--------------|-------|---------------------|---------------------|----------|-------|

| ANS7                           | ANS6  | ANS5         | ANS4  | ANS3 <sup>(2)</sup> | ANS2 <sup>(2)</sup> | ANS1     | ANS0  |

| bit 7                          |       |              | •     |                     |                     |          | bit 0 |

|                                |       |              |       |                     |                     |          |       |

|                                |       |              |       |                     |                     |          |       |

| Legend:                        |       |              |       |                     |                     |          |       |

| <b>Legend:</b><br>R = Readable | bit   | W = Writable | bit   | U = Unimplen        | nented bit, reac    | l as '0' |       |

bit 7-0 ANS<7:0>: Analog Select bits

Analog select between analog or digital function on pins AN<7:0>, respectively.

1 = Analog input. Pin is assigned as analog input<sup>(1)</sup>.

0 = Digital I/O. Pin is assigned to port or special function.

- **Note 1:** Setting a pin to an analog input automatically disables the digital input circuitry, weak pull-ups, and interrupt-on-change if available. The corresponding TRIS bit must be set to Input mode in order to allow external control of the voltage on the pin.

- 2: PIC16F616/HV616.

### 4.2.4 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

### 4.2.4.1 RA0/AN0<sup>(1)</sup>/C1IN+/ICSPDAT

Figure 4-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to the comparator

- In-Circuit Serial Programming data

### 4.2.4.2 RA1/AN1<sup>(1)</sup>/C12IN0-/VREF<sup>(1)</sup>/ ICSPCLK

Figure 4-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to the comparator

- a voltage reference input for the ADC<sup>(1)</sup>

- In-Circuit Serial Programming clock

Note 1: PIC16F616/16HV616 only.

### FIGURE 4-1: BLOCK DIAGRAM OF RA<1:0>

NOTES:

## FIGURE 10-6: EXAMPLE PWM (ENHANCED MODE) OUTPUT RELATIONSHIPS (ACTIVE-HIGH STATE)

|       |                           |                          |          | Width                | Period               |          |

|-------|---------------------------|--------------------------|----------|----------------------|----------------------|----------|

| 00    | (Single Output)           | P1A Modulated            |          | Delay <sup>(1)</sup> | Delay <sup>(1)</sup> |          |

|       |                           | P1A Modulated            | _        |                      |                      |          |

| 10    | (Half-Bridge)             | P1B Modulated            |          |                      |                      | i        |

|       |                           | P1A Active               |          |                      | '                    | <br>     |

| 01    | (Full-Bridge,<br>Forward) | P1B Inactive             |          |                      |                      |          |

|       | Forward)                  | P1C Inactive             | <u> </u> | 1                    |                      |          |

|       |                           | P1D Modulated            |          |                      | <u> </u>             | 1<br>    |

|       |                           | P1A Inactive             |          |                      | 1<br>1<br>1          |          |

| 11    | (Full-Bridge,<br>Reverse) | P1B Modulated            |          |                      |                      | <u> </u> |

|       |                           | P1C Active -             |          |                      |                      | i        |

|       |                           | P1D Inactive             |          |                      | 1<br>1<br>1          | <u> </u> |

| Relat | ionships:                 | c * (PR2 + 1) * (TMR2 Pr |          |                      |                      |          |

Note 1: Dead-band delay is programmed using the PWM1CON register (Section 10.4.6 "Programmable Dead-Band Delay mode").

| P1M<  | 1:0>                      | Signal                                                                          | 0 Pulse Width                         | <b>—</b>             | PR2+1     |

|-------|---------------------------|---------------------------------------------------------------------------------|---------------------------------------|----------------------|-----------|

|       |                           | _                                                                               |                                       | Period ——            | <b>→</b>  |

| 00    | (Single Output)           | P1A Modulated                                                                   |                                       |                      | 1         |

|       |                           | P1A Modulated                                                                   | Delay <sup>(1)</sup>                  | Delay <sup>(1)</sup> |           |

| 10    | (Half-Bridge)             | P1B Modulated                                                                   |                                       |                      | ;         |

|       |                           | P1A Active                                                                      | 1<br>1<br>                            |                      |           |

| 01    | (Full-Bridge,<br>Forward) | P1B Inactive                                                                    | · · · · · · · · · · · · · · · · · · · | I                    | I<br><br> |

|       | ,                         | P1C Inactive                                                                    | <br>                                  | 1                    | 1         |

|       |                           | P1D Modulated                                                                   |                                       |                      |           |

|       |                           | P1A Inactive                                                                    |                                       | <br> <br>            | <br>      |

| 11    | (Full-Bridge,<br>Reverse) | P1B Modulated                                                                   |                                       | I                    |           |

|       | Nevelocy                  | P1C Active                                                                      |                                       |                      |           |

|       |                           | P1D Inactive                                                                    |                                       |                      | <br> <br> |

| Relat | • Pulse Width = To        | c * (PR2 + 1) * (TMR2 Presca<br>>sc * (CCPR1L<7:0>:CCP1C(<br>: * (PWM1CON<6:0>) |                                       | cale Value)          |           |

### FIGURE 10-7: EXAMPLE ENHANCED PWM OUTPUT RELATIONSHIPS (ACTIVE-LOW STATE)

### 10.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPASx bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator C1

- Comparator C2

- · Setting the ECCPASE bit in firmware

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see Section 10.4.5 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSSAC and PSSBD bits of the ECCPAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

### REGISTER 10-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

|           |       | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------|-------|--------|---------|---------|---------|--------|--------|--------|--------|

| bit 7 bit | E     | CCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 | PSSBD0 |

|           | bit 7 | 7      |         |         |         |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in shutd<br/>0 = ECCP outputs are operating</li> <li>bit 6-4 ECCPAS&lt;2:0&gt;: ECCP Auto-shutdown Source Select bits</li> <li>000 = Auto-Shutdown is disabled</li> <li>001 = Comparator C1 output high</li> </ul> |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 000 = Auto-Shutdown is disabled                                                                                                                                                                                                                                                 | iown state |

|                                                                                                                                                                                                                                                                                 |            |

| 010 = Comparator C2 output high <sup>(1)</sup><br>011 = Either Comparators output is high<br>100 = VIL on INT pin<br>101 = VIL on INT pin or Comparator C1 output high<br>110 = VIL on INT pin or Comparator C2 output high                                                     |            |

| 111 = VIL on INT pin or either Comparators output is high                                                                                                                                                                                                                       |            |

| bit 3-2 <b>PSSACn:</b> Pins P1A and P1C Shutdown State Control bits<br>00 = Drive pins P1A and P1C to '0'<br>01 = Drive pins P1A and P1C to '1'<br>1x = Pins P1A and P1C tri-state                                                                                              |            |

| bit 1-0 <b>PSSBDn:</b> Pins P1B and P1D Shutdown State Control bits<br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state                                                                                              |            |

### 12.2 Calibration Bits

The 8 MHz internal oscillator is factory calibrated. These calibration values are stored in fuses located in the Calibration Word (2008h). The Calibration Word is not erased when using the specified bulk erase sequence in the *Memory Programming Specification* (DS41284) and thus, does not require reprogramming.

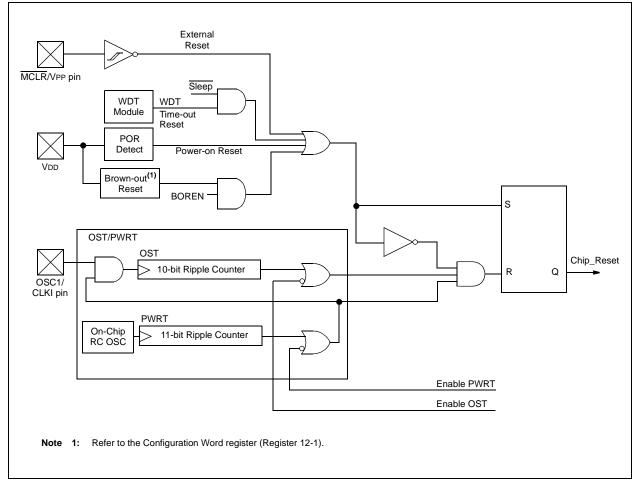

### 12.3 Reset

The PIC16F610/616/16HV610/616 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

WDT wake-up does not cause register resets in the same manner as a WDT Reset since wake-up is viewed as the resumption of normal operation. TO and  $\overline{PD}$  bits are set or cleared differently in different Reset situations, as indicated in Table 12-2. Software can use these bits to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse-width specifications.

### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

### 12.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Temporary holding registers W\_TEMP and STATUS\_TEMP should be placed in the last 16 bytes of GPR (see Figure 2-4). These 16 locations are common to all banks and do not require banking. This makes context save and restore operations simpler. The code shown in Example 12-1 can be used to:

- Store the W register

- Store the STATUS register

- Execute the ISR code

- Restore the Status (and Bank Select Bit register)

- Restore the W register

| Note: | The PIC16F610/616/16HV610/616 does      |  |  |  |

|-------|-----------------------------------------|--|--|--|

|       | not require saving the PCLATH. However, |  |  |  |

|       | if computed GOTO's are used in both the |  |  |  |

|       | ISR and the main code, the PCLATH must  |  |  |  |

|       | be saved and restored in the ISR.       |  |  |  |

### EXAMPLE 12-1: SAVING STATUS AND W REGISTERS IN RAM

| MOVWF<br>SWAPF | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits |

|----------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| MOVWF<br>:     | STATUS_TEMP        | Save status to bank zero STATUS_TEMP register                                                                             |

| :(ISR)         |                    | ;Insert user code here                                                                                                    |

| SWAPF          | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W<br>;(sets bank to original state)                                                       |

| MOVWF          | STATUS             | ;Move W into STATUS register                                                                                              |

| SWAPF          | W_TEMP,F           | ;Swap W_TEMP                                                                                                              |

| SWAPF          | W_TEMP,W           | ;Swap W_TEMP into W                                                                                                       |

| Mnemonic,<br>Operands                  |      | Description                  |                | 14-Bit Opcode |      |             |      | Status   |         |

|----------------------------------------|------|------------------------------|----------------|---------------|------|-------------|------|----------|---------|

|                                        |      |                              |                | MSb           |      |             | LSb  | Affected | Notes   |

| BYTE-ORIENTED FILE REGISTER OPERATIONS |      |                              |                |               |      |             |      |          |         |

| ADDWF                                  | f, d | Add W and f                  | 1              | 00            | 0111 | dfff        | ffff | C, DC, Z | 1, 2    |

| ANDWF                                  | f, d | AND W with f                 | 1              | 00            | 0101 | dfff        | ffff | Z        | 1, 2    |

| CLRF                                   | f    | Clear f                      | 1              | 00            | 0001 | lfff        | ffff | Z        | 2       |

| CLRW                                   | -    | Clear W                      | 1              | 00            | 0001 | 0xxx        | xxxx | Z        |         |

| COMF                                   | f, d | Complement f                 | 1              | 00            | 1001 | dfff        | ffff | Z        | 1, 2    |

| DECF                                   | f, d | Decrement f                  | 1              | 00            | 0011 | dfff        | ffff | Z        | 1, 2    |

| DECFSZ                                 | f, d | Decrement f, Skip if 0       | 1 <b>(2)</b>   | 00            | 1011 | dfff        | ffff |          | 1, 2, 3 |

| INCF                                   | f, d | Increment f                  | 1              | 00            | 1010 | dfff        | ffff | Z        | 1, 2    |

| INCFSZ                                 | f, d | Increment f, Skip if 0       | 1 <b>(2)</b>   | 00            | 1111 | dfff        | ffff |          | 1, 2, 3 |

| IORWF                                  | f, d | Inclusive OR W with f        | 1              | 00            | 0100 | dfff        | ffff | Z        | 1, 2    |

| MOVF                                   | f, d | Move f                       | 1              | 00            | 1000 | dfff        | ffff | Z        | 1, 2    |

| MOVWF                                  | f    | Move W to f                  | 1              | 00            | 0000 | lfff        | ffff |          |         |

| NOP                                    | _    | No Operation                 | 1              | 00            | 0000 | 0xx0        | 0000 |          |         |

| RLF                                    | f, d | Rotate Left f through Carry  | 1              | 00            | 1101 | dfff        | ffff | С        | 1, 2    |

| RRF                                    | f, d | Rotate Right f through Carry | 1              | 00            | 1100 | dfff        | ffff | C        | 1, 2    |

| SUBWF                                  | f, d | Subtract W from f            | 1              | 00            | 0010 |             | ffff | C, DC, Z | 1, 2    |

| SWAPF                                  | f, d | Swap nibbles in f            | 1              | 00            | 1110 |             | ffff | -,, -    | 1, 2    |

| XORWF                                  | f, d | Exclusive OR W with f        | 1              | 00            | 0110 |             | ffff | Z        | 1, 2    |

|                                        | .,   | BIT-ORIENTED FILE REGIS      |                |               |      |             |      |          | -, -    |

| BCF                                    | f. b | Bit Clear f                  | 1              | 01            |      | bfff        | ffff |          | 1, 2    |

| BSF                                    | f, b | Bit Set f                    | 1              | 01            |      | bfff        |      |          | 1, 2    |

| BTFSC                                  | f, b | Bit Test f, Skip if Clear    |                | 01            |      | bfff        |      |          | 3       |

| BTFSS                                  | f, b | Bit Test f, Skip if Set      | 1 (2)<br>1 (2) | 01            |      |             | ffff |          | 3       |

| ыгээ                                   | Ι, D |                              |                | -             | 11bb | bfff        | IIII |          | 3       |

|                                        |      | LITERAL AND CONTRO           | 1              | IONS          |      |             |      | r        | r       |

| ADDLW                                  | k    | Add literal and W            | 1              | 11            |      | kkkk        |      | C, DC, Z |         |

| ANDLW                                  | k    | AND literal with W           | 1              | 11            | 1001 | kkkk        | kkkk | Z        |         |

| CALL                                   | k    | Call Subroutine              | 2              | 10            | 0kkk | kkkk        | kkkk |          |         |

| CLRWDT                                 | -    | Clear Watchdog Timer         | 1              | 00            | 0000 | 0110        | 0100 | TO, PD   |         |

| GOTO                                   | k    | Go to address                | 2              | 10            | 1kkk | kkkk        | kkkk |          |         |

| IORLW                                  | k    | Inclusive OR literal with W  | 1              | 11            | 1000 | kkkk        | kkkk | Z        |         |

| MOVLW                                  | k    | Move literal to W            | 1              | 11            | 00xx | kkkk        | kkkk |          |         |

| RETFIE                                 | -    | Return from interrupt        | 2              | 00            | 0000 | 0000        | 1001 |          |         |

| RETLW                                  | k    | Return with literal in W     | 2              | 11            | 01xx | kkkk        | kkkk |          |         |

| RETURN                                 | -    | Return from Subroutine       | 2              | 00            | 0000 | 0000        | 1000 |          |         |

| SLEEP                                  | -    | Go into Standby mode         | 1              | 00            | 0000 | 0110        | 0011 | TO, PD   |         |

| SUBLW                                  | k    | Subtract W from literal      | 1              | 11            | 110x | kkkk        | kkkk | C, DC, Z |         |

| XORLW                                  | k    | Exclusive OR literal with W  | 1              | 11            | 1010 | le le le le | kkkk | Z        |         |

### TABLE 13-2: PIC16F610/616/16HV610/616 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] DECFSZ f,d                                                                                                                                                                                                                                                                                                 |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                    |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                         |

| Status Affected: | None                                                                                                                                                                                                                                                                                                               |

| Description:     | The contents of register 'f' are decremented. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'.<br>If the result is '1', the next instruction is executed. If the result is '0', then a NOP is executed instead, making it a two-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                                |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCFSZ f,d                                                                                                                                                                                                                                                                                                                    |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                       |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                            |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                  |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a two-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |

| Operands:        | $0 \leq k \leq 2047$                                                                                                                                                                             |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |

| Status Affected: | None                                                                                                                                                                                             |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |

| IORLW            | Inclusive OR literal with W                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |

| Operands:        | $0 \leq k \leq 255$                                                                                                       |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |

| Status Affected: | Z                                                                                                                         |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                            |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                                  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |

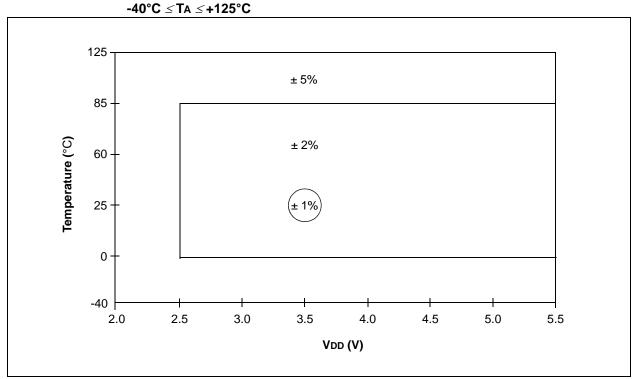

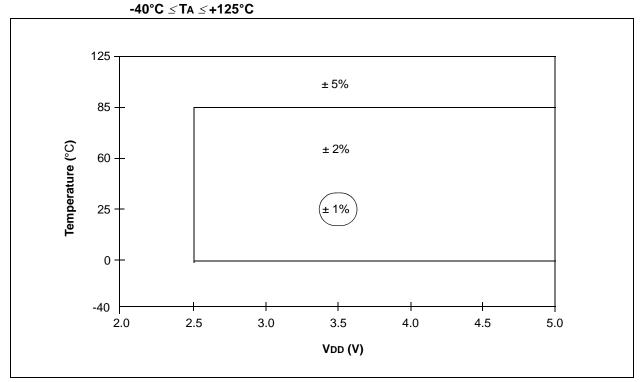

FIGURE 15-3: PIC16F610/616 FREQUENCY TOLERANCE GRAPH,

FIGURE 15-4: PIC16HV610/616 FREQUENCY TOLERANCE GRAPH,

### 15.3 DC Characteristics: PIC16HV610/616-I (Industrial) PIC16HV610/616-E (Extended)

| DC CHARACTERISTICS |                                        |     | ard Oper<br>ing temp                    |     | -40°C ⊴ | s otherwise stated)<br>35°C for industrial<br>125°C for extended |                                     |

|--------------------|----------------------------------------|-----|-----------------------------------------|-----|---------|------------------------------------------------------------------|-------------------------------------|

| Param              | Device Characteristics                 | Min | Тур†                                    | Max | Units   |                                                                  | Conditions                          |

| No.                |                                        |     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     |         | VDD                                                              | Note                                |

| D010               | Supply Current (IDD) <sup>(1, 2)</sup> | _   | 160                                     | 230 | μΑ      | 2.0                                                              | Fosc = 32 kHz                       |

|                    | PIC16HV610/616                         | _   | 240                                     | 310 | μA      | 3.0                                                              | LP Oscillator mode                  |

|                    |                                        | _   | 280                                     | 400 | μA      | 4.5                                                              |                                     |

| D011*              |                                        | _   | 270                                     | 380 | μA      | 2.0                                                              | Fosc = 1 MHz                        |

|                    |                                        | _   | 400                                     | 560 | μA      | 3.0                                                              | XT Oscillator mode                  |

|                    |                                        | _   | 520                                     | 780 | μA      | 4.5                                                              |                                     |

| D012               |                                        | —   | 380                                     | 540 | μA      | 2.0                                                              | Fosc = 4 MHz                        |

|                    |                                        | _   | 575                                     | 810 | μA      | 3.0                                                              | XT Oscillator mode                  |

|                    |                                        | _   | 0.875                                   | 1.3 | mA      | 4.5                                                              |                                     |

| D013*              |                                        | —   | 215                                     | 310 | μA      | 2.0                                                              | Fosc = 1 MHz                        |

|                    |                                        | _   | 375                                     | 565 | μA      | 3.0                                                              | EC Oscillator mode                  |

|                    |                                        | —   | 570                                     | 870 | μA      | 4.5                                                              |                                     |

| D014               |                                        | —   | 330                                     | 475 | μA      | 2.0                                                              | Fosc = 4 MHz                        |

|                    |                                        | —   | 550                                     | 800 | μA      | 3.0                                                              | EC Oscillator mode                  |

|                    |                                        | —   | 0.85                                    | 1.2 | mA      | 4.5                                                              |                                     |

| D016*              |                                        | _   | 310                                     | 435 | μA      | 2.0                                                              | Fosc = 4 MHz                        |

|                    |                                        | _   | 500                                     | 700 | μA      | 3.0                                                              | INTOSC mode                         |

|                    |                                        | —   | 0.74                                    | 1.1 | mA      | 4.5                                                              |                                     |

| D017               |                                        | _   | 460                                     | 650 | μΑ      | 2.0                                                              | Fosc = 8 MHz                        |

|                    |                                        | _   | 0.75                                    | 1.1 | mA      | 3.0                                                              | INTOSC mode                         |

|                    |                                        |     | 1.2                                     | 1.6 | mA      | 4.5                                                              |                                     |

| D018               |                                        | -   | 320                                     | 465 | μΑ      | 2.0                                                              | Fosc = 4 MHz                        |

|                    |                                        | _   | 510                                     | 750 | μΑ      | 3.0                                                              | EXTRC mode <sup>(3)</sup>           |

|                    |                                        | —   | 0.770                                   | 1.0 | mA      | 4.5                                                              |                                     |

| D019               |                                        | —   | 2.5                                     | 3.4 | mA      | 4.5                                                              | Fosc = 20 MHz<br>HS Oscillator mode |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

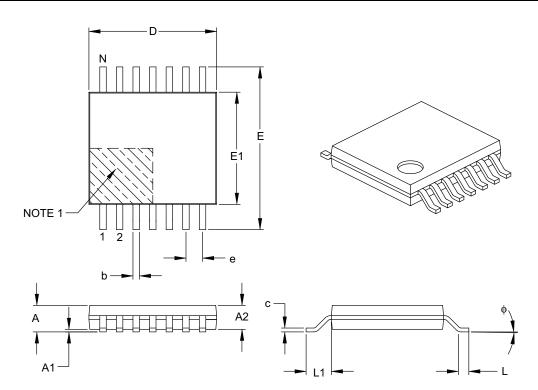

### 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            |                | MILLIMETERS |      |  |

|--------------------------|------------------|----------------|-------------|------|--|

| Dimensio                 | Dimension Limits |                | NOM         | MAX  |  |

| Number of Pins N         |                  | 14             |             |      |  |

| Pitch                    | е                |                | 0.65 BSC    |      |  |

| Overall Height           | Α                | -              | -           | 1.20 |  |

| Molded Package Thickness | A2               | 0.80           | 1.00        | 1.05 |  |

| Standoff                 | A1               | 0.05           | -           | 0.15 |  |

| Overall Width E          |                  | 6.40 BSC       |             |      |  |

| Molded Package Width     | E1               | 4.30 4.40 4.50 |             |      |  |

| Molded Package Length    | D                | 4.90           | 5.00        | 5.10 |  |

| Foot Length              | L                | 0.45           | 0.60        | 0.75 |  |

| Footprint                | L1               | 1.00 REF       |             |      |  |

| Foot Angle               | φ                | 0°             | -           | 8°   |  |

| Lead Thickness           | С                | 0.09           | -           | 0.20 |  |

| Lead Width b             |                  | 0.19           | -           | 0.30 |  |

### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

NOTES:

|      | Reset Values (special registers)  |    |

|------|-----------------------------------|----|

|      | Special Function Registers        | 14 |

|      | Special Register Summary          |    |

|      | SRCON0 (SR Latch Control 0)       | 69 |

|      | SRCON1 (SR Latch Control 1)       | 69 |

|      | STATUS                            |    |

|      | T1CON                             |    |

|      | T2CON                             |    |

|      | TRISA (Tri-State PORTA)           |    |

|      | TRISC (Tri-State PORTC)           |    |

|      | VRCON (Voltage Reference Control) | 72 |

|      | WPUA (Weak Pull Up PORTA)         |    |

| Rese | ət                                |    |

| Revi | sion History                      |    |

### S

| Shoot-through Current          |     |

|--------------------------------|-----|

| Sleep                          |     |

| Power-Down Mode                |     |

| Wake-up                        |     |

| Wake-up using Interrupts       |     |

| Software Simulator (MPLAB SIM) | 141 |

| Special Event Trigger          | 76  |

| Special Function Registers     | 14  |

| SRCON0 Register                |     |

| SRCON1 Register                |     |

| STATUS Register                |     |

### т

| T1CON Register              | . 52 |

|-----------------------------|------|

| T2CON Register              | . 56 |

| Thermal Considerations      | 155  |

| Time-out Sequence           | 114  |

| Timer0                      |      |

| Associated Registers        | . 47 |

| External Clock              | . 46 |

| Interrupt                   | . 47 |

| Operation                   | . 45 |

| Specifications              | 162  |

| ТОСКІ                       | . 46 |

| Timer1                      | . 49 |

| Associated registers        | . 54 |

| Asynchronous Counter Mode   | . 50 |

| Reading and Writing         | . 50 |

| Interrupt                   | . 51 |

| Modes of Operation          | . 49 |

| Operation                   | . 49 |

| Operation During Sleep      |      |

| Oscillator                  | . 50 |

| Prescaler                   | . 50 |

| Specifications              | 162  |

| Timer1 Gate                 |      |

| Inverting Gate              | .51  |

| Selecting Source50          | , 65 |

| SR Latch                    |      |

| Synchronizing COUT w/Timer1 |      |

| TMR1H Register              | . 49 |

| TMR1L Register              | . 49 |

| Timer2                      |      |

| Associated registers        | . 56 |

| Timers                      |      |

| Timer1                      |      |

| T1CON                       | . 52 |

| Timer2                      |      |

| T2CON                       | . 56 |

| Timing Diagrams             |      |

| A/D Conversion                               | 167 |

|----------------------------------------------|-----|

| A/D Conversion (Sleep Mode)                  | 167 |

| Brown-out Reset (BOR)                        | 160 |

| Brown-out Reset Situations                   | 113 |

| CLKOUT and I/O                               | 159 |

| Clock Timing                                 | 157 |

| Comparator Output                            | 57  |

| Enhanced Capture/Compare/PWM (ECCP)          | 163 |

| Full-Bridge PWM Output                       | 98  |

| Half-Bridge PWM Output 96,                   | 104 |

| INT Pin Interrupt                            | 120 |

| PWM Auto-shutdown                            |     |

| Auto-restart Enabled                         | 103 |

| Firmware Restart                             | 103 |

| PWM Direction Change                         | 99  |

| PWM Direction Change at Near 100% Duty Cycle | 100 |

| PWM Output (Active-High)                     |     |

| PWM Output (Active-Low)                      | 95  |

| Reset, WDT, OST and Power-up Timer           | 160 |

| Time-out Sequence                            |     |

| Case 1                                       | 115 |

| Case 2                                       | 115 |

| Case 3                                       | 115 |

| Timer0 and Timer1 External Clock             |     |

| Timer1 Incrementing Edge                     | 52  |

| Wake-up from Interrupt                       | 125 |

| Timing Parameter Symbology                   | 156 |

| TRISA                                        | 33  |

| TRISA Register                               |     |

| TRISC                                        | 42  |

| TRISC Register                               | 42  |

|                                              |     |

### ۷

| Voltage Reference (VR)                         |       |

|------------------------------------------------|-------|

| Specifications                                 | 164   |

| Voltage Reference. See Comparator Voltage Refe | rence |

| (CVREF)                                        |       |

| Voltage References                             |       |

| Associated registers                           | 67    |

| VP6 Stabilization                              | 71    |

| VREF. SEE ADC Reference Voltage                |       |

### W

| Wake-up Using Interrupts |     |

|--------------------------|-----|

| Watchdog Timer (WDT)     | 122 |

| Associated registers     |     |

| Specifications           | 161 |

| WPUA Register            | 35  |

| WWW Address              |     |

| WWW, On-Line Support     |     |