Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f616-e-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.5 PIR1 Register

The PIR1 register contains the peripheral interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

## REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R/W-0                 | R/W-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-------|-------|-----|-----------------------|--------|

| _     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF  | C1IF  | —   | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                       |       |       |     |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7         | Unimplemented: Read as '0'                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6         | ADIF: A/D Interrupt Flag bit <sup>(1)</sup>                                                                                              |

|               | 1 = A/D conversion complete                                                                                                              |

|               | 0 = A/D conversion has not completed or has not been started                                                                             |

| bit 5         | CCP1IF: CCP1 Interrupt Flag bit <sup>(1)</sup>                                                                                           |

|               | Capture mode:                                                                                                                            |

|               | 1 = A TMR1 register capture occurred (must be cleared in software)                                                                       |

|               | 0 = No TMR1 register capture occurred<br>Compare mode:                                                                                   |

|               | 1 = A TMR1 register compare match occurred (must be cleared in software)                                                                 |

|               | 0 = No TMR1 register compare match occurred                                                                                              |

|               | <u>PWM mode</u> :                                                                                                                        |

|               | Unused in this mode                                                                                                                      |

| bit 4         | C2IF: Comparator C2 Interrupt Flag bit                                                                                                   |

|               | 1 = Comparator C2 output has changed (must be cleared in software)                                                                       |

|               | 0 = Comparator C2 output has not changed                                                                                                 |

| bit 3         | C1IF: Comparator C1 Interrupt Flag bit                                                                                                   |

|               | <ul> <li>1 = Comparator C1 output has changed (must be cleared in software)</li> <li>0 = Comparator C1 output has not changed</li> </ul> |

| <b>h</b> it 0 | · · · · ·                                                                                                                                |

| bit 2         | Unimplemented: Read as '0'                                                                                                               |

| bit 1         | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <sup>(1)</sup>                                                                            |

|               | <ul> <li>1 = Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = Timer2 to PR2 match has not occurred</li> </ul>     |

| bit 0         | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                               |

|               | 1 = Timer1 register overflowed (must be cleared in software)                                                                             |

|               | 0 = Timer1 has not overflowed                                                                                                            |

| Note 1:       | PIC16F616/16HV616 only. PIC16F610/16HV610 unimplemented, read as '0'.                                                                    |

#### 3.4.1.1 OSCTUNE Register

The oscillator is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-1). The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

### REGISTER 3-1: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 7-5 Unimplemented: Read as '0'

bit 4-0

| TUN<4:0>: Frequency Tuning bits                                               |  |

|-------------------------------------------------------------------------------|--|

| 01111 = Maximum frequency                                                     |  |

| 01110 =                                                                       |  |

| •                                                                             |  |

| •                                                                             |  |

| •                                                                             |  |

| 00001 =                                                                       |  |

| 00000 = Oscillator module is running at the manufacturer calibrated frequency |  |

| 11111 =                                                                       |  |

| •                                                                             |  |

| •                                                                             |  |

| •                                                                             |  |

| 10000 = Minimum frequency                                                     |  |

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|--------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | IOSCFS | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | _                    | _                                              |

| OSCTUNE               | —      | —     | —     | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  | 0 0000               | u uuuu                                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 12-1) for operation of all register bits.

NOTES:

# 4.0 I/O PORTS

There are as many as eleven general purpose I/O pins and an input pin available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

## 4.1 PORTA and the TRISA Registers

PORTA is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISA (Register 4-2). Setting a TRISA bit (= 1) will make the corresponding PORTA pin an input (i.e., disable the output driver). Clearing a TRISA bit (= 0) will make the corresponding PORTA pin an output (i.e., enables output driver and puts the contents of the output latch on the selected pin). The exception is RA3, which is input only and its TRIS bit will always read as '1'. Example 4-1 shows how to initialize PORTA.

Reading the PORTA register (Register 4-1) reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the

#### REGISTER 4-1: PORTA: PORTA REGISTER

port pins are read, this value is modified and then written to the PORT data latch. RA3 reads '0' when MCLRE = 1.

The TRISA register controls the direction of the PORTA pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISA register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL register must be initialized to    |

|-------|----------------------------------------------|

|       | configure an analog channel as a digital     |

|       | input. Pins configured as analog inputs will |

|       | read '0' and cannot generate an interrupt.   |

#### EXAMPLE 4-1: INITIALIZING PORTA

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| CLRF  | PORTA       | ;Init PORTA            |

| BSF   | STATUS, RPO | ;Bank 1                |

| CLRF  | ANSEL       | ;digital I/O           |

| MOVLW | 0Ch         | ;Set RA<3:2> as inputs |

| MOVWF | TRISA       | ;and set RA<5:4,1:0>   |

|       |             | ;as outputs            |

| BCF   | STATUS, RPO | ;Bank 0                |

|       |             |                        |

| U-0   | U-0 | R/W-x | R/W-0 | R-x | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| —     | —   | RA5   | RA4   | RA3 | RA2   | RA1   | RA0   |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:       |         |                                        |                                          |            |

|---------------|---------|----------------------------------------|------------------------------------------|------------|

| R = Readab    | le bit  | W = Writable bit                       | U = Unimplemented bit, r                 | ead as '0' |

| -n = Value at | t POR   | '1' = Bit is set                       | 0' = Bit is cleared $x = Bit is unknown$ |            |

| hit 7 C       | Unimala | mented Dood op (o)                     |                                          |            |

| bit 7-6       | Unimple | mented: Read as '0'                    |                                          |            |

| bit 5-0       |         | : PORTA I/O Pin bit<br>TA pin is > VIH |                                          |            |

1 = PORTA pin is > VIH

0 = PORTA pin is < VIL

### REGISTER 4-2: TRISA: PORTA TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R-1    | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISA<5:0>: PORTA Tri-State Control bit

1 = PORTA pin configured as an input (tri-stated)

0 = PORTA pin configured as an output

Note 1: TRISA<3> always reads '1'.

2: TRISA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

bit 5-0

| U-0                                | U-0                                  | R/W-1                      | R/W-1                                   | U-0 | R/W-1                              | R/W-1 | R/W-1 |  |

|------------------------------------|--------------------------------------|----------------------------|-----------------------------------------|-----|------------------------------------|-------|-------|--|

|                                    | —                                    | WPUA5                      | WPUA4                                   | —   | WPUA2                              | WPUA1 | WPUA0 |  |

| bit 7                              |                                      |                            |                                         |     |                                    |       | bit 0 |  |

|                                    |                                      |                            |                                         |     |                                    |       |       |  |

| Legend:                            |                                      |                            |                                         |     |                                    |       |       |  |

| R = Readable bit W =               |                                      | W = Writable               | W = Writable bit                        |     | U = Unimplemented bit, read as '0' |       |       |  |

| -n = Value at POR '1' = Bit is set |                                      |                            | '0' = Bit is cleared x = Bit is unknown |     | nown                               |       |       |  |

|                                    |                                      |                            |                                         |     |                                    |       |       |  |

| bit 7-6                            | Unimplemen                           | Unimplemented: Read as '0' |                                         |     |                                    |       |       |  |

| bit 5-4                            | WPUA<5:4>: Weak Pull-up Control bits |                            |                                         |     |                                    |       |       |  |

|                                    | 1 = Pull-up enabled                  |                            |                                         |     |                                    |       |       |  |

|                                    | 0 = Pull-up disabled                 |                            |                                         |     |                                    |       |       |  |

#### REGISTER 4-4: WPUA: WEAK PULL-UP PORTA REGISTER

bit 3Unimplemented: Read as '0'bit 2-0WPUA<2:0>: Weak Pull-up Control bits

- - 1 =Pull-up enabled 0 =Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

- **3:** The RA3 pull-up is enabled when configured as MCLR and disabled as an input in the Configuration Word.

- 4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

### REGISTER 4-5: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

# REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (CONTINUED)

| bit 2 | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>TMR1CS = 1:</u>                                                                                                                                 |

|       | 1 = Do not synchronize external clock input                                                                                                        |

|       | 0 = Synchronize external clock input                                                                                                               |

|       | <u>TMR1CS = 0:</u>                                                                                                                                 |

|       | This bit is ignored. Timer1 uses the internal clock                                                                                                |

| bit 1 | TMR1CS: Timer1 Clock Source Select bit                                                                                                             |

|       | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock<br><u>If TMR1ACS = 0:</u><br>FOSC/4<br><u>If TMR1ACS = 1:</u><br>FOSC |

| bit 0 | <b>TMR1ON:</b> Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1                                                                             |

Note 1: T1GINV bit inverts the Timer1 gate logic, regardless of source.

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CM2CON1 register, as a Timer1 gate source.

| R/W-0        | R-0                                                    | R/W-0                                                                                                        | R/W-0                                           | U-0              | R/W-0            | R/W-0            | R/W-0         |

|--------------|--------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-------------------------------------------------|------------------|------------------|------------------|---------------|

| C2ON         | C2OUT                                                  | C2OE                                                                                                         | C2POL                                           | —                | C2R              | C2CH1            | C2CH0         |

| bit 7        |                                                        |                                                                                                              |                                                 |                  |                  |                  | bit (         |

| Legend:      |                                                        |                                                                                                              |                                                 |                  |                  |                  |               |

| R = Readat   | ole bit                                                | W = Writable                                                                                                 | bit                                             | U = Unimple      | emented bit, rea | ad as '0'        |               |

| -n = Value a | at POR                                                 | '1' = Bit is set                                                                                             |                                                 | ʻ0' = Bit is cl  | eared            | x = Bit is unki  | nown          |

| bit 7        | C2ON: Com                                              | parator C2 Enal                                                                                              | ble bit                                         |                  |                  |                  |               |

|              | 1 = Compara                                            | tor C2 is enable<br>tor C2 is disabl                                                                         | ed                                              |                  |                  |                  |               |

| bit 6        | C2OUT: Corr                                            | nparator C2 Ou                                                                                               | tput bit                                        |                  |                  |                  |               |

|              | C2OUT = 0 v $C2OUT = 1 v$ $If C2POL = 0$ $C2OUT = 1 v$ | <u>(inverted polar</u><br>when C2VIN+ ><br>when C2VIN+ <<br>(non-inverted)<br>when C2VIN+ ><br>when C2VIN+ < | C2VIN-<br>C2VIN-<br><u>polarity):</u><br>C2VIN- |                  |                  |                  |               |

| bit 5        | 1 = C2OUT is                                           | parator C2 Outp<br>s present on C2<br>s internal only                                                        |                                                 |                  |                  |                  |               |

| bit 4        | 1 = C2OUT                                              | nparator C2 Ou<br>ogic is inverted<br>ogic is not inve                                                       | . ,                                             | Select bit       |                  |                  |               |

| bit 3        | Unimplemer                                             | nted: Read as '                                                                                              | 0'                                              |                  |                  |                  |               |

| bit 2        | C2R: Compa                                             | rator C2 Refere                                                                                              | ence Select bi                                  | ts (non-invertii | ng input)        |                  |               |

|              |                                                        | connects to C2                                                                                               |                                                 |                  |                  |                  |               |

| bit 1-0      | C2CH<1:0>:                                             | Comparator C                                                                                                 | 2 Channel Sel                                   | lect bits        |                  |                  |               |

|              | 01 = C2VIN-<br>10 = C2VIN-                             | pin of C2 conne<br>pin of C2 conne<br>pin of C2 conne<br>pin of C2 conne                                     | ects to C12IN1<br>ects to C12IN2                | 1-<br>2-         |                  |                  |               |

| Note 1: (    | Comparator outpu                                       | -                                                                                                            |                                                 |                  | 20E = 1, C201    | N = 1 and corres | sponding port |

# REGISTER 8-2: CM2CON0: COMPARATOR 2 CONTROL REGISTER 0

**Note 1:** Comparator output requires the following three conditions: C2OE = 1, C2ON = 1 and corresponding port TRIS bit = 0.

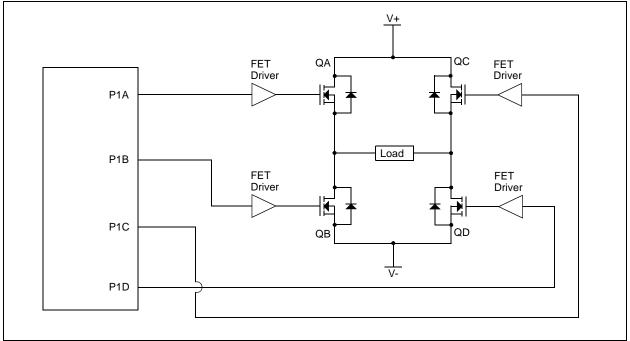

#### 10.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 10-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 10-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 10-11. P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

# FIGURE 10-10: EXAMPLE OF FULL-BRIDGE APPLICATION

# 12.4 Interrupts

The PIC16F610/616/16HV610/616 has multiple sources of interrupt:

- External Interrupt RA2/INT

- Timer0 Overflow Interrupt

- PORTA Change Interrupts

- 2 Comparator Interrupts

- A/D Interrupt (PIC16F616/16HV616 only)

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt (PIC16F616/16HV616 only)

- Enhanced CCP Interrupt (PIC16F616/16HV616 only)

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

The Global Interrupt Enable bit, GIE of the INTCON register, enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register and PIE1 register. GIE is cleared on Reset.

When an interrupt is serviced, the following actions occur automatically:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INT-CON register:

- INT Pin Interrupt

- PORTA Change Interrupt

- Timer0 Overflow Interrupt

The peripheral interrupt flags are contained in the special register, PIR1. The corresponding interrupt enable bit is contained in special register, PIE1.

The following interrupt flags are contained in the PIR1 register:

- A/D Interrupt

- 2 Comparator Interrupts

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

- Enhanced CCP Interrupt

For external interrupt events, such as the INT pin or PORTA change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 12-8). The latency is the same for one or twocycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, ADC, Enhanced CCP modules, refer to the respective peripheral section.

#### 12.4.1 RA2/INT INTERRUPT

The external interrupt on the RA2/INT pin is edgetriggered; either on the rising edge if the INTEDG bit of the OPTION register is set, or the falling edge, if the INTEDG bit is clear. When a valid edge appears on the RA2/INT pin, the INTF bit of the INTCON register is set. This interrupt can be disabled by clearing the INTE control bit of the INTCON register. The INTF bit must be cleared by software in the Interrupt Service Routine before re-enabling this interrupt. The RA2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. See **Section 12.7** "**Power-Down Mode (Sleep)**" for details on Sleep and Figure 12-9 for timing of wake-up from Sleep through RA2/INT interrupt.

Note: The ANSEL register must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0' and cannot generate an interrupt.

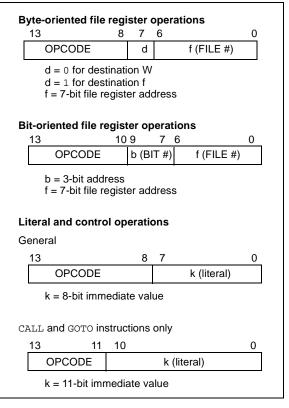

# 13.0 INSTRUCTION SET SUMMARY

The PIC16F610/616/16HV610/616 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the  $MPASM^{TM}$  assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 13.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (RMW) operation. The register is read, the data is modified, and the result is stored according to either the instruction or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                     |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                            |

| W     | Working register (accumulator)                                                                                                                                                  |

| b     | Bit address within an 8-bit file register                                                                                                                                       |

| k     | Literal field, constant data or label                                                                                                                                           |

| x     | Don't care location (= 0 or 1).<br>The assembler will generate code with $x = 0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                             |

| PC    | Program Counter                                                                                                                                                                 |

| TO    | Time-out bit                                                                                                                                                                    |

| С     | Carry bit                                                                                                                                                                       |

| DC    | Digit carry bit                                                                                                                                                                 |

| Z     | Zero bit                                                                                                                                                                        |

| PD    | Power-down bit                                                                                                                                                                  |

#### FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| ADDLW            | Add literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDLW k                                                                                                   |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |

| Status Affected: | C, DC, Z                                                                                                                                                                           |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |

| BSF              | Bit Set f                                                           |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $1 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is set.                                     |

| ANDLW            | AND literal with W                                                                                                     |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] ANDLW k                                                                                                      |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |  |  |  |  |  |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |  |  |  |  |  |

# 13.2 Instruction Descriptions

| BTFSS            | Bit Test f, Skip if Set                                                                                                                                                                                           |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] BTFSS f,b                                                                                                                                                                                               |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$0 \le b < 7$                                                                                                                                                                                |  |  |  |  |  |

| Operation:       | skip if (f <b>) = 1</b>                                                                                                                                                                                           |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                              |  |  |  |  |  |

| Description:     | If bit 'b' in register 'f' is '0', the next<br>instruction is executed.<br>If bit 'b' is '1', then the next<br>instruction is discarded and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |  |  |  |  |  |

| CLRWDT           | Clear Watchdog Timer                                                                                                              |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] CLRWDT                                                                                                                    |  |  |  |  |  |

| Operands:        | None                                                                                                                              |  |  |  |  |  |

| Operation:       | $00h \rightarrow WDT$<br>$0 \rightarrow WDT \text{ prescaler,}$<br>$1 \rightarrow \overline{TO}$<br>$1 \rightarrow \overline{PD}$ |  |  |  |  |  |

| Status Affected: | TO, PD                                                                                                                            |  |  |  |  |  |

| Description:     | CLRWDT instruction resets the<br>Watchdog Timer. It also resets the<br>prescaler of the WDT.<br>Status bits TO and PD are set.    |  |  |  |  |  |

| CALL             | Call Subroutine                                                                                                                                                                                                                               |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] CALL k                                                                                                                                                                                                                       |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                                                                            |  |  |  |  |  |

| Operation:       | (PC)+ 1→ TOS,<br>k → PC<10:0>,<br>(PCLATH<4:3>) → PC<12:11>                                                                                                                                                                                   |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                                                                          |  |  |  |  |  |

| Description:     | Call Subroutine. First, return<br>address (PC + 1) is pushed onto<br>the stack. The eleven-bit<br>immediate address is loaded into<br>PC bits <10:0>. The upper bits of<br>the PC are loaded from PCLATH.<br>CALL is a two-cycle instruction. |  |  |  |  |  |

| COMF             | Complement f                                                                                                                                                   |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] COMF f,d                                                                                                                                      |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0\leq f\leq 127\\ d\in [0,1] \end{array}$                                                                                                    |  |  |  |  |  |

| Operation:       | $(\overline{f}) \rightarrow (destination)$                                                                                                                     |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                              |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>complemented. If 'd' is '0', the<br>result is stored in W. If 'd' is '1',<br>the result is stored back in<br>register 'f'. |  |  |  |  |  |

Decrement f

[label] DECF f,d

| CLRF             | Clear f                                                                                    |  |  |  |

|------------------|--------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [label]CLRF f                                                                              |  |  |  |

| Operands:        | $0 \le f \le 127$                                                                          |  |  |  |

| Operation:       | $\begin{array}{l} \text{O0h} \rightarrow (\text{f}) \\ 1 \rightarrow \text{Z} \end{array}$ |  |  |  |

| Status Affected: | Z                                                                                          |  |  |  |

| Description:     | The contents of register 'f' are<br>cleared and the Z bit is set.                          |  |  |  |

| 0 | perands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                               |  |  |  |  |

|---|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 0 | peration:       | (f) - 1 $\rightarrow$ (destination)                                                                                                             |  |  |  |  |

| S | tatus Affected: | Z                                                                                                                                               |  |  |  |  |

| D | escription:     | Decrement register 'f'. If 'd' is '0<br>the result is stored in the W<br>register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

DECF

Syntax:

| CLRW             | Clear W                                                               |  |  |  |  |

|------------------|-----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ label ] CLRW                                                        |  |  |  |  |

| Operands:        | None                                                                  |  |  |  |  |

| Operation:       | $\begin{array}{l} 00h \rightarrow (W) \\ 1 \rightarrow Z \end{array}$ |  |  |  |  |

| Status Affected: | Z                                                                     |  |  |  |  |

| Description:     | W register is cleared. Zero bit (Z) is set.                           |  |  |  |  |

is '0',

#### 15.6 DC Characteristics: PIC16HV610/616- I (Industrial)

| DC CHARACTERISTICSStandard Operating Conditions (unless otherwise stated)<br>Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |                                                  |     |            |     |       |            |                                                |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|-----|------------|-----|-------|------------|------------------------------------------------|--|--|

| Param                                                                                                                                                    |                                                  |     | <b>.</b> . |     |       | Conditions |                                                |  |  |

| No.                                                                                                                                                      | Device Characteristics                           | Min | Тур†       | Мах | Units | VDD        | Note                                           |  |  |

| D020                                                                                                                                                     | Power-down Base<br>Current(IPD) <sup>(2,3)</sup> | -   | 135        | 200 | μA    | 2.0        | WDT, BOR, Comparators, VREF and T1OSC disabled |  |  |

|                                                                                                                                                          |                                                  |     | 210        | 280 | μΑ    | 3.0        |                                                |  |  |

|                                                                                                                                                          | PIC16HV610/616                                   |     | 260        | 350 | μA    | 4.5        |                                                |  |  |

| D021                                                                                                                                                     |                                                  |     | 135        | 200 | μA    | 2.0        | WDT Current <sup>(1)</sup>                     |  |  |

|                                                                                                                                                          |                                                  |     | 210        | 285 | μA    | 3.0        |                                                |  |  |

|                                                                                                                                                          |                                                  |     | 265        | 360 | μΑ    | 4.5        |                                                |  |  |

| D022                                                                                                                                                     |                                                  |     | 215        | 285 | μA    | 3.0        | BOR Current <sup>(1)</sup>                     |  |  |

|                                                                                                                                                          |                                                  |     | 265        | 360 | μΑ    | 4.5        |                                                |  |  |

| D023                                                                                                                                                     |                                                  |     | 240        | 340 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , both       |  |  |

|                                                                                                                                                          |                                                  |     | 320        | 420 | μΑ    | 3.0        | comparators enabled                            |  |  |

|                                                                                                                                                          |                                                  |     | 370        | 500 | μΑ    | 4.5        |                                                |  |  |

| D024                                                                                                                                                     |                                                  |     | 185        | 270 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , single     |  |  |

|                                                                                                                                                          |                                                  |     | 265        | 350 | μΑ    | 3.0        | comparator enabled                             |  |  |

|                                                                                                                                                          |                                                  |     | 320        | 430 | μΑ    | 4.5        |                                                |  |  |

| D025                                                                                                                                                     |                                                  | _   | 165        | 235 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)      |  |  |

|                                                                                                                                                          |                                                  |     | 255        | 330 | μΑ    | 3.0        |                                                |  |  |

|                                                                                                                                                          |                                                  |     | 330        | 430 | μΑ    | 4.5        |                                                |  |  |

| D026*                                                                                                                                                    |                                                  |     | 175        | 245 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)       |  |  |

|                                                                                                                                                          |                                                  |     | 275        | 350 | μΑ    | 3.0        |                                                |  |  |

|                                                                                                                                                          |                                                  |     | 355        | 450 | μΑ    | 4.5        |                                                |  |  |

| D027                                                                                                                                                     |                                                  | —   | 140        | 205 | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz      |  |  |

|                                                                                                                                                          |                                                  |     | 220        | 290 | μΑ    | 3.0        |                                                |  |  |

|                                                                                                                                                          |                                                  |     | 270        | 360 | μΑ    | 4.5        |                                                |  |  |

| D028                                                                                                                                                     |                                                  | —   | 210        | 280 | μΑ    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in  |  |  |

|                                                                                                                                                          |                                                  | _   | 260        | 350 | μΑ    | 4.5        | progress                                       |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

3: Shunt regulator is always enabled and always draws operating current.

## 15.9 DC Characteristics: PIC16F610/616/16HV610/616- I (Industrial) PIC16F610/616/16HV610/616 - E (Extended)

| DC CHARACTERISTICS |       |                                                        |      |            | less otherwise stated)<br>TA $\leq$ +85°C for industrial<br>TA $\leq$ +125°C for extended |      |                                                                        |

|--------------------|-------|--------------------------------------------------------|------|------------|-------------------------------------------------------------------------------------------|------|------------------------------------------------------------------------|

| Param<br>No.       | Sym   | Characteristic                                         | Min  | Min Typ† M |                                                                                           |      | Conditions                                                             |

| D101*              | COSC2 | Capacitive Loading Specs on<br>Output Pins<br>OSC2 pin | _    | _          | 15                                                                                        | pF   | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1 |

| D101A*             | Сю    | All I/O pins                                           | _    | _          | 50                                                                                        | pF   |                                                                        |

|                    |       | Program Flash Memory                                   |      |            |                                                                                           |      |                                                                        |

| D130               | Eр    | Cell Endurance                                         | 10K  | 100K       | _                                                                                         | E/W  | $-40^{\circ}C \leq TA \leq +85^{\circ}C$                               |

| D130A              | ED    | Cell Endurance                                         | 1K   | 10K        | _                                                                                         | E/W  | $+85^{\circ}C \le TA \le +125^{\circ}C$                                |

| D131               | Vpr   | VDD for Read                                           | Vmin | —          | 5.5                                                                                       | V    | VMIN = Minimum operating<br>voltage                                    |

| D132               | VPEW  | VDD for Erase/Write                                    | 4.5  | _          | 5.5                                                                                       | V    |                                                                        |

| D133               | TPEW  | Erase/Write cycle time                                 | _    | 2          | 2.5                                                                                       | ms   |                                                                        |

| D134               | Tretd | Characteristic Retention                               | 40   | -          | —                                                                                         | Year | Provided no other specifications are violated                          |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

| TABLE 15-18. OSCILLATOR FARAMETERS FOR FICTOR 010 - 11 (high temp.) |        |                                                |                        |       |     |     | _   |                                                                                                                                |

|---------------------------------------------------------------------|--------|------------------------------------------------|------------------------|-------|-----|-----|-----|--------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                        | Sym    | Characteristic                                 | Frequency<br>Tolerance | Units | Min | Тур | Max | Conditions                                                                                                                     |

| OS08                                                                | INTosc | Int. Calibrated INTOSC<br>Freq. <sup>(1)</sup> | ±10%                   | MHz   | 7.2 | 8.0 |     | $\begin{array}{l} 2.0V \leq V \text{DD} \leq 5.5V \\ -40^{\circ}\text{C} \leq T \text{A} \leq 150^{\circ}\text{C} \end{array}$ |

## TABLE 15-18: OSCILLATOR PARAMETERS FOR PIC16F616 - H (High Temp.)

**Note 1:** To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1 μF and 0.01 μF values in parallel are recommended.

#### TABLE 15-19: COMPARATOR SPECIFICATIONS FOR PIC16F616 – H (High Temp.)

| Param<br>No. | Sym | Characteristic       | Units | Min | Тур | Max | Conditions    |

|--------------|-----|----------------------|-------|-----|-----|-----|---------------|

| CM01         | Vos | Input Offset Voltage | mV    |     | ±5  | ±20 | (VDD - 1.5)/2 |

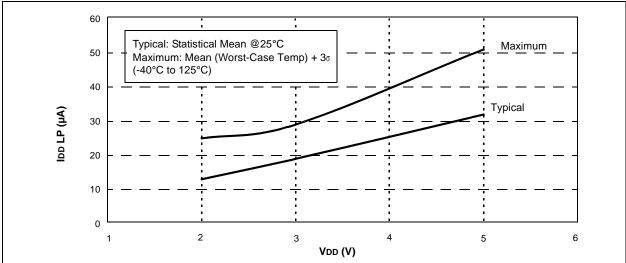

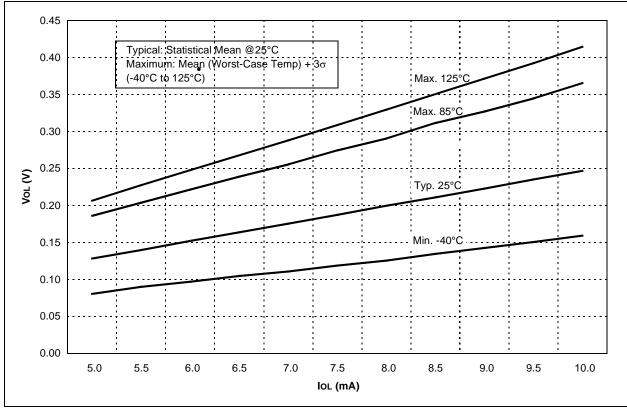

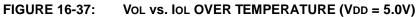

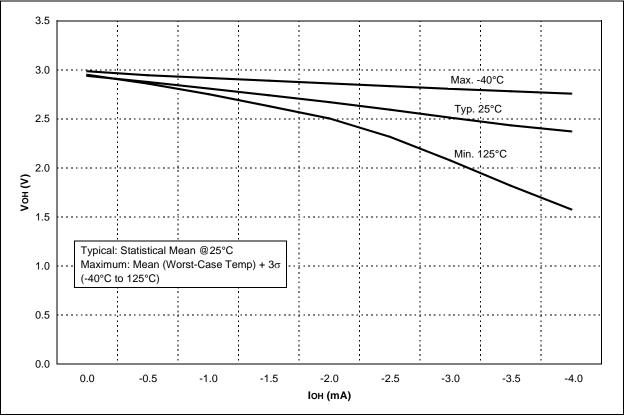

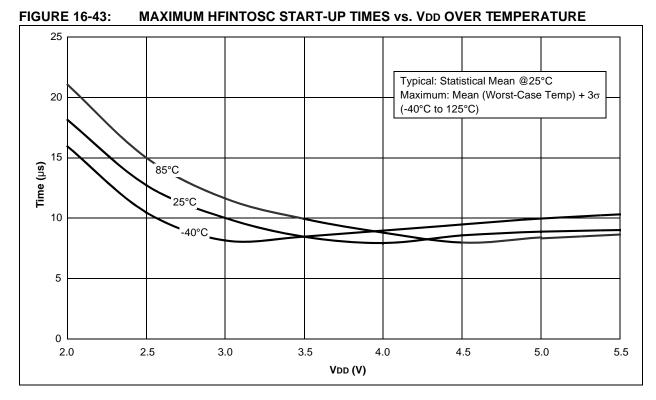

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

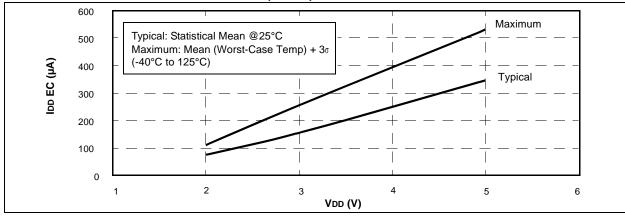

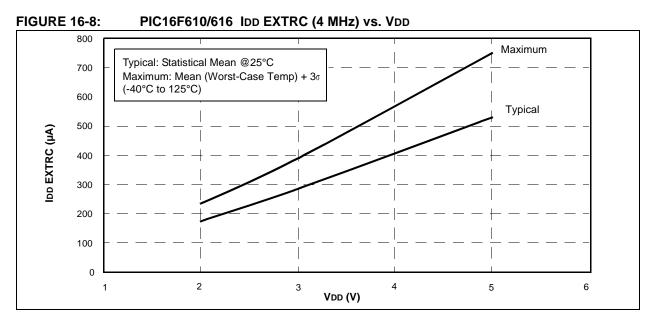

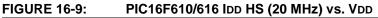

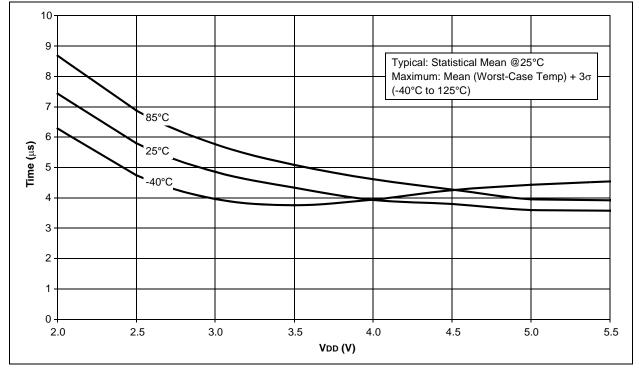

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where s is a standard deviation, over each temperature range.

### FIGURE 16-2: PIC16F610/616 IDD EC (1 MHz) vs. VDD

| Initializing PORTC42                                |

|-----------------------------------------------------|

| Saving Status and W Registers in RAM121             |

| Code Protection                                     |

| Comparator                                          |

| C2OUT as T1 Gate65                                  |

| Operation57                                         |

| Operation During Sleep61                            |

| Response Time                                       |

| Synchronizing COUT w/Timer165                       |

| Comparator Analog Input Connection Considerations64 |

| Comparator Hysteresis                               |

| Comparator Module                                   |

| Associated registers67                              |

| C1 Output State Versus Input Conditions             |

| Comparator Voltage Reference (CVREF)70              |

| Effects of a Reset61                                |

| Comparator Voltage Reference (CVREF)                |

| Response Time                                       |

| Comparator Voltage Reference (CVREF)                |

| Specifications164                                   |

| Comparators                                         |

| C2OUT as T1 Gate50                                  |

| Effects of a Reset61                                |

| Specifications164                                   |

| Compare Module. See Enhanced Capture/Compare/PWM    |

| (ECCP)                                              |

| CONFIG Register                                     |

| Configuration Bits109                               |

| CPU Features                                        |

| Customer Change Notification Service                |

| Customer Notification Service                       |

| Customer Support                                    |

|                                                     |

# D

| Data Memory               | 14       |

|---------------------------|----------|

| DC and AC Characteristics |          |

| Graphs and Tables         |          |

| DC Characteristics        |          |

| Extended and Industrial   | 153, 154 |

| Industrial and Extended   |          |

| Development Support       |          |

| Device Overview           | 9        |

|                           |          |

# Е

| ECCP. See Enhanced Capture/Compare/PWM        |       |

|-----------------------------------------------|-------|

| ECCPAS Register                               | . 102 |

| Effects of Reset                              |       |

| PWM mode                                      | 92    |

| Electrical Specifications                     |       |

| Enhanced Capture/Compare/PWM                  | 85    |

| Enhanced Capture/Compare/PWM (ECCP)           |       |

| Enhanced PWM Mode                             | 93    |

| Auto-Restart                                  | . 103 |

| Auto-shutdown                                 | . 102 |

| Direction Change in Full-Bridge Output Mode   | 99    |

| Full-Bridge Application                       | 97    |

| Full-Bridge Mode                              | 97    |

| Half-Bridge Application                       | 96    |

| Half-Bridge Application Examples              | . 104 |

| Half-Bridge Mode                              |       |

| Output Relationships (Active-High and Active- | Low)  |

| 94                                            |       |

| Output Relationships Diagram                  | 95    |

| Programmable Dead Band Delay                  | . 104 |

| Shoot-through Current                         |       |

| Start-up Considerations                       |       |

|                                               | -     |

| Specifications<br>Timer Resources                      |      |

|--------------------------------------------------------|------|

| Errata                                                 | 8    |

| F                                                      |      |

| Firmware Instructions<br>Fuses. See Configuration Bits | 129  |

|                                                        |      |

| G                                                      |      |

| General Purpose Register File                          | . 14 |

| Н                                                      |      |

| High Temperature Operation                             | 168  |

| 1                                                      |      |

| ID Locations                                           | 125  |

| In-Circuit Debugger                                    |      |

| In-Circuit Serial Programming (ICSP)                   | 126  |

| Indirect Addressing, INDF and FSR registers            |      |

| Instruction Format                                     |      |

| Instruction Set                                        |      |

| ADDLW                                                  |      |

| ADDWF                                                  |      |

| ANDLW<br>ANDWF                                         |      |

| ANDWF<br>MOVF                                          |      |

| BCF                                                    |      |

| BSF                                                    |      |

| BTFSC                                                  |      |

| BTFSS                                                  |      |

| CALL                                                   | 132  |

| CLRF                                                   | 132  |

| CLRW                                                   | 132  |

| CLRWDT                                                 |      |

| COMF                                                   |      |