# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2000                       |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                           |

| Supplier Device Package    | 14-SOIC                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f616-i-sl |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the peripheral interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | R/W-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-------|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE  | C1IE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |       |       |     |                       | bit 0  |

| Legend:                           |                 |                                                   |                               |                    |  |  |  |  |  |

|-----------------------------------|-----------------|---------------------------------------------------|-------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit W = Writable bit |                 | U = Unimplemented bit,                            | read as '0'                   |                    |  |  |  |  |  |

| -n = Value                        | e at POR        | '1' = Bit is set                                  | '0' = Bit is cleared          | x = Bit is unknown |  |  |  |  |  |

| L:4 7                             |                 |                                                   |                               |                    |  |  |  |  |  |

| bit 7                             | •               | mented: Read as '0'                               | (1)                           |                    |  |  |  |  |  |

| bit 6                             |                 | D Converter (ADC) Interrupt                       | Enable bit <sup>(1)</sup>     |                    |  |  |  |  |  |

|                                   |                 | les the ADC interrupt<br>bles the ADC interrupt   |                               |                    |  |  |  |  |  |

| bit 5                             | CCP1IE:         | CCP1 Interrupt Enable bit <sup>(1)</sup>          | 1                             |                    |  |  |  |  |  |

|                                   |                 | les the CCP1 interrupt<br>bles the CCP1 interrupt |                               |                    |  |  |  |  |  |

| bit 4                             | <b>C2IE:</b> Co | mparator C2 Interrupt Enable                      | e bit                         |                    |  |  |  |  |  |

|                                   | 1 = Enab        | les the Comparator C2 interr                      | rupt                          |                    |  |  |  |  |  |

|                                   | 0 = Disat       | oles the Comparator C2 inter                      | rupt                          |                    |  |  |  |  |  |

| bit 3                             | <b>C1IE:</b> Co | mparator C1 Interrupt Enabl                       | e bit                         |                    |  |  |  |  |  |

|                                   | 1 = Enab        | les the Comparator C1 interr                      | rupt                          |                    |  |  |  |  |  |

|                                   | 0 = Disat       | oles the Comparator C1 inter                      | rupt                          |                    |  |  |  |  |  |

| bit 2                             | Unimple         | mented: Read as '0'                               |                               |                    |  |  |  |  |  |

| bit 1                             | TMR2IE:         | Timer2 to PR2 Match Interru                       | upt Enable bit <sup>(1)</sup> |                    |  |  |  |  |  |

|                                   | 1 = Enab        | 1 = Enables the Timer2 to PR2 match interrupt     |                               |                    |  |  |  |  |  |

|                                   | 0 = Disat       | oles the Timer2 to PR2 matcl                      | h interrupt                   |                    |  |  |  |  |  |

| bit 0                             | TMR1IE:         | Timer1 Overflow Interrupt E                       | nable bit                     |                    |  |  |  |  |  |

|                                   | 1 = Enab        | les the Timer1 overflow inter                     | rupt                          |                    |  |  |  |  |  |

|                                   | 0 = Disat       | oles the Timer1 overflow inte                     | rrupt                         |                    |  |  |  |  |  |

| Note 1:                           | PIC16F616/16    | 6HV616 only. PIC16F610/16                         | HV610 unimplemented, read a   | as '0'.            |  |  |  |  |  |

### 3.0 OSCILLATOR MODULE

#### 3.1 Overview

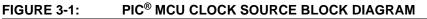

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured with a choice of two selectable speeds: internal or external system clock source.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

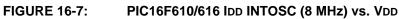

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The Internal Oscillator module provides a selectable system clock mode of either 4 MHz (Postscaler) or 8 MHz (INTOSC).

#### 3.3.4 EXTERNAL RC MODES

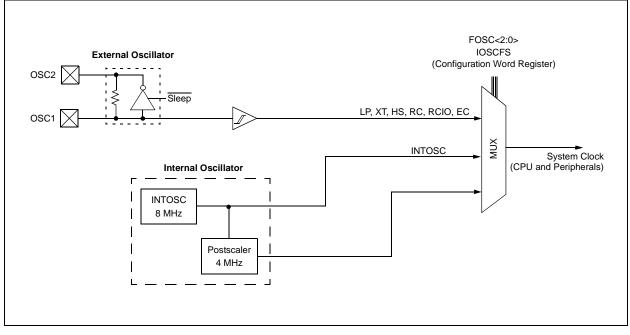

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

#### FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

#### 3.4 Internal Clock Modes

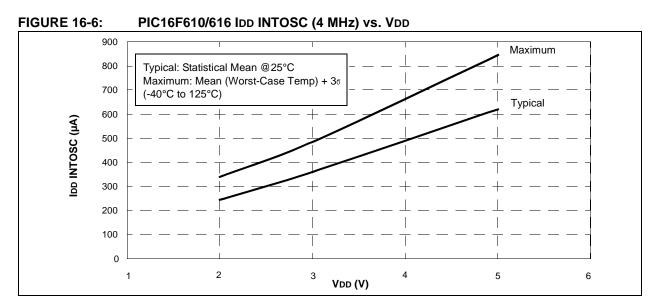

The Oscillator module provides a selectable system clock source of either 4 MHz or 8 MHz. The selectable frequency is configured through the IOSCFS bit of the Configuration Word.

The frequency of the internal oscillator can be can be user-adjusted via software using the OSCTUNE register.

#### 3.4.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 12.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

| U-0          | U-0                  | R/W-1                                | R/W-1 | U-0                                | R/W-1 | R/W-1              | R/W-1 |  |  |

|--------------|----------------------|--------------------------------------|-------|------------------------------------|-------|--------------------|-------|--|--|

|              | —                    | WPUA5                                | WPUA4 | _                                  | WPUA2 | WPUA1              | WPUA0 |  |  |

| bit 7        |                      |                                      |       |                                    |       |                    | bit 0 |  |  |

|              |                      |                                      |       |                                    |       |                    |       |  |  |

| Legend:      |                      |                                      |       |                                    |       |                    |       |  |  |

| R = Readal   | ble bit              | W = Writable                         | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |  |

| -n = Value a | at POR               | '1' = Bit is set                     |       | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |

|              |                      |                                      |       |                                    |       |                    |       |  |  |

| bit 7-6      | Unimplemen           | ted: Read as 'o                      | )'    |                                    |       |                    |       |  |  |

| bit 5-4      | WPUA<5:4>:           | WPUA<5:4>: Weak Pull-up Control bits |       |                                    |       |                    |       |  |  |

|              | 1 = Pull-up er       |                                      |       |                                    |       |                    |       |  |  |

|              | 0 = Pull-up disabled |                                      |       |                                    |       |                    |       |  |  |

#### REGISTER 4-4: WPUA: WEAK PULL-UP PORTA REGISTER

bit 3Unimplemented: Read as '0'bit 2-0WPUA<2:0>: Weak Pull-up Control bits

- - 1 =Pull-up enabled 0 =Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

- **3:** The RA3 pull-up is enabled when configured as MCLR and disabled as an input in the Configuration Word.

- 4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### REGISTER 4-5: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | IOCA5 | IOCA4 | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

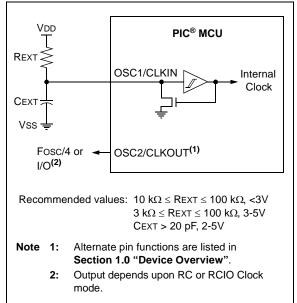

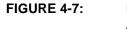

### 4.3.1 RC0/AN4<sup>(1)</sup>/C2IN+

The RC0 is configurable to function as one of the following:  $\label{eq:configurable}$

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to Comparator C2

#### 4.3.2 RC1/AN5<sup>(1)</sup>/C12IN1-

The RC1 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

an analog inverting input to the comparator

Note 1: PIC16F616/16HV616 only.

#### 4.3.3 RC2/AN6<sup>(1)</sup>/C12IN2-/P1D<sup>(1)</sup>

The RC2 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog input to Comparators C1 and C2

- a digital output from the Enhanced CCP<sup>(1)</sup>

#### 4.3.4 RC3/AN7<sup>(1)</sup>/C12IN3-/P1C<sup>(1)</sup>

The RC3 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to Comparators C1 and C2

- a digital output from the Enhanced CCP<sup>(1)</sup>

Note 1: PIC16F616/16HV616 only.

#### 7: BLOCK DIAGRAM OF RC2 AND RC3

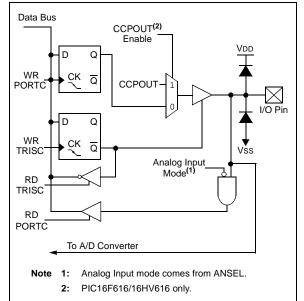

#### 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                 | R/W-0                 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|-----------------------|---------|---------|---------|--------|--------|--------|

| T1GINV <sup>(1)</sup> | TMR1GE <sup>(2)</sup> | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7                 |                       |         |         |         |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | <b>T1GINV:</b> Timer1 Gate Invert bit <sup>(1)</sup><br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                             |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup> If TMR1ON = 0:     This bit is ignored     If TMR1ON = 1:     1 = Timer1 counting is controlled by the Timer1 Gate function     0 = Timer1 is always counting            |

| bit 5-4 | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:8 Prescale Value<br>10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                          |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit<br><u>If INTOSC without CLKOUT oscillator is active:</u><br>1 = LP oscillator is enabled for Timer1 clock<br>0 = LP oscillator is off<br><u>Else:</u><br>This bit is ignored |

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER (CONTINUED)

| bit 2 | T1SYNC: Timer1 External Clock Input Synchronization Control bit                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <u>TMR1CS = 1:</u>                                                                                                                                 |

|       | 1 = Do not synchronize external clock input                                                                                                        |

|       | 0 = Synchronize external clock input                                                                                                               |

|       | <u>TMR1CS = 0:</u>                                                                                                                                 |

|       | This bit is ignored. Timer1 uses the internal clock                                                                                                |

| bit 1 | TMR1CS: Timer1 Clock Source Select bit                                                                                                             |

|       | 1 = External clock from T1CKI pin (on the rising edge)<br>0 = Internal clock<br><u>If TMR1ACS = 0:</u><br>FOSC/4<br><u>If TMR1ACS = 1:</u><br>FOSC |

| bit 0 | <b>TMR1ON:</b> Timer1 On bit<br>1 = Enables Timer1<br>0 = Stops Timer1                                                                             |

Note 1: T1GINV bit inverts the Timer1 gate logic, regardless of source.

2: TMR1GE bit must be set to use either T1G pin or C2OUT, as selected by the T1GSS bit of the CM2CON1 register, as a Timer1 gate source.

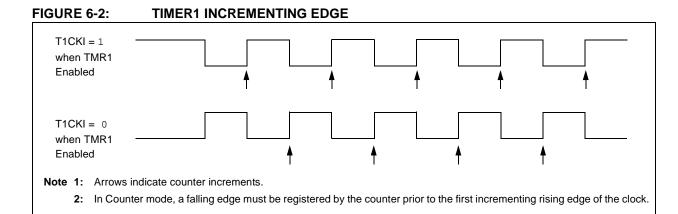

#### 10.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 10-6 shows the pin assignments for each Enhanced PWM mode.

Figure 10-5 shows an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

#### FIGURE 10-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- 3: Any pin not used by an Enhanced PWM mode is available for alternate pin functions

#### TABLE 10-6: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M | CCP1/P1A | P1B | P1C | P1D |

|----------------------|-----|----------|-----|-----|-----|

| Single               | 00  | Yes      | No  | No  | No  |

| Half-Bridge          | 10  | Yes      | Yes | No  | No  |

| Full-Bridge, Forward | 01  | Yes      | Yes | Yes | Yes |

| Full-Bridge, Reverse | 11  | Yes      | Yes | Yes | Yes |

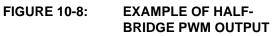

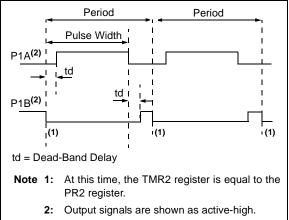

#### 10.4.1 HALF-BRIDGE MODE

In Half-Bridge mode, two pins are used as outputs to drive push-pull loads. The PWM output signal is output on the CCP1/P1A pin, while the complementary PWM output signal is output on the P1B pin (see Figure 10-8). This mode can be used for half-bridge applications, as shown in Figure 10-9, or for full-bridge applications, where four power switches are being modulated with two PWM signals.

In Half-Bridge mode, the programmable dead-band delay can be used to prevent shoot-through current in halfbridge power devices. The value of the PDC<6:0> bits of the PWM1CON register sets the number of instruction cycles before the output is driven active. If the value is greater than the duty cycle, the corresponding output remains inactive during the entire cycle. See **10.4.6 "Programmable Dead-Band Delay mode"** for more details of the dead-band delay operations. Since the P1A and P1B outputs are multiplexed with the PORT data latches, the associated TRIS bits must be cleared to configure P1A and P1B as outputs.

#### FIGURE 10-9: EXAMPLE OF HALF-BRIDGE APPLICATIONS

#### 10.4.3 START-UP CONSIDERATIONS

When any PWM mode is used, the application hardware must use the proper external pull-up and/or pull-down resistors on the PWM output pins.

Note: When the microcontroller is released from Reset, all of the I/O pins are in the highimpedance state. The external circuits must keep the power switch devices in the OFF state until the microcontroller drives the I/O pins with the proper signal levels or activates the PWM output(s).

The CCP1M<1:0> bits of the CCP1CON register allow the user to choose whether the PWM output signals are active-high or active-low for each pair of PWM output pins (P1A/P1C and P1B/P1D). The PWM output polarities must be selected before the PWM pins are configured as outputs. Changing the polarity configuration while the PWM pins are configured as outputs is not recommended since it may result in damage to the application circuits.

The P1A, P1B, P1C and P1D output latches may not be in the proper states when the PWM module is initialized. Enabling the PWM pins for output at the same time as the Enhanced PWM modes may cause damage to the application circuit. The Enhanced PWM modes must be enabled in the proper Output mode and complete a full PWM cycle before configuring the PWM pins as outputs. The completion of a full PWM cycle is indicated by the TMR2IF bit of the PIR1 register being set as the second PWM period begins.

### 12.0 SPECIAL FEATURES OF THE CPU

The PIC16F610/616/16HV610/616 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

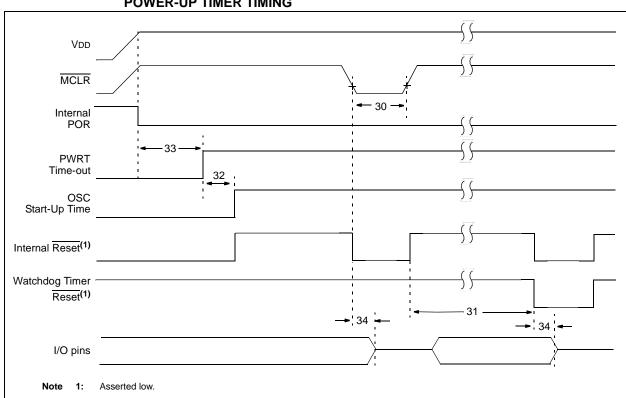

The PIC16F610/616/16HV610/616 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Powerup Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

#### 12.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See the *Memory Programming Specification* (DS41284) for more information.

#### 12.2 Calibration Bits

The 8 MHz internal oscillator is factory calibrated. These calibration values are stored in fuses located in the Calibration Word (2008h). The Calibration Word is not erased when using the specified bulk erase sequence in the *Memory Programming Specification* (DS41284) and thus, does not require reprogramming.

#### 12.3 Reset

The PIC16F610/616/16HV610/616 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

WDT wake-up does not cause register resets in the same manner as a WDT Reset since wake-up is viewed as the resumption of normal operation. TO and PD bits are set or cleared differently in different Reset situations, as indicated in Table 12-2. Software can use these bits to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

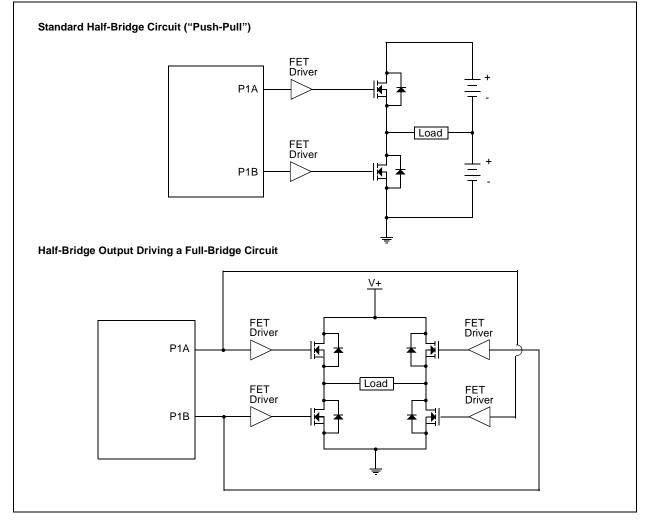

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse-width specifications.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

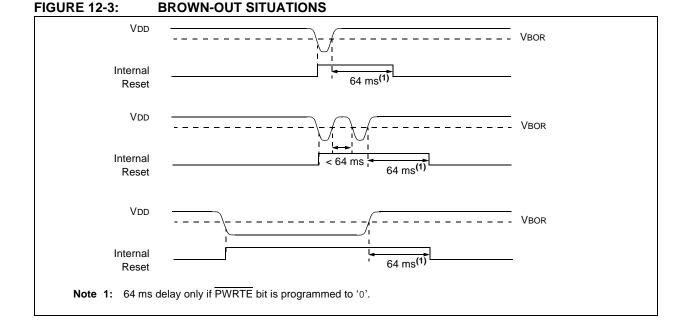

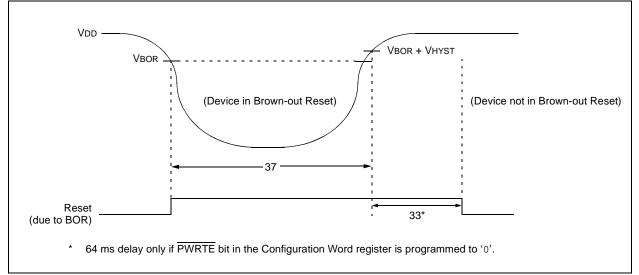

#### 12.3.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. Selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition.

A brown-out occurs when VDD falls below VBOR for greater than parameter TBOR (see **Section 15.0** "**Electrical Specifications**"). The brown-out condition will reset the device. This will occur regardless of VDD slew rate. A Brown-out Reset may not occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out Reset, Watchdog timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 12-3). If enabled, the Power-up Timer will be invoked by the Reset and keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the <u>PWRTE</u> bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

### 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

#### 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

#### 15.8 DC Characteristics: PIC16F610/616/16HV610/616- I (Industrial) PIC16F610/616/16HV610/616 - E (Extended)

| DC CHARACTERISTICS |      |                                           | $ \begin{array}{ll} \mbox{Standard Operating Conditions (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for extended} \end{array} $ |          |          |       |                                                                                                                               |

|--------------------|------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                            | Min                                                                                                                                                                                                                                                          | Тур†     | Мах      | Units | Conditions                                                                                                                    |

|                    | VIL  | Input Low Voltage                         |                                                                                                                                                                                                                                                              |          |          |       |                                                                                                                               |

|                    |      | I/O port:                                 |                                                                                                                                                                                                                                                              |          |          |       |                                                                                                                               |

| D030               |      | with TTL buffer                           | Vss                                                                                                                                                                                                                                                          | —        | 0.8      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                              |

| D030A              |      |                                           | Vss                                                                                                                                                                                                                                                          | —        | 0.15 VDD | V     | $2.0V \leq V\text{DD} \leq 4.5V$                                                                                              |

| D031               |      | with Schmitt Trigger buffer               | Vss                                                                                                                                                                                                                                                          | —        | 0.2 Vdd  | V     | $2.0V \leq V\text{DD} \leq 5.5V$                                                                                              |

| D032               |      | MCLR, OSC1 (RC mode)                      | Vss                                                                                                                                                                                                                                                          | —        | 0.2 Vdd  | V     |                                                                                                                               |

| D033               |      | OSC1 (XT and LP modes)                    | Vss                                                                                                                                                                                                                                                          | _        | 0.3      | V     |                                                                                                                               |

| D033A              |      | OSC1 (HS mode)                            | Vss                                                                                                                                                                                                                                                          | —        | 0.3 Vdd  | V     |                                                                                                                               |

|                    | Vih  | Input High Voltage<br>I/O ports:          |                                                                                                                                                                                                                                                              | _        |          |       |                                                                                                                               |

| D040               |      | with TTL buffer                           | 2.0                                                                                                                                                                                                                                                          | _        | Vdd      | V     | $4.5V \leq V\text{DD} \leq 5.5V$                                                                                              |

| D040A              |      |                                           | 0.25 Vdd + 0.8                                                                                                                                                                                                                                               |          | Vdd      | V     | $2.0V \leq V \text{DD} \leq 4.5 \text{V}$                                                                                     |

| D041               |      | with Schmitt Trigger buffer               | 0.8 Vdd                                                                                                                                                                                                                                                      |          | Vdd      | V     | $2.0V \leq V \text{DD} \leq 5.5 \text{V}$                                                                                     |

| D042               |      | MCLR                                      | 0.8 Vdd                                                                                                                                                                                                                                                      | —        | Vdd      | V     |                                                                                                                               |

| D043               |      | OSC1 (XT and LP modes)                    | 1.6                                                                                                                                                                                                                                                          | —        | Vdd      | V     |                                                                                                                               |

| D043A              |      | OSC1 (HS mode)                            | 0.7 Vdd                                                                                                                                                                                                                                                      | _        | Vdd      | V     |                                                                                                                               |

| D043B              |      | OSC1 (RC mode)                            | 0.9 Vdd                                                                                                                                                                                                                                                      | _        | Vdd      | V     | (Note 1)                                                                                                                      |

|                    | lı∟  | Input Leakage Current <sup>(2,3)</sup>    |                                                                                                                                                                                                                                                              |          |          |       |                                                                                                                               |

| D060               |      | I/O ports                                 | —                                                                                                                                                                                                                                                            | ± 0.1    | ± 1      | μA    | $\label{eq:VSS} \begin{split} &V{\sf SS} \leq V{\sf PIN} \leq V{\sf DD}, \\ &P{\sf in} \mbox{ at high-impedance} \end{split}$ |

| D061               |      | RA3/MCLR <sup>(3,4)</sup>                 | —                                                                                                                                                                                                                                                            | $\pm0.7$ | ± 5      | μΑ    | $VSS \leq VPIN \leq VDD$                                                                                                      |

| D063               |      | OSC1                                      | _                                                                                                                                                                                                                                                            | ± 0.1    | ± 5      | μΑ    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration                                                            |

| D070*              | Ipur | PORTA Weak Pull-up Current <sup>(5)</sup> | 50                                                                                                                                                                                                                                                           | 250      | 400      | μΑ    | VDD = 5.0V, VPIN = VSS                                                                                                        |

|                    | Vol  | Output Low Voltage                        | _                                                                                                                                                                                                                                                            | _        | 0.6      | V     | IOL = 7.0 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                  |

| D080               |      | I/O ports                                 | _                                                                                                                                                                                                                                                            | _        | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                   |

|                    | Vон  | Output High Voltage                       | Vdd - 0.7                                                                                                                                                                                                                                                    | _        | _        | V     | IOH = -2.5 mA, VDD = 4.5V,<br>-40°C to +125°C                                                                                 |

| D090               |      | I/O ports <sup>(2)</sup>                  | Vdd - 0.7                                                                                                                                                                                                                                                    | _        | _        | V     | IOH = -3.0 mA, VDD = 4.5V,<br>-40°C to +85°C                                                                                  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: This specification applies to RA3/MCLR configured as RA3 input with internal pull-up disabled.

5: This specification applies to all weak pull-up pins, including the weak pull-up on RA3/MCLR. When RA3/MCLR is configured as MCLR reset pin, the weak pull-up is always enabled.

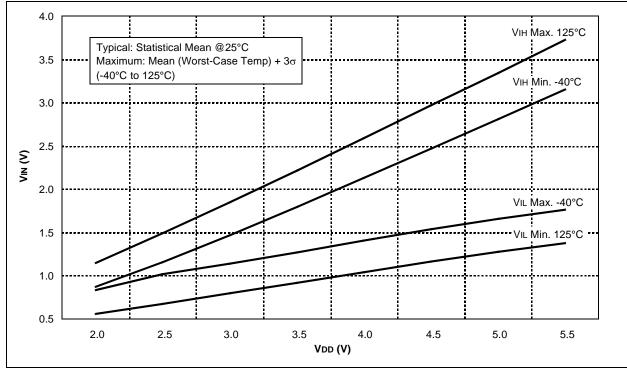

### FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

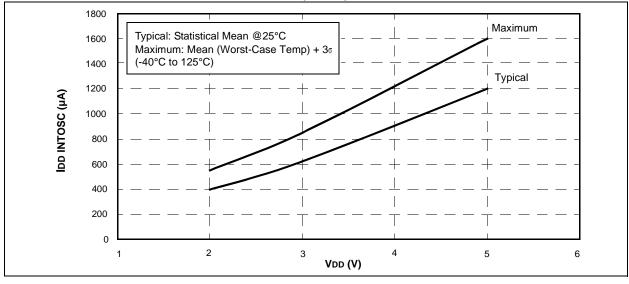

#### FIGURE 16-41: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

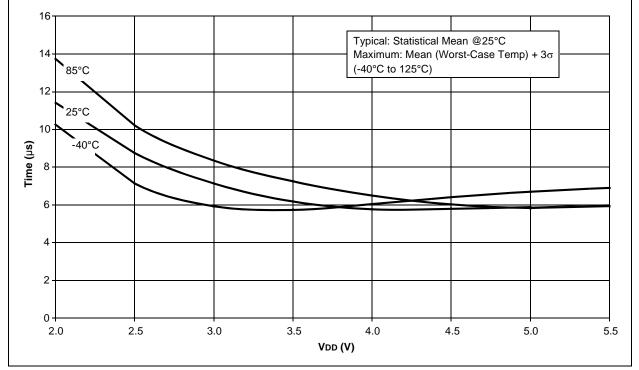

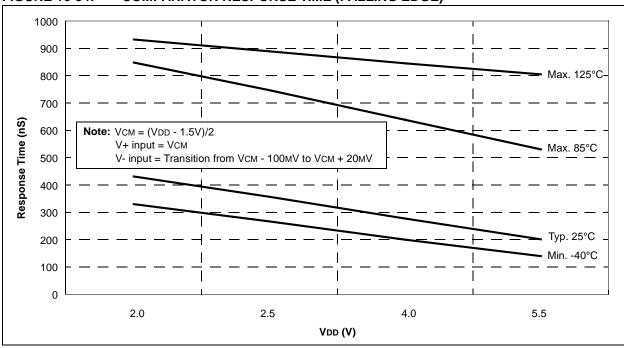

#### FIGURE 16-54: COMPARATOR RESPONSE TIME (FALLING EDGE)

### APPENDIX B: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{0}}$  devices to the <code>PIC16F6XX</code> Family of devices.

#### B.1 PIC16F676 to PIC16F610/616/16HV610/616

#### TABLE B-1: FEATURE COMPARISON

| Feature                    | PIC16F676     | PIC16F610/16HV610 | PIC16F616/16HV616 |

|----------------------------|---------------|-------------------|-------------------|

| Max Operating Speed        | 20 MHz        | 20 MHz            | 20 MHz            |

| Max Program Memory (Words) | 1024          | 1024              | 2048              |

| SRAM (bytes)               | 64            | 64                | 128               |

| A/D Resolution             | 10-bit        | None              | 10-bit            |

| Timers (8/16-bit)          | 1/1           | 1/1               | 2/1               |

| Oscillator Modes           | 8             | 8                 | 8                 |

| Brown-out Reset            | Y             | Y                 | Y                 |

| Internal Pull-ups          | RA0/1/2/4/5   | RA0/1/2/4/5, MCLR | RA0/1/2/4/5, MCLR |

| Interrupt-on-change        | RA0/1/2/3/4/5 | RA0/1/2/3/4/5     | RA0/1/2/3/4/5     |

| Comparator                 | 1             | 2                 | 2                 |

| ECCP                       | Ν             | Ν                 | Y                 |

| INTOSC Frequencies         | 4 MHz         | 4/8 MHz           | 4/8 MHz           |

| Internal Shunt Regulator   | Ν             | Y (PIC16HV610)    | Y (PIC16HV616)    |

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.