Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

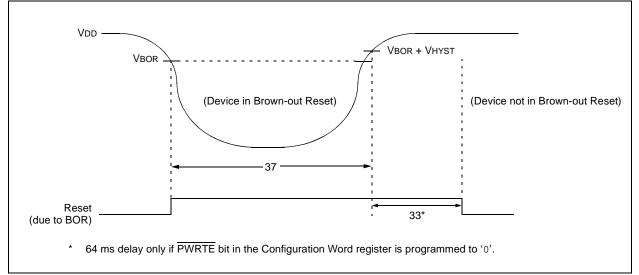

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                          |

| Supplier Device Package    | 14-TSSOP                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f616-i-st |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

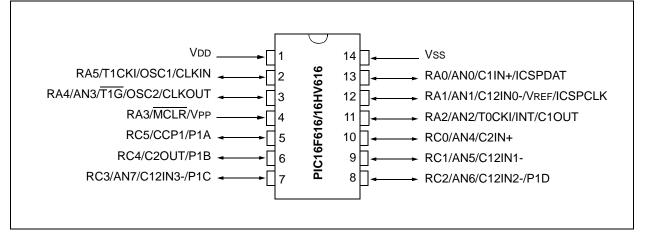

### PIC16F616/16HV616 14-Pin Diagram (PDIP, SOIC, TSSOP)

#### TABLE 2: PIC16F616/16HV616 14-PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР      | Interrupts | Pull-ups | Basic       |

|--------------------|-----|----------|-------------|-------|----------|------------|----------|-------------|

| RA0                | 13  | AN0      | C1IN+       |       | _        | IOC        | Y        | ICSPDAT     |

| RA1                | 12  | AN1/VREF | C12IN0-     |       | _        | IOC        | Y        | ICSPCLK     |

| RA2                | 11  | AN2      | C1OUT       | T0CKI | —        | INT/IOC    | Y        | —           |

| RA3 <sup>(1)</sup> | 4   | _        | —           | _     |          | IOC        | Y(2)     | MCLR/Vpp    |

| RA4                | 3   | AN3      | —           | T1G   | _        | IOC        | Y        | OSC2/CLKOUT |

| RA5                | 2   | —        | —           | T1CKI | -        | IOC        | Y        | OSC1/CLKIN  |

| RC0                | 10  | AN4      | C2IN+       | —     | —        | —          | —        | —           |

| RC1                | 9   | AN5      | C12IN1-     | _     |          | —          | —        | —           |

| RC2                | 8   | AN6      | C12IN2-     | _     | P1D      | —          | —        | —           |

| RC3                | 7   | AN7      | C12IN3-     | —     | P1C      | —          | —        | —           |

| RC4                | 6   | —        | C2OUT       | _     | P1B      | —          | —        | —           |

| RC5                | 5   | _        | —           | _     | CCP1/P1A | _          | _        | _           |

|                    | 1   | _        | —           |       | _        | _          | _        | Vdd         |

| _                  | 14  | _        |             | _     | _        | —          | —        | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### **TABLE 1-2:** PIC16F616/16HV616 PINOUT DESCRIPTION

| Name                         | Function | Input<br>Type | Output<br>Type | Description                                          |

|------------------------------|----------|---------------|----------------|------------------------------------------------------|

| RA0/AN0/C1IN+/ICSPDAT        | RA0      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                              | AN0      | AN            | _              | A/D Channel 0 input                                  |

|                              | C1IN+    | AN            | _              | Comparator C1 non-inverting input                    |

|                              | ICSPDAT  | ST            | CMOS           | Serial Programming Data I/O                          |

| RA1/AN1/C12IN0-/VREF/ICSPCLK | RA1      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                              | AN1      | AN            | _              | A/D Channel 1 input                                  |

|                              | C12IN0-  | AN            | _              | Comparators C1 and C2 inverting input                |

|                              | VREF     | AN            | _              | External Voltage Reference for A/D                   |

|                              | ICSPCLK  | ST            | _              | Serial Programming Clock                             |

| RA2/AN2/T0CKI/INT/C1OUT      | RA2      | ST            | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                              | AN2      | AN            | _              | A/D Channel 2 input                                  |

|                              | TOCKI    | ST            | —              | Timer0 clock input                                   |

|                              | INT      | ST            | —              | External Interrupt                                   |

|                              | C1OUT    | _             | CMOS           | Comparator C1 output                                 |

| RA3/MCLR/Vpp                 | RA3      | TTL           | _              | PORTA input with interrupt-on-change                 |

|                              | MCLR     | ST            | _              | Master Clear w/internal pull-up                      |

|                              | VPP      | HV            | _              | Programming voltage                                  |

| RA4/AN3/T1G/OSC2/CLKOUT      | RA4      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

| (A4/AN3/110/0302/0EK001      | AN3      | AN            |                | A/D Channel 3 input                                  |

|                              | TIG      |               |                |                                                      |

|                              |          | ST<br>—       |                | Timer1 gate (count enable)                           |

|                              | OSC2     |               | XTAL           | Crystal/Resonator                                    |

|                              | CLKOUT   |               | CMOS           | Fosc/4 output                                        |

| RA5/T1CKI/OSC1/CLKIN         | RA5      | TTL           | CMOS           | PORTA I/O with prog. pull-up and interrupt-on-change |

|                              | T1CKI    | ST            |                | Timer1 clock input                                   |

|                              | OSC1     | XTAL          | _              | Crystal/Resonator                                    |

|                              | CLKIN    | ST            | -              | External clock input/RC oscillator connection        |

| RC0/AN4/C2IN+                | RC0      | TTL           | CMOS           | PORTC I/O                                            |

|                              | AN4      | AN            | _              | A/D Channel 4 input                                  |

|                              | C2IN+    | AN            | —              | Comparator C2 non-inverting input                    |

| RC1/AN5/C12IN1-              | RC1      | TTL           | CMOS           | PORTC I/O                                            |

|                              | AN5      | AN            |                | A/D Channel 5 input                                  |

|                              | C12IN1-  | AN            | —              | Comparators C1 and C2 inverting input                |

| RC2/AN6/C12IN2-/P1D          | RC2      | TTL           | CMOS           | PORTC I/O                                            |

|                              | AN6      | AN            | _              | A/D Channel 6 input                                  |

|                              | C12IN2-  | AN            | —              | Comparators C1 and C2 inverting input                |

|                              | P1D      | —             | CMOS           | PWM output                                           |

| RC3/AN7/C12IN3-/P1C          | RC3      | TTL           | CMOS           | PORTC I/O                                            |

|                              | AN7      | AN            | —              | A/D Channel 7 input                                  |

|                              | C12IN3-  | AN            | —              | Comparators C1 and C2 inverting input                |

|                              | P1C      | —             | CMOS           | PWM output                                           |

| RC4/C2OUT/P1B                | RC4      | TTL           | CMOS           | PORTC I/O                                            |

|                              | C2OUT    | —             | CMOS           | Comparator C2 output                                 |

|                              | P1B      | —             | CMOS           | PWM output                                           |

| RC5/CCP1/P1A                 | RC5      | TTL           | CMOS           | PORTC I/O                                            |

|                              | CCP1     | ST            | CMOS           | Capture input/Compare output                         |

|                              | P1A      | —             | CMOS           | PWM output                                           |

| /dd                          | Vdd      | Power         |                | Positive supply                                      |

| Vss                          | Vss      | Power         | _              | Ground reference                                     |

AN = Analog input or outputCMOS = CMOS compatible input or outputHV = High VoltageST = Schmitt Trigger input with CMOS levelsTTL = TTL compatible inputXTAL = Crystal

NOTES:

#### 3.4.1.1 OSCTUNE Register

The oscillator is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-1). The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

#### REGISTER 3-1: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | —   | —   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 7-5 Unimplemented: Read as '0'

bit 4-0

| TUN<4:0>: Frequency Tuning bits                                               |  |

|-------------------------------------------------------------------------------|--|

| 01111 = Maximum frequency                                                     |  |

| 01110 =                                                                       |  |

| •                                                                             |  |

| •                                                                             |  |

| •                                                                             |  |

| 00001 =                                                                       |  |

| 00000 = Oscillator module is running at the manufacturer calibrated frequency |  |

| 11111 =                                                                       |  |

| •                                                                             |  |

| •                                                                             |  |

| •                                                                             |  |

| 10000 = Minimum frequency                                                     |  |

#### TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES

| Name                  | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|--------|-------|-------|-------|-------|-------|-------|-------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | IOSCFS | CP    | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | _                    | _                                              |

| OSCTUNE               | —      | —     | —     | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  | 0 0000               | u uuuu                                         |

**Legend:** x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

**Note 1:** Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 12-1) for operation of all register bits.

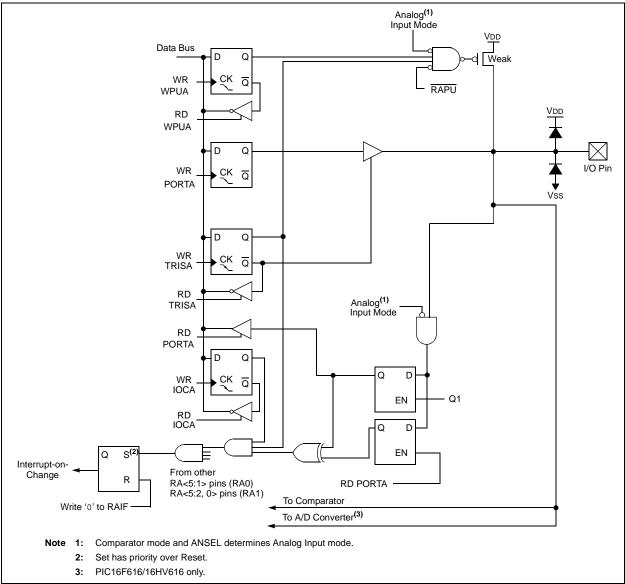

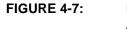

#### 4.2.4 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

#### 4.2.4.1 RA0/AN0<sup>(1)</sup>/C1IN+/ICSPDAT

Figure 4-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to the comparator

- In-Circuit Serial Programming data

#### 4.2.4.2 RA1/AN1<sup>(1)</sup>/C12IN0-/VREF<sup>(1)</sup>/ ICSPCLK

Figure 4-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to the comparator

- a voltage reference input for the ADC<sup>(1)</sup>

- In-Circuit Serial Programming clock

Note 1: PIC16F616/16HV616 only.

#### FIGURE 4-1: BLOCK DIAGRAM OF RA<1:0>

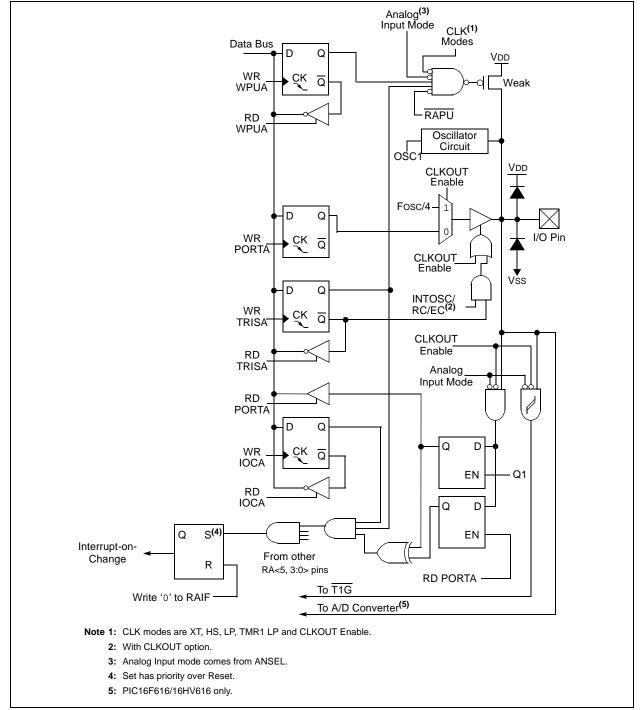

### 4.2.4.5 RA4/AN3<sup>(1)</sup>/T1G/OSC2/CLKOUT

Figure 4-4 shows the diagram for this pin. The RA4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- a Timer1 gate (count enable)

- a crystal/resonator connection

- · a clock output

- Note 1: PIC16F616/16HV616 only.

#### FIGURE 4-4: BLOCK DIAGRAM OF RA4

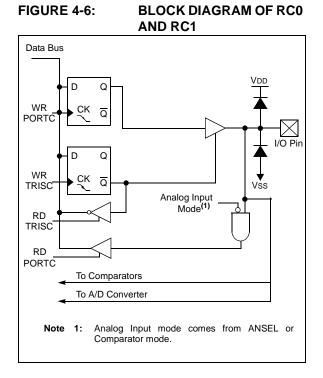

### 4.3.1 RC0/AN4<sup>(1)</sup>/C2IN+

The RC0 is configurable to function as one of the following:  $\label{eq:configurable}$

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to Comparator C2

### 4.3.2 RC1/AN5<sup>(1)</sup>/C12IN1-

The RC1 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

an analog inverting input to the comparator

Note 1: PIC16F616/16HV616 only.

#### 4.3.3 RC2/AN6<sup>(1)</sup>/C12IN2-/P1D<sup>(1)</sup>

The RC2 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog input to Comparators C1 and C2

- a digital output from the Enhanced CCP<sup>(1)</sup>

#### 4.3.4 RC3/AN7<sup>(1)</sup>/C12IN3-/P1C<sup>(1)</sup>

The RC3 is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to Comparators C1 and C2

- a digital output from the Enhanced CCP<sup>(1)</sup>

Note 1: PIC16F616/16HV616 only.

#### 7: BLOCK DIAGRAM OF RC2 AND RC3

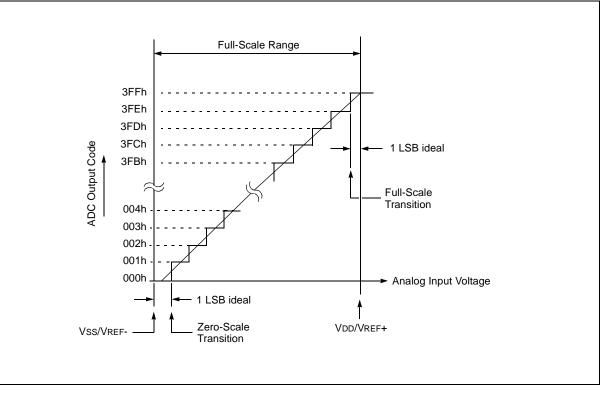

#### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the analog-to-digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 9.2.6 "A/D Conversion   |

|       | Procedure".                              |

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete analog-to-digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The ECCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not ensure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

See Section 10.0 "Enhanced Capture/Compare/ PWM (With Auto-Shutdown and Dead Band) Module (PIC16F616/16HV616 Only)" for more information.

#### 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an analog-to-digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt may be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 9.3 "A/D Acquisition Requirements".

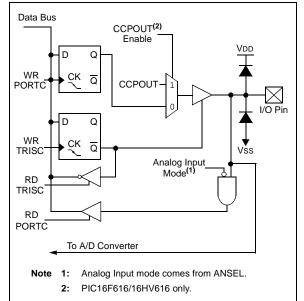

#### FIGURE 9-4: ANALOG INPUT MODEL

| Name                    | Bit 7      | Bit 6                         | Bit 5                 | Bit 4  | Bit 3               | Bit 2               | Bit 1                 | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-------------------------|------------|-------------------------------|-----------------------|--------|---------------------|---------------------|-----------------------|--------|----------------------|---------------------------------|

| ADCON0 <sup>(1)</sup>   | ADFM       | VCFG                          | CHS3                  | CHS2   | CHS1                | CHS0                | GO/DONE               | ADON   | 0000 0000            | 0000 0000                       |

| ADCON1 <sup>(1)</sup>   | _          | ADCS2                         | ADCS1                 | ADCS0  | _                   | _                   | _                     | _      | -000                 | -000                            |

| ANSEL                   | ANS        | ANS6                          | ANS5                  | ANS4   | ANS3 <sup>(1)</sup> | ANS2 <sup>(1)</sup> | ANS1                  | ANS0   | 1111 1111            | 1111 1111                       |

| ADRESH <sup>(1,2)</sup> | A/D Result | A/D Result Register High Byte |                       |        |                     |                     |                       |        |                      | uuuu uuuu                       |

| ADRESL <sup>(1,2)</sup> | A/D Result | Register Lov                  | v Byte                |        |                     |                     |                       |        | xxxx xxxx            | uuuu uuuu                       |

| INTCON                  | GIE        | PEIE                          | TOIE                  | INTE   | RAIE                | T0IF                | INTF                  | RAIF   | 0000 0000            | 0000 0000                       |

| PIE1                    | —          | ADIE <sup>(1)</sup>           | CCP1IE <sup>(1)</sup> | C2IE   | C1IE                | -                   | TMR2IE <sup>(1)</sup> | TMR1IE | -000 0-00            | -000 0-00                       |

| PIR1                    | _          | ADIF <sup>(1)</sup>           | CCP1IF <sup>(1)</sup> | C2IF   | C1IF                | _                   | TMR2IF <sup>(1)</sup> | TMR1IF | -000 0-00            | -000 0-00                       |

| PORTA                   | _          | _                             | RA5                   | RA4    | RA3                 | RA2                 | RA1                   | RA0    | x0 x000              | u0 u000                         |

| PORTC                   | _          | _                             | RC5                   | RC4    | RC3                 | RC2                 | RC1                   | RC0    | xx 00xx              | uu 00uu                         |

| TRISA                   | _          |                               | TRISA5                | TRISA4 | TRISA3              | TRISA2              | TRISA1                | TRISA0 | 11 1111              | 11 1111                         |

| TRISC                   | _          |                               | TRISC5                | TRISC4 | TRISC3              | TRISC2              | TRISC1                | TRISC0 | 11 1111              | 11 1111                         |

#### **TABLE 9-2:** SUMMARY OF ASSOCIATED ADC REGISTERS

x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module. Legend:

Note 1:

PIC16F616/16HV616 only. 2: Read-only Register.

NOTES:

| Name                  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|-----------------------|--------|--------|-------|-------|-------|-------|-------|-------|----------------------|---------------------------------|

| OPTION_REG            | RAPU   | INTEDG | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   | 1111 1111            | 1111 1111                       |

| CONFIG <sup>(1)</sup> | IOSCFS | CP     | MCLRE | PWRTE | WDTE  | FOSC2 | FOSC1 | FOSC0 | _                    | _                               |

#### TABLE 12-8: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of all Configuration Word register bits.

| MOVF             | Move f                                                                                                                                                                                                                                                                                     |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                                                  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \left[0,1\right] \end{array}$                                                                                                                                                                                                                 |

| Operation:       | (f) $\rightarrow$ (dest)                                                                                                                                                                                                                                                                   |

| Status Affected: | Z                                                                                                                                                                                                                                                                                          |

| Description:     | The contents of register 'f' is<br>moved to a destination dependent<br>upon the status of 'd'. If $d = 0$ ,<br>destination is W register. If $d = 1$ ,<br>the destination is file register 'f'<br>itself. $d = 1$ is useful to test a file<br>register since status flag Z is<br>affected. |

| Words:           | 1                                                                                                                                                                                                                                                                                          |

| Cycles:          | 1                                                                                                                                                                                                                                                                                          |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                                                                |

|                  | After Instruction<br>W = value in FSR<br>register<br>Z = 1                                                                                                                                                                                                                                 |

| MOVWF            | Move W to f                                |

|------------------|--------------------------------------------|

| Syntax:          | [label] MOVWF f                            |

| Operands:        | $0 \leq f \leq 127$                        |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| Words:           | 1                                          |

| Cycles:          | 1                                          |

| Example:         | MOVW OPTION<br>F                           |

|                  | Before Instruction                         |

|                  | OPTION = 0xFF                              |

|                  | W = 0x4F<br>After Instruction              |

|                  | OPTION = 0x4F                              |

|                  | W = 0x4F                                   |

|                  |                                            |

| MOVLW            | Move literal to W                                                                                   |

|------------------|-----------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                            |

| Operands:        | $0 \le k \le 255$                                                                                   |

| Operation:       | $k \rightarrow (W)$                                                                                 |

| Status Affected: | None                                                                                                |

| Description:     | The eight-bit literal 'k' is loaded into<br>W register. The "don't cares" will<br>assemble as '0's. |

| Words:           | 1                                                                                                   |

| Cycles:          | 1                                                                                                   |

| Example:         | MOVLW 0x5A                                                                                          |

|                  | After Instruction<br>W = 0x5A                                                                       |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

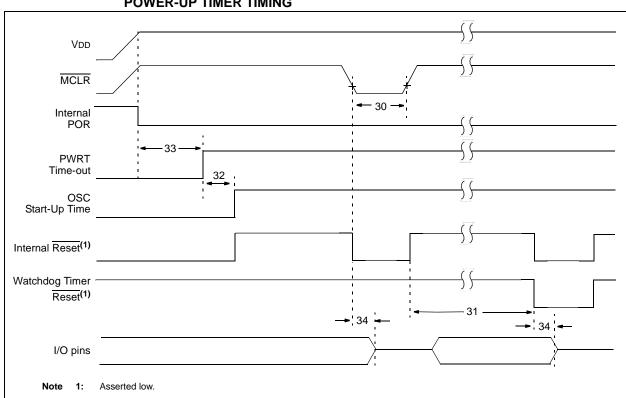

### FIGURE 15-8: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

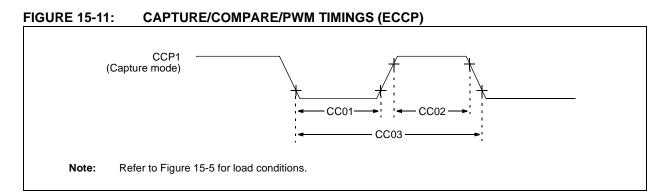

#### TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |      |     |       |                                       |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|------|-----|-------|---------------------------------------|

| Param<br>No.                                                                                                         | Sym  | Character            | istic          | Min                   | Тур† | Max | Units | Conditions                            |

| CC01*                                                                                                                | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —    | _   | ns    |                                       |

| CC02*                                                                                                                | ТссН | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —    |     | ns    |                                       |

| CC03*                                                                                                                | TccP | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —   | ns    | N = prescale<br>value (1, 4 or<br>16) |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 15-7: **COMPARATOR SPECIFICATIONS**

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                        |         |     |       |           |       |          |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------------|---------|-----|-------|-----------|-------|----------|--|

| Param<br>No. | Sym                                                                                                                  | Characteristics                        |         | Min | Тур†  | Мах       | Units | Comments |  |

| CM01         | Vos                                                                                                                  | Input Offset Voltage <sup>(2)</sup>    |         |     | ± 5.0 | ± 10      | mV    |          |  |

| CM02         | Vсм                                                                                                                  | Input Common Mode Voltage              |         | 0   | —     | Vdd - 1.5 | V     |          |  |

| CM03*        | CMRR                                                                                                                 | Common Mode Rejection Ratio            |         | +55 | —     | —         | dB    |          |  |

| CM04*        | Trt                                                                                                                  | Response Time <sup>(1)</sup>           | Falling | —   | 150   | 600       | ns    |          |  |

|              |                                                                                                                      |                                        | Rising  |     | 200   | 1000      | ns    |          |  |

| CM05*        | TMC2COV                                                                                                              | Comparator Mode Change to Output Valid |         | —   | —     | 10        | μS    |          |  |

| CM06*        | VHYS                                                                                                                 | Input Hysteresis Voltage               |         | _   | 45    | 60        | mV    |          |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV. Note 1: The other input is at (VDD -1.5)/2.

2: Input offset voltage is measured with one comparator input at (VDD - 1.5V)/2.

#### **COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS TABLE 15-8:**

|              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                                  |     |                  |                |            |                                             |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------------------|-----|------------------|----------------|------------|---------------------------------------------|

| Param<br>No. | Sym                                                                                                                  | Characteristics                  | Min | Тур†             | Max            | Units      | Comments                                    |

| CV01         | Clsb                                                                                                                 | Step Size <sup>(2)</sup>         |     | Vdd/24<br>Vdd/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02         | CACC                                                                                                                 | Absolute Accuracy <sup>(3)</sup> | _   |                  | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03         | CR                                                                                                                   | Unit Resistor Value (R)          | —   | 2k               | _              | Ω          |                                             |

| CV04         | CST                                                                                                                  | Settling Time <sup>(1)</sup>     | _   | —                | 10             | μS         |                                             |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

- 2: See Section 8.11 "Comparator Voltage Reference" for more information.

- **3:** Absolute Accuracy when CVREF output is  $\leq$  (VDD-1.5).

#### TABLE 15-9: VOLTAGE REFERENCE SPECIFICATIONS

| VR Voltage Reference Specifications |         | Standard Operating Conditions (unless otherwise stat<br>Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |      |       |          |

|-------------------------------------|---------|-----------------------------------------------------------------------------------------------------------------------|------|------|------|-------|----------|

| Param<br>No.                        | Symbol  | Characteristics                                                                                                       | Min  | Тур  | Max  | Units | Comments |

| VR01                                | VP6out  | VP6 voltage output                                                                                                    | 0.50 | 0.6  | 0.7  | V     |          |

| VR02                                | V1P2out | V1P2 voltage output                                                                                                   | 1.05 | 1.20 | 1.35 | V     |          |

| VR03*                               | TSTABLE | Settling Time                                                                                                         |      | 10   |      | μS    |          |

These parameters are characterized but not tested.

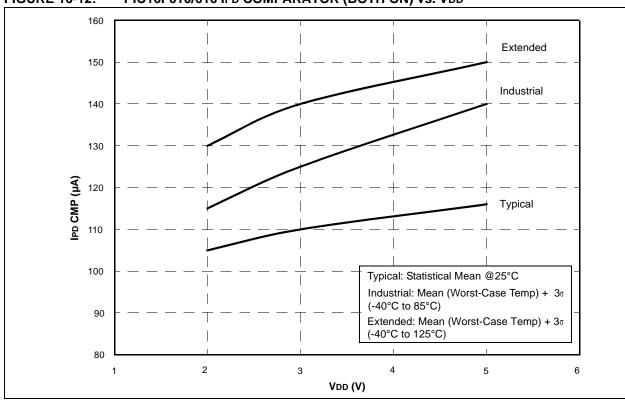

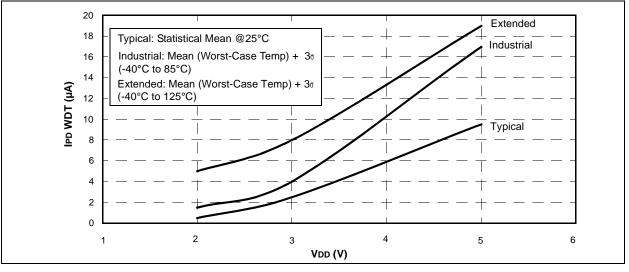

#### FIGURE 16-12: PIC16F610/616 IPD COMPARATOR (BOTH ON) vs. VDD

### APPENDIX B: MIGRATING FROM OTHER PIC<sup>®</sup> DEVICES

This discusses some of the issues in migrating from other  $\text{PIC}^{\textcircled{0}}$  devices to the PIC16F6XX Family of devices.

#### B.1 PIC16F676 to PIC16F610/616/16HV610/616

#### TABLE B-1: FEATURE COMPARISON

| Feature                    | PIC16F676     | PIC16F610/16HV610 | PIC16F616/16HV616 |

|----------------------------|---------------|-------------------|-------------------|

| Max Operating Speed        | 20 MHz        | 20 MHz            | 20 MHz            |

| Max Program Memory (Words) | 1024          | 1024              | 2048              |

| SRAM (bytes)               | 64            | 64                | 128               |

| A/D Resolution             | 10-bit        | None              | 10-bit            |

| Timers (8/16-bit)          | 1/1           | 1/1               | 2/1               |

| Oscillator Modes           | 8             | 8                 | 8                 |

| Brown-out Reset            | Y             | Y                 | Y                 |

| Internal Pull-ups          | RA0/1/2/4/5   | RA0/1/2/4/5, MCLR | RA0/1/2/4/5, MCLR |

| Interrupt-on-change        | RA0/1/2/3/4/5 | RA0/1/2/3/4/5     | RA0/1/2/3/4/5     |

| Comparator                 | 1             | 2                 | 2                 |

| ECCP                       | Ν             | Ν                 | Y                 |

| INTOSC Frequencies         | 4 MHz         | 4/8 MHz           | 4/8 MHz           |

| Internal Shunt Regulator   | Ν             | Y (PIC16HV610)    | Y (PIC16HV616)    |

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

### READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:  | Technical Publications Manager         | Total Pages Sent                                       |

|------|----------------------------------------|--------------------------------------------------------|

| RE:  | Reader Response                        |                                                        |

| Fron | n: Name                                |                                                        |

|      | Company                                |                                                        |

|      | Address                                |                                                        |

|      | City / State / ZIP / Country           |                                                        |

|      | Telephone: ()                          | FAX: ()                                                |

| Appl | ication (optional):                    |                                                        |

| Wou  | ld you like a reply?YN                 |                                                        |

| Devi | ce: PIC16F610/616/16HV610/616          | Literature Number: DS41288F                            |

| Que  | stions:                                |                                                        |

| 1 \  | What are the best features of this do  | cument?                                                |

| 1.   |                                        |                                                        |

| -    |                                        |                                                        |

| 2.   | How does this document meet your h     | nardware and software development needs?               |

|      |                                        |                                                        |

| -    |                                        |                                                        |

| 3. I | Do you find the organization of this d | ocument easy to follow? If not, why?                   |

| -    |                                        |                                                        |

| -    |                                        |                                                        |

| 4.   | What additions to the document do y    | ou think would enhance the structure and subject?      |

| -    |                                        |                                                        |

| -    |                                        |                                                        |

| 5.   | What deletions from the document co    | ould be made without affecting the overall usefulness? |

| -    |                                        |                                                        |

| -    |                                        |                                                        |

| 6.   | s there any incorrect or misleading in | nformation (what and where)?                           |

| -    |                                        |                                                        |

| -    |                                        | at2                                                    |

| 1.   | How would you improve this docume      | nt (                                                   |

| -    |                                        |                                                        |