Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 16-VQFN Exposed Pad                                                       |

| Supplier Device Package    | 16-QFN (4x4)                                                              |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f616t-i-ml |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.2.2.6 PCON Register

The Power Control (PCON) register (see Table 12-2) contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the software enable of the  $\overline{\text{BOR}}.$

The PCON register bits are shown in Register 2-6.

# REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0 | R/W-0 <sup>(1)</sup> |

|-------|-----|-----|-----|-----|-----|-------|----------------------|

| —     | —   | —   | —   | —   | —   | POR   | BOR                  |

| bit 7 |     |     |     |     |     |       | bit 0                |

| Legend:                               |                                |                            |                                 |                      |

|---------------------------------------|--------------------------------|----------------------------|---------------------------------|----------------------|

| R = Reada                             | ble bit                        | W = Writable bit           | U = Unimplemented bit,          | read as '0'          |

| -n = Value                            | at POR                         | '1' = Bit is set           | '0' = Bit is cleared            | x = Bit is unknown   |

|                                       |                                |                            |                                 |                      |

| bit 7-2                               | Unimplen                       | nented: Read as '0'        |                                 |                      |

| bit 1                                 | POR: Power-on Reset Status bit |                            |                                 |                      |

|                                       | 1 = No Power-on Reset occurred |                            |                                 |                      |

|                                       | 0 = A Pov                      | ver-on Reset occurred (mus | t be set in software after a Po | wer-on Reset occurs) |

| bit 0 BOR: Brown-out Reset Status bit |                                |                            |                                 |                      |

|                                       | 1 = No Br                      | own-out Reset occurred     |                                 |                      |

0 = A Brown-out Reset occurred (must be set in software after a Brown-out Reset occurs)

**Note 1:** Reads as '0' if Brown-out Reset is disabled.

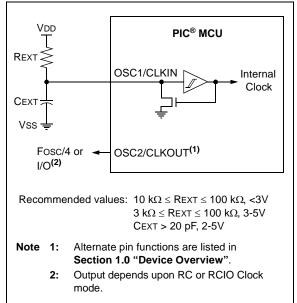

# 3.3.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

#### FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

# 3.4 Internal Clock Modes

The Oscillator module provides a selectable system clock source of either 4 MHz or 8 MHz. The selectable frequency is configured through the IOSCFS bit of the Configuration Word.

The frequency of the internal oscillator can be can be user-adjusted via software using the OSCTUNE register.

# 3.4.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 12.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

# PIC16F610/616/16HV610/616

# 6.2.1 INTERNAL CLOCK SOURCE

When the internal clock source is selected the TMR1H:TMR1L register pair will increment on multiples of TCY as determined by the Timer1 prescaler.

### 6.2.2 EXTERNAL CLOCK SOURCE

When the external clock source is selected, the Timer1 module may work as a timer or a counter.

When counting, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously.

If an external clock oscillator is needed (and the microcontroller is using the INTOSC without CLKOUT), Timer1 can use the LP oscillator as a clock source.

| Note: | In Counter mode, a falling edge must be      |

|-------|----------------------------------------------|

|       | registered by the counter prior to the first |

|       | incrementing rising edge.                    |

# 6.3 Timer1 Prescaler

Timer1 has four prescaler options allowing 1, 2, 4 or 8 divisions of the clock input. The T1CKPS bits of the T1CON register control the prescale counter. The prescale counter is not directly readable or writable; however, the prescaler counter is cleared upon a write to TMR1H or TMR1L.

# 6.4 Timer1 Oscillator

A low-power 32.768 kHz crystal oscillator is built-in between pins OSC1 (input) and OSC2 (output). The oscillator is enabled by setting the T1OSCEN control bit of the T1CON register. The oscillator will continue to run during Sleep.

The Timer1 oscillator is shared with the system LP oscillator. Thus, Timer1 can use this mode only when the primary system clock is derived from the internal oscillator or when the oscillator is in the LP Oscillator mode. The user must provide a software time delay to ensure proper oscillator start-up.

TRISA5 and TRISA4 bits are set when the Timer1 oscillator is enabled. RA5 and RA4 bits read as '0' and TRISA5 and TRISA4 bits read as '1'.

Note: The oscillator requires a start-up and stabilization time before use. Thus, T1OSCEN should be set and a suitable delay observed prior to enabling Timer1.

# 6.5 Timer1 Operation in Asynchronous Counter Mode

If control bit T1SYNC of the T1CON register is set, the external clock input is not synchronized. The timer continues to increment asynchronous to the internal phase clocks. The timer will continue to run during Sleep and can generate an interrupt on overflow, which will wake-up the processor. However, special precautions in software are needed to read/write the timer (see Section 6.5.1 "Reading and Writing Timer1 in Asynchronous Counter Mode").

- Note: When switching from synchronous to asynchronous operation, it is possible to skip an increment. When switching from asynchronous to synchronous operation, it is possible to produce an additional increment.

- Note: In asynchronous counter mode or when using the internal oscillator and T1ACS=1, Timer1 can not be used as a time base for the capture or compare modes of the ECCP module (for PIC16F616/HV616 only).

#### 6.5.1 READING AND WRITING TIMER1 IN ASYNCHRONOUS COUNTER MODE

Reading TMR1H or TMR1L while the timer is running from an external asynchronous clock will ensure a valid read (taken care of in hardware). However, the user should keep in mind that reading the 16-bit timer in two 8-bit values itself, poses certain problems, since the timer may overflow between the reads.

For writes, it is recommended that the user simply stop the timer and write the desired values. A write contention may occur by writing to the timer registers, while the register is incrementing. This may produce an unpredictable value in the TMR1H:TMR1L register pair.

# 6.6 Timer1 Gate

Timer1 gate source is software configurable to be the T1G pin or the output of Comparator C2. This allows the device to directly time external events using T1G or analog events using Comparator C2. See the CM2CON1 register (Register 8-3) for selecting the Timer1 gate source. This feature can simplify the software for a Delta-Sigma A/D converter and many

# TABLE 6-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER1

| Name    | Bit 7                                                                       | Bit 6               | Bit 5                 | Bit 4   | Bit 3   | Bit 2  | Bit 1                 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|-----------------------------------------------------------------------------|---------------------|-----------------------|---------|---------|--------|-----------------------|-----------|----------------------|---------------------------------|

| CM2CON0 | C2ON                                                                        | C2OUT               | C2OE                  | C2POL   | _       | C2R    | C2CH1                 | C2CH0     | 0000 -000            | 0000 -000                       |

| CM2CON1 | MC1OUT                                                                      | MC2OUT              | _                     | T1ACS   | C1HYS   | C2HYS  | T1GSS                 | C2SYNC    | 00-0 0010            | 00-0 0010                       |

| INTCON  | GIE                                                                         | PEIE                | TOIE                  | INTE    | RAIE    | T0IF   | INTF                  | RAIF      | 0000 0000            | 0000 0000                       |

| PIE1    | _                                                                           | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE    | C1IE    | _      | TMR2IE <sup>(1)</sup> | TMR1IE    | -000 0-00            | -000 0-00                       |

| PIR1    | —                                                                           | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF    | C1IF    | _      | TMR2IF <sup>(1)</sup> | TMR1IF    | -000 0-00            | -000 0-00                       |

| TMR1H   | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register  |                     |                       |         |         |        | xxxx xxxx             | uuuu uuuu |                      |                                 |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register |                     |                       |         |         |        |                       | xxxx xxxx | uuuu uuuu            |                                 |

| T1CON   | T1GINV                                                                      | TMR1GE              | T1CKPS1               | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS                | TMR10N    | 0000 0000            | uuuu uuuu                       |

**Legend:** x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used by the Timer1 module.

Note 1: PIC16F616/16HV616 only.

| R/W-0              | R/W-0               | R/W-0                                                                  | R/W-0           | R/S-0             | R/S-0             | U-0             | R/W-0   |

|--------------------|---------------------|------------------------------------------------------------------------|-----------------|-------------------|-------------------|-----------------|---------|

| SR1 <sup>(2)</sup> | SR0 <sup>(2)</sup>  | C1SEN                                                                  | C2REN           | PULSS             | PULSR             | —               | SRCLKEN |

| bit 7              |                     |                                                                        |                 |                   |                   |                 | bit 0   |

| Legend:            |                     |                                                                        |                 | S = Bit is set o  | nlv -             |                 |         |

| R = Readable b     | t                   | W = Writable bi                                                        | +               |                   | ented bit, read a | s 'O'           |         |

| -n = Value at P    |                     | (1) = Bit is set                                                       | ·               | '0' = Bit is clea | -                 | x = Bit is unkr |         |

|                    | JK                  | I = DILIS SEL                                                          |                 |                   | ieu               |                 | IOWIT   |

| bit 7              | 1 = C2OUT           | h Configuration bing pin is the latch $\overline{Q}$ pin is the C2 con | output          |                   |                   |                 |         |

| bit 6              | 1 = C1OUT           | n Configuration bi<br>pin is the latch Q<br>pin is the C1 Cor          | output          |                   |                   |                 |         |

| bit 5              |                     | et Enable bit<br>arator output sets<br>arator output has               |                 | latch             |                   |                 |         |

| bit 4              | 1 = C2  comparation | eset Enable bit<br>arator output rese<br>arator output has             |                 | latch             |                   |                 |         |

| bit 3              | 1 = Triggers        | the SET Input of pulse generator to trigger pulse gen                  | set SR latch. E |                   | reset by hardwa   | are.            |         |

| bit 2              | 1 = Triggers        | e the Reset Input o<br>pulse generator to<br>trigger pulse gen         | reset SR latch  |                   | ely reset by hard | ware.           |         |

| bit 1              | Unimplement         | ed: Read as '0'                                                        |                 |                   |                   |                 |         |

| bit 0              |                     | R Latch Set Clock<br>of SR latch is pul-<br>of SR latch is not         | sed with SRCL   |                   |                   |                 |         |

#### REGISTER 8-4: SRCON0: SR LATCH CONTROL 0 REGISTER

the pin), regardless of the SR latch operation.2: To enable an SR Latch output to the pin, the appropriate CxOE, and TRIS bits must be properly configured.

# REGISTER 8-5: SRCON1: SR LATCH CONTROL 1 REGISTER

| R/W-0     | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0   | U-0 |

|-----------|-------|-----|-----|-----|-----|-------|-----|

| SRCS1     | SRCS0 | —   | —   | —   | —   | —     | —   |

| bit 7 bit |       |     |     |     |     | bit 0 |     |

| Legend:           |                  | S = Bit is set only -    |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 7-6 | SRCS<1:0>: SR Latch Clock Prescale bits |

|---------|-----------------------------------------|

|         | 00 = Fosc/16                            |

|         | 01 = Fosc/32                            |

|         | 10 = Fosc/64                            |

11 = Fosc/128

bit 5-0 Unimplemented: Read as '0'

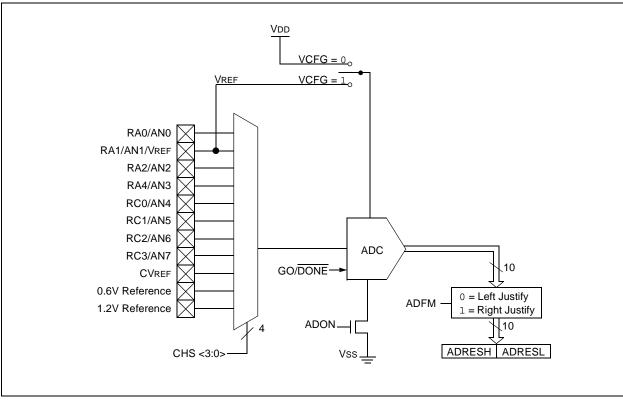

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE (PIC16F616/16HV616 ONLY)

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 9-1 shows the block diagram of the ADC.

# FIGURE 9-1: ADC BLOCK DIAGRAM

Note: The ADRESL and ADRESH registers are read-only.

# 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 9-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =  $50^{\circ}C$  and external impedance of  $10k\Omega 5.0V VDD$  TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF $= 5\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-T_{C}}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} \qquad (1 - e^{\frac{-T_{C}}{RC}}) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}$$

$$V_{APPLIED}\left(1 - e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \quad \text{; combining [1] and [2]}$$

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

**3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

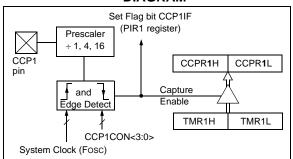

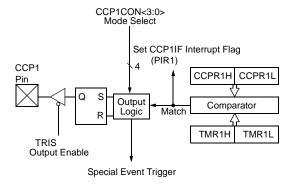

# 10.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (see Figure 10-1).

#### 10.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCP1 pin is configured as an output, |

|-------|---------------------------------------------|

|       | a write to the port can cause a capture     |

|       | condition.                                  |

#### FIGURE 10-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

# 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in operating mode.

#### 10.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (see Example 10-1).

#### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

# 10.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 module may:

- Toggle the CCP1 output

- Set the CCP1 output

- Clear the CCP1 output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

# FIGURE 10-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 10.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |

|-------|---------------------------------------------|

|       | the CCP1 compare output latch to the        |

|       | default low level. This is not the PORT I/O |

|       | data latch.                                 |

#### 10.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 10.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 10.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP1 module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP1 module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

| Name                   | Bit 7                                                                                           | Bit 6               | Bit 5                 | Bit 4   | Bit 3   | Bit 2     | Bit 1                 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|-------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------|---------|-----------|-----------------------|-----------|----------------------|---------------------------------|

| CCP1CON <sup>(1)</sup> | P1M1                                                                                            | P1M0                | DC1B1                 | DC1B0   | CCP1M3  | CCP1M2    | CCP1M1                | CCP1M0    | 0000 0000            | 0000 0000                       |

| CCPR1L <sup>(1)</sup>  | Capture/Compare/PWM Register 1 Low Byte xxxx xxx                                                |                     |                       |         |         |           | xxxx xxxx             | uuuu uuuu |                      |                                 |

| CCPR1H <sup>(1)</sup>  | Capture/Compare/PWM Register 1 High Byte xxxx xxxx uuuu uuuu                                    |                     |                       |         |         | uuuu uuuu |                       |           |                      |                                 |

| INTCON                 | GIE                                                                                             | PEIE                | T0IE                  | INTE    | RAIE    | T0IF      | INTF                  | RAIF      | 0000 0000            | 0000 0000                       |

| PIE1                   | _                                                                                               | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE    | C1IE    |           | TMR2IE <sup>(1)</sup> | TMR1IE    | -000 0-00            | 0000 0-00                       |

| PIR1                   | —                                                                                               | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF    | C1IF    | —         | TMR2IF <sup>(1)</sup> | TMR1IF    | -000 0-00            | 0000 0-00                       |

| T1CON                  | T1GINV                                                                                          | TMR1GE              | T1CKPS1               | T1CKPS0 | T1OSCEN | T1SYNC    | TMR1CS                | TMR10N    | 0000 0000            | uuuu uuuu                       |

| TMR1L                  | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu |                     |                       |         |         |           |                       |           |                      |                                 |

| TMR1H                  | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuuu  |                     |                       |         |         |           |                       |           |                      |                                 |

| TRISA                  | —                                                                                               | —                   | TRISA5                | TRISA4  | TRISA3  | TRISA2    | TRISA1                | TRISA0    | 11 1111              | 11 1111                         |

| TRISC                  | _                                                                                               | _                   | TRISC5                | TRISC4  | TRISC3  | TRISC2    | TRISC1                | TRISC0    | 11 1111              | 11 1111                         |

|                        |                                                                                                 |                     |                       |         |         | <u> </u>  |                       |           |                      |                                 |

#### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM. Note 1: PIC16F616/16HV616 only.

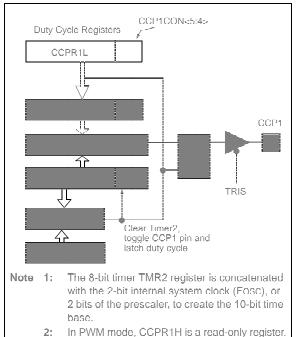

# 10.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to make the CCP1 pin an output.

| Note: | Clearing   | the | CCP1CON          | register | will |

|-------|------------|-----|------------------|----------|------|

|       | relinquish | CCP | 1 control of the | ne CCP1  | pin. |

Figure 10-3 shows a simplified block diagram of PWM operation.

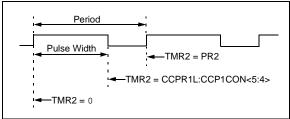

Figure 10-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 10.3.7** "Setup for PWM Operation".

FIGURE 10-3: SIMPLIFIED PWM BLOCK DIAGRAM

The PWM output (Figure 10-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 10-4: CCP PWM OUTPUT

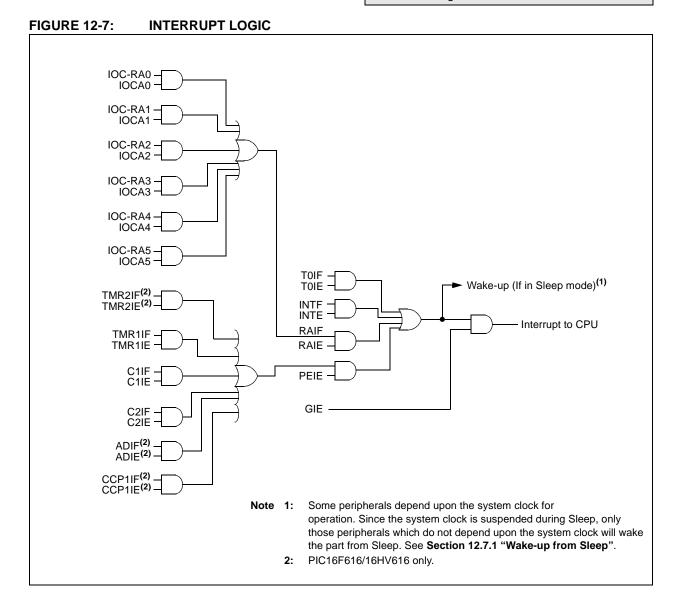

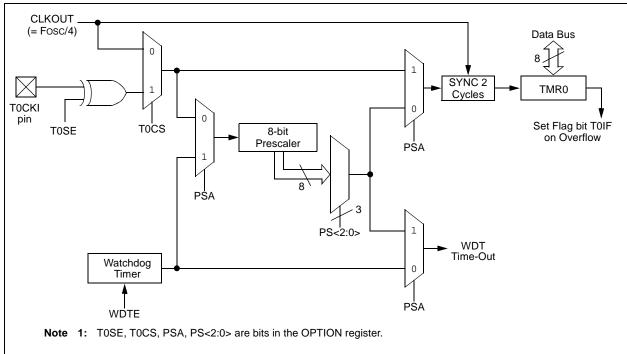

# 12.4.2 TIMER0 INTERRUPT

An overflow (FFh  $\rightarrow$  00h) in the TMR0 register will set the T0IF bit of the INTCON register. The interrupt can be enabled/disabled by setting/clearing T0IE bit of the INTCON register. See **Section 5.0 "Timer0 Module"** for operation of the Timer0 module.

# 12.4.3 PORTA INTERRUPT-ON-CHANGE

An input change on PORTA sets the RAIF bit of the INTCON register. The interrupt can be enabled/ disabled by setting/clearing the RAIE bit of the INTCON register. Plus, individual pins can be configured through the IOCA register.

Note: If a change on the I/O pin should occur when any PORTA operation is being executed, then the RAIF interrupt flag may not get set.

# 12.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin and INTOSC. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT Time-out generates a device Reset. If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 12.1 "Configuration Bits").

# 12.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see Table 15-4, Parameter 31). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

#### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT Time-out occurs.

# FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

# TABLE 12-7: WDT STATUS

| Conditions                                   | WDT                          |

|----------------------------------------------|------------------------------|

| WDTE = 0                                     |                              |

| CLRWDT Command                               | Cleared                      |

| Exit Sleep + System Clock = EXTRC, INTRC, EC |                              |

| Exit Sleep + System Clock = XT, HS, LP       | Cleared until the end of OST |

# 14.11 PICkit 2 Development Programmer/Debugger and PICkit 2 Debug Express

The PICkit<sup>™</sup> 2 Development Programmer/Debugger is a low-cost development tool with an easy to use interface for programming and debugging Microchip's Flash families of microcontrollers. The full featured Windows® programming interface supports baseline (PIC10F, PIC12F5xx, PIC16F5xx), midrange (PIC12F6xx, PIC16F), PIC18F, PIC24, dsPIC30, dsPIC33, and PIC32 families of 8-bit, 16-bit, and 32-bit microcontrollers, and many Microchip Serial EEPROM products. With Microchip's powerful MPLAB Integrated Development Environment (IDE) the PICkit<sup>™</sup> 2 enables in-circuit debugging on most PIC<sup>®</sup> microcontrollers. In-Circuit-Debugging runs, halts and single steps the program while the PIC microcontroller is embedded in the application. When halted at a breakpoint, the file registers can be examined and modified.

The PICkit 2 Debug Express include the PICkit 2, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

# 14.12 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an MMC card for file storage and data applications.

# 14.13 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# PIC16F610/616/16HV610/616

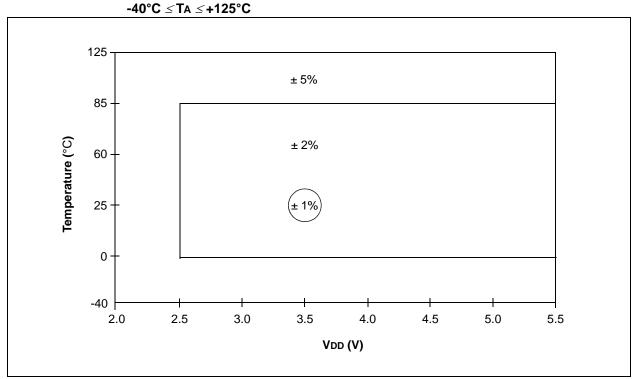

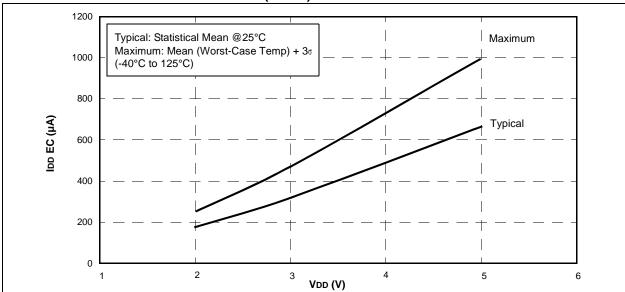

FIGURE 15-3: PIC16F610/616 FREQUENCY TOLERANCE GRAPH,

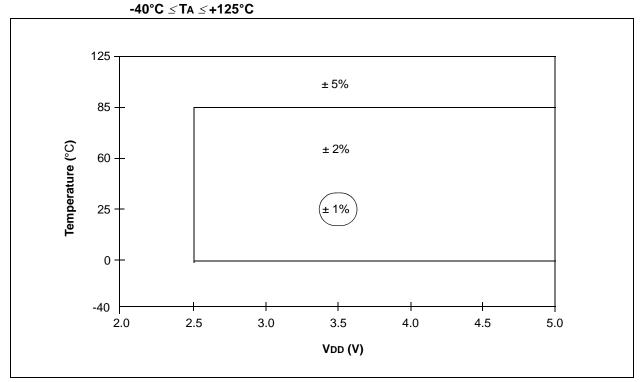

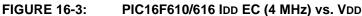

FIGURE 15-4: PIC16HV610/616 FREQUENCY TOLERANCE GRAPH,

# 15.11 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

#### 1. TppS2ppS

2. TppS

| <u>z. rpp3</u>                        |                                            |     |                |  |  |

|---------------------------------------|--------------------------------------------|-----|----------------|--|--|

| т                                     |                                            |     |                |  |  |

| F                                     | Frequency                                  | Т   | Time           |  |  |

| Lowerc                                | Lowercase letters (pp) and their meanings: |     |                |  |  |

| рр                                    |                                            |     |                |  |  |

| сс                                    | CCP1                                       | osc | OSC1           |  |  |

| ck                                    | CLKOUT                                     | rd  | RD             |  |  |

| CS                                    | CS                                         | rw  | RD or WR       |  |  |

| di                                    | SDI                                        | sc  | SCK            |  |  |

| do                                    | SDO                                        | SS  | SS             |  |  |

| dt                                    | Data in                                    | tO  | TOCKI          |  |  |

| io                                    | I/O Port                                   | t1  | T1CKI          |  |  |

| mc                                    | MCLR                                       | wr  | WR             |  |  |

| Uppercase letters and their meanings: |                                            |     |                |  |  |

| S                                     |                                            |     |                |  |  |

| F                                     | Fall                                       | Р   | Period         |  |  |

| н                                     | High                                       | R   | Rise           |  |  |

| I                                     | Invalid (High-impedance)                   | V   | Valid          |  |  |

| L                                     | Low                                        | Z   | High-impedance |  |  |

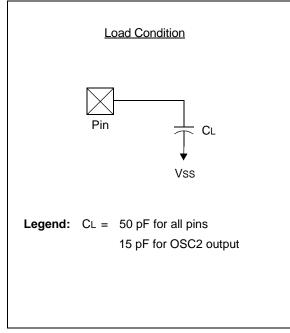

#### FIGURE 15-5: LOAD CONDITIONS

# PIC16F610/616/16HV610/616

# PIC16F610/616/16HV610/616

# APPENDIX A: DATA SHEET REVISION HISTORY

# **Revision A**

This is a new data sheet.

# Revision B (12/06)

Added PIC16F610/16HV610 parts. Replaced Package Drawings.

# Revision C (03/2007)

Replaced Package Drawings (Rev. AM); Replaced Development Support Section; Revised Product ID System.

# Revision D (06/2008)

Added Graphs; Revised 28-Pin ICD Pinout, Electrical Specifications Section; Package Details.

# **Revision E (09/2009)**

Added section 15.13 (High Temperature Operation) to the Electrical Specifications Chapter; Other minor corrections.

# **Revision F (11/2009)**

Updated Figure 16-52.

# READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:  | Technical Publications Manager                                                          | Total Pages Sent                                       |  |  |  |  |

|------|-----------------------------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|

| RE:  | Reader Response                                                                         |                                                        |  |  |  |  |

| Fron | n: Name                                                                                 |                                                        |  |  |  |  |

|      | Company                                                                                 |                                                        |  |  |  |  |

|      | Address                                                                                 |                                                        |  |  |  |  |

|      | City / State / ZIP / Country                                                            |                                                        |  |  |  |  |

|      | Telephone: ()                                                                           | FAX: ()                                                |  |  |  |  |

| Appl | ication (optional):                                                                     |                                                        |  |  |  |  |

| Wou  | ld you like a reply?YN                                                                  |                                                        |  |  |  |  |

| Devi | ce: PIC16F610/616/16HV610/616                                                           | Literature Number: DS41288F                            |  |  |  |  |

| Que  | stions:                                                                                 |                                                        |  |  |  |  |

| 1 \  | What are the best features of this do                                                   | cument?                                                |  |  |  |  |

| 1.   |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| 2.   | How does this document meet your h                                                      | nardware and software development needs?               |  |  |  |  |

|      |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| 3. I | 3. Do you find the organization of this document easy to follow? If not, why?           |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| 4.   | 4. What additions to the document do you think would enhance the structure and subject? |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| 5.   | What deletions from the document co                                                     | ould be made without affecting the overall usefulness? |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| 6.   | s there any incorrect or misleading in                                                  | nformation (what and where)?                           |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |

| -    |                                                                                         | at2                                                    |  |  |  |  |

| 1.   | How would you improve this docume                                                       | nt (                                                   |  |  |  |  |

| -    |                                                                                         |                                                        |  |  |  |  |