## Microchip Technology - PIC16HV610-E/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 1.75KB (1K x 14)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                |                                                                          |

| RAM Size                   | 64 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                  |

| Data Converters            | -                                                                        |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv610-e-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

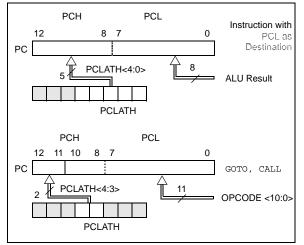

## 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in Figure 2-5 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-5 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

## 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, "Implementing a Table Read" (DS00556).

## 2.3.2 STACK

The PIC16F610/616/16HV610/616 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

## 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-7.

A simple program to clear RAM location 40h-4Fh using indirect addressing is shown in Example 2-1.

|       | MOVLW    | 0x40   | ;initialize pointer  |

|-------|----------|--------|----------------------|

|       | MOVWF    | FSR    | ;to RAM              |

| NEXT  | CLRF     | INDF   | ;clear INDF register |

|       | INCF     | FSR, F | ;inc pointer         |

|       | BTFSS    | FSR,4  | ;all done?           |

|       | GOTO     | NEXT   | ;no clear next       |

| CONTI | CONTINUE |        | ;yes continue        |

| 1     |          |        |                      |

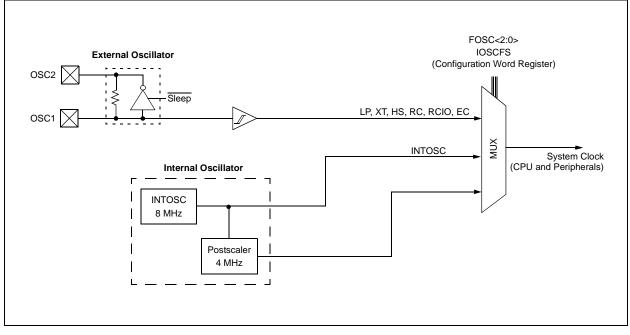

## 3.0 OSCILLATOR MODULE

## 3.1 Overview

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured with a choice of two selectable speeds: internal or external system clock source.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The Internal Oscillator module provides a selectable system clock mode of either 4 MHz (Postscaler) or 8 MHz (INTOSC).

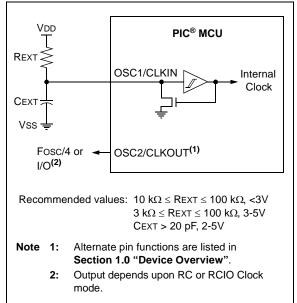

### 3.3.4 EXTERNAL RC MODES

The external Resistor-Capacitor (RC) modes support the use of an external RC circuit. This allows the designer maximum flexibility in frequency choice while keeping costs to a minimum when clock accuracy is not required. There are two modes: RC and RCIO.

In RC mode, the RC circuit connects to OSC1. OSC2/ CLKOUT outputs the RC oscillator frequency divided by 4. This signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements. Figure 3-5 shows the external RC mode connections.

#### FIGURE 3-5: EXTERNAL RC MODES

In RCIO mode, the RC circuit is connected to OSC1. OSC2 becomes an additional general purpose I/O pin.

The RC oscillator frequency is a function of the supply voltage, the resistor (REXT) and capacitor (CEXT) values and the operating temperature. Other factors affecting the oscillator frequency are:

- threshold voltage variation

- component tolerances

- packaging variations in capacitance

The user also needs to take into account variation due to tolerance of external RC components used.

### 3.4 Internal Clock Modes

The Oscillator module provides a selectable system clock source of either 4 MHz or 8 MHz. The selectable frequency is configured through the IOSCFS bit of the Configuration Word.

The frequency of the internal oscillator can be can be user-adjusted via software using the OSCTUNE register.

#### 3.4.1 INTOSC AND INTOSCIO MODES

The INTOSC and INTOSCIO modes configure the internal oscillators as the system clock source when the device is programmed using the oscillator selection or the FOSC<2:0> bits in the Configuration Word register (CONFIG). See Section 12.0 "Special Features of the CPU" for more information.

In **INTOSC** mode, OSC1/CLKIN is available for general purpose I/O. OSC2/CLKOUT outputs the selected internal oscillator frequency divided by 4. The CLKOUT signal may be used to provide a clock for external circuitry, synchronization, calibration, test or other application requirements.

In **INTOSCIO** mode, OSC1/CLKIN and OSC2/CLKOUT are available for general purpose I/O.

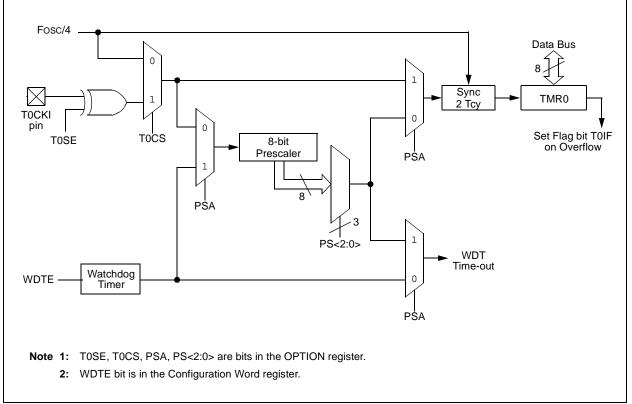

## 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- · Programmable internal or external clock source

- Programmable external clock edge selection

- Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

## 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

## 5.1.3 SOFTWARE PROGRAMMABLE PRESCALER

A single software programmable prescaler is available for use with either Timer0 or the Watchdog Timer (WDT), but not both simultaneously. The prescaler assignment is controlled by the PSA bit of the OPTION register. To assign the prescaler to Timer0, the PSA bit must be cleared to a '0'.

There are 8 prescaler options for the Timer0 module ranging from 1:2 to 1:256. The prescale values are selectable via the PS<2:0> bits of the OPTION register. In order to have a 1:1 prescaler value for the Timer0 module, the prescaler must be assigned to the WDT module.

The prescaler is not readable or writable. When assigned to the Timer0 module, all instructions writing to the TMR0 register will clear the prescaler.

When the prescaler is assigned to WDT, a CLRWDT instruction will clear the prescaler along with the WDT.

#### 5.1.3.1 Switching Prescaler Between Timer0 and WDT Modules

As a result of having the prescaler assigned to either Timer0 or the WDT, it is possible to generate an unintended device Reset when switching prescaler values. When changing the prescaler assignment from Timer0 to the WDT module, the instruction sequence shown in Example 5-1 must be executed.

## EXAMPLE 5-1: CHANGING PRESCALER (TIMER0 $\rightarrow$ WDT)

| BANKSEL | TMR0           | ;                  |

|---------|----------------|--------------------|

| CLRWDT  |                | ;Clear WDT         |

| CLRF    | TMR0           | ;Clear TMR0 and    |

|         |                | ;prescaler         |

| BANKSEI | OPTION_REG     | ;                  |

| BSF     | OPTION_REG,PSA | ;Select WDT        |

| CLRWDT  | ;              |                    |

|         | ;              |                    |

| MOVLW   | b'11111000'    | ;Mask prescaler    |

| ANDWF   | OPTION_REG,W   | ;bits              |

| IORLW   | b'00000101'    | ;Set WDT prescaler |

| MOVWF   | OPTION_REG     | ;to 1:32           |

|         |                |                    |

When changing the prescaler assignment from the WDT to the Timer0 module, the following instruction sequence must be executed (see Example 5-2).

| EXAMPLE 5-2: | CHANGING PRESCALER         |  |  |  |  |

|--------------|----------------------------|--|--|--|--|

|              | (WDT $\rightarrow$ TIMER0) |  |  |  |  |

| CLRWDT  |             | ;Clear WDT and<br>;prescaler |

|---------|-------------|------------------------------|

| BANKSEL | OPTION_REG  | ;                            |

| MOVLW   | b'11110000' | ;Mask TMR0 select and        |

| ANDWF   |             | prescaler bits               |

| IORLW   | b'00000011' | ;Set prescale to 1:16        |

| MOVWF   | OPTION_REG  | ;                            |

#### 5.1.4 TIMER0 INTERRUPT

Timer0 will generate an interrupt when the TMR0 register overflows from FFh to 00h. The T0IF interrupt flag bit of the INTCON register is set every time the TMR0 register overflows, regardless of whether or not the Timer0 interrupt is enabled. The T0IF bit must be cleared in software. The Timer0 interrupt enable is the T0IE bit of the INTCON register.

| Note: | The Timer0 interrupt cannot wake the                         |

|-------|--------------------------------------------------------------|

|       | processor from Sleep since the timer is frozen during Sleep. |

|       | nozen uunny Sleep.                                           |

## 5.1.5 USING TIMER0 WITH AN EXTERNAL CLOCK

When Timer0 is in Counter mode, the synchronization of the T0CKI input and the Timer0 register is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks. Therefore, the high and low periods of the external clock source must meet the timing requirements as shown in **Section 15.0 "Electrical Specifications"**.

| U-0              | R/W-0                                                         | R/W-0                        | R/W-0 | U-0                  | U-0                | U-0               | U-0 |

|------------------|---------------------------------------------------------------|------------------------------|-------|----------------------|--------------------|-------------------|-----|

| _                | ADCS2                                                         | ADCS1                        | ADCS0 | —                    | —                  | —                 | _   |

| bit 7            |                                                               |                              |       |                      |                    |                   | bit |

| Legend:          |                                                               |                              |       |                      |                    |                   |     |

| R = Readable bi  | t                                                             | W = Writable b               | it    | U = Unimpleme        | ented bit, read as | s 'O'             |     |

| -n = Value at PO | R                                                             | '1' = Bit is set             |       | '0' = Bit is clear   | ed                 | x = Bit is unknow | vn  |

| bit 7<br>bit 6-4 | ADCS<2:0>: /<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32 | 2<br>ock derived from a<br>6 |       | ernal oscillator = 5 | 00 kHz max)        |                   |     |

| bit 3-0          | Unimplement                                                   | ed: Read as '0'              |       |                      |                    |                   |     |

#### REGISTER 9-2: ADCON1: A/D CONTROL REGISTER 1

#### **REGISTER 9-3:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0 (READ-ONLY)

| R-x                               | R-x    | R-x    | R-x                                | R-x    | R-x    | R-x    | R-x    |

|-----------------------------------|--------|--------|------------------------------------|--------|--------|--------|--------|

| ADRES9                            | ADRES8 | ADRES7 | ADRES6                             | ADRES5 | ADRES4 | ADRES3 | ADRES2 |

| bit 7                             |        |        |                                    |        |        |        | bit 0  |

|                                   |        |        |                                    |        |        |        |        |

| Legend:                           |        |        |                                    |        |        |        |        |

| R = Readable bit W = Writable bit |        |        | U = Unimplemented bit, read as '0' |        |        |        |        |

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### REGISTER 9-4: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0 (READ-ONLY)

| R-x                                                                  | R-x    | U-0              | U-0 | U-0                                     | U-0 | U-0 | U-0   |  |  |

|----------------------------------------------------------------------|--------|------------------|-----|-----------------------------------------|-----|-----|-------|--|--|

| ADRES1                                                               | ADRES0 | —                | —   | —                                       | —   | —   | —     |  |  |

| bit 7                                                                |        |                  |     |                                         |     |     | bit 0 |  |  |

|                                                                      |        |                  |     |                                         |     |     |       |  |  |

| Legend:                                                              |        |                  |     |                                         |     |     |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |                  |     |                                         |     |     |       |  |  |

| -n = Value at PO                                                     | R      | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |     |     |       |  |  |

| bit 7-6 | ADRES<1:0>: ADC Result Register bits<br>Lower 2 bits of 10-bit conversion result |

|---------|----------------------------------------------------------------------------------|

| bit 5-0 | Reserved: Do not use.                                                            |

#### REGISTER 9-5: ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1 (READ-ONLY)

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | R-x    | R-x    |

|-------|-----|-----|-----|-----|-----|--------|--------|

| —     | —   | —   | —   | —   | —   | ADRES9 | ADRES8 |

| bit 7 |     |     |     |     |     |        | bit 0  |

| Legend:           |                  |                          |                                    |  |  |  |  |

|-------------------|------------------|--------------------------|------------------------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | U = Unimplemented bit, read as '0' |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown                 |  |  |  |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

## REGISTER 9-6: ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1 (READ-ONLY)

| R-x    |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:                                                              |                  |                      |                    |  |  |  |

|----------------------------------------------------------------------|------------------|----------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                  |                      |                    |  |  |  |

| -n = Value at POR                                                    | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result

## 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 9-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =  $50^{\circ}C$  and external impedance of  $10k\Omega 5.0V VDD$  TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF $= 5\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} \ charged \ to \ within \ 1/2 \ lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-Tc}{RC}}\right) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \qquad ;[2] \ V_{CHOLD} \ charge \ response \ to \ V_{APPLIED} \ (1 - e^{\frac{-Tc}{RC}}) = V_{CHOLD} \ (1 - e^{\frac{-Tc}{RC}}) = V$$

$$V_{APPLIED}\left(1 - e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \quad \text{; combining [1] and [2]}$$

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

**3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

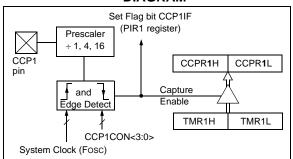

### 10.1 Capture Mode

In Capture mode, CCPR1H:CCPR1L captures the 16-bit value of the TMR1 register when an event occurs on pin CCP1. An event is defined as one of the following and is configured by the CCP1M<3:0> bits of the CCP1CON register:

- · Every falling edge

- · Every rising edge

- Every 4th rising edge

- Every 16th rising edge

When a capture is made, the Interrupt Request Flag bit CCP1IF of the PIR1 register is set. The interrupt flag must be cleared in software. If another capture occurs before the value in the CCPR1H, CCPR1L register pair is read, the old captured value is overwritten by the new captured value (see Figure 10-1).

#### 10.1.1 CCP1 PIN CONFIGURATION

In Capture mode, the CCP1 pin should be configured as an input by setting the associated TRIS control bit.

| Note: | If the CCP1 pin is configured as an output, |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | a write to the port can cause a capture     |  |  |  |  |  |  |  |

|       | condition.                                  |  |  |  |  |  |  |  |

#### FIGURE 10-1: CAPTURE MODE OPERATION BLOCK DIAGRAM

#### 10.1.2 TIMER1 MODE SELECTION

Timer1 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

#### 10.1.3 SOFTWARE INTERRUPT

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCP1IE interrupt enable bit of the PIE1 register clear to avoid false interrupts. Additionally, the user should clear the CCP1IF interrupt flag bit of the PIR1 register following any change in operating mode.

#### 10.1.4 CCP PRESCALER

There are four prescaler settings specified by the CCP1M<3:0> bits of the CCP1CON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCP1CON register before changing the prescaler (see Example 10-1).

#### EXAMPLE 10-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEI | CCP1CON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCP1CON             |

| CLRF    | CCP1CON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ; the new prescaler     |

|         |             | ; move value and CCP ON |

| MOVWF   | CCP1CON     | ;Load CCP1CON with this |

|         |             | ; value                 |

|         |             |                         |

#### 10.3.1 PWM PERIOD

The PWM period is specified by writing to the PR2 register of Timer2. The PWM period can be calculated using the formula of Equation 10-1.

### EQUATION 10-1: PWM PERIOD

$$PWM Period = [(PR2) + 1] \bullet 4 \bullet Tosc \bullet$$

$$(TMR2 Prescale Value)$$

When TMR2 is equal to PR2, the following three events occur on the next increment cycle:

- TMR2 is cleared

- The CCP1 pin is set. (Exception: If the PWM duty cycle = 0%, the pin will not be set.)

- The PWM duty cycle is latched from CCPR1L into CCPR1H.

| Note: | The Timer2 postscaler (see Section 7.1 |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------|--|--|--|--|--|--|--|--|--|

|       | "Timer2 Operation") is not used in the |  |  |  |  |  |  |  |  |  |

|       | determination of the PWM frequency.    |  |  |  |  |  |  |  |  |  |

#### 10.3.2 PWM DUTY CYCLE

The PWM duty cycle is specified by writing a 10-bit value to multiple registers: CCPR1L register and CCP1<1:0> bits of the CCP1CON register. The CCPR1L contains the eight MSbs and the CCP1<1:0> bits of the CCP1CON register contain the two LSbs. CCPR1L and CCP1<1:0> bits of the CCP1CON register can be written to at any time. The duty cycle value is not latched into CCPR1H until after the period completes (i.e., a match between PR2 and TMR2 registers occurs). While using the PWM, the CCPR1H register is read-only.

Equation 10-2 is used to calculate the PWM pulse width.

Equation 10-3 is used to calculate the PWM duty cycle ratio.

## EQUATION 10-2: PULSE WIDTH

$Pulse Width = (CCPR1L:CCP1CON < 5:4>) \bullet$

TOSC • (TMR2 Prescale Value)

## EQUATION 10-3: DUTY CYCLE RATIO

$$Duty Cycle Ratio = \frac{(CCPR1L:CCP1CON < 5:4>)}{4(PR2 + 1)}$$

The CCPR1H register and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering is essential for glitchless PWM operation.

The 8-bit timer TMR2 register is concatenated with either the 2-bit internal system clock (Fosc), or 2 bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2 prescaler is set to 1:1.

When the 10-bit time base matches the CCPR1H and 2-bit latch, then the CCP1 pin is cleared (see Figure 10-3).

### 10.3.3 PWM RESOLUTION

The resolution determines the number of available duty cycles for a given period. For example, a 10-bit resolution will result in 1024 discrete duty cycles, whereas an 8-bit resolution will result in 256 discrete duty cycles.

The maximum PWM resolution is 10 bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 10-4.

#### EQUATION 10-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PR2 + 1)]}{\log(2)}$$

bits

Note: If the pulse width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### TABLE 10-4: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz)

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1         | 1         |

| PR2 Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

## TABLE 10-5: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale (1, 4, 16) | 16       | 4        | 1         | 1         | 1          | 1         |

| PR2 Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

© 2009 Microchip Technology Inc.

## 10.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 10.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 3.0** "**Oscillator Module**" for additional details.

#### 10.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

### 10.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Configure the PWM pin (CCP1) as an input by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1 bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output by clearing the associated TRIS bit.

## 12.0 SPECIAL FEATURES OF THE CPU

The PIC16F610/616/16HV610/616 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The PIC16F610/616/16HV610/616 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Powerup Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

## 12.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See the *Memory Programming Specification* (DS41284) for more information.

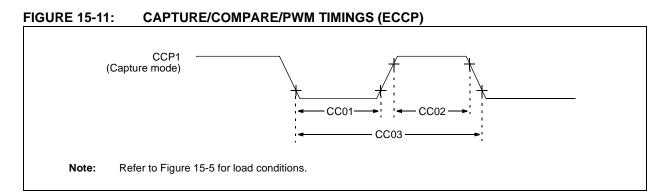

## TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

|              | Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |                      |                |                       |      |     |       |                                       |  |  |  |  |

|--------------|----------------------------------------------------------------------------------------------------------------------|----------------------|----------------|-----------------------|------|-----|-------|---------------------------------------|--|--|--|--|

| Param<br>No. | Sym                                                                                                                  | Character            | istic          | Min                   | Тур† | Max | Units | Conditions                            |  |  |  |  |

| CC01*        | TccL                                                                                                                 | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |  |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | —    | _   | ns    |                                       |  |  |  |  |

| CC02*        | ТссН                                                                                                                 | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |  |  |  |  |

|              |                                                                                                                      |                      | With Prescaler | 20                    | —    |     | ns    |                                       |  |  |  |  |

| CC03*        | TccP                                                                                                                 | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | —   | ns    | N = prescale<br>value (1, 4 or<br>16) |  |  |  |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## TABLE 15-12: PIC16F616/16HV616 A/D CONVERSION REQUIREMENTS

| Param<br>No. | Sym  | Characteristic                                                        | Min | Тур†         | Max | Units | Conditions                                                                                                                                      |

|--------------|------|-----------------------------------------------------------------------|-----|--------------|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| AD130*       | TAD  | A/D Clock Period                                                      | 1.6 |              | 9.0 | μS    | Tosc-based, VREF $\geq$ 3.0V                                                                                                                    |

|              |      |                                                                       | 3.0 | —            | 9.0 | μS    | Tosc-based, VREF full range                                                                                                                     |

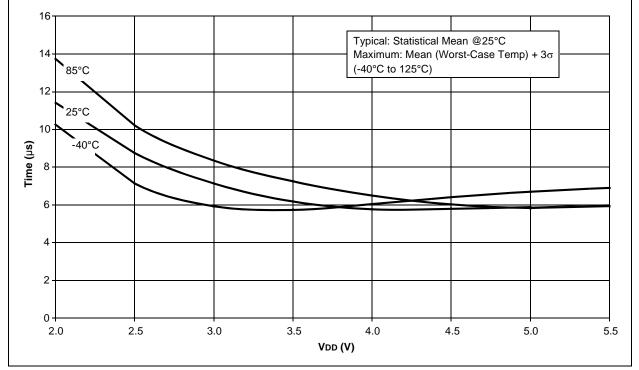

|              |      | A/D Internal RC<br>Oscillator Period                                  | 3.0 | 6.0          | 9.0 | μs    | ADCS<1:0> = 11 (ADRC mode)<br>At VDD = 2.5V                                                                                                     |

|              |      |                                                                       | 1.6 | 4.0          | 6.0 | μS    | At VDD = 5.0V                                                                                                                                   |

| AD131        | TCNV | Conversion Time<br>(not including<br>Acquisition Time) <sup>(1)</sup> | _   | 11           | _   | TAD   | Set GO/DONE bit to new data in A/D<br>Result register                                                                                           |

| AD132*       | TACQ | Acquisition Time                                                      |     | 11.5         |     | μS    |                                                                                                                                                 |

| AD133*       | TAMP | Amplifier Settling Time                                               |     |              | 5   | μS    |                                                                                                                                                 |

| AD134        | Tgo  | Q4 to A/D Clock Start                                                 | _   | Tosc/2       |     | —     |                                                                                                                                                 |

|              |      |                                                                       | _   | Tosc/2 + Tcy | _   | _     | If the A/D clock source is selected as RC, a time of TcY is added before the A/D clock starts. This allows the SLEE instruction to be executed. |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: ADRESH and ADRESL registers may be read on the following TCY cycle.

2: See Section 9.3 "A/D Acquisition Requirements" for minimum conditions.

| Param | Device          | 1 Juniter | Min | <b>T</b> |     |     | Condition                                                           |

|-------|-----------------|-----------|-----|----------|-----|-----|---------------------------------------------------------------------|

| No.   | Characteristics | Units     |     | Тур      | Max | Vdd | Note                                                                |

| D020E |                 |           | _   | 0.05     | 12  | 2.0 |                                                                     |

| Powe  | Power Down IPD  | μA        | _   | 0.15     | 13  | 3.0 | IPD Base                                                            |

|       |                 |           | _   | 0.35     | 14  | 5.0 |                                                                     |

| D021E |                 |           | _   | 0.5      | 20  | 2.0 |                                                                     |

|       |                 | μA        | _   | 2.5      | 25  | 3.0 | WDT Current                                                         |

|       |                 |           | _   | 9.5      | 36  | 5.0 |                                                                     |

| D022E |                 | μA        | _   | 5.0      | 28  | 3.0 | BOR Current                                                         |

|       |                 | μΑ        | _   | 6.0      | 36  | 5.0 | BOR Current                                                         |

| D023E |                 |           | _   | 105      | 195 | 2.0 |                                                                     |

|       |                 | μA        | _   | 110      | 210 | 3.0 | <ul> <li>IPD Current (Both</li> <li>Comparators Enabled)</li> </ul> |

|       |                 |           | _   | 116      | 220 | 5.0 |                                                                     |

|       |                 | μA        | _   | 50       | 105 | 2.0 |                                                                     |

|       |                 |           | _   | 55       | 110 | 3.0 | <ul> <li>IPD Current (One Comparator</li> <li>Enabled)</li> </ul>   |

|       |                 |           | _   | 60       | 125 | 5.0 |                                                                     |

| D024E |                 |           | _   | 30       | 58  | 2.0 |                                                                     |

|       |                 | μΑ        | _   | 45       | 85  | 3.0 | IPD (CVREF, High Range)                                             |

|       |                 |           | _   | 75       | 142 | 5.0 |                                                                     |

| D025E |                 |           | _   | 39       | 76  | 2.0 |                                                                     |

|       |                 | μA        | —   | 59       | 114 | 3.0 | IPD (CVREF, Low Range)                                              |

|       |                 |           | _   | 98       | 190 | 5.0 |                                                                     |

| D026E |                 |           | _   | 5.5      | 30  | 2.0 |                                                                     |

|       |                 | μA        | _   | 7.0      | 35  | 3.0 | IPD (T1 OSC, 32 kHz)                                                |

|       |                 |           |     | 8.5      | 45  | 5.0 |                                                                     |

| D027E |                 | μA        | _   | 0.2      | 12  | 3.0 | IPD (A2D on, not converting)                                        |

|       |                 | μΛ        |     | 0.3      | 15  | 5.0 |                                                                     |

#### TABLE 15-15: DC CHARACTERISTICS FOR IPD SPECIFICATIONS FOR PIC16F616 - H (High Temp.)

#### TABLE 15-16: WATCHDOG TIMER SPECIFICATIONS FOR PIC16F616 – H (High Temp.)

| Param<br>No. | Sym | Characteristic                                   | Units | Min | Тур | Max | Conditions        |

|--------------|-----|--------------------------------------------------|-------|-----|-----|-----|-------------------|

| 31           |     | Watchdog Timer Time-out Period<br>(No Prescaler) | ms    | 6   | 20  | 70  | 150°C Temperature |

#### TABLE 15-17: LEAKAGE CURRENT SPECIFICATIONS FOR PIC16F616 – H (High Temp.)

| Param<br>No. | Sym | Characteristic                                         | Units | Min | Тур  | Max  | Conditions             |

|--------------|-----|--------------------------------------------------------|-------|-----|------|------|------------------------|

| D061         | lı∟ | Input Leakage Current <sup>(1)</sup><br>(GP3/RA3/MCLR) | μA    | —   | ±0.5 | ±5.0 | $Vss \le Vpin \le Vdd$ |

| D062         | lı∟ | Input Leakage Current <sup>(2)</sup><br>(GP3/RA3/MCLR) | μA    | 50  | 250  | 400  | VDD = 5.0V             |

**Note 1:** This specification applies when GP3/RA3/MCLR is configured as an input with the pull-up disabled. The leakage current for the GP3/RA3/MCLR pin is higher than for the standard I/O port pins.

2: This specification applies when GP3/RA3/MCLR is configured as the MCLR Reset pin function with the weak pull-up enabled.

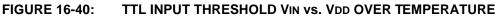

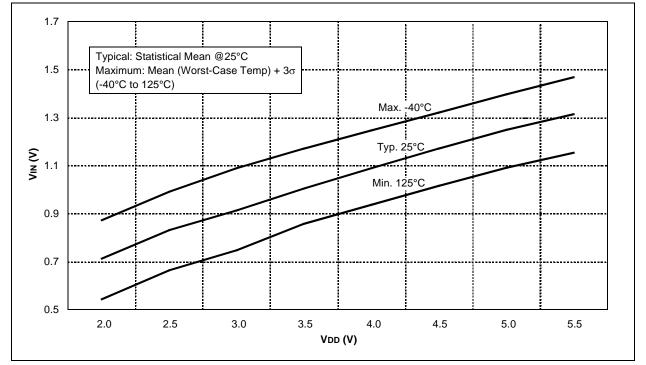

#### FIGURE 16-41: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

| Initializing PORTC42                                |

|-----------------------------------------------------|

| Saving Status and W Registers in RAM121             |

| Code Protection                                     |

| Comparator                                          |

| C2OUT as T1 Gate65                                  |

| Operation57                                         |

| Operation During Sleep61                            |

| Response Time                                       |

| Synchronizing COUT w/Timer165                       |

| Comparator Analog Input Connection Considerations64 |

| Comparator Hysteresis                               |

| Comparator Module                                   |

| Associated registers67                              |

| C1 Output State Versus Input Conditions             |

| Comparator Voltage Reference (CVREF)70              |

| Effects of a Reset61                                |

| Comparator Voltage Reference (CVREF)                |

| Response Time                                       |

| Comparator Voltage Reference (CVREF)                |

| Specifications164                                   |

| Comparators                                         |

| C2OUT as T1 Gate50                                  |

| Effects of a Reset61                                |

| Specifications164                                   |

| Compare Module. See Enhanced Capture/Compare/PWM    |

| (ECCP)                                              |

| CONFIG Register                                     |

| Configuration Bits109                               |

| CPU Features109                                     |

| Customer Change Notification Service                |

| Customer Notification Service                       |

| Customer Support                                    |

|                                                     |

## D

| Data Memory               | 14       |

|---------------------------|----------|

| DC and AC Characteristics |          |

| Graphs and Tables         |          |

| DC Characteristics        |          |

| Extended and Industrial   | 153, 154 |

| Industrial and Extended   |          |

| Development Support       |          |

| Device Overview           | 9        |

|                           |          |

## Е

| ECCP. See Enhanced Capture/Compare/PWM          |     |

|-------------------------------------------------|-----|

| ECCPAS Register1                                | 02  |

| Effects of Reset                                |     |

| PWM mode                                        | 92  |

| Electrical Specifications1                      |     |

| Enhanced Capture/Compare/PWM                    | .85 |

| Enhanced Capture/Compare/PWM (ECCP)             |     |

| Enhanced PWM Mode                               | .93 |

| Auto-Restart1                                   | 03  |

| Auto-shutdown1                                  | 02  |

| Direction Change in Full-Bridge Output Mode     | 99  |

| Full-Bridge Application                         | .97 |

| Full-Bridge Mode                                | .97 |

| Half-Bridge Application                         | 96  |

| Half-Bridge Application Examples1               | 04  |

| Half-Bridge Mode                                |     |

| Output Relationships (Active-High and Active-Lo | ow) |

| 94                                              |     |

| Output Relationships Diagram                    | .95 |

| Programmable Dead Band Delay1                   |     |

| Shoot-through Current                           |     |

| Start-up Considerations1                        |     |

|                                                 |     |

| Specifications<br>Timer Resources                      |      |

|--------------------------------------------------------|------|

| Errata                                                 | 8    |

| F                                                      |      |

| Firmware Instructions<br>Fuses. See Configuration Bits | 129  |

|                                                        |      |

| G                                                      |      |

| General Purpose Register File                          | . 14 |

| Н                                                      |      |

| High Temperature Operation                             | 168  |

| 1                                                      |      |

| ID Locations                                           | 125  |

| In-Circuit Debugger                                    |      |

| In-Circuit Serial Programming (ICSP)                   | 126  |

| Indirect Addressing, INDF and FSR registers            |      |

| Instruction Format                                     |      |

| Instruction Set                                        |      |

| ADDLW                                                  |      |

| ADDWF                                                  |      |

| ANDLW<br>ANDWF                                         |      |

| ANDWF<br>MOVF                                          |      |

| BCF                                                    |      |

| BSF                                                    |      |

| BTFSC                                                  |      |

| BTFSS                                                  |      |

| CALL                                                   | 132  |

| CLRF                                                   | 132  |

| CLRW                                                   | 132  |

| CLRWDT                                                 |      |

| COMF                                                   |      |

| DECF                                                   |      |

| DECFSZ<br>GOTO                                         |      |

| INCF                                                   |      |

| INCFSZ                                                 |      |

| IORLW                                                  |      |

| IORWF                                                  | 133  |

| MOVLW                                                  | 134  |

| MOVWF                                                  |      |

| NOP                                                    |      |

| RETFIE                                                 |      |

| RETLW                                                  |      |

| RETURN<br>RLF                                          |      |

| RRF                                                    |      |

| SLEEP                                                  |      |

| SUBLW                                                  |      |

| SUBWF                                                  | 137  |

| SWAPF                                                  | 137  |

| XORLW                                                  |      |

| XORWF                                                  |      |

| Summary Table                                          |      |

| INTCON Register                                        | . 20 |

| Internal Oscillator Block<br>INTOSC                    |      |

| Specifications 158,                                    | 159  |

| Internal Sampling Switch (Rss) Impedance               |      |

| Internet Address                                       |      |

| Interrupts                                             |      |

| ADC                                                    |      |

| Associated Registers                                   | 120  |