Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 1.75KB (1K x 14)                                                          |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 64 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | -                                                                         |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv610-i-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | Program Memory   | Data Memory  |     | 10-bit A/D |             | Timers   |                  |  |

|------------|------------------|--------------|-----|------------|-------------|----------|------------------|--|

| Device     | Flash<br>(words) | SRAM (bytes) | I/O | (ch)       | Comparators | 8/16-bit | Voltage Range    |  |

| PIC16F610  | 1024             | 64           | 11  | —          | 2           | 1/1      | 2.0-5.5V         |  |

| PIC16HV610 | 1024             | 64           | 11  | —          | 2           | 1/1      | 2.0-user defined |  |

| PIC16F616  | 2048             | 128          | 11  | 8          | 2           | 2/1      | 2.0-5.5V         |  |

| PIC16HV616 | 2048             | 128          | 11  | 8          | 2           | 2/1      | 2.0-user defined |  |

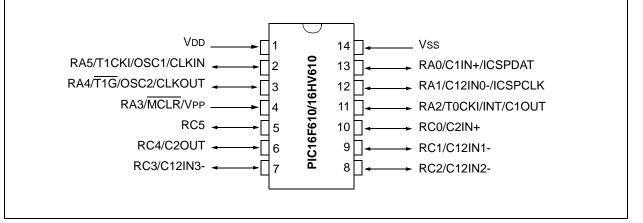

### PIC16F610/16HV610 14-Pin Diagram (PDIP, SOIC, TSSOP)

#### TABLE 1: PIC16F610/16HV610 14-PIN SUMMARY

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups         | Basic       |

|--------------------|-----|-------------|-------|------------|------------------|-------------|

| RA0                | 13  | C1IN+       | _     | IOC        | Y                | ICSPDAT     |

| RA1                | 12  | C12IN0-     | _     | IOC        | Y                | ICSPCLK     |

| RA2                | 11  | C1OUT       | T0CKI | INT/IOC    | Y                | —           |

| RA3 <sup>(1)</sup> | 4   | _           | _     | IOC        | Y <sup>(2)</sup> | MCLR/Vpp    |

| RA4                | 3   | —           | T1G   | IOC        | Y                | OSC2/CLKOUT |

| RA5                | 2   | —           | T1CKI | IOC        | Y                | OSC1/CLKIN  |

| RC0                | 10  | C2IN+       | _     | —          | —                | —           |

| RC1                | 9   | C12IN1-     |       | —          | _                | —           |

| RC2                | 8   | C12IN2-     | —     | —          | —                | —           |

| RC3                | 7   | C12IN3-     |       | _          | _                | —           |

| RC4                | 6   | C2OUT       | -     | —          | —                | —           |

| RC5                | 5   | _           |       |            | _                | _           |

|                    | 1   | _           | _     | _          |                  | Vdd         |

|                    | 14  |             |       |            | —                | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

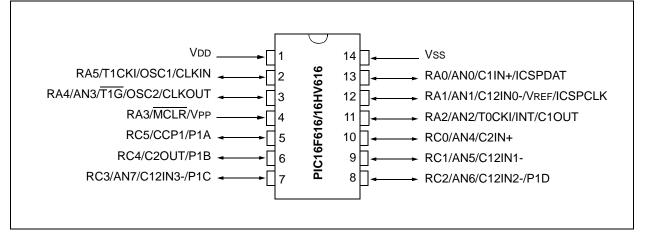

### PIC16F616/16HV616 14-Pin Diagram (PDIP, SOIC, TSSOP)

#### TABLE 2: PIC16F616/16HV616 14-PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР      | Interrupts | Pull-ups | Basic       |

|--------------------|-----|----------|-------------|-------|----------|------------|----------|-------------|

| RA0                | 13  | AN0      | C1IN+       |       | _        | IOC        | Y        | ICSPDAT     |

| RA1                | 12  | AN1/VREF | C12IN0-     |       | _        | IOC        | Y        | ICSPCLK     |

| RA2                | 11  | AN2      | C1OUT       | T0CKI | —        | INT/IOC    | Y        | —           |

| RA3 <sup>(1)</sup> | 4   | _        | —           | _     |          | IOC        | Y(2)     | MCLR/Vpp    |

| RA4                | 3   | AN3      | —           | T1G   | _        | IOC        | Y        | OSC2/CLKOUT |

| RA5                | 2   | —        | —           | T1CKI | -        | IOC        | Y        | OSC1/CLKIN  |

| RC0                | 10  | AN4      | C2IN+       | —     | —        | —          | —        | —           |

| RC1                | 9   | AN5      | C12IN1-     | _     |          | —          | —        | —           |

| RC2                | 8   | AN6      | C12IN2-     | _     | P1D      | —          | —        | —           |

| RC3                | 7   | AN7      | C12IN3-     | —     | P1C      | —          | —        | —           |

| RC4                | 6   | —        | C2OUT       | _     | P1B      | —          | —        | —           |

| RC5                | 5   | _        | —           | _     | CCP1/P1A | _          | _        | _           |

|                    | 1   | _        | —           |       | _        | _          | _        | Vdd         |

| _                  | 14  | _        |             | _     | _        | —          | —        | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

#### 2.2.2.5 PIR1 Register

The PIR1 register contains the peripheral interrupt flag bits, as shown in Register 2-5.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-5: PIR1: PERIPHERAL INTERRUPT REQUEST REGISTER 1

| U-0   | R/W-0               | R/W-0                 | R/W-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-------|-------|-----|-----------------------|--------|

| _     | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF  | C1IF  | —   | TMR2IF <sup>(1)</sup> | TMR1IF |

| bit 7 |                     |                       |       |       |     |                       | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7         | Unimplemented: Read as '0'                                                                                                               |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6         | ADIF: A/D Interrupt Flag bit <sup>(1)</sup>                                                                                              |

|               | 1 = A/D conversion complete                                                                                                              |

|               | 0 = A/D conversion has not completed or has not been started                                                                             |

| bit 5         | CCP1IF: CCP1 Interrupt Flag bit <sup>(1)</sup>                                                                                           |

|               | Capture mode:                                                                                                                            |

|               | 1 = A TMR1 register capture occurred (must be cleared in software)                                                                       |

|               | 0 = No TMR1 register capture occurred<br>Compare mode:                                                                                   |

|               | 1 = A TMR1 register compare match occurred (must be cleared in software)                                                                 |

|               | 0 = No TMR1 register compare match occurred                                                                                              |

|               | <u>PWM mode</u> :                                                                                                                        |

|               | Unused in this mode                                                                                                                      |

| bit 4         | C2IF: Comparator C2 Interrupt Flag bit                                                                                                   |

|               | 1 = Comparator C2 output has changed (must be cleared in software)                                                                       |

|               | 0 = Comparator C2 output has not changed                                                                                                 |

| bit 3         | C1IF: Comparator C1 Interrupt Flag bit                                                                                                   |

|               | <ul> <li>1 = Comparator C1 output has changed (must be cleared in software)</li> <li>0 = Comparator C1 output has not changed</li> </ul> |

| <b>h</b> it 0 | · · · · ·                                                                                                                                |

| bit 2         | Unimplemented: Read as '0'                                                                                                               |

| bit 1         | TMR2IF: Timer2 to PR2 Match Interrupt Flag bit <sup>(1)</sup>                                                                            |

|               | <ul> <li>1 = Timer2 to PR2 match occurred (must be cleared in software)</li> <li>0 = Timer2 to PR2 match has not occurred</li> </ul>     |

| bit 0         | TMR1IF: Timer1 Overflow Interrupt Flag bit                                                                                               |

|               | 1 = Timer1 register overflowed (must be cleared in software)                                                                             |

|               | 0 = Timer1 has not overflowed                                                                                                            |

| Note 1:       | PIC16F616/16HV616 only. PIC16F610/16HV610 unimplemented, read as '0'.                                                                    |

| U-0                 | U-0                                  | R/W-1            | R/W-1 | U-0                                | R/W-1 | R/W-1              | R/W-1 |  |

|---------------------|--------------------------------------|------------------|-------|------------------------------------|-------|--------------------|-------|--|

|                     | —                                    | WPUA5            | WPUA4 | _                                  | WPUA2 | WPUA1              | WPUA0 |  |

| bit 7               |                                      |                  |       |                                    |       |                    | bit 0 |  |

|                     |                                      |                  |       |                                    |       |                    |       |  |

| Legend:             |                                      |                  |       |                                    |       |                    |       |  |

| R = Readal          | ble bit                              | W = Writable     | bit   | U = Unimplemented bit, read as '0' |       |                    |       |  |

| -n = Value a        | at POR                               | '1' = Bit is set |       | '0' = Bit is cle                   | ared  | x = Bit is unknown |       |  |

|                     |                                      |                  |       |                                    |       |                    |       |  |

| bit 7-6             | Unimplemen                           | ted: Read as 'o  | )'    |                                    |       |                    |       |  |

| bit 5-4             | WPUA<5:4>: Weak Pull-up Control bits |                  |       |                                    |       |                    |       |  |

| 1 = Pull-up enabled |                                      |                  |       |                                    |       |                    |       |  |

|                     | 0 = Pull-up disabled                 |                  |       |                                    |       |                    |       |  |

#### REGISTER 4-4: WPUA: WEAK PULL-UP PORTA REGISTER

bit 3Unimplemented: Read as '0'bit 2-0WPUA<2:0>: Weak Pull-up Control bits

- - 1 =Pull-up enabled 0 =Pull-up disabled

**Note 1:** Global RAPU must be enabled for individual pull-ups to be enabled.

- 2: The weak pull-up device is automatically disabled if the pin is in Output mode (TRISA = 0).

- **3:** The RA3 pull-up is enabled when configured as MCLR and disabled as an input in the Configuration Word.

- 4: WPUA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

#### REGISTER 4-5: IOCA: INTERRUPT-ON-CHANGE PORTA REGISTER

| U-0   | U-0 | R/W-0         | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|---------------|-------|-------|-------|-------|-------|

| —     | —   | - IOCA5 IOCA4 |       | IOCA3 | IOCA2 | IOCA1 | IOCA0 |

| bit 7 |     |               |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 IOCA<5:0>: Interrupt-on-change PORTA Control bit

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOCA<5:4> always reads '1' in XT, HS and LP Oscillator modes.

| Name       | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3               | Bit 2               | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|-------|--------|--------|--------|---------------------|---------------------|--------|--------|----------------------|---------------------------------|

| ANSEL      | ANS7  | ANS6   | ANS5   | ANS4   | ANS3 <sup>(1)</sup> | ANS2 <sup>(1)</sup> | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| CM1CON0    | C10N  | C10UT  | C10E   | C1POL  | —                   | C1R                 | C1CH1  | C1CH0  | 0000 -000            | 0000 -000                       |

| CM2CON0    | C2ON  | C2OUT  | C2OE   | C2POL  | —                   | C2R                 | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| INTCON     | GIE   | PEIE   | TOIE   | INTE   | RAIE                | T0IF                | INTF   | RAIF   | 0000 0000            | 0000 0000                       |

| IOCA       |       | —      | IOCA5  | IOCA4  | IOCA3               | IOCA2               | IOCA1  | IOCA0  | 00 0000              | 00 0000                         |

| OPTION_REG | RAPU  | INTEDG | TOCS   | TOSE   | PSA                 | PS2                 | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| PORTA      | _     | _      | RA5    | RA4    | RA3                 | RA2                 | RA1    | RA0    | x0 x000              | u0 u000                         |

| TRISA      | _     | —      | TRISA5 | TRISA4 | TRISA3              | TRISA2              | TRISA1 | TRISA0 | 11 1111              | 11 1111                         |

| WPUA       | _     | _      | WPUA5  | WPUA4  | _                   | WPUA2               | WPUA1  | WPUA0  | 11 -111              | 11 -111                         |

#### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH PORTA

$\label{eq:Legend: Legend: Legend: u = unchanged, - = unimplemented locations read as `0'. Shaded cells are not used by PORTA.$

Note 1: For PIC16F616/HV616 only.

other applications. For more information on Delta-Sigma A/D converters, see the Microchip web site (www.microchip.com).

| Note: | TMR1GE bit of the T1CON register must                 |

|-------|-------------------------------------------------------|

|       | be set to use either $\overline{T1G}$ or C2OUT as the |

|       | Timer1 gate source. See the CM2CON1                   |

|       | register (Register 8-3) for more informa-             |

|       | tion on selecting the Timer1 gate source.             |

Timer1 gate can be inverted using the T1GINV bit of the T1CON register, whether it originates from the T1G pin or Comparator C2 output. This configures Timer1 to measure either the active-high or active-low time between events.

### 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

- T1SYNC bit of the T1CON register

- TMR1CS bit of the T1CON register

- T1OSCEN bit of the T1CON register (can be set)

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

### 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

#### 6.9 ECCP Capture/Compare Time Base (PIC16F616/16HV616 Only)

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 10.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC16F616/16HV616 Only)".

#### 6.10 ECCP Special Event Trigger (PIC16F616/16HV616 Only)

When the ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see **Section 10.2.4** "**Special Event Trigger**".

#### 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see **Section 8.8.2** "Synchronizing Comparator C2 Output to Timer1".

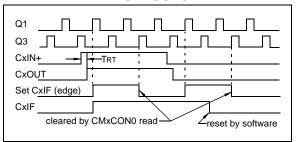

#### 8.4 Comparator Interrupt Operation

The comparator interrupt flag can be set whenever there is a change in the output value of the comparator. Changes are recognized by means of a mismatch circuit which consists of two latches and an exclusive-or gate (see Figure 8-2 and Figure 8-3). One latch is updated with the comparator output level when the CMxCON0 register is read. This latch retains the value until the next read of the CMxCON0 register or the occurrence of a Reset. The other latch of the mismatch circuit is updated on every Q1 system clock. A mismatch condition will occur when a comparator output change is clocked through the second latch on the Q1 clock cycle. At this point the two mismatch latches have opposite output levels which is detected by the exclusive-or gate and fed to the interrupt circuitry. The mismatch condition persists until either the CMxCON0 register is read or the comparator output returns to the previous state.

- Note 1: A write operation to the CMxCON0 register will also clear the mismatch condition because all writes include a read operation at the beginning of the write cycle.

- **2:** Comparator interrupts will operate correctly regardless of the state of CxOE.

The comparator interrupt is set by the mismatch edge and not the mismatch level. This means that the interrupt flag can be reset without the additional step of reading or writing the CMxCON0 register to clear the mismatch registers. When the mismatch registers are cleared, an interrupt will occur upon the comparator's return to the previous state, otherwise no interrupt will be generated.

Software will need to maintain information about the status of the comparator output, as read from the CMxCON0 register, or CM2CON1 register, to determine the actual change that has occurred.

The CxIF bit of the PIR1 register is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, an interrupt can be generated.

The CxIE bit of the PIE1 register and the PEIE and GIE bits of the INTCON register must all be set to enable comparator interrupts. If any of these bits are cleared, the interrupt is not enabled, although the CxIF bit of the PIR1 register will still be set if an interrupt condition occurs.

# FIGURE 8-4: COMPARATOR INTERRUPT TIMING W/O CMxCON0 READ

### FIGURE 8-5:

COMPARATOR INTERRUPT TIMING WITH CMxCON0 READ

reset by software

- Note 1: If a change in the CMxCON0 register (CxOUT) should occur when a read operation is being executed (start of the Q2 cycle), then the CxIF of the PIR1 register interrupt flag may not get set.

- When either comparator is first enabled, bias circuitry in the comparator module may cause an invalid output from the comparator until the bias circuitry is stable. Allow about 1 μs for bias settling then clear the mismatch condition and interrupt flags before enabling comparator interrupts.

| R/W-0              | R/W-0               | R/W-0                                                                  | R/W-0           | R/S-0             | R/S-0             | U-0             | R/W-0   |

|--------------------|---------------------|------------------------------------------------------------------------|-----------------|-------------------|-------------------|-----------------|---------|

| SR1 <sup>(2)</sup> | SR0 <sup>(2)</sup>  | C1SEN                                                                  | C2REN           | PULSS             | PULSR             | —               | SRCLKEN |

| bit 7              |                     |                                                                        |                 |                   |                   |                 | bit 0   |

| Legend:            |                     |                                                                        |                 | S = Bit is set o  | nly -             |                 |         |

| R = Readable b     | t                   | W = Writable bi                                                        | +               |                   | ented bit, read a | s 'O'           |         |

| -n = Value at P    |                     | (1) = Bit is set                                                       | ·               | '0' = Bit is clea | -                 | x = Bit is unkr |         |

|                    | JK                  | I = DILIS SEL                                                          |                 |                   | ieu               |                 | IOWIT   |

| bit 7              | 1 = C2OUT           | h Configuration bing pin is the latch $\overline{Q}$ pin is the C2 con | output          |                   |                   |                 |         |

| bit 6              | 1 = C1OUT           | h Configuration bi<br>pin is the latch Q<br>pin is the C1 Cor          | output          |                   |                   |                 |         |

| bit 5              |                     | et Enable bit<br>arator output sets<br>arator output has               |                 | latch             |                   |                 |         |

| bit 4              | 1 = C2  comparation | eset Enable bit<br>arator output rese<br>arator output has             |                 | latch             |                   |                 |         |

| bit 3              | 1 = Triggers        | the SET Input of pulse generator to trigger pulse gen                  | set SR latch. E |                   | reset by hardwa   | are.            |         |

| bit 2              | 1 = Triggers        | e the Reset Input o<br>pulse generator to<br>trigger pulse gen         | reset SR latch  |                   | ely reset by hard | ware.           |         |

| bit 1              | Unimplement         | ed: Read as '0'                                                        |                 |                   |                   |                 |         |

| bit 0              |                     | R Latch Set Clock<br>of SR latch is pul-<br>of SR latch is not         | sed with SRCL   |                   |                   |                 |         |

#### REGISTER 8-4: SRCON0: SR LATCH CONTROL 0 REGISTER

the pin), regardless of the SR latch operation.2: To enable an SR Latch output to the pin, the appropriate CxOE, and TRIS bits must be properly configured.

#### REGISTER 8-5: SRCON1: SR LATCH CONTROL 1 REGISTER

| R/W-0       | R/W-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 |

|-------------|-------|-----|-----|-----|-----|-----|-----|

| SRCS1       | SRCS0 | —   | —   | —   | —   | —   | —   |

| bit 7 bit 0 |       |     |     |     |     |     |     |

| Legend:           |                  | S = Bit is set only -    |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 7-6 | SRCS<1:0>: SR Latch Clock Prescale bits |

|---------|-----------------------------------------|

|         | 00 = Fosc/16                            |

|         | 01 = Fosc/32                            |

|         | 10 = Fosc/64                            |

11 = Fosc/128

bit 5-0 Unimplemented: Read as '0'

#### EXAMPLE 9-1: A/D CONVERSION

| ;for poll<br>;and AN0<br>; | ing, Vdd refe<br>input.<br>on start & po | gures the ADC<br>rrence, Frc clock<br>lling for completion |

|----------------------------|------------------------------------------|------------------------------------------------------------|

| ,<br>BANKSEL               | ADCON1                                   | ;                                                          |

| MOVLW                      |                                          | ,<br>;ADC Fre clock                                        |

| MOVWF                      |                                          | ;                                                          |

| BANKSEL                    |                                          | ;                                                          |

| BSF                        | TRISA,0                                  | ;Set RA0 to input                                          |

| BANKSEL                    |                                          | ;                                                          |

| BSF                        | ANSEL,0                                  | Set RA0 to analog                                          |

| BANKSEL                    |                                          | ;                                                          |

| MOVLW                      | B'10000001'                              | Right justify,                                             |

| MOVWF                      | ADCON0                                   | ;Vdd Vref, ANO, On                                         |

| CALL                       | SampleTime                               | Acquisiton delay                                           |

| BSF                        | ADCON0,GO                                | ;Start conversion                                          |

| BTFSC                      | ADCON0,GO                                | ;Is conversion done?                                       |

| GOTO                       | \$-1                                     | ;No, test again                                            |

| BANKSEL                    | ADRESH                                   | ;                                                          |

| MOVF                       | ADRESH,W                                 | ;Read upper 2 bits                                         |

| MOVWF                      | RESULTHI                                 | ;store in GPR space                                        |

| BANKSEL                    | ADRESL                                   | ;                                                          |

| MOVF                       | ADRESL,W                                 | ;Read lower 8 bits                                         |

| MOVWF                      | RESULTLO                                 | ;Store in GPR space                                        |

|                            |                                          |                                                            |

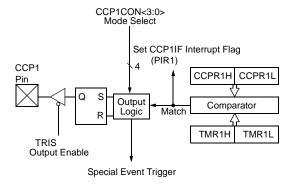

#### 10.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 module may:

- Toggle the CCP1 output

- Set the CCP1 output

- Clear the CCP1 output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

#### FIGURE 10-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 10.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|

|       | the CCP1 compare output latch to the        |  |  |  |  |  |  |  |

|       | default low level. This is not the PORT I/O |  |  |  |  |  |  |  |

|       | data latch.                                 |  |  |  |  |  |  |  |

#### 10.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 10.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 10.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP1 module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP1 module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

| FIGURE 12-9:                                            | WAKE-UP FROM S                                                                                      | SLEEP THRO           | UGH INTER       | RUPT                     |                   |                   |

|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------|-----------------|--------------------------|-------------------|-------------------|

| ; Q1 Q2<br>OSC1/¯<br>CLKOUT <sup>(4)</sup> ;<br>INT pin | :  Q3   Q4 ; Q1   Q2   Q3   Q4 ; Q<br>////////////////////////////////////                          |                      | Q1 Q2 Q3 Q4<br> | ( Q1 Q2  Q3 Q4;<br>/~_~/ | Q1 Q2 Q3 Q4;(<br> | Q1 Q2 Q3 Q4<br>\/ |

| INTF flag<br>(INTCON reg.)                              |                                                                                                     |                      | Interrupt Laten | <sub>Cy</sub> (3)        |                   |                   |

| GIE bit<br>(INTCON reg.)                                |                                                                                                     | rocessor in<br>Sleep |                 |                          |                   |                   |

| Instruction Flow<br>PC X F                              | PC { PC+1 }                                                                                         | PC + 2               | X PC + 2        | PC+2 X                   | 0004h X           | 0005h             |

|                                                         | c) = Sleep Inst(PC + 1)                                                                             |                      | Inst(PC + 2)    |                          | Inst(0004h)       | Inst(0005h)       |

| Instruction { Inst(                                     | PC – 1) Sleep                                                                                       |                      | Inst(PC + 1)    | Dummy Cycle              | Dummy Cycle       | Inst(0004h)       |

| 2: Tost = 1                                             | or LP Oscillator mode assumed<br>1024 Tosc (drawing not to scale<br>' assumed. In this case after w | e). This delay does  |                 |                          |                   | in-line.          |

4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

#### 12.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using  $\mathsf{ICSP}^{\mathsf{TM}}$  for verification purposes.

| Note: | The entire Flash program memory will be   |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|

|       | erased when the code protection is turned |  |  |  |  |  |  |  |

|       | off. See the Memory Programming           |  |  |  |  |  |  |  |

|       | Specification (DS41284) for more          |  |  |  |  |  |  |  |

|       | information.                              |  |  |  |  |  |  |  |

#### 12.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are used.

#### 14.2 MPLAB C Compilers for Various Device Families

The MPLAB C Compiler code development systems are complete ANSI C compilers for Microchip's PIC18, PIC24 and PIC32 families of microcontrollers and the dsPIC30 and dsPIC33 families of digital signal controllers. These compilers provide powerful integration capabilities, superior code optimization and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

#### 14.3 HI-TECH C for Various Device Families

The HI-TECH C Compiler code development systems are complete ANSI C compilers for Microchip's PIC family of microcontrollers and the dsPIC family of digital signal controllers. These compilers provide powerful integration capabilities, omniscient code generation and ease of use.

For easy source level debugging, the compilers provide symbol information that is optimized to the MPLAB IDE debugger.

The compilers include a macro assembler, linker, preprocessor, and one-step driver, and can run on multiple platforms.

#### 14.4 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multi-purpose source files

- Directives that allow complete control over the assembly process

#### 14.5 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler and the MPLAB C18 C Compiler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

#### 14.6 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC devices. MPLAB C Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command line interface

- · Rich directive set

- Flexible macro language

- MPLAB IDE compatibility

#### TABLE 15-7: **COMPARATOR SPECIFICATIONS**

|              | <b>rd Operatii</b><br>ng Tempera | ng Conditions (unless otherwise ature $-40^{\circ}C \le TA \le +125^{\circ}C$ | stated) |     |       |           |       |          |

|--------------|----------------------------------|-------------------------------------------------------------------------------|---------|-----|-------|-----------|-------|----------|

| Param<br>No. | Sym                              | Characteristics                                                               |         | Min | Тур†  | Мах       | Units | Comments |

| CM01         | Vos                              | Input Offset Voltage <sup>(2)</sup>                                           |         |     | ± 5.0 | ± 10      | mV    |          |

| CM02         | Vсм                              | Input Common Mode Voltage                                                     |         | 0   | —     | Vdd - 1.5 | V     |          |

| CM03*        | CMRR                             | Common Mode Rejection Ratio                                                   |         | +55 | —     | —         | dB    |          |

| CM04*        | Trt                              | Response Time <sup>(1)</sup>                                                  | Falling | —   | 150   | 600       | ns    |          |

|              |                                  |                                                                               | Rising  |     | 200   | 1000      | ns    |          |

| CM05*        | TMC2COV                          | Comparator Mode Change to Output Valid                                        |         | —   | —     | 10        | μS    |          |

| CM06*        | VHYS                             | Input Hysteresis Voltage                                                      |         |     | 45    | 60        | mV    |          |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Response time is measured with one comparator input at (VDD - 1.5)/2 - 100 mV to (VDD - 1.5)/2 + 20 mV. Note 1: The other input is at (VDD -1.5)/2.

2: Input offset voltage is measured with one comparator input at (VDD - 1.5V)/2.

#### **COMPARATOR VOLTAGE REFERENCE (CVREF) SPECIFICATIONS TABLE 15-8:**

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                  |     |                  |                |            |                                             |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------------------|-----|------------------|----------------|------------|---------------------------------------------|

| Param<br>No.                                                                                                         | Sym  | Characteristics                  | Min | Тур†             | Max            | Units      | Comments                                    |

| CV01                                                                                                                 | Clsb | Step Size <sup>(2)</sup>         |     | Vdd/24<br>Vdd/32 |                | V<br>V     | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV02                                                                                                                 | CACC | Absolute Accuracy <sup>(3)</sup> | _   |                  | ± 1/2<br>± 1/2 | LSb<br>LSb | Low Range (VRR = 1)<br>High Range (VRR = 0) |

| CV03                                                                                                                 | CR   | Unit Resistor Value (R)          | —   | 2k               | _              | Ω          |                                             |

| CV04                                                                                                                 | CST  | Settling Time <sup>(1)</sup>     | _   | —                | 10             | μS         |                                             |

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: Settling time measured while VRR = 1 and VR<3:0> transitions from '0000' to '1111'.

- 2: See Section 8.11 "Comparator Voltage Reference" for more information.

- **3:** Absolute Accuracy when CVREF output is  $\leq$  (VDD-1.5).

#### TABLE 15-9: VOLTAGE REFERENCE SPECIFICATIONS

| VR Voltage Reference Specifications |         | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |      |      |       |          |

|-------------------------------------|---------|----------------------------------------------------------------------------------------------------------------------|------|------|------|-------|----------|

| Param<br>No.                        | Symbol  | Characteristics                                                                                                      | Min  | Тур  | Max  | Units | Comments |

| VR01                                | VP6out  | VP6 voltage output                                                                                                   | 0.50 | 0.6  | 0.7  | V     |          |

| VR02                                | V1P2out | V1P2 voltage output                                                                                                  | 1.05 | 1.20 | 1.35 | V     |          |

| VR03*                               | TSTABLE | Settling Time                                                                                                        |      | 10   |      | μS    |          |

These parameters are characterized but not tested.

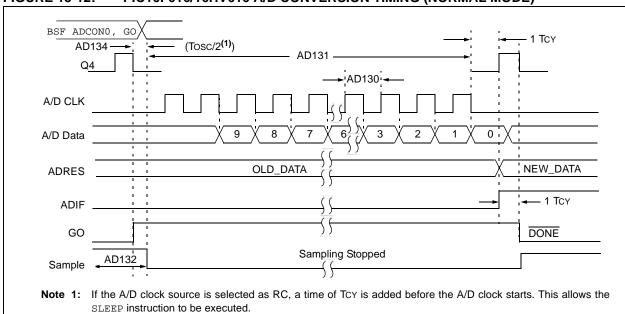

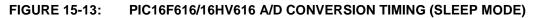

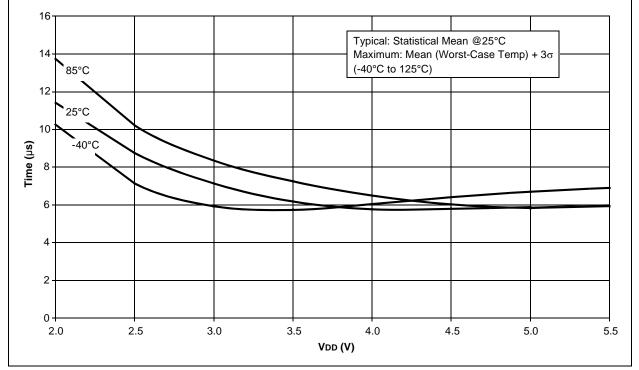

### FIGURE 15-12: PIC16F616/16HV616 A/D CONVERSION TIMING (NORMAL MODE)

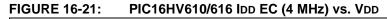

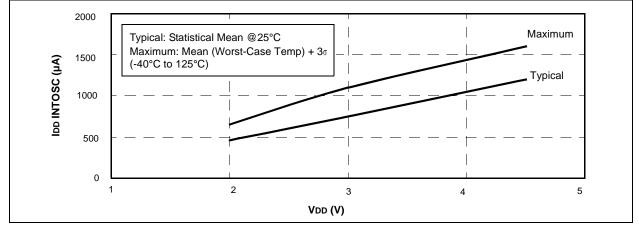

#### FIGURE 16-20: PIC16HV610/616 IDD EC (1 MHz) vs. VDD

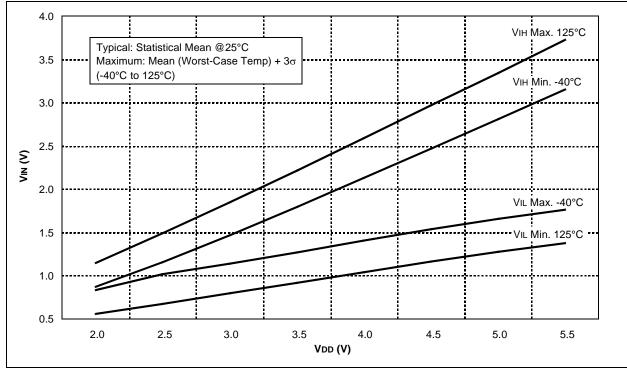

#### FIGURE 16-41: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

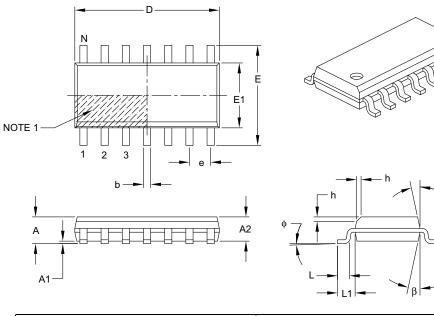

#### 14-Lead Plastic Small Outline (SL) – Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |

|--------------------------|------------------|-------------|----------|------|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |

| Number of Pins           | N                |             | 14       |      |  |

| Pitch                    | е                |             | 1.27 BSC |      |  |

| Overall Height           | А                | -           | -        | 1.75 |  |

| Molded Package Thickness | A2               | 1.25        | -        | -    |  |

| Standoff §               | A1               | 0.10        | -        | 0.25 |  |

| Overall Width            | E                | 6.00 BSC    |          |      |  |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |  |

| Overall Length           | D                | 8.65 BSC    |          |      |  |

| Chamfer (optional)       | h                | 0.25        | -        | 0.50 |  |

| Foot Length              | L                | 0.40        | -        | 1.27 |  |

| Footprint                | L1               |             | 1.04 REF |      |  |

| Foot Angle               | φ                | 0°          | -        | 8°   |  |

| Lead Thickness           | С                | 0.17        | -        | 0.25 |  |

| Lead Width               | b                | 0.31        | -        | 0.51 |  |

| Mold Draft Angle Top     | α                | 5°          | -        | 15°  |  |

| Mold Draft Angle Bottom  | β                | 5°          | -        | 15°  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-065B

NOTES: