Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product StatusActiveCore ProcessorPICCore Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-AMS Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14tps://www.exfl.com/product-detail/microchip-technology/pic16hv610-i-st | Details                    |                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------------------------------------------------|

| Core Size8-BitSpeed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                              | Product Status             | Active                                                                    |

| Speed20MHzConnectivity-PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                            | Core Processor             | PIC                                                                       |

| Connectivity-PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                                      | Core Size                  | 8-Bit                                                                     |

| PeripheralsBrown-out Detect/Reset, POR, WDTNumber of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                                                   | Speed                      | 20MHz                                                                     |

| Number of I/O11Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                                                                                              | Connectivity               | -                                                                         |

| Program Memory Size1.75KB (1K x 14)Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)                                                                                                                                                                                                             | Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Program Memory TypeFLASHEEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                 | Number of I/O              | 11                                                                        |

| EEPROM Size-RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                         | Program Memory Size        | 1.75KB (1K x 14)                                                          |

| RAM Size64 x 8Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                     | Program Memory Type        | FLASH                                                                     |

| Voltage - Supply (Vcc/Vdd)2V ~ 5VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                   | EEPROM Size                | -                                                                         |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                    | RAM Size                   | 64 x 8                                                                    |

| Oscillator TypeInternalOperating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                                    | Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Operating Temperature-40°C ~ 85°C (TA)Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                                                           | Data Converters            | -                                                                         |

| Mounting TypeSurface MountPackage / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                                                                                                 | Oscillator Type            | Internal                                                                  |

| Package / Case14-TSSOP (0.173", 4.40mm Width)Supplier Device Package14-TSSOP                                                                                                                                                                                                                                                                                                                                                                                                           | Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Supplier Device Package 14-TSSOP                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Mounting Type              | Surface Mount                                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                           |

| Purchase URL https://www.e-xfl.com/product-detail/microchip-technology/pic16hv610-i-st                                                                                                                                                                                                                                                                                                                                                                                                 | Supplier Device Package    | 14-TSSOP                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv610-i-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.2.2.1 STATUS Register

The STATUS register, shown in Register 2-1, contains:

- the arithmetic status of the ALU

- · the Reset status

-n = Value at POR

• the bank select bits for data memory (RAM)

The STATUS register can be the destination for any instruction, like any other register. If the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic. Furthermore, the TO and PD bits are not writable. Therefore, the result of an instruction with the STATUS register as destination may be different than intended.

For example, CLRF STATUS, will clear the upper three bits and set the Z bit. This leaves the STATUS register as `000u uluu' (where u = unchanged).

It is recommended, therefore, that only BCF, BSF, SWAPF and MOVWF instructions are used to alter the STATUS register, because these instructions do not affect any Status bits. For other instructions not affecting any Status bits, see the **Section 13.0 "Instruction Set Summary"**.

- Note 1: Bits IRP and RP1 of the STATUS register are not used by the PIC16F610/616/16HV610/616 and should be maintained as clear. Use of these bits is not recommended, since this may affect upward compatibility with future products.

- 2: The <u>C</u> and <u>DC</u> bits operate as a Borrow and Digit Borrow out bit, respectively, in subtraction. See the SUBLW and SUBWF instructions for examples.

x = Bit is unknown

### REGISTER 2-1: STATUS: STATUS REGISTER

'1' = Bit is set

| Reserved         | Reserved | R/W-0           | R-1 | R-1          | R/W-x              | R/W-x | R/W-x |

|------------------|----------|-----------------|-----|--------------|--------------------|-------|-------|

| IRP              | RP1      | RP0             | то  | PD           | Z                  | DC    | С     |

| bit 7            |          | •               | •   |              |                    |       | bit 0 |

|                  |          |                 |     |              |                    |       |       |

| Legend:          |          |                 |     |              |                    |       |       |

| R = Readable bit |          | W = Writable bi | t   | U = Unimplem | ented bit, read as | '0'   |       |

'0' = Bit is cleared

| bit 7   | IRP: This bit is reserved and should be maintained as '0'                                                                                                                                                                                           |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | RP1: This bit is reserved and should be maintained as '0'                                                                                                                                                                                           |

| bit 5   | <b>RP0:</b> Register Bank Select bit (used for direct addressing)<br>1 = Bank 1 (80h – FFh)<br>0 = Bank 0 (00h – 7Fh)                                                                                                                               |

| bit 4   | <b>TO:</b> Time-out bit<br>1 = After power-up, CLRWDT instruction or SLEEP instruction                                                                                                                                                              |

|         | 0 = A WDT time-out occurred                                                                                                                                                                                                                         |

| bit 3   | PD: Power-down bit                                                                                                                                                                                                                                  |

|         | 1 = After power-up or by the CLRWDT instruction                                                                                                                                                                                                     |

|         | 0 = By execution of the SLEEP instruction                                                                                                                                                                                                           |

| bit 2   | Z: Zero bit                                                                                                                                                                                                                                         |

|         | 1 = The result of an arithmetic or logic operation is zero                                                                                                                                                                                          |

|         | 0 = The result of an arithmetic or logic operation is not zero                                                                                                                                                                                      |

| bit 1   | DC: Digit Carry/Borrow bit (ADDWF, ADDLW, SUBLW, SUBWF instructions), For Borrow, the polarity is reversed.                                                                                                                                         |

|         | 1 = A carry-out from the 4th low-order bit of the result occurred                                                                                                                                                                                   |

|         | 0 = No carry-out from the 4th low-order bit of the result                                                                                                                                                                                           |

| bit 0   | C: Carry/Borrow bit <sup>(1)</sup> (ADDWF, ADDLW, SUBLW, SUBWF instructions)                                                                                                                                                                        |

|         | 1 = A carry-out from the Most Significant bit of the result occurred                                                                                                                                                                                |

|         | 0 = No carry-out from the Most Significant bit of the result occurred                                                                                                                                                                               |

| Note 1: | For Borrow, the polarity is reversed. A subtraction is executed by adding the two's complement of the second operand.<br>For rotate (RRF, RLF) instructions, this bit is loaded with either the high-order or low-order bit of the source register. |

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

#### REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RAIE  | T0IF  | INTF  | RAIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |

| bit 5 | <b>T0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                       |

| bit 4 | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                         |

| bit 3 | <b>RAIE:</b> PORTA Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA change interrupt<br>0 = Disables the PORTA change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                       |

| bit 1 | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                       |

| bit 0 | <b>RAIF:</b> PORTA Change Interrupt Flag bit<br>1 = When at least one of the PORTA <5:0> pins changed state (must be cleared in software)<br>0 = None of the PORTA <5:0> pins have changed state |

|       |                                                                                                                                                                                                  |

Note 1: IOCA register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

#### 2.2.2.4 PIE1 Register

The PIE1 register contains the peripheral interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

#### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| U-0   | R/W-0               | R/W-0                 | R/W-0 | R/W-0 | U-0 | R/W-0                 | R/W-0  |

|-------|---------------------|-----------------------|-------|-------|-----|-----------------------|--------|

| —     | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE  | C1IE  | —   | TMR2IE <sup>(1)</sup> | TMR1IE |

| bit 7 |                     |                       |       |       |     |                       | bit 0  |

| Legend:    |                                                                          |                                                   |                             |                    |  |  |  |

|------------|--------------------------------------------------------------------------|---------------------------------------------------|-----------------------------|--------------------|--|--|--|

| R = Read   | able bit                                                                 | W = Writable bit                                  | U = Unimplemented bit,      | read as '0'        |  |  |  |

| -n = Value | e at POR                                                                 | '1' = Bit is set                                  | '0' = Bit is cleared        | x = Bit is unknown |  |  |  |

| L:4 7      |                                                                          |                                                   |                             |                    |  |  |  |

| bit 7      | •                                                                        | mented: Read as '0'                               | (1)                         |                    |  |  |  |

| bit 6      |                                                                          | D Converter (ADC) Interrupt                       | Enable bit <sup>(1)</sup>   |                    |  |  |  |

|            |                                                                          | les the ADC interrupt<br>bles the ADC interrupt   |                             |                    |  |  |  |

| bit 5      | CCP1IE:                                                                  | CCP1 Interrupt Enable bit <sup>(1)</sup>          | 1                           |                    |  |  |  |

|            |                                                                          | les the CCP1 interrupt<br>bles the CCP1 interrupt |                             |                    |  |  |  |

| bit 4      | <b>C2IE:</b> Co                                                          | C2IE: Comparator C2 Interrupt Enable bit          |                             |                    |  |  |  |

|            | 1 = Enab                                                                 | les the Comparator C2 interr                      | rupt                        |                    |  |  |  |

|            | 0 = Disat                                                                | oles the Comparator C2 inter                      | rupt                        |                    |  |  |  |

| bit 3      | <b>C1IE:</b> Co                                                          | mparator C1 Interrupt Enabl                       | e bit                       |                    |  |  |  |

|            | 1 = Enab                                                                 | les the Comparator C1 interr                      | rupt                        |                    |  |  |  |

|            | 0 = Disat                                                                | oles the Comparator C1 inter                      | rupt                        |                    |  |  |  |

| bit 2      | 2 Unimplemented: Read as '0'                                             |                                                   |                             |                    |  |  |  |

| bit 1      | 1 <b>TMR2IE:</b> Timer2 to PR2 Match Interrupt Enable bit <sup>(1)</sup> |                                                   |                             |                    |  |  |  |

|            | 1 = Enab                                                                 | les the Timer2 to PR2 match                       | n interrupt                 |                    |  |  |  |

|            | 0 = Disat                                                                | oles the Timer2 to PR2 matcl                      | h interrupt                 |                    |  |  |  |

| bit 0      | TMR1IE:                                                                  | Timer1 Overflow Interrupt E                       | nable bit                   |                    |  |  |  |

|            | 1 = Enab                                                                 | les the Timer1 overflow inter                     | rupt                        |                    |  |  |  |

|            | 0 = Disat                                                                | oles the Timer1 overflow inte                     | rrupt                       |                    |  |  |  |

| Note 1:    | PIC16F616/16                                                             | 6HV616 only. PIC16F610/16                         | HV610 unimplemented, read a | as '0'.            |  |  |  |

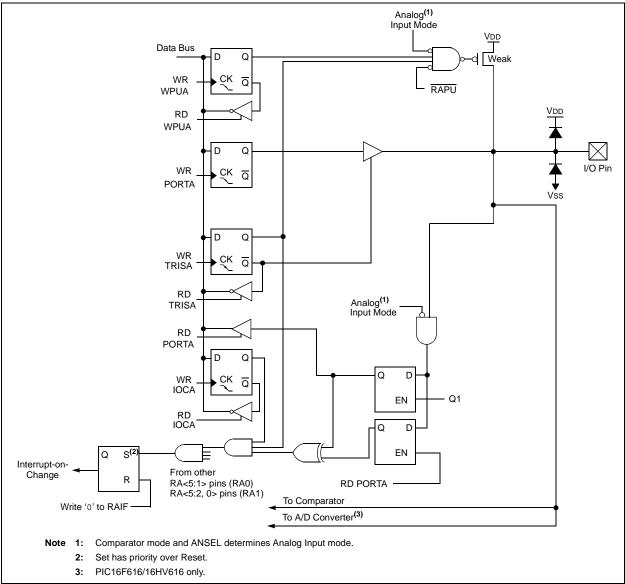

#### 4.2.4 PIN DESCRIPTIONS AND DIAGRAMS

Each PORTA pin is multiplexed with other functions. The pins and their combined functions are briefly described here. For specific information about individual functions such as the Comparator or the ADC, refer to the appropriate section in this data sheet.

### 4.2.4.1 RA0/AN0<sup>(1)</sup>/C1IN+/ICSPDAT

Figure 4-1 shows the diagram for this pin. The RA0 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog non-inverting input to the comparator

- In-Circuit Serial Programming data

#### 4.2.4.2 RA1/AN1<sup>(1)</sup>/C12IN0-/VREF<sup>(1)</sup>/ ICSPCLK

Figure 4-1 shows the diagram for this pin. The RA1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- an analog inverting input to the comparator

- a voltage reference input for the ADC<sup>(1)</sup>

- In-Circuit Serial Programming clock

Note 1: PIC16F616/16HV616 only.

#### FIGURE 4-1: BLOCK DIAGRAM OF RA<1:0>

#### 7.0 **TIMER2 MODULE** (PIC16F616/16HV616 ONLY)

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

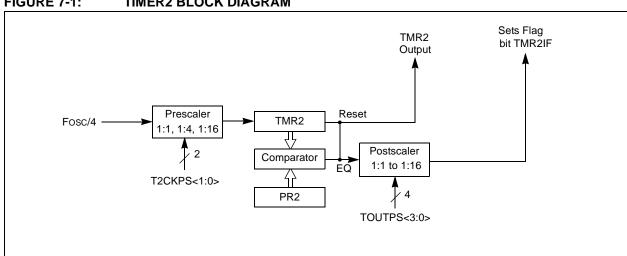

See Figure 7-1 for a block diagram of Timer2.

#### 7.1 **Timer2 Operation**

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

| FIGURE 7-1: | <b>TIMER2 BLOCK DIAGRAM</b> |

|-------------|-----------------------------|

|             |                             |

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by setting the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR) Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

#### REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

| R/W-0                  | R/W-0                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                       | R/W-0                               | R/W-0             | R/W-0             | R/W-0            | R/W-0 |

|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-------------------|-------------------|------------------|-------|

| ADFM                   | VCFG                                                                                                                                                                                                                          | CHS3                                                                                                                                                                        | CHS2                                | CHS1              | CHS0              | GO/DONE          | ADON  |

| bit 7                  |                                                                                                                                                                                                                               |                                                                                                                                                                             |                                     |                   |                   |                  | bit   |

|                        |                                                                                                                                                                                                                               |                                                                                                                                                                             |                                     |                   |                   |                  |       |

| Legend:<br>P - Poodobl | o hit                                                                                                                                                                                                                         | W = Writable bi                                                                                                                                                             | ÷                                   |                   | ented bit, read a | ος (Ω'           |       |

| R = Readable bit       |                                                                                                                                                                                                                               |                                                                                                                                                                             | it.                                 | •                 |                   |                  |       |

| -n = Value at          | POR                                                                                                                                                                                                                           | '1' = Bit is set                                                                                                                                                            |                                     | '0' = Bit is clea | reu               | x = Bit is unkno | wn    |

| bit 7                  | <b>ADFM:</b> A/D C<br>1 = Right justi<br>0 = Left justifie                                                                                                                                                                    |                                                                                                                                                                             | Format Select I                     | bit               |                   |                  |       |

| bit 6                  | <b>VCFG:</b> Voltag<br>1 = VREF pin<br>0 = VDD                                                                                                                                                                                | e Reference bit                                                                                                                                                             |                                     |                   |                   |                  |       |

| bit 5-2                | 0000 = Char<br>0001 = Char<br>0010 = Char<br>0011 = Char<br>0100 = Char<br>0101 = Char<br>0110 = Char<br>0111 = Char<br>1000 = Rese<br>1001 = Rese<br>1010 = Rese<br>1011 = Rese<br>1100 = CVRE<br>1101 = 0.6V<br>1110 = 1.2V | nel 01 (AN1)<br>nel 02 (AN2)<br>nel 03 (AN3)<br>nel 04 (AN4)<br>nel 05 (AN5)<br>nel 06 (AN6)<br>nel 07 (AN7)<br>rved – do not use<br>rved – do not use<br>rved – do not use | ference <sup>(1)</sup>              |                   |                   |                  |       |

| bit 1                  | 1 = A/D conve<br>This bit is                                                                                                                                                                                                  | D Conversion Sta<br>rsion cycle in pro-<br>automatically clea<br>rsion completed/r                                                                                          | gress. Setting t<br>ared by hardwar |                   |                   |                  |       |

| bit 0                  | ADON: ADC I<br>1 = ADC is en                                                                                                                                                                                                  | Enable bit                                                                                                                                                                  |                                     | ng current        |                   |                  |       |

Note 1: When the CHS<3:0> bits change to select the 1.2V or 0.6V Fixed Voltage Reference, the reference output voltage will have a transient. If the Comparator module uses this VP6 reference voltage, the comparator output may momentarily change state due to the transient.

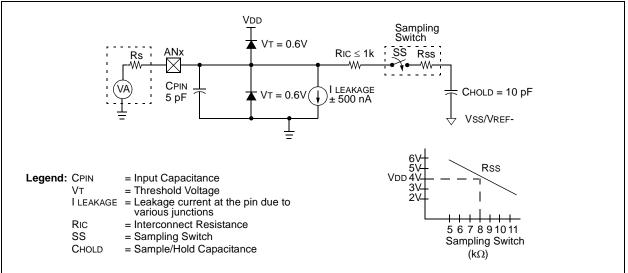

#### FIGURE 9-4: ANALOG INPUT MODEL

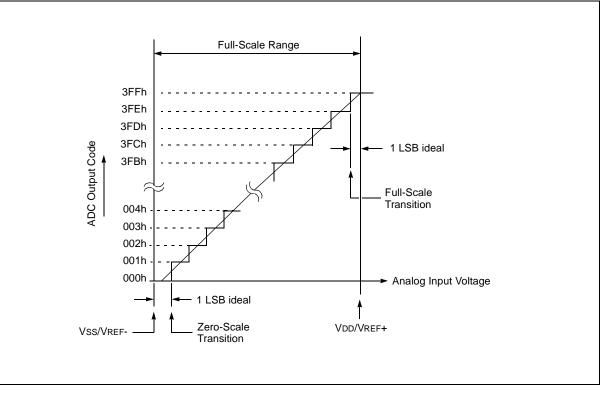

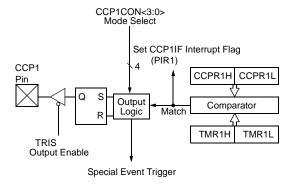

### 10.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 module may:

- Toggle the CCP1 output

- Set the CCP1 output

- Clear the CCP1 output

- Generate a Special Event Trigger

- Generate a Software Interrupt

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

#### FIGURE 10-2: COMPARE MODE OPERATION BLOCK DIAGRAM

Special Event Trigger will:

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 10.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|

|       | the CCP1 compare output latch to the        |  |  |  |  |  |

|       | default low level. This is not the PORT I/O |  |  |  |  |  |

|       | data latch.                                 |  |  |  |  |  |

#### 10.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 10.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 10.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP1 module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP1 module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

- Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMR1IF of the PIR1 register.

- 2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring.

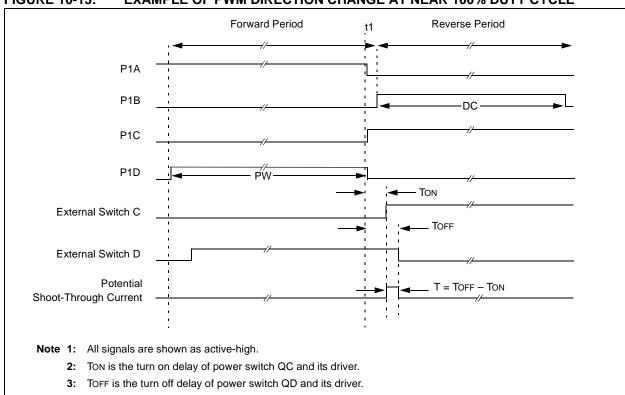

#### FIGURE 10-13: EXAMPLE OF PWM DIRECTION CHANGE AT NEAR 100% DUTY CYCLE

### 12.7 Power-Down Mode (Sleep)

The Power-Down mode is entered by executing a  $\ensuremath{\mathtt{SLEEP}}$  instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit in the STATUS register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are highimpedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSS for lowest current consumption. The contribution from on-chip pullups on PORTA should be considered.

The  $\overline{\text{MCLR}}$  pin must be at a logic high level.

| Note: | It should be noted that a Reset generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

#### 12.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from RA2/INT pin, PORTA change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The TO and PD bits in the STATUS register can be used to determine the cause of device Reset. The PD bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. Timer1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP Capture mode interrupt.

- 3. A/D conversion (when A/D clock source is RC).

- 4. Comparator output changes state.

- 5. Interrupt-on-change.

- 6. External Interrupt from INT pin.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up is regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

| Note: | If the global interrupts are disabled (GIE is<br>cleared) and any interrupt source has both<br>its interrupt enable bit and the correspond- |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------|

|       | ing interrupt flag bits set, the device will immediately wake-up from Sleep.                                                                |

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

#### 12.7.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs **before** the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will Immediately wake-up from Sleep. The SLEEP instruction is executed. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the PD bit. If the PD bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction. See Figure 12-9 for more details.

| Rotate Left f through Carry                                                                                                                                                                                          |  |  |  |  |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| [ <i>label</i> ] RLF f,d                                                                                                                                                                                             |  |  |  |  |  |  |  |  |

| $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                      |  |  |  |  |  |  |  |  |

| See description below                                                                                                                                                                                                |  |  |  |  |  |  |  |  |

| С                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| The contents of register 'f' are<br>rotated one bit to the left through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is stored<br>back in register 'f'. |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

| 1                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| RLF REG1,0                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |

| RLF REG1,0<br>Before Instruction                                                                                                                                                                                     |  |  |  |  |  |  |  |  |

| Before Instruction<br>REG1 = 1110 0110                                                                                                                                                                               |  |  |  |  |  |  |  |  |

| Before Instruction                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

| Before Instruction<br>$\begin{array}{rcl} \operatorname{REG1} &=& 1110 & 0110 \\ C &=& 0 \end{array}$ After Instruction                                                                                              |  |  |  |  |  |  |  |  |

| Before Instruction                                                                                                                                                                                                   |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                      |  |  |  |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                      |

| Operands:        | None                                                                                                                                                                                                                               |

| Operation:       | $\begin{array}{l} 00h \rightarrow WDT, \\ 0 \rightarrow WDT \text{ prescaler}, \\ 1 \rightarrow \overline{TO}, \\ 0 \rightarrow PD \end{array}$                                                                                    |

| Status Affected: | TO, PD                                                                                                                                                                                                                             |

| Description:     | The power-down Status bit, $\overline{PD}$ is<br>cleared. Time-out Status bit, $\overline{TO}$<br>is set. Watchdog Timer and its<br>prescaler are cleared.<br>The processor is put into Sleep<br>mode with the oscillator stopped. |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                                        |  |  |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RRF f,d                                                                                                                                                                                                            |  |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                                               |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                                   |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are<br>rotated one bit to the right through<br>the Carry flag. If 'd' is '0', the<br>result is placed in the W register.<br>If 'd' is '1', the result is placed<br>back in register 'f'.<br>register f |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                      |                          |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|--------------------------|--|--|--|--|--|

| Syntax:          | [label] SL                                                                                                                   | [ <i>label</i> ] SUBLW k |  |  |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                          |                          |  |  |  |  |  |

| Operation:       | $k \text{-} (W) \to (W)$                                                                                                     | V)                       |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |                          |  |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |                          |  |  |  |  |  |

|                  | Result                                                                                                                       | Condition                |  |  |  |  |  |

|                  | $\mathbf{C} = 0$                                                                                                             | M > k                    |  |  |  |  |  |

| <b>C</b> = 0 | W > k           |

|--------------|-----------------|

| <b>C</b> = 1 | $W \leq k$      |

| DC = 0       | W<3:0> > k<3:0> |

| DC = 1       | W<3:0> ≤ k<3:0> |

### 14.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 14.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

### 14.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

#### 15.2 DC Characteristics: PIC16F610/616-I (Industrial) PIC16F610/616-E (Extended)

| DC CHARACTERISTICS |                                        | Standard Operating Co<br>Operating temperature |          |       | -40°C ⊴ | s otherwise stated)<br>35°C for industrial<br>125°C for extended |                           |

|--------------------|----------------------------------------|------------------------------------------------|----------|-------|---------|------------------------------------------------------------------|---------------------------|

| Param              | Device Characteristics                 | Min                                            | Тур†     | Max   | Units   |                                                                  | Conditions                |

| No.                |                                        |                                                | <i>.</i> |       |         | VDD                                                              | Note                      |

| D010               | Supply Current (IDD) <sup>(1, 2)</sup> | —                                              | 13       | 25    | μA      | 2.0                                                              | Fosc = 32 kHz             |

|                    | PIC16F610/616                          | —                                              | 19       | 29    | μA      | 3.0                                                              | LP Oscillator mode        |

|                    |                                        | _                                              | 32       | 51    | μA      | 5.0                                                              |                           |

| D011*              |                                        | —                                              | 135      | 225   | μA      | 2.0                                                              | Fosc = 1 MHz              |

|                    |                                        | _                                              | 185      | 285   | μA      | 3.0                                                              | XT Oscillator mode        |

|                    |                                        | _                                              | 300      | 405   | μA      | 5.0                                                              | 7                         |

| D012               |                                        | —                                              | 240      | 360   | μA      | 2.0                                                              | Fosc = 4 MHz              |

|                    |                                        | _                                              | 360      | 505   | μA      | 3.0                                                              | XT Oscillator mode        |

|                    |                                        | —                                              | 0.66     | 1.0   | mA      | 5.0                                                              |                           |

| D013*              |                                        | —                                              | 75       | 110   | μA      | 2.0                                                              | Fosc = 1 MHz              |

|                    |                                        | _                                              | 155      | 255   | μA      | 3.0                                                              | EC Oscillator mode        |

|                    |                                        | —                                              | 345      | 530   | μA      | 5.0                                                              |                           |

| D014               |                                        | _                                              | 185      | 255   | μA      | 2.0                                                              | Fosc = 4 MHz              |

|                    |                                        | _                                              | 325      | 475   | μA      | 3.0                                                              | EC Oscillator mode        |

|                    |                                        | _                                              | 0.665    | 1.0   | mA      | 5.0                                                              |                           |

| D016*              |                                        |                                                | 245      | 340   | μΑ      | 2.0                                                              | Fosc = 4 MHz              |

|                    |                                        | _                                              | 360      | 485   | μA      | 3.0                                                              | INTOSC mode               |

|                    |                                        | —                                              | 0.620    | 0.845 | mA      | 5.0                                                              |                           |

| D017               |                                        |                                                | 395      | 550   | μΑ      | 2.0                                                              | Fosc = 8 MHz              |

|                    |                                        |                                                | 0.620    | 0.850 | mA      | 3.0                                                              | INTOSC mode               |

|                    |                                        |                                                | 1.2      | 1.6   | mA      | 5.0                                                              |                           |

| D018               |                                        |                                                | 175      | 235   | μΑ      | 2.0                                                              | Fosc = 4 MHz              |

|                    |                                        |                                                | 285      | 390   | μA      | 3.0                                                              | EXTRC mode <sup>(3)</sup> |

|                    |                                        |                                                | 530      | 750   | μA      | 5.0                                                              |                           |

| D019               |                                        |                                                | 2.2      | 3.1   | mA      | 4.5                                                              | Fosc = 20 MHz             |

|                    |                                        | —                                              | 2.8      | 3.35  | mA      | 5.0                                                              | HS Oscillator mode        |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

#### 15.6 DC Characteristics: PIC16HV610/616- I (Industrial)

| DC CHA                       | RACTERISTICS                                     | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial |            |     |       |            |                                                |  |

|------------------------------|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-------|------------|------------------------------------------------|--|

| Param Device Characteristics |                                                  |                                                                                                                                    | <b>.</b> . |     |       | Conditions |                                                |  |

| No.                          | Device Characteristics                           | Min                                                                                                                                | Тур†       | Мах | Units | VDD        | Note                                           |  |

| D020                         | Power-down Base<br>Current(IPD) <sup>(2,3)</sup> | -                                                                                                                                  | 135        | 200 | μA    | 2.0        | WDT, BOR, Comparators, VREF and T1OSC disabled |  |

|                              |                                                  |                                                                                                                                    | 210        | 280 | μΑ    | 3.0        |                                                |  |

|                              | PIC16HV610/616                                   |                                                                                                                                    | 260        | 350 | μA    | 4.5        |                                                |  |

| D021                         |                                                  |                                                                                                                                    | 135        | 200 | μA    | 2.0        | WDT Current <sup>(1)</sup>                     |  |

|                              |                                                  |                                                                                                                                    | 210        | 285 | μA    | 3.0        |                                                |  |

|                              |                                                  |                                                                                                                                    | 265        | 360 | μΑ    | 4.5        |                                                |  |

| D022                         |                                                  |                                                                                                                                    | 215        | 285 | μA    | 3.0        | BOR Current <sup>(1)</sup>                     |  |

|                              |                                                  |                                                                                                                                    | 265        | 360 | μΑ    | 4.5        |                                                |  |

| D023                         |                                                  |                                                                                                                                    | 240        | 340 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , both       |  |

|                              |                                                  |                                                                                                                                    | 320        | 420 | μΑ    | 3.0        | comparators enabled                            |  |

|                              |                                                  |                                                                                                                                    | 370        | 500 | μΑ    | 4.5        |                                                |  |

| D024                         |                                                  |                                                                                                                                    | 185        | 270 | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , single     |  |

|                              |                                                  |                                                                                                                                    | 265        | 350 | μΑ    | 3.0        | comparator enabled                             |  |

|                              |                                                  |                                                                                                                                    | 320        | 430 | μΑ    | 4.5        |                                                |  |

| D025                         |                                                  | _                                                                                                                                  | 165        | 235 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)      |  |

|                              |                                                  |                                                                                                                                    | 255        | 330 | μΑ    | 3.0        |                                                |  |

|                              |                                                  |                                                                                                                                    | 330        | 430 | μΑ    | 4.5        |                                                |  |

| D026*                        |                                                  |                                                                                                                                    | 175        | 245 | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)       |  |

|                              |                                                  |                                                                                                                                    | 275        | 350 | μΑ    | 3.0        |                                                |  |

|                              |                                                  |                                                                                                                                    | 355        | 450 | μΑ    | 4.5        |                                                |  |

| D027                         |                                                  | —                                                                                                                                  | 140        | 205 | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz      |  |

|                              |                                                  |                                                                                                                                    | 220        | 290 | μΑ    | 3.0        |                                                |  |

|                              |                                                  |                                                                                                                                    | 270        | 360 | μΑ    | 4.5        |                                                |  |

| D028                         |                                                  | —                                                                                                                                  | 210        | 280 | μΑ    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in  |  |

|                              |                                                  | _                                                                                                                                  | 260        | 350 | μΑ    | 4.5        | progress                                       |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral ∆ current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.