Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 11                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 128 × 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                   |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 14-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv616-e-sl |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|            | Program Memory   | Data Memory  |    | 10-bit A/D                  |   | Timers      |                  |               |  |

|------------|------------------|--------------|----|-----------------------------|---|-------------|------------------|---------------|--|

| Device     | Flash<br>(words) | SRAM (bytes) |    | Flash SRAM (bytes) //O (ch) |   | Comparators | 8/16-bit         | Voltage Range |  |

| PIC16F610  | 1024             | 64           | 11 | —                           | 2 | 1/1         | 2.0-5.5V         |               |  |

| PIC16HV610 | 1024             | 64           | 11 | —                           | 2 | 1/1         | 2.0-user defined |               |  |

| PIC16F616  | 2048             | 128          | 11 | 8                           | 2 | 2/1         | 2.0-5.5V         |               |  |

| PIC16HV616 | 2048             | 128          | 11 | 8                           | 2 | 2/1         | 2.0-user defined |               |  |

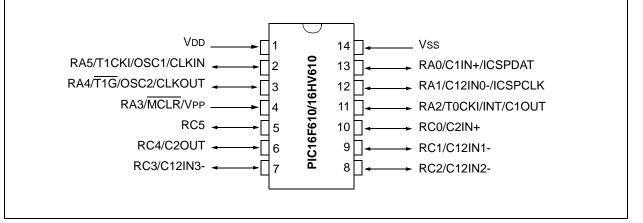

# PIC16F610/16HV610 14-Pin Diagram (PDIP, SOIC, TSSOP)

# TABLE 1: PIC16F610/16HV610 14-PIN SUMMARY

| I/O                | Pin | Comparators | Timer | Interrupts | Pull-ups         | Basic       |

|--------------------|-----|-------------|-------|------------|------------------|-------------|

| RA0                | 13  | C1IN+       | _     | IOC        | Y                | ICSPDAT     |

| RA1                | 12  | C12IN0-     | _     | IOC        | Y                | ICSPCLK     |

| RA2                | 11  | C1OUT       | T0CKI | INT/IOC    | Y                | —           |

| RA3 <sup>(1)</sup> | 4   | _           | _     | IOC        | Y <sup>(2)</sup> | MCLR/Vpp    |

| RA4                | 3   | —           | T1G   | IOC        | Y                | OSC2/CLKOUT |

| RA5                | 2   | —           | T1CKI | IOC        | Y                | OSC1/CLKIN  |

| RC0                | 10  | C2IN+       | _     | —          | —                | —           |

| RC1                | 9   | C12IN1-     |       | —          | _                | —           |

| RC2                | 8   | C12IN2-     | —     | —          | —                | —           |

| RC3                | 7   | C12IN3-     |       | _          | _                | —           |

| RC4                | 6   | C2OUT       | -     | —          | —                | —           |

| RC5                | 5   | _           |       | _          | _                | _           |

|                    | 1   | _           | _     | _          |                  | Vdd         |

|                    | 14  |             |       |            | —                | Vss         |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

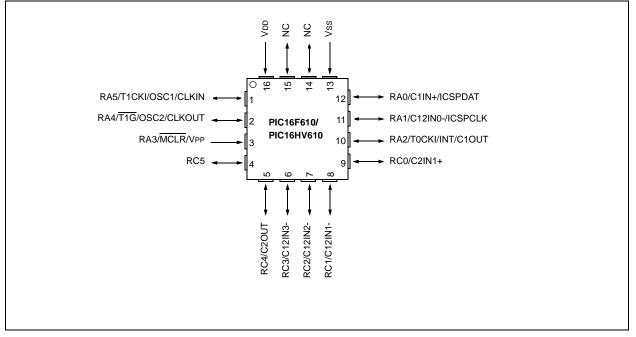

# PIC16F610/16HV610 16-Pin Diagram (QFN)

| TABLE 3: | PIC16F610/16HV610 | <b>16-PIN SUMMARY</b> |

|----------|-------------------|-----------------------|

|          |                   |                       |

| I/O                | Pin | Comparators | Timers | Interrupts | Pull-ups | Basic       |

|--------------------|-----|-------------|--------|------------|----------|-------------|

| RA0                | 12  | C1IN+       | _      | IOC        | Y        | ICSPDAT     |

| RA1                | 11  | C12IN0-     | _      | IOC        | Y        | ICSPCLK     |

| RA2                | 10  | C1OUT       | T0CKI  | INT/IOC    | Y        | —           |

| RA3 <sup>(1)</sup> | 3   | _           | _      | IOC        | Y(2)     | MCLR/Vpp    |

| RA4                | 2   | —           | T1G    | IOC        | Y        | OSC2/CLKOUT |

| RA5                | 1   | —           | T1CKI  | IOC        | Y        | OSC1/CLKIN  |

| RC0                | 9   | C2IN+       | _      | —          | —        | —           |

| RC1                | 8   | C12IN1-     |        | —          | —        | —           |

| RC2                | 7   | C12IN2-     | -      | —          | —        | —           |

| RC3                | 6   | C12IN3-     |        | —          | —        | —           |

| RC4                | 5   | C2OUT       | _      | —          | —        | —           |

| RC5                | 4   | _           | _      | _          |          | _           |

|                    | 16  |             | _      |            | —        | Vdd         |

| _                  | 13  |             | _      |            |          | Vss         |

Note 1: Input only.

**2:** Only when pin is configured for external  $\overline{MCLR}$ .

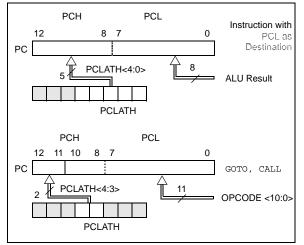

# 2.3 PCL and PCLATH

The Program Counter (PC) is 13 bits wide. The low byte comes from the PCL register, which is a readable and writable register. The high byte (PC<12:8>) is not directly readable or writable and comes from PCLATH. On any Reset, the PC is cleared. Figure 2-5 shows the two situations for the loading of the PC. The upper example in Figure 2-5 shows how the PC is loaded on a write to PCL (PCLATH<4:0>  $\rightarrow$  PCH). The lower example in Figure 2-5 shows how the PC is loaded during a CALL or GOTO instruction (PCLATH<4:3>  $\rightarrow$  PCH).

FIGURE 2-5: LOADING OF PC IN DIFFERENT SITUATIONS

# 2.3.1 MODIFYING PCL

Executing any instruction with the PCL register as the destination simultaneously causes the Program Counter PC<12:8> bits (PCH) to be replaced by the contents of the PCLATH register. This allows the entire contents of the program counter to be changed by writing the desired upper 5 bits to the PCLATH register. When the lower 8 bits are written to the PCL register, all 13 bits of the program counter will change to the values contained in the PCLATH register.

A computed GOTO is accomplished by adding an offset to the program counter (ADDWF PCL). Care should be exercised when jumping into a look-up table or program branch table (computed GOTO) by modifying the PCL register. Assuming that PCLATH is set to the table start address, if the table length is greater than 255 instructions or if the lower 8 bits of the memory address rolls over from 0xFF to 0x00 in the middle of the table, then PCLATH must be incremented for each address rollover that occurs between the table beginning and the target location within the table.

For more information refer to Application Note AN556, "Implementing a Table Read" (DS00556).

# 2.3.2 STACK

The PIC16F610/616/16HV610/616 Family has an 8-level x 13-bit wide hardware stack (see Figure 2-1). The stack space is not part of either program or data space and the Stack Pointer is not readable or writable. The PC is PUSHed onto the stack when a CALL instruction is executed or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation.

The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. The tenth push overwrites the second push (and so on).

- Note 1: There are no Status bits to indicate stack overflow or stack underflow conditions.

- 2: There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions or the vectoring to an interrupt address.

# 2.4 Indirect Addressing, INDF and FSR Registers

The INDF register is not a physical register. Addressing the INDF register will cause indirect addressing.

Indirect addressing is possible by using the INDF register. Any instruction using the INDF register actually accesses data pointed to by the File Select Register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although Status bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR and the IRP bit of the STATUS register, as shown in Figure 2-7.

A simple program to clear RAM location 40h-4Fh using indirect addressing is shown in Example 2-1.

|       | MOVLW | 0x40   | ;initialize pointer  |

|-------|-------|--------|----------------------|

|       | MOVWF | FSR    | ;to RAM              |

| NEXT  | CLRF  | INDF   | ;clear INDF register |

|       | INCF  | FSR, F | ;inc pointer         |

|       | BTFSS | FSR,4  | ;all done?           |

|       | GOTO  | NEXT   | ;no clear next       |

| CONTI | NUE   |        | ;yes continue        |

| 1     |       |        |                      |

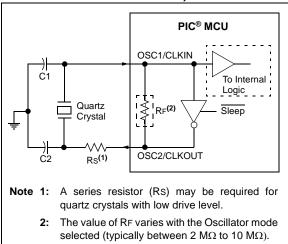

# 3.3.3 LP, XT, HS MODES

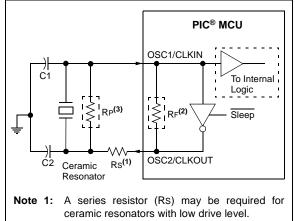

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

#### FIGURE 3-3: QUARTZ CRYSTAL OPERATION (LP, XT OR HS MODE)

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- **2:** Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

#### CERAMIC RESONATOR OPERATION (XT OR HS MODE)

- **2:** The value of RF varies with the Oscillator mode selected (typically between 2 MΩ to 10 MΩ).

- **3:** An additional parallel feedback resistor (RP) may be required for proper ceramic resonator operation.

other applications. For more information on Delta-Sigma A/D converters, see the Microchip web site (www.microchip.com).

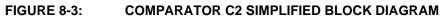

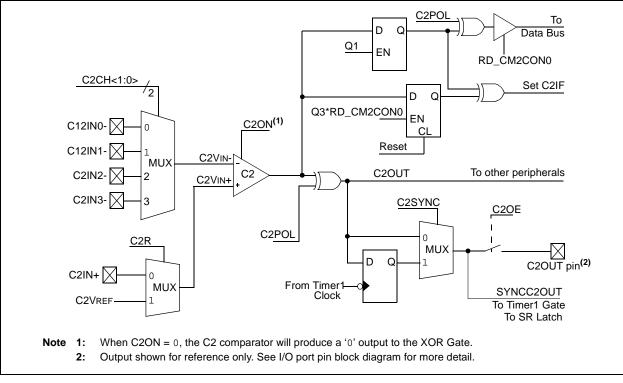

| Note: | TMR1GE bit of the T1CON register must                 |

|-------|-------------------------------------------------------|

|       | be set to use either $\overline{T1G}$ or C2OUT as the |

|       | Timer1 gate source. See the CM2CON1                   |

|       | register (Register 8-3) for more informa-             |

|       | tion on selecting the Timer1 gate source.             |

Timer1 gate can be inverted using the T1GINV bit of the T1CON register, whether it originates from the T1G pin or Comparator C2 output. This configures Timer1 to measure either the active-high or active-low time between events.

# 6.7 Timer1 Interrupt

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit of the PIR1 register is set. To enable the interrupt on rollover, you must set these bits:

- TMR1IE bit of the PIE1 register

- PEIE bit of the INTCON register

- GIE bit of the INTCON register

- T1SYNC bit of the T1CON register

- TMR1CS bit of the T1CON register

- T1OSCEN bit of the T1CON register (can be set)

The interrupt is cleared by clearing the TMR1IF bit in the Interrupt Service Routine.

Note: The TMR1H:TTMR1L register pair and the TMR1IF bit should be cleared before enabling interrupts.

# 6.8 Timer1 Operation During Sleep

Timer1 can only operate during Sleep when setup in Asynchronous Counter mode. In this mode, an external crystal or clock source can be used to increment the counter. To set up the timer to wake the device:

- TMR1ON bit of the T1CON register must be set

- TMR1IE bit of the PIE1 register must be set

- PEIE bit of the INTCON register must be set

The device will wake-up on an overflow and execute the next instruction. If the GIE bit of the INTCON register is set, the device will call the Interrupt Service Routine (0004h).

# 6.9 ECCP Capture/Compare Time Base (PIC16F616/16HV616 Only)

The ECCP module uses the TMR1H:TMR1L register pair as the time base when operating in Capture or Compare mode.

In Capture mode, the value in the TMR1H:TMR1L register pair is copied into the CCPR1H:CCPR1L register pair on a configured event.

In Compare mode, an event is triggered when the value CCPR1H:CCPR1L register pair matches the value in the TMR1H:TMR1L register pair. This event can be a Special Event Trigger.

For more information, see Section 10.0 "Enhanced Capture/Compare/PWM (With Auto-Shutdown and Dead Band) Module (PIC16F616/16HV616 Only)".

# 6.10 ECCP Special Event Trigger (PIC16F616/16HV616 Only)

When the ECCP is configured to trigger a special event, the trigger will clear the TMR1H:TMR1L register pair. This special event does not cause a Timer1 interrupt. The ECCP module may still be configured to generate a ECCP interrupt.

In this mode of operation, the CCPR1H:CCPR1L register pair effectively becomes the period register for Timer1.

Timer1 should be synchronized to the FOSC to utilize the Special Event Trigger. Asynchronous operation of Timer1 can cause a Special Event Trigger to be missed.

In the event that a write to TMR1H or TMR1L coincides with a Special Event Trigger from the ECCP, the write will take precedence.

For more information, see **Section 10.2.4** "**Special Event Trigger**".

# 6.11 Comparator Synchronization

The same clock used to increment Timer1 can also be used to synchronize the comparator output. This feature is enabled in the Comparator module.

When using the comparator for Timer1 gate, the comparator output should be synchronized to Timer1. This ensures Timer1 does not miss an increment if the comparator changes.

For more information, see Section 8.8.2 "Synchronizing Comparator C2 Output to Timer1".

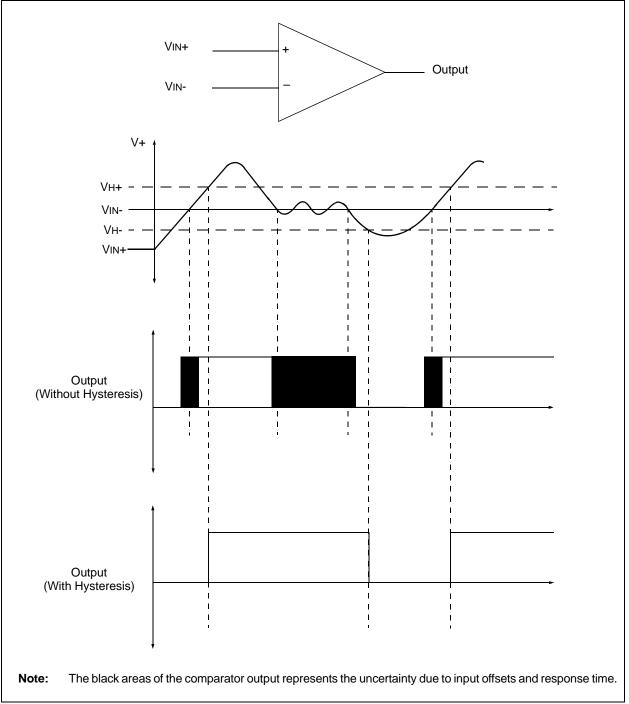

### 8.9 Comparator Hysteresis

Each comparator has built-in hysteresis that is user enabled by setting the C1HYS or C2HYS bits of the CM2CON1 register. The hysteresis feature can help filter noise and reduce multiple comparator output transitions when the output is changing state. Figure 8-9 shows the relationship between the analog input levels and digital output of a comparator with and without hysteresis. The output of the comparator changes from a low state to a high state only when the analog voltage at VIN+ rises above the upper hysteresis threshold (VH+). The output of the comparator changes from a high state to a low state only when the analog voltage at VIN+ falls below the lower hysteresis threshold (VH-).

FIGURE 8-7: COMPARATOR HYSTERESIS

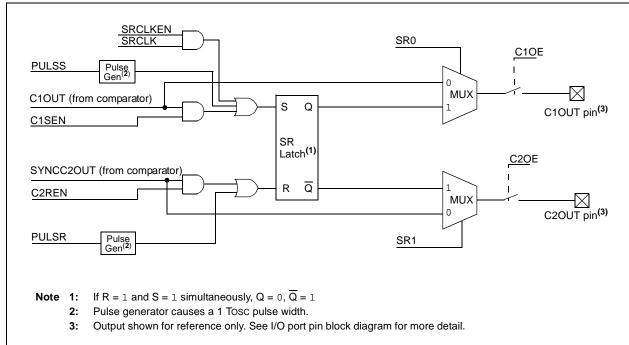

### 8.10 Comparator SR Latch

The SR latch module provides additional control of the comparator outputs. The module consists of a single SR latch and output multiplexers. The SR latch can be set, reset or toggled by the comparator outputs. The SR latch may also be set or reset, independent of comparator output, by control bits in the SRCON0 control register. The SR latch output multiplexers select whether the latch outputs or the comparator outputs are directed to the I/O port logic for eventual output to a pin.

The SR latch also has a variable clock, which is connected to the set input of the latch. The SRCLKEN bit of SRCON0 enables the SR latch set clock. The clock will periodically pulse the set input of the latch. Control over the frequency of the SR latch set clock is provided by the SRCS<1:0> bits of SRCON1 register.

#### 8.10.1 LATCH OPERATION

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. Each latch input is connected to a comparator output and a software controlled pulse generator. The latch can be set by C1OUT or the PULSS bit of the SRCON0 register. The latch can be reset by C2OUT or the PULSR bit of the SRCON0 register. The latch is reset-dominant, therefore, if both Set and Reset

inputs are high the latch will go to the Reset state. Both the PULSS and PULSR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

### 8.10.2 LATCH OUTPUT

The SR<1:0> bits of the SRCON0 register control the latch output multiplexers and determine four possible output configurations. In these four configurations, the CxOUT I/O port logic is connected to:

- C1OUT and C2OUT

- C1OUT and SR latch Q

- C2OUT and SR latch Q

- SR latch Q and Q

After any Reset, the default output configuration is the unlatched C1OUT and C2OUT mode. This maintains compatibility with devices that do not have the SR latch feature.

The applicable TRIS bits of the corresponding ports must be cleared to enable the port pin output drivers. Additionally, the CxOE comparator output enable bits of the CMxCON0 registers must be set in order to make the comparator or latch outputs available on the output pins. The latch configuration enable states are completely independent of the enable states for the comparators.

#### FIGURE 8-8: SR LATCH SIMPLIFIED BLOCK DIAGRAM

| R/W-0                                                                | R/W-0              | R/W-0                        | R/W-0           | R/W-0            | R/W-0             | R/W-0                 | R/W-0 |  |  |

|----------------------------------------------------------------------|--------------------|------------------------------|-----------------|------------------|-------------------|-----------------------|-------|--|--|

| C1VREN                                                               | C2VREN             | VRR                          | FVREN           | VR3              | VR2               | VR1                   | VR0   |  |  |

| bit 7                                                                |                    |                              |                 |                  |                   |                       | bit 0 |  |  |

|                                                                      |                    |                              |                 |                  |                   |                       |       |  |  |

| Legend:                                                              |                    |                              |                 |                  |                   |                       |       |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                    |                              |                 |                  |                   |                       |       |  |  |

| -n = Value at F                                                      | POR                | '1' = Bit is set             |                 | '0' = Bit is cle | ared              | x = Bit is unkr       | nown  |  |  |

|                                                                      |                    |                              |                 |                  |                   |                       |       |  |  |

| bit 7                                                                | C1VREN: Co         | mparator 1 Vol               | tage Referenc   | e Enable bit     |                   |                       |       |  |  |

|                                                                      | 1 = CVREF cir      | cuit powered c               | on and routed t | O C1VREF inpu    | it of Comparate   | or C1                 |       |  |  |

|                                                                      | 0 = 0.6 Volt c     | onstant referer              | nce routed to C | 1VREF input of   | f Comparator C    | ;1                    |       |  |  |

| bit 6                                                                | C2VREN: Co         | mparator 2 Vol               | tage Referenc   | e Enable bit     |                   |                       |       |  |  |

|                                                                      |                    | •                            |                 |                  | it of Comparate   |                       |       |  |  |

|                                                                      | 0 = 0.6 Volt c     | onstant referer              | nce routed to C | 2VREF input of   | f Comparator C    | 2                     |       |  |  |

| bit 5                                                                | VRR: CVREF         | Range Selection              | on bit          |                  |                   |                       |       |  |  |

|                                                                      | 1 = Low range      |                              |                 |                  |                   |                       |       |  |  |

|                                                                      | 0 = High rang      | е                            |                 |                  |                   |                       |       |  |  |

| bit 4                                                                | FVREN: Fixe        | d Voltage Refe               | rence (0.6V) E  | nable bit        |                   |                       |       |  |  |

|                                                                      | 1 = Enabled        |                              |                 |                  |                   |                       |       |  |  |

|                                                                      | 0 = Disabled       |                              |                 |                  |                   |                       |       |  |  |

| bit 3-0                                                              |                    | •                            | •               |                  | Selection bits (C | $\leq$ VR<3:0> $\leq$ | 15)   |  |  |

|                                                                      |                    | $\underline{1}$ : CVREF = (V |                 |                  |                   |                       |       |  |  |

|                                                                      | <u>VVhen VRR =</u> | $\underline{0}$ : CVREF = V  | DD/4 + (VR<3:0  | )>/32) * VDD     |                   |                       |       |  |  |

|                                                                      |                    |                              |                 |                  |                   |                       |       |  |  |

# REGISTER 8-6: VRCON: VOLTAGE REFERENCE CONTROL REGISTER

# 9.3 A/D Acquisition Requirements

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 9-4. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 9-4. The maximum recommended impedance for analog sources is 10 k $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased. After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 9-1 may be used. This equation assumes that 1/2 LSb error is used (1024 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

#### EQUATION 9-1: ACQUISITION TIME EXAMPLE

Assumptions: Temperature =  $50^{\circ}C$  and external impedance of  $10k\Omega 5.0V VDD$  TACQ = Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient = TAMP + TC + TCOFF $= 5\mu s + TC + [(Temperature - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$

The value for TC can be approximated with the following equations:

$$V_{APPLIED}\left(1 - \frac{1}{2047}\right) = V_{CHOLD} \qquad ;[1] V_{CHOLD} charged to within 1/2 lsb$$

$$V_{APPLIED}\left(1 - e^{\frac{-T_{C}}{RC}}\right) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED} \qquad (1 - e^{\frac{-T_{C}}{RC}}) = V_{CHOLD} \qquad ;[2] V_{CHOLD} charge response to V_{APPLIED}$$

$$V_{APPLIED}\left(1 - e^{\frac{-1}{RC}}\right) = V_{APPLIED}\left(1 - \frac{1}{2047}\right) \quad \text{; combining [1] and [2]}$$

Solving for TC:

$$TC = -CHOLD(RIC + RSS + RS) \ln(1/2047)$$

=  $-10pF(1k\Omega + 7k\Omega + 10k\Omega) \ln(0.0004885)$

=  $1.37\mu s$

Therefore:

$$TACQ = 5\mu s + 1.37\mu s + [(50^{\circ}C - 25^{\circ}C)(0.05\mu s/^{\circ}C)]$$

= 7.67\mu s

**Note 1:** The reference voltage (VREF) has no effect on the equation, since it cancels itself out.

2: The charge holding capacitor (CHOLD) is not discharged after each conversion.

**3:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

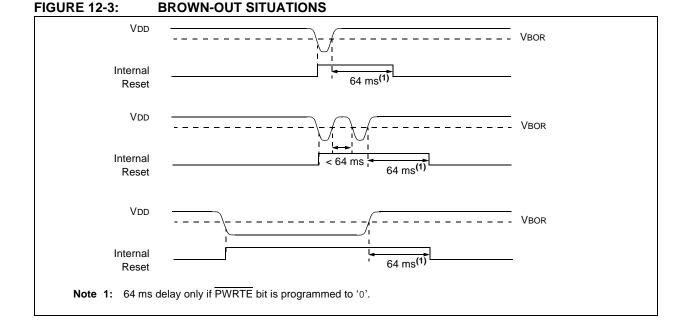

### 12.3.4 BROWN-OUT RESET (BOR)

The BOREN0 and BOREN1 bits in the Configuration Word register select one of three BOR modes. Selecting BOREN<1:0> = 10, the BOR is automatically disabled in Sleep to conserve power and enabled on wake-up. See Register 12-1 for the Configuration Word definition.

A brown-out occurs when VDD falls below VBOR for greater than parameter TBOR (see **Section 15.0** "**Electrical Specifications**"). The brown-out condition will reset the device. This will occur regardless of VDD slew rate. A Brown-out Reset may not occur if VDD falls below VBOR for less than parameter TBOR.

On any Reset (Power-on, Brown-out Reset, Watchdog timer, etc.), the chip will remain in Reset until VDD rises above VBOR (see Figure 12-3). If enabled, the Power-up Timer will be invoked by the Reset and keep the chip in Reset an additional 64 ms.

Note: The Power-up Timer is enabled by the <u>PWRTE</u> bit in the Configuration Word register.

If VDD drops below VBOR while the Power-up Timer is running, the chip will go back into a Brown-out Reset and the Power-up Timer will be re-initialized. Once VDD rises above VBOR, the Power-up Timer will execute a 64 ms Reset.

#### © 2009 Microchip Technology Inc.

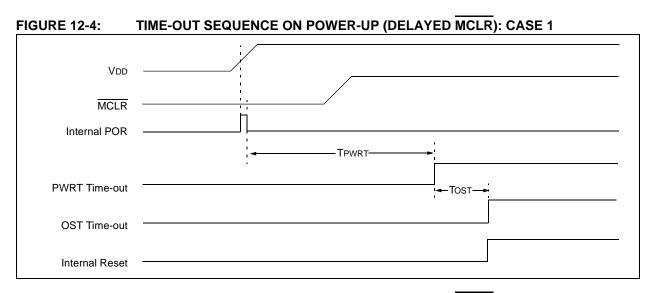

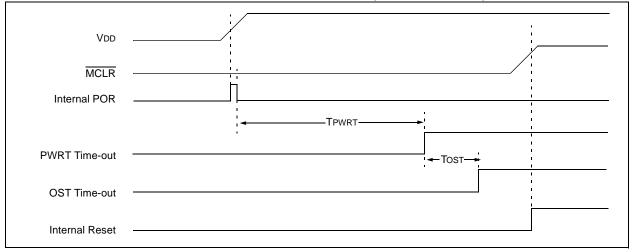

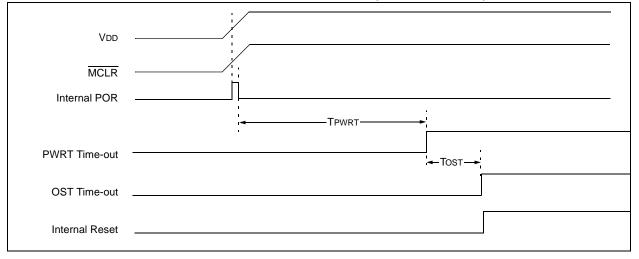

#### FIGURE 12-5: TIME-OUT SEQUENCE ON POWER-UP (DELAYED MCLR): CASE 2

#### FIGURE 12-6: TIME-OUT SEQUENCE ON POWER-UP (MCLR WITH VDD)

# 12.6 Watchdog Timer (WDT)

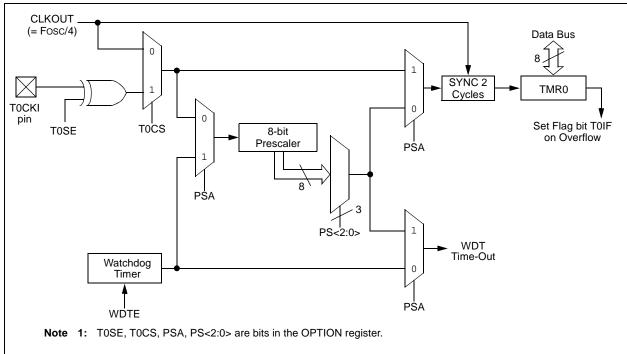

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin and INTOSC. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT Time-out generates a device Reset. If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 12.1 "Configuration Bits").

### 12.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see Table 15-4, Parameter 31). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

#### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT Time-out occurs.

#### FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

#### TABLE 12-7: WDT STATUS

| Conditions                                   | WDT                          |  |

|----------------------------------------------|------------------------------|--|

| WDTE = 0                                     |                              |  |

| CLRWDT Command                               | Cleared                      |  |

| Exit Sleep + System Clock = EXTRC, INTRC, EC |                              |  |

| Exit Sleep + System Clock = XT, HS, LP       | Cleared until the end of OST |  |

| Mnemonic, |      | <b>_</b>                     | Cycles         |       | 14-Bit | Opcode      | Status |          |         |

|-----------|------|------------------------------|----------------|-------|--------|-------------|--------|----------|---------|

| Oper      | ,    | Description                  |                | MSb   |        |             | LSb    | Affected | Notes   |

| -         |      | BYTE-ORIENTED FILE REGI      | STER OPE       | RATIO | NS     |             |        |          |         |

| ADDWF     | f, d | Add W and f                  | 1              | 00    | 0111   | dfff        | ffff   | C, DC, Z | 1, 2    |

| ANDWF     | f, d | AND W with f                 | 1              | 00    | 0101   | dfff        | ffff   | Z        | 1, 2    |

| CLRF      | f    | Clear f                      | 1              | 00    | 0001   | lfff        | ffff   | Z        | 2       |

| CLRW      | -    | Clear W                      | 1              | 00    | 0001   | 0xxx        | xxxx   | Z        |         |

| COMF      | f, d | Complement f                 | 1              | 00    | 1001   | dfff        | ffff   | Z        | 1, 2    |

| DECF      | f, d | Decrement f                  | 1              | 00    | 0011   | dfff        | ffff   | Z        | 1, 2    |

| DECFSZ    | f, d | Decrement f, Skip if 0       | 1 <b>(2)</b>   | 00    | 1011   | dfff        | ffff   |          | 1, 2, 3 |

| INCF      | f, d | Increment f                  | 1              | 00    | 1010   | dfff        | ffff   | Z        | 1, 2    |

| INCFSZ    | f, d | Increment f, Skip if 0       | 1 <b>(2)</b>   | 00    | 1111   | dfff        | ffff   |          | 1, 2, 3 |

| IORWF     | f, d | Inclusive OR W with f        | 1              | 00    | 0100   | dfff        | ffff   | Z        | 1, 2    |

| MOVF      | f, d | Move f                       | 1              | 00    | 1000   | dfff        | ffff   | Z        | 1, 2    |

| MOVWF     | f    | Move W to f                  | 1              | 00    | 0000   | lfff        | ffff   |          |         |

| NOP       | _    | No Operation                 | 1              | 00    | 0000   | 0xx0        | 0000   |          |         |

| RLF       | f, d | Rotate Left f through Carry  | 1              | 00    | 1101   | dfff        | ffff   | С        | 1, 2    |

| RRF       | f, d | Rotate Right f through Carry | 1              | 00    | 1100   | dfff        | ffff   | C        | 1, 2    |

| SUBWF     | f, d | Subtract W from f            | 1              | 00    | 0010   |             | ffff   | C, DC, Z | 1, 2    |

| SWAPF     | f, d | Swap nibbles in f            | 1              | 00    | 1110   |             | ffff   | -,, -    | 1, 2    |

| XORWF     | f, d | Exclusive OR W with f        | 1              | 00    | 0110   |             | ffff   | Z        | 1, 2    |

|           | .,   | BIT-ORIENTED FILE REGIS      |                |       |        |             |        |          | -, -    |

| BCF       | f. b | Bit Clear f                  | 1              | 01    |        | bfff        | ffff   |          | 1, 2    |

| BSF       | f, b | Bit Set f                    | 1              | 01    |        | bfff        |        |          | 1, 2    |

| BTFSC     | f, b | Bit Test f, Skip if Clear    |                | 01    |        | bfff        |        |          | 3       |

| BTFSS     | f, b | Bit Test f, Skip if Set      | 1 (2)<br>1 (2) | 01    |        |             | ffff   |          | 3       |

| ыгээ      | Ι, D |                              |                | -     | 11bb   | bfff        | IIII   |          | 3       |

|           |      | LITERAL AND CONTRO           | 1              | IONS  |        |             |        | r        | r       |

| ADDLW     | k    | Add literal and W            | 1              | 11    |        | kkkk        |        | C, DC, Z |         |

| ANDLW     | k    | AND literal with W           | 1              | 11    | 1001   | kkkk        | kkkk   | Z        |         |

| CALL      | k    | Call Subroutine              | 2              | 10    | 0kkk   | kkkk        | kkkk   |          |         |

| CLRWDT    | -    | Clear Watchdog Timer         | 1              | 00    | 0000   | 0110        | 0100   | TO, PD   |         |

| GOTO      | k    | Go to address                | 2              | 10    | 1kkk   | kkkk        | kkkk   |          |         |

| IORLW     | k    | Inclusive OR literal with W  | 1              | 11    | 1000   | kkkk        | kkkk   | Z        |         |

| MOVLW     | k    | Move literal to W            | 1              | 11    | 00xx   | kkkk        | kkkk   |          |         |

| RETFIE    | -    | Return from interrupt        | 2              | 00    | 0000   | 0000        | 1001   |          |         |

| RETLW     | k    | Return with literal in W     | 2              | 11    | 01xx   | kkkk        | kkkk   |          |         |

| RETURN    | -    | Return from Subroutine       | 2              | 00    | 0000   | 0000        | 1000   |          |         |

| SLEEP     | -    | Go into Standby mode         | 1              | 00    | 0000   | 0110        | 0011   | TO, PD   |         |

| SUBLW     | k    | Subtract W from literal      | 1              | 11    | 110x   | kkkk        | kkkk   | C, DC, Z |         |

| XORLW     | k    | Exclusive OR literal with W  | 1              | 11    | 1010   | le le le le | kkkk   | Z        |         |

### TABLE 13-2: PIC16F610/616/16HV610/616 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF PORTA, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

### 15.2 DC Characteristics: PIC16F610/616-I (Industrial) PIC16F610/616-E (Extended)

| DC CHARACTERISTICS           |                                        |     | ard Oper<br>ing temp |       | -40°C ⊴ | s otherwise stated)<br>35°C for industrial<br>125°C for extended |                           |  |

|------------------------------|----------------------------------------|-----|----------------------|-------|---------|------------------------------------------------------------------|---------------------------|--|

| Param Device Characteristics |                                        | Min | Тур†                 | Max   | Units   | Conditions                                                       |                           |  |

| No.                          |                                        | VDI |                      | VDD   | Note    |                                                                  |                           |  |

| D010                         | Supply Current (IDD) <sup>(1, 2)</sup> | —   | 13                   | 25    | μΑ      | 2.0                                                              | Fosc = 32 kHz             |  |

|                              | PIC16F610/616                          | —   | 19                   | 29    | μA      | 3.0                                                              | LP Oscillator mode        |  |

|                              |                                        | _   | 32                   | 51    | μA      | 5.0                                                              |                           |  |

| D011*                        |                                        | —   | 135                  | 225   | μA      | 2.0                                                              | Fosc = 1 MHz              |  |

|                              |                                        | _   | 185                  | 285   | μA      | 3.0                                                              | XT Oscillator mode        |  |

|                              |                                        | _   | 300                  | 405   | μA      | 5.0                                                              | 7                         |  |

| D012                         |                                        | —   | 240                  | 360   | μA      | 2.0                                                              | Fosc = 4 MHz              |  |

|                              |                                        | _   | 360                  | 505   | μA      | 3.0                                                              | XT Oscillator mode        |  |

|                              |                                        | —   | 0.66                 | 1.0   | mA      | 5.0                                                              |                           |  |

| D013*                        |                                        | —   | 75                   | 110   | μA      | 2.0                                                              | Fosc = 1 MHz              |  |

|                              |                                        | _   | 155                  | 255   | μA      | 3.0                                                              | EC Oscillator mode        |  |

|                              |                                        | —   | 345                  | 530   | μA      | 5.0                                                              |                           |  |

| D014                         |                                        | _   | 185                  | 255   | μA      | 2.0                                                              | Fosc = 4 MHz              |  |

|                              |                                        | _   | 325                  | 475   | μA      | 3.0                                                              | EC Oscillator mode        |  |

|                              |                                        | _   | 0.665                | 1.0   | mA      | 5.0                                                              |                           |  |

| D016*                        |                                        |     | 245                  | 340   | μΑ      | 2.0                                                              | Fosc = 4 MHz              |  |

|                              |                                        | _   | 360                  | 485   | μA      | 3.0                                                              | INTOSC mode               |  |

|                              |                                        | —   | 0.620                | 0.845 | mA      | 5.0                                                              |                           |  |

| D017                         |                                        |     | 395                  | 550   | μΑ      | 2.0                                                              | Fosc = 8 MHz              |  |

|                              |                                        |     | 0.620                | 0.850 | mA      | 3.0                                                              | INTOSC mode               |  |

|                              |                                        |     | 1.2                  | 1.6   | mA      | 5.0                                                              |                           |  |

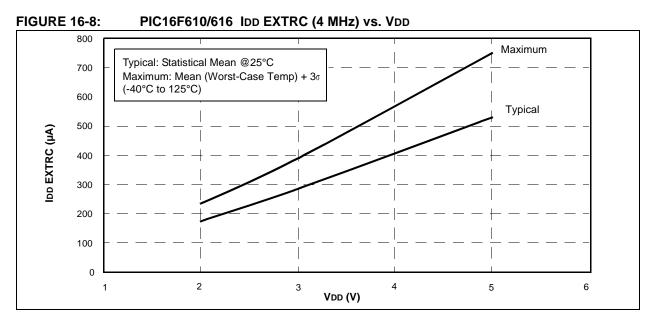

| D018                         |                                        |     | 175                  | 235   | μΑ      | 2.0                                                              | Fosc = 4 MHz              |  |

|                              |                                        |     | 285                  | 390   | μA      | 3.0                                                              | EXTRC mode <sup>(3)</sup> |  |

|                              |                                        |     | 530                  | 750   | μA      | 5.0                                                              |                           |  |

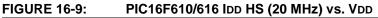

| D019                         |                                        |     | 2.2                  | 3.1   | mA      | 4.5                                                              | Fosc = 20 MHz             |  |

|                              |                                        | —   | 2.8                  | 3.35  | mA      | 5.0                                                              | HS Oscillator mode        |  |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

3: For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

### 15.3 DC Characteristics: PIC16HV610/616-I (Industrial) PIC16HV610/616-E (Extended)

| DC CHARACTERISTICS |                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |     |       |            |                                     |

|--------------------|----------------------------------------|------------------------------------------------------|-------|-----|-------|------------|-------------------------------------|

| Param              | Device Characteristics                 | Min                                                  | Тур†  | Мах | Units | Conditions |                                     |

| No.                |                                        |                                                      |       |     |       | Vdd        | Note                                |

| D010               | Supply Current (IDD) <sup>(1, 2)</sup> | _                                                    | 160   | 230 | μΑ    | 2.0        | Fosc = 32 kHz                       |

|                    | PIC16HV610/616                         | _                                                    | 240   | 310 | μΑ    | 3.0        | LP Oscillator mode                  |

|                    |                                        | _                                                    | 280   | 400 | μΑ    | 4.5        |                                     |

| D011*              |                                        | _                                                    | 270   | 380 | μΑ    | 2.0        | Fosc = 1 MHz                        |

|                    |                                        | _                                                    | 400   | 560 | μA    | 3.0        | XT Oscillator mode                  |

|                    |                                        | —                                                    | 520   | 780 | μΑ    | 4.5        | 7                                   |

| D012               |                                        | _                                                    | 380   | 540 | μΑ    | 2.0        | Fosc = 4 MHz                        |

|                    |                                        | _                                                    | 575   | 810 | μΑ    | 3.0        | XT Oscillator mode                  |

|                    |                                        | _                                                    | 0.875 | 1.3 | mA    | 4.5        |                                     |

| D013*              |                                        | —                                                    | 215   | 310 | μΑ    | 2.0        | Fosc = 1 MHz                        |

|                    |                                        | _                                                    | 375   | 565 | μΑ    | 3.0        | EC Oscillator mode                  |

|                    |                                        | —                                                    | 570   | 870 | μΑ    | 4.5        |                                     |

| D014               |                                        | —                                                    | 330   | 475 | μΑ    | 2.0        | Fosc = 4 MHz                        |

|                    |                                        | —                                                    | 550   | 800 | μΑ    | 3.0        | EC Oscillator mode                  |

|                    |                                        | —                                                    | 0.85  | 1.2 | mA    | 4.5        |                                     |

| D016*              |                                        | —                                                    | 310   | 435 | μΑ    | 2.0        | Fosc = 4 MHz                        |

|                    |                                        |                                                      | 500   | 700 | μA    | 3.0        | INTOSC mode                         |

|                    |                                        |                                                      | 0.74  | 1.1 | mA    | 4.5        |                                     |

| D017               |                                        | _                                                    | 460   | 650 | μΑ    | 2.0        | Fosc = 8 MHz                        |

|                    |                                        | _                                                    | 0.75  | 1.1 | mA    | 3.0        | INTOSC mode                         |

|                    |                                        | _                                                    | 1.2   | 1.6 | mA    | 4.5        |                                     |

| D018               |                                        | _                                                    | 320   | 465 | μΑ    | 2.0        | FOSC = 4 MHz                        |

|                    |                                        | _                                                    | 510   | 750 | μΑ    | 3.0        | EXTRC mode <sup>(3)</sup>           |

|                    |                                        | -                                                    | 0.770 | 1.0 | mA    | 4.5        |                                     |

| D019               |                                        | —                                                    | 2.5   | 3.4 | mA    | 4.5        | Fosc = 20 MHz<br>HS Oscillator mode |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 4.5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in k $\Omega$ .

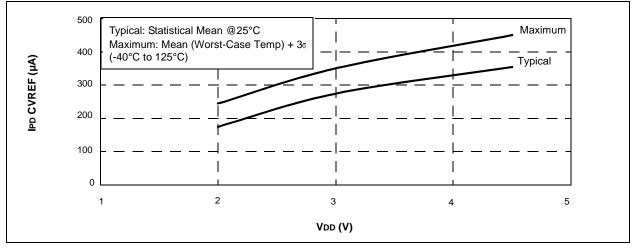

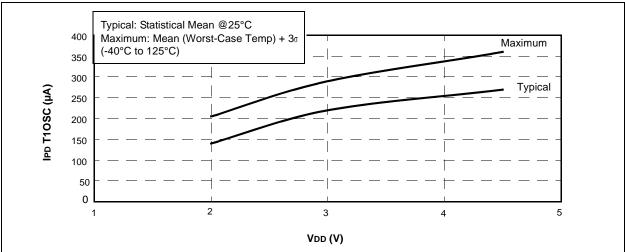

# FIGURE 16-32: PIC16HV610/616 IPD CVREF (LOW RANGE) vs. VDD

| Res      | et Values (special registers)   | 117 |

|----------|---------------------------------|-----|

| Spe      | cial Function Registers         | 14  |

| Spe      | cial Register Summary           | 17  |

| SRO      | CON0 (SR Latch Control 0)       | 69  |

| SRO      | CON1 (SR Latch Control 1)       | 69  |

| STA      | TUS                             | 18  |

| T1C      | ON                              | 52  |

| T2C      | ON                              |     |

| TRI      | SA (Tri-State PORTA)            |     |

| TRI      | SC (Tri-State PORTC)            |     |

| VRC      | CON (Voltage Reference Control) | 72  |

| WP       | UA (Weak Pull Up PORTA)         |     |

| Reset    |                                 |     |

| Revision | History                         |     |

# S

| Shoot-through Current          | 104 |

|--------------------------------|-----|

| Sleep                          |     |

| Power-Down Mode                | 124 |

| Wake-up                        | 124 |

| Wake-up using Interrupts       | 124 |

| Software Simulator (MPLAB SIM) | 141 |

| Special Event Trigger          | 76  |

| Special Function Registers     | 14  |

| SRCON0 Register                | 69  |

| SRCON1 Register                | 69  |

| STATUS Register                |     |

# т

| T1CON Register              | . 52 |

|-----------------------------|------|

| T2CON Register              | . 56 |

| Thermal Considerations      | 155  |

| Time-out Sequence           | 114  |

| Timer0                      |      |

| Associated Registers        | . 47 |

| External Clock              | . 46 |

| Interrupt                   | . 47 |

| Operation                   | . 45 |

| Specifications              | 162  |

| ТОСКІ                       | . 46 |

| Timer1                      | . 49 |

| Associated registers        | . 54 |

| Asynchronous Counter Mode   | . 50 |

| Reading and Writing         | . 50 |

| Interrupt                   | . 51 |

| Modes of Operation          | . 49 |

| Operation                   | . 49 |

| Operation During Sleep      |      |

| Oscillator                  | . 50 |

| Prescaler                   | . 50 |

| Specifications              | 162  |

| Timer1 Gate                 |      |

| Inverting Gate              | . 51 |

| Selecting Source50,         | 65   |

| SR Latch                    |      |

| Synchronizing COUT w/Timer1 |      |

| TMR1H Register              | . 49 |

| TMR1L Register              | . 49 |

| Timer2                      |      |

| Associated registers        | . 56 |

| Timers                      |      |

| Timer1                      |      |

| T1CON                       | . 52 |

| Timer2                      |      |

| T2CON                       | . 56 |

| Timing Diagrams             |      |

| A/D Conversion                               | 167 |

|----------------------------------------------|-----|

| A/D Conversion (Sleep Mode)                  | 167 |

| Brown-out Reset (BOR)                        | 160 |

| Brown-out Reset Situations                   | 113 |

| CLKOUT and I/O                               | 159 |

| Clock Timing                                 | 157 |

| Comparator Output                            | 57  |

| Enhanced Capture/Compare/PWM (ECCP)          | 163 |

| Full-Bridge PWM Output                       | 98  |

| Half-Bridge PWM Output 96,                   | 104 |

| INT Pin Interrupt                            | 120 |

| PWM Auto-shutdown                            |     |

| Auto-restart Enabled                         | 103 |

| Firmware Restart                             | 103 |

| PWM Direction Change                         | 99  |

| PWM Direction Change at Near 100% Duty Cycle | 100 |

| PWM Output (Active-High)                     |     |

| PWM Output (Active-Low)                      | 95  |

| Reset, WDT, OST and Power-up Timer           | 160 |

| Time-out Sequence                            |     |

| Case 1                                       | 115 |

| Case 2                                       | 115 |

| Case 3                                       | 115 |

| Timer0 and Timer1 External Clock             |     |

| Timer1 Incrementing Edge                     | 52  |

| Wake-up from Interrupt                       | 125 |

| Timing Parameter Symbology                   | 156 |

| TRISA                                        | 33  |

| TRISA Register                               |     |

| TRISC                                        | 42  |

| TRISC Register                               | 42  |

|                                              |     |

# ۷

| Voltage Reference (VR)                         |       |

|------------------------------------------------|-------|

| Specifications                                 | 164   |

| Voltage Reference. See Comparator Voltage Refe | rence |

| (CVREF)                                        |       |

| Voltage References                             |       |

| Associated registers                           | 67    |

| VP6 Stabilization                              | 71    |

| VREF. SEE ADC Reference Voltage                |       |

#### W

| Wake-up Using Interrupts |     |

|--------------------------|-----|

| Watchdog Timer (WDT)     | 122 |

| Associated registers     |     |

| Specifications           | 161 |

| WPUA Register            | 35  |

| WWW Address              |     |

| WWW, On-Line Support     |     |