## Microchip Technology - PIC16HV616-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                         |

| Number of I/O              | 11                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | -                                                                        |

| RAM Size                   | 128 × 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                  |

| Data Converters            | A/D 8x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Through Hole                                                             |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 14-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv616-i-p |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### FIGURE 2-3: DATA MEMORY MAP OF THE PIC16F610/16HV610

|                                                                                              | File<br>Address |                               | File<br>Address |  |

|----------------------------------------------------------------------------------------------|-----------------|-------------------------------|-----------------|--|

| Indirect Addr.(1)                                                                            | 00h             | Indirect Addr. <sup>(1)</sup> | 80h             |  |

| TMR0                                                                                         | 01h             | OPTION REG                    | 81h             |  |

| PCL                                                                                          | 02h             | PCL                           | 82h             |  |

| STATUS                                                                                       | 03h             | STATUS                        | 83h             |  |

| FSR                                                                                          | 03h<br>04h      | FSR                           | 84h             |  |

| PORTA                                                                                        | 05h             | TRISA                         | 85h             |  |

| 1 OKIN                                                                                       | 06h             | INIOA                         | 86h             |  |

| PORTC                                                                                        | 07h             | TRISC                         | 87h             |  |

| Tokto                                                                                        | 08h             | 11100                         | 88h             |  |

|                                                                                              | 09h             |                               | 89h             |  |

| PCLATH                                                                                       | 0Ah             | PCLATH                        | 8Ah             |  |

| INTCON                                                                                       |                 | INTCON                        |                 |  |

| PIR1                                                                                         | 0Bh             | PIE1                          | 8Bh             |  |

| FIRI                                                                                         | 0Ch             | FIEI                          | 8Ch             |  |

| TMD4                                                                                         | 0Dh             | DOON                          | 8Dh             |  |

| TMR1L                                                                                        | 0Eh             | PCON                          | 8Eh             |  |

| TMR1H                                                                                        | 0Fh             | 000711115                     | 8Fh             |  |

| T1CON                                                                                        | 10h             | OSCTUNE                       | 90h             |  |

|                                                                                              | 11h             | ANSEL                         | 91h             |  |

|                                                                                              | 12h             |                               | 92h             |  |

|                                                                                              | 13h             |                               | 93h             |  |

|                                                                                              | 14h             |                               | 94h             |  |

|                                                                                              | 15h             | WPUA                          | 95h             |  |

|                                                                                              | 16h             | IOCA                          | 96h             |  |

|                                                                                              | 17h             |                               | 97h             |  |

|                                                                                              | 18h             |                               | 98h             |  |

| VRCON                                                                                        | 19h             | SRCON0                        | 99h             |  |

| CM1CON0                                                                                      | 1Ah             | SRCON1                        | 9Ah             |  |

| CM2CON0                                                                                      | 1Bh             |                               | 9Bh             |  |

| CM2CON1                                                                                      | 1Ch             |                               | 9Ch             |  |

|                                                                                              | 1Dh             |                               | 9Dh             |  |

|                                                                                              | 1Eh             |                               | 9Eh             |  |

|                                                                                              | 1Fh             |                               | 9Fh             |  |

|                                                                                              | 20h             |                               | A0h             |  |

|                                                                                              | 3Fh             |                               |                 |  |

|                                                                                              | 40h             |                               |                 |  |

| General<br>Purpose<br>Registers                                                              |                 |                               |                 |  |

| 64 Bytes                                                                                     | 6Fh             |                               |                 |  |

| Accesses 70h-7Fh                                                                             | 70h<br>7Fh      | Accesses 70h-7Fh              | F0h<br>FFh      |  |

| Bank 0                                                                                       | Bank 1          |                               |                 |  |

| Unimplemented data memory locations, read as '0'.<br><b>Note 1:</b> Not a physical register. |                 |                               |                 |  |

## FIGURE 2-4:

#### DATA MEMORY MAP OF THE PIC16F616/16HV616

|                               |                           | PIC10F010/10F                      |               |

|-------------------------------|---------------------------|------------------------------------|---------------|

|                               | File<br>Address           | A                                  | File<br>ddres |

| Indirect Addr. <sup>(1)</sup> | 00h                       | Indirect Addr.(1)                  | 80h           |

| TMR0                          | 01h                       | OPTION_REG                         | 81h           |

| PCL                           | 02h                       | PCL                                | 82h           |

| STATUS                        | 03h                       | STATUS                             | 83h           |

| FSR                           | 04h                       | FSR                                | 84h           |

| PORTA                         | 05h                       | TRISA                              | 85h           |

|                               | 06h                       |                                    | 86h           |

| PORTC                         | 07h                       | TRISC                              | 87h           |

|                               | 08h                       |                                    | 88h           |

|                               | 09h                       |                                    | 89h           |

| PCLATH                        | 0Ah                       | PCLATH                             | 8Ah           |

| INTCON                        | 0Bh                       | INTCON                             | 8Bh           |

| PIR1                          | 0Ch                       | PIE1                               | 8Ch           |

|                               | 0Dh                       |                                    | 8Dh           |

| TMR1L                         | 0Eh                       | PCON                               | 8Eh           |

| TMR1H                         | 0Fh                       |                                    | 8Fh           |

| T1CON                         | 10h                       | OSCTUNE                            | 90h           |

| TMR2                          | 11h                       | ANSEL                              | 91h           |

| T2CON                         | 12h                       | PR2                                | 92h           |

| CCPR1L                        | 13h                       |                                    | 93h           |

| CCPR1H                        | 14h                       |                                    | 94h           |

| CCP1CON                       | 15h                       | WPUA                               | 95h           |

| PWM1CON                       | 16h                       | IOCA                               | 96h           |

| ECCPAS                        | 17h                       | 100/1                              | 97h           |

| 2001710                       | 18h                       |                                    | 98h           |

| VRCON                         | 19h                       | SRCON0                             | 99h           |

| CM1CON0                       | 1Ah                       | SRCON1                             | 99n<br>9Ah    |

| CM2CON0                       | 1Bh                       | ORCONT                             | 9Bh           |

| CM2CON1                       | 1Ch                       |                                    | 9Dh           |

| 011200111                     |                           |                                    |               |

| ADRESH                        | 1Dh                       | ADRESL                             | 9Dh           |

|                               | 1Eh                       | ADCON1                             | 9Eh           |

| ADCON0                        | 1Fh                       | General                            | 9Fh<br>A0h    |

|                               | 20h                       | Purpose                            | 7.01          |

|                               |                           | Registers                          |               |

| General                       |                           | 32 Bytes                           | BFł           |

| Purpose                       |                           |                                    | CO            |

| Registers                     |                           |                                    |               |

| 96 Bytes                      |                           |                                    |               |

|                               |                           |                                    |               |

|                               |                           |                                    |               |

|                               |                           |                                    |               |

|                               | 7Fh                       | Accesses 70h-7Fh                   | F0h<br>FFh    |

| Bank 0                        | J / F(1                   | Bank 1                             | <u> </u>      |

|                               | ata memor<br>iysical regi | y locations, read as '0'.<br>ster. |               |

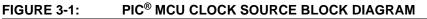

## 3.0 OSCILLATOR MODULE

## 3.1 Overview

The Oscillator module has a wide variety of clock sources and selection features that allow it to be used in a wide range of applications while maximizing performance and minimizing power consumption. Figure 3-1 illustrates a block diagram of the Oscillator module.

Clock sources can be configured from external oscillators, quartz crystal resonators, ceramic resonators and Resistor-Capacitor (RC) circuits. In addition, the system clock source can be configured with a choice of two selectable speeds: internal or external system clock source.

The Oscillator module can be configured in one of eight clock modes.

- 1. EC External clock with I/O on OSC2/CLKOUT.

- 2. LP 32 kHz Low-Power Crystal mode.

- 3. XT Medium Gain Crystal or Ceramic Resonator Oscillator mode.

- 4. HS High Gain Crystal or Ceramic Resonator mode.

- 5. RC External Resistor-Capacitor (RC) with Fosc/4 output on OSC2/CLKOUT.

- 6. RCIO External Resistor-Capacitor (RC) with I/O on OSC2/CLKOUT.

- 7. INTOSC Internal oscillator with Fosc/4 output on OSC2 and I/O on OSC1/CLKIN.

- 8. INTOSCIO Internal oscillator with I/O on OSC1/CLKIN and OSC2/CLKOUT.

Clock Source modes are configured by the FOSC<2:0> bits in the Configuration Word register (CONFIG). The Internal Oscillator module provides a selectable system clock mode of either 4 MHz (Postscaler) or 8 MHz (INTOSC).

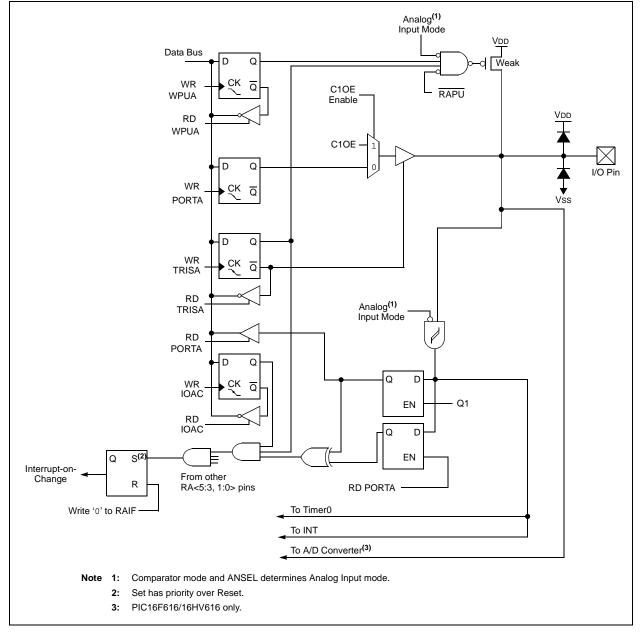

## 4.2.4.3 RA2/AN2<sup>(1)</sup>/T0CKI/INT/C1OUT

Figure 4-2 shows the diagram for this pin. The RA2 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC<sup>(1)</sup>

- the clock input for TMR0

- an external edge triggered interrupt

- a digital output from Comparator C1

## FIGURE 4-2: BLOCK DIAGRAM OF RA2

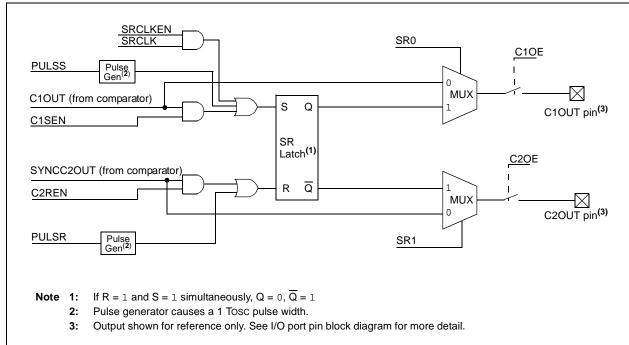

## 8.10 Comparator SR Latch

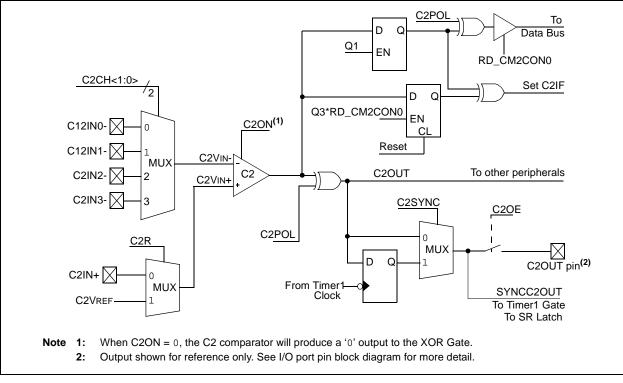

The SR latch module provides additional control of the comparator outputs. The module consists of a single SR latch and output multiplexers. The SR latch can be set, reset or toggled by the comparator outputs. The SR latch may also be set or reset, independent of comparator output, by control bits in the SRCON0 control register. The SR latch output multiplexers select whether the latch outputs or the comparator outputs are directed to the I/O port logic for eventual output to a pin.

The SR latch also has a variable clock, which is connected to the set input of the latch. The SRCLKEN bit of SRCON0 enables the SR latch set clock. The clock will periodically pulse the set input of the latch. Control over the frequency of the SR latch set clock is provided by the SRCS<1:0> bits of SRCON1 register.

### 8.10.1 LATCH OPERATION

The latch is a Set-Reset latch that does not depend on a clock source. Each of the Set and Reset inputs are active-high. Each latch input is connected to a comparator output and a software controlled pulse generator. The latch can be set by C1OUT or the PULSS bit of the SRCON0 register. The latch can be reset by C2OUT or the PULSR bit of the SRCON0 register. The latch is reset-dominant, therefore, if both Set and Reset

inputs are high the latch will go to the Reset state. Both the PULSS and PULSR bits are self resetting which means that a single write to either of the bits is all that is necessary to complete a latch Set or Reset operation.

## 8.10.2 LATCH OUTPUT

The SR<1:0> bits of the SRCON0 register control the latch output multiplexers and determine four possible output configurations. In these four configurations, the CxOUT I/O port logic is connected to:

- C1OUT and C2OUT

- C1OUT and SR latch Q

- C2OUT and SR latch Q

- SR latch Q and Q

After any Reset, the default output configuration is the unlatched C1OUT and C2OUT mode. This maintains compatibility with devices that do not have the SR latch feature.

The applicable TRIS bits of the corresponding ports must be cleared to enable the port pin output drivers. Additionally, the CxOE comparator output enable bits of the CMxCON0 registers must be set in order to make the comparator or latch outputs available on the output pins. The latch configuration enable states are completely independent of the enable states for the comparators.

#### FIGURE 8-8: SR LATCH SIMPLIFIED BLOCK DIAGRAM

## 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/ DONE bit of the ADCON0 register to a '1' will start the analog-to-digital conversion.

| Note: | The GO/DONE bit should not be set in the |

|-------|------------------------------------------|

|       | same instruction that turns on the ADC.  |

|       | Refer to Section 9.2.6 "A/D Conversion   |

|       | Procedure".                              |

### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

#### 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete analog-to-digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

| Note: | A device Reset forces all registers to their |

|-------|----------------------------------------------|

|       | Reset state. Thus, the ADC module is         |

|       | turned off and any pending conversion is     |

|       | terminated.                                  |

### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

## 9.2.5 SPECIAL EVENT TRIGGER

The ECCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not ensure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

See Section 10.0 "Enhanced Capture/Compare/ PWM (With Auto-Shutdown and Dead Band) Module (PIC16F616/16HV616 Only)" for more information.

## 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an analog-to-digital conversion:

- 1. Configure Port:

- Disable pin output driver (See TRIS register)

- Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- Configure voltage reference

- Select ADC input channel

- Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- Clear ADC interrupt flag

- Enable ADC interrupt

- · Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- 5. Start conversion by setting the GO/DONE bit.

- 6. Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- 8. Clear the ADC interrupt flag (required if interrupt is enabled).

- **Note 1:** The global interrupt may be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 9.3 "A/D Acquisition Requirements".

## 10.3.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the CCP1 pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 10.3.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 3.0** "**Oscillator Module**" for additional details.

#### 10.3.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

## 10.3.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the CCP module for PWM operation:

- 1. Configure the PWM pin (CCP1) as an input by setting the associated TRIS bit.

- 2. Set the PWM period by loading the PR2 register.

- Configure the CCP module for the PWM mode by loading the CCP1CON register with the appropriate values.

- 4. Set the PWM duty cycle by loading the CCPR1L register and CCP1 bits of the CCP1CON register.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Set the Timer2 prescale value by loading the T2CKPS bits of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Enable PWM output after a new PWM cycle has started:

- Wait until Timer2 overflows (TMR2IF bit of the PIR1 register is set).

- Enable the CCP1 pin output by clearing the associated TRIS bit.

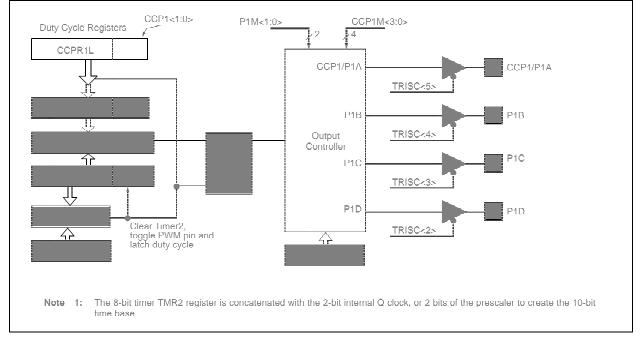

## 10.4 PWM (Enhanced Mode)

The Enhanced PWM Mode can generate a PWM signal on up to four different output pins with up to 10-bits of resolution. It can do this through four different PWM Output modes:

- Single PWM

- Half-Bridge PWM

- Full-Bridge PWM, Forward mode

- Full-Bridge PWM, Reverse mode

To select an Enhanced PWM mode, the P1M bits of the CCP1CON register must be set appropriately.

The PWM outputs are multiplexed with I/O pins and are designated P1A, P1B, P1C and P1D. The polarity of the PWM pins is configurable and is selected by setting the CCP1M bits in the CCP1CON register appropriately.

Table 10-6 shows the pin assignments for each Enhanced PWM mode.

Figure 10-5 shows an example of a simplified block diagram of the Enhanced PWM module.

**Note:** To prevent the generation of an incomplete waveform when the PWM is first enabled, the ECCP module waits until the start of a new PWM period before generating a PWM signal.

## FIGURE 10-5: EXAMPLE SIMPLIFIED BLOCK DIAGRAM OF THE ENHANCED PWM MODE

Note 1: The TRIS register value for each PWM output must be configured appropriately.

- 2: Clearing the CCP1CON register will relinquish ECCP control of all PWM output pins.

- 3: Any pin not used by an Enhanced PWM mode is available for alternate pin functions

#### TABLE 10-6: EXAMPLE PIN ASSIGNMENTS FOR VARIOUS PWM ENHANCED MODES

| ECCP Mode            | P1M | CCP1/P1A | P1B | P1C | P1D |

|----------------------|-----|----------|-----|-----|-----|

| Single               | 00  | Yes      | No  | No  | No  |

| Half-Bridge          | 10  | Yes      | Yes | No  | No  |

| Full-Bridge, Forward | 01  | Yes      | Yes | Yes | Yes |

| Full-Bridge, Reverse | 11  | Yes      | Yes | Yes | Yes |

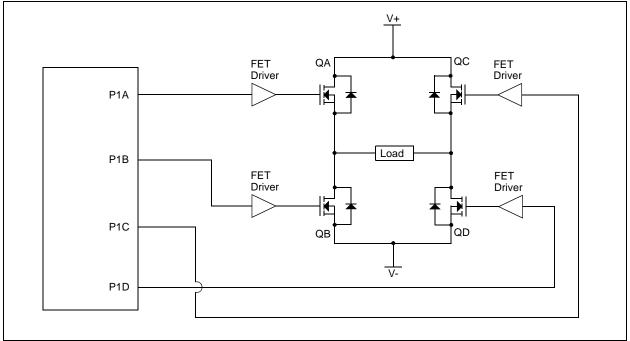

#### 10.4.2 FULL-BRIDGE MODE

In Full-Bridge mode, all four pins are used as outputs. An example of full-bridge application is shown in Figure 10-10.

In the Forward mode, pin CCP1/P1A is driven to its active state, pin P1D is modulated, while P1B and P1C will be driven to their inactive state as shown in Figure 10-11.

In the Reverse mode, P1C is driven to its active state, pin P1B is modulated, while P1A and P1D will be driven to their inactive state as shown Figure 10-11. P1A, P1B, P1C and P1D outputs are multiplexed with the PORT data latches. The associated TRIS bits must be cleared to configure the P1A, P1B, P1C and P1D pins as outputs.

## FIGURE 10-10: EXAMPLE OF FULL-BRIDGE APPLICATION

#### 10.4.4 ENHANCED PWM AUTO-SHUTDOWN MODE

The PWM mode supports an Auto-Shutdown mode that will disable the PWM outputs when an external shutdown event occurs. Auto-Shutdown mode places the PWM output pins into a predetermined state. This mode is used to help prevent the PWM from damaging the application.

The auto-shutdown sources are selected using the ECCPASx bits of the ECCPAS register. A shutdown event may be generated by:

- A logic '0' on the INT pin

- Comparator C1

- Comparator C2

- · Setting the ECCPASE bit in firmware

A shutdown condition is indicated by the ECCPASE (Auto-Shutdown Event Status) bit of the ECCPAS register. If the bit is a '0', the PWM pins are operating normally. If the bit is a '1', the PWM outputs are in the shutdown state.

When a shutdown event occurs, two things happen:

The ECCPASE bit is set to '1'. The ECCPASE will remain set until cleared in firmware or an auto-restart occurs (see Section 10.4.5 "Auto-Restart Mode").

The enabled PWM pins are asynchronously placed in their shutdown states. The PWM output pins are grouped into pairs [P1A/P1C] and [P1B/P1D]. The state of each pin pair is determined by the PSSAC and PSSBD bits of the ECCPAS register. Each pin pair may be placed into one of three states:

- Drive logic '1'

- Drive logic '0'

- Tri-state (high-impedance)

#### REGISTER 10-2: ECCPAS: ENHANCED CAPTURE/COMPARE/PWM AUTO-SHUTDOWN CONTROL REGISTER

|           |       | R/W-0  | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|-----------|-------|--------|---------|---------|---------|--------|--------|--------|--------|

| bit 7 bit | E     | CCPASE | ECCPAS2 | ECCPAS1 | ECCPAS0 | PSSAC1 | PSSAC0 | PSSBD1 | PSSBD0 |

|           | bit 7 | 7      |         |         |         |        |        |        | bit 0  |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

| <ul> <li>1 = A shutdown event has occurred; ECCP outputs are in shutd<br/>0 = ECCP outputs are operating</li> <li>bit 6-4 ECCPAS&lt;2:0&gt;: ECCP Auto-shutdown Source Select bits</li> <li>000 = Auto-Shutdown is disabled</li> <li>001 = Comparator C1 output high</li> </ul> |            |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 000 = Auto-Shutdown is disabled                                                                                                                                                                                                                                                 | iown state |

|                                                                                                                                                                                                                                                                                 |            |

| 010 = Comparator C2 output high <sup>(1)</sup><br>011 = Either Comparators output is high<br>100 = VIL on INT pin<br>101 = VIL on INT pin or Comparator C1 output high<br>110 = VIL on INT pin or Comparator C2 output high                                                     |            |

| 111 = VIL on INT pin or either Comparators output is high                                                                                                                                                                                                                       |            |

| bit 3-2 <b>PSSACn:</b> Pins P1A and P1C Shutdown State Control bits<br>00 = Drive pins P1A and P1C to '0'<br>01 = Drive pins P1A and P1C to '1'<br>1x = Pins P1A and P1C tri-state                                                                                              |            |

| bit 1-0 <b>PSSBDn:</b> Pins P1B and P1D Shutdown State Control bits<br>00 = Drive pins P1B and P1D to '0'<br>01 = Drive pins P1B and P1D to '1'<br>1x = Pins P1B and P1D tri-state                                                                                              |            |

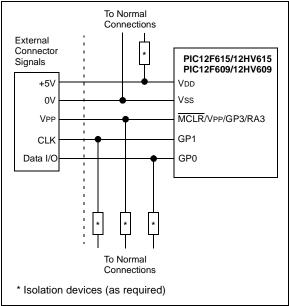

## 12.10 In-Circuit Serial Programming™

The PIC16F610/616/16HV610/616 microcontrollers can be serially programmed while in the end application circuit. This is simply done with five connections for:

- clock

- data

- power

- ground

- programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the RA0 and RA1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the *Memory Programming Specification* (DS41284) for more information. RA0 becomes the programming data and RA1 becomes the programming clock. Both RA0 and RA1 are Schmitt Trigger inputs in Program/Verify mode.

A typical In-Circuit Serial Programming connection is shown in Figure 12-10.

#### FIGURE 12-10: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION

| Note: | To erase t | he device VDD r | must be above   |

|-------|------------|-----------------|-----------------|

|       | the Bulk E | rase VDD minimu | um given in the |

|       | Memory     | Programming     | Specification   |

|       | (DS41284)  | )               |                 |

## 12.11 In-Circuit Debugger

Since in-circuit debugging requires access to three pins, MPLAB<sup>®</sup> ICD 2 development with an 14-pin device is not practical. A special 28-pin PIC16F610/616/ 16HV610/616 ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

A special debugging adapter allows the ICD device to be used in place of a PIC16F610/616/16HV610/616 device. The debugging adapter is the only source of the ICD device.

When the ICD pin on the PIC16F610/616/16HV610/ 616 ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-9 shows which features are consumed by the background debugger.

| TABLE 12-9: DEBUGGER RESOURCES |

|--------------------------------|

|--------------------------------|

| Resource       | Description                         |

|----------------|-------------------------------------|

| I/O pins       | ICDCLK, ICDDATA                     |

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>700h-7FFh |

For more information, see "*MPLAB*<sup>®</sup> *ICD 2 In-Circuit Debugger User's Guide*" (DS51331), available on Microchip's web site (www.microchip.com).

## 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

## 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 15.11 Timing Parameter Symbology

The timing parameter symbols have been created with one of the following formats:

#### 1. TppS2ppS

2. TppS

| <u>z. rpp3</u> |                                      |     |                |

|----------------|--------------------------------------|-----|----------------|

| т              |                                      |     |                |

| F              | Frequency                            | Т   | Time           |

| Lowerc         | ase letters (pp) and their meanings: |     |                |

| рр             |                                      |     |                |

| сс             | CCP1                                 | osc | OSC1           |

| ck             | CLKOUT                               | rd  | RD             |

| CS             | CS                                   | rw  | RD or WR       |

| di             | SDI                                  | sc  | SCK            |

| do             | SDO                                  | SS  | SS             |

| dt             | Data in                              | tO  | TOCKI          |

| io             | I/O Port                             | t1  | T1CKI          |

| mc             | MCLR                                 | wr  | WR             |

| Upperc         | ase letters and their meanings:      |     |                |

| S              |                                      |     |                |

| F              | Fall                                 | Р   | Period         |

| н              | High                                 | R   | Rise           |

| I              | Invalid (High-impedance)             | V   | Valid          |

| L              | Low                                  | Z   | High-impedance |

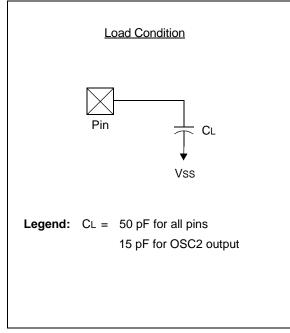

#### FIGURE 15-5: LOAD CONDITIONS

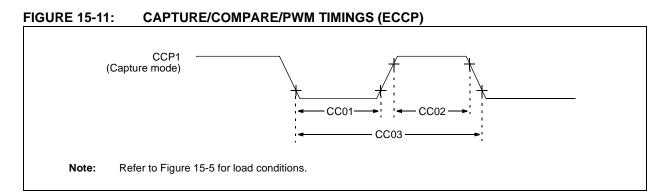

## TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |     |       |            |                                       |

|----------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|-----|-------|------------|---------------------------------------|

| Param<br>No.                                                                                                         | Sym  | Character            | Min            | Тур†                  | Max | Units | Conditions |                                       |

| CC01*                                                                                                                | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —   | _     | ns         |                                       |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —   | _     | ns         |                                       |

| CC02*                                                                                                                | ТссН | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | —   | _     | ns         |                                       |

|                                                                                                                      |      |                      | With Prescaler | 20                    | —   |       | ns         |                                       |

| CC03*                                                                                                                | TccP | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —   | —     | ns         | N = prescale<br>value (1, 4 or<br>16) |

These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

| SHUNT        | REGULAT       | OR CHARACTERISTICS          | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |     |     |       |                                        |  |

|--------------|---------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------|-----|-----|-------|----------------------------------------|--|

| Param<br>No. | Symbol        | Characteristics             | Min                                                                                                                  | Тур | Max | Units | Comments                               |  |

| SR01         | VSHUNT        | Shunt Voltage               | 4.75                                                                                                                 | 5   | 5.4 | V     |                                        |  |

| SR02         | ISHUNT        | Shunt Current               | 4                                                                                                                    | —   | 50  | mA    |                                        |  |

| SR03*        | TSETTLE       | Settling Time               | —                                                                                                                    |     | 150 | ns    | To 1% of final value                   |  |

| SR04         | CLOAD         | Load Capacitance            | 0.01                                                                                                                 | -   | 10  | μF    | Bypass capacitor on VDD pin            |  |

| SR05         | $\Delta$ ISNT | Regulator operating current | —                                                                                                                    | 180 | —   | μΑ    | Includes band gap<br>reference current |  |

## TABLE 15-10: SHUNT REGULATOR SPECIFICATIONS (PIC16HV610/616 only)

These parameters are characterized but not tested.

\*

### TABLE 15-11: PIC16F616/16HV616 A/D CONVERTER (ADC) CHARACTERISTICS:

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |          |       |                                                                     |  |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|----------|-------|---------------------------------------------------------------------|--|

| Param<br>No.                                                                                                         | Sym  | Characteristic                                       | Min        | Тур† | Мах      | Units | Conditions                                                          |  |

| AD01                                                                                                                 | Nr   | Resolution                                           | _          | _    | 10 bits  | bit   |                                                                     |  |

| AD02                                                                                                                 | EIL  | Integral Error                                       | _          | _    | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |  |

| AD03                                                                                                                 | Edl  | Differential Error                                   | _          | —    | ±1       | LSb   | No missing codes to 10 bits<br>VREF = 5.12V <sup>(5)</sup>          |  |

| AD04                                                                                                                 | EOFF | Offset Error                                         | _          | +1.5 | + 2.0    | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |  |

| AD07                                                                                                                 | Egn  | Gain Error                                           | _          | _    | ±1       | LSb   | VREF = 5.12V <sup>(5)</sup>                                         |  |

| AD06<br>AD06A                                                                                                        | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.5 | _    | —<br>Vdd | V     | Absolute minimum to ensure 1 LSb<br>accuracy                        |  |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                     | Vss        | _    | Vref     | V     |                                                                     |  |

| AD08                                                                                                                 | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | —          |      | 10       | kΩ    |                                                                     |  |

| AD09*                                                                                                                | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | —    | 1000     | μΑ    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |  |

|                                                                                                                      |      |                                                      | —          | _    | 50       | μΑ    | During A/D conversion cycle.                                        |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

**5:** VREF = 5V for PIC16HV616.

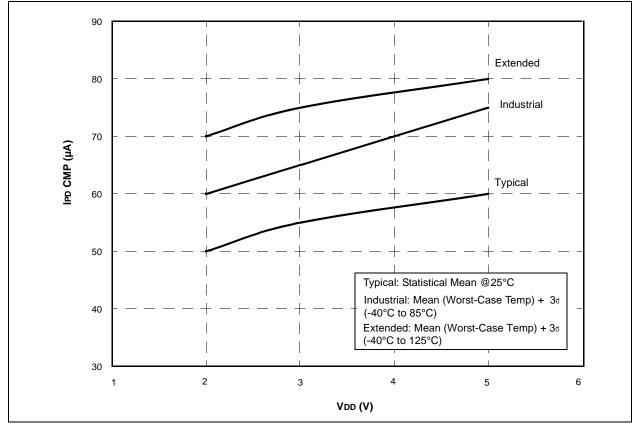

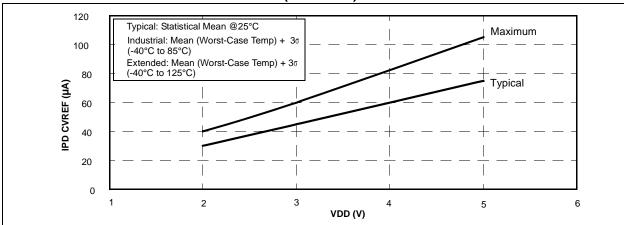

## FIGURE 16-16: PIC16F610/616 IPD CVREF (HI RANGE) vs. VDD

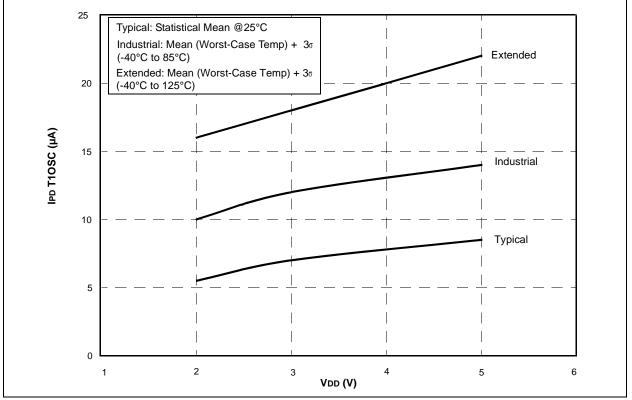

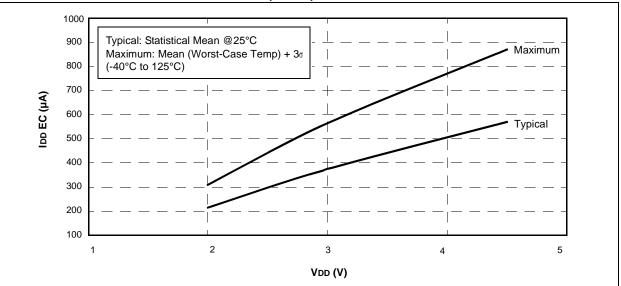

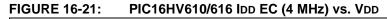

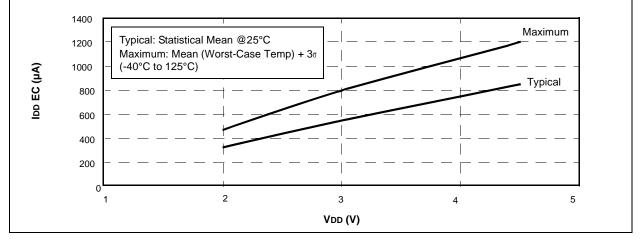

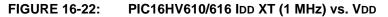

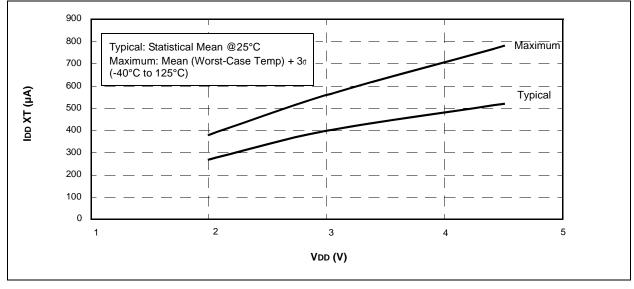

#### FIGURE 16-20: PIC16HV610/616 IDD EC (1 MHz) vs. VDD

NOTES:

## READER RESPONSE

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:                     | Technical Publications Manager                                   | Total Pages Sent                                       |  |  |  |  |  |  |

|-------------------------|------------------------------------------------------------------|--------------------------------------------------------|--|--|--|--|--|--|

| RE:                     | Reader Response                                                  |                                                        |  |  |  |  |  |  |

| Fron                    | n: Name                                                          |                                                        |  |  |  |  |  |  |

|                         | Company                                                          |                                                        |  |  |  |  |  |  |

|                         | Address                                                          |                                                        |  |  |  |  |  |  |

|                         | City / State / ZIP / Country                                     |                                                        |  |  |  |  |  |  |

|                         | Telephone: ()                                                    | FAX: ()                                                |  |  |  |  |  |  |

| Application (optional): |                                                                  |                                                        |  |  |  |  |  |  |

| Wou                     | Would you like a reply?YN                                        |                                                        |  |  |  |  |  |  |

| Devi                    | ce: PIC16F610/616/16HV610/616                                    | Literature Number: DS41288F                            |  |  |  |  |  |  |

| Que                     | stions:                                                          |                                                        |  |  |  |  |  |  |

| 1 \                     | <ol> <li>What are the best features of this document?</li> </ol> |                                                        |  |  |  |  |  |  |

| 1.                      |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| 2.                      | How does this document meet your h                               | nardware and software development needs?               |  |  |  |  |  |  |

|                         |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| 3. I                    | Do you find the organization of this d                           | ocument easy to follow? If not, why?                   |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| 4.                      | What additions to the document do y                              | ou think would enhance the structure and subject?      |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| 5.                      | What deletions from the document co                              | ould be made without affecting the overall usefulness? |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| 6.                      | s there any incorrect or misleading in                           | nformation (what and where)?                           |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |

| -                       |                                                                  | at2                                                    |  |  |  |  |  |  |

| 1.                      | How would you improve this docume                                | nt (                                                   |  |  |  |  |  |  |

| -                       |                                                                  |                                                        |  |  |  |  |  |  |