Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 20MHz                                                                      |

| Connectivity               | -                                                                          |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 11                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | -                                                                          |

| RAM Size                   | 128 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5V                                                                    |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                            |

| Supplier Device Package    | 14-TSSOP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16hv616t-i-st |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, PORTA change and external RA2/INT pin interrupts.

Note: Interrupt flag bits are set when an interrupt condition occurs, regardless of the state of its corresponding enable bit or the global enable bit, GIE of the INTCON register. User software should ensure the appropriate interrupt flag bits are clear prior to enabling an interrupt.

# REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | RAIE  | T0IF  | INTF  | RAIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                    |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                         |

| bit 5 | <b>T0IE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                       |

| bit 4 | INTE: RA2/INT External Interrupt Enable bit<br>1 = Enables the RA2/INT external interrupt<br>0 = Disables the RA2/INT external interrupt                                                         |

| bit 3 | <b>RAIE:</b> PORTA Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the PORTA change interrupt<br>0 = Disables the PORTA change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                       |

| bit 1 | INTF: RA2/INT External Interrupt Flag bit<br>1 = The RA2/INT external interrupt occurred (must be cleared in software)<br>0 = The RA2/INT external interrupt did not occur                       |

| bit 0 | <b>RAIF:</b> PORTA Change Interrupt Flag bit<br>1 = When at least one of the PORTA <5:0> pins changed state (must be cleared in software)<br>0 = None of the PORTA <5:0> pins have changed state |

|       |                                                                                                                                                                                                  |

Note 1: IOCA register must also be enabled.

2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

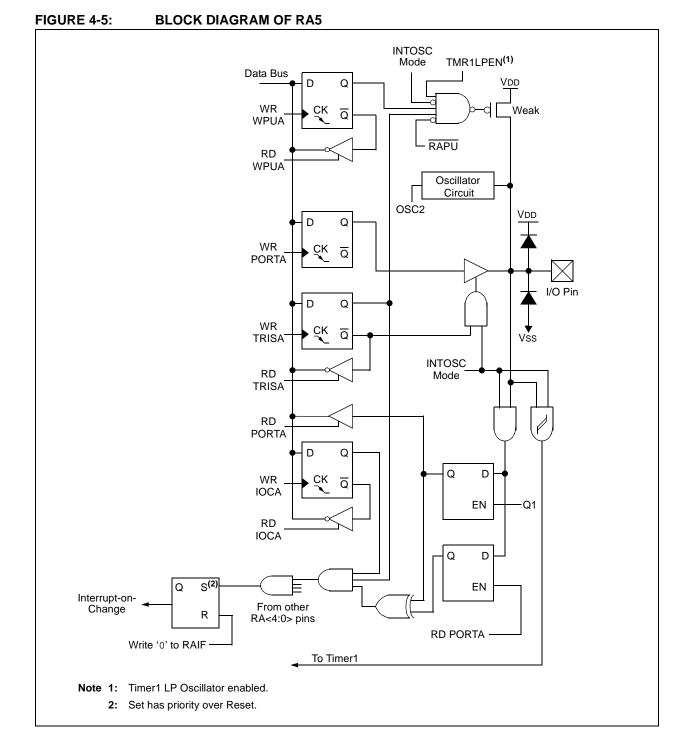

# 4.2.4.6 RA5/T1CKI/OSC1/CLKIN

Figure 4-5 shows the diagram for this pin. The RA5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

# 4.3 PORTC and the TRISC Registers

PORTC is a general purpose I/O port consisting of 6 bidirectional pins. The pins can be configured for either digital I/O or analog input to A/D Converter (ADC) or Comparator. For specific information about individual functions such as the Enhanced CCP or the ADC, refer to the appropriate section in this data sheet.

| Note: | The ANSEL register must be initialized to    |

|-------|----------------------------------------------|

|       | configure an analog channel as a digital     |

|       | input. Pins configured as analog inputs will |

|       | read '0' and cannot generate an interrupt.   |

#### EXAMPLE 4-2: INITIALIZING PORTC

| BCF   | STATUS, RPO | ;Bank 0                |

|-------|-------------|------------------------|

| CLRF  | PORTC       | ;Init PORTC            |

| BSF   | STATUS, RPO | ;Bank 1                |

| CLRF  | ANSEL       | ;digital I/O           |

| MOVLW | 0Ch         | ;Set RC<3:2> as inputs |

| MOVWF | TRISC       | ;and set RC<5:4,1:0>   |

|       |             | ;as outputs            |

| BCF   | STATUS, RPO | ;Bank 0                |

### REGISTER 4-6: PORTC: PORTC REGISTER

| U-0   | U-0 | R/W-x | R/W-x | R/W-0 | R/W-0 | R/W-x | R/W-x |

|-------|-----|-------|-------|-------|-------|-------|-------|

| —     | —   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| bit 7 |     |       |       |       |       |       | bit 0 |

### Legend:

| Legena.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | id as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 5-0 RC<5:0>: PORTC I/O Pin bit

1 = PORTC pin is > VIH

0 = PORTC pin is < VIL

### REGISTER 4-7: TRISC: PORTC TRI-STATE REGISTER

| U-0   | U-0 | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  | R/W-1  |

|-------|-----|--------|--------|--------|--------|--------|--------|

| —     | —   | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 |

| bit 7 |     |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

TRISC<5:0>: PORTC Tri-State Control bit

1 = PORTC pin configured as an input (tri-stated)

0 = PORTC pin configured as an output

bit 5-0

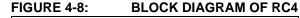

# 4.3.5 RC4/C2OUT/P1B<sup>(1)</sup>

The RC4 is configurable to function as one of the following:

- a general purpose I/O

- a digital output from Comparator C2

- a digital output from the Enhanced CCP<sup>(1)</sup>

Note 1: PIC16F616/16HV616 only.

2: Enabling both C2OUT and P1B will cause a conflict on RC4 and create unpredictable results. Therefore, if C2OUT is enabled, the ECCP can not be used in Half-Bridge or Full-Bridge mode and vice-versa.

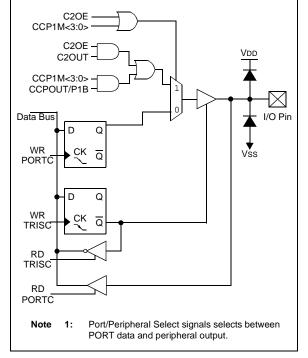

# 4.3.6 RC5/CCP1<sup>(1)</sup>/P1A<sup>(1)</sup>

The RC5 is configurable to function as one of the following:  $\label{eq:configurable}$

- a general purpose I/O

- a digital input/output for the Enhanced CCP<sup>(1)</sup>

- Note 1: PIC16F616/16HV616 only.

FIGURE 4-9: BLO

#### BLOCK DIAGRAM OF RC5 PIN

| TABLE 4-2: | SUMMARY OF REGISTERS ASSOCIATED WITH PORTC |

|------------|--------------------------------------------|

| IADEE + 2. |                                            |

| Name                   | Bit 7 | Bit 6 | Bit 5  | Bit 4  | Bit 3               | Bit 2               | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|-------|-------|--------|--------|---------------------|---------------------|--------|--------|----------------------|---------------------------------|

| ANSEL                  | ANS7  | ANS6  | ANS5   | ANS4   | ANS3 <sup>(1)</sup> | ANS2 <sup>(1)</sup> | ANS1   | ANS0   | 1111 1111            | 1111 1111                       |

| CCP1CON <sup>(1)</sup> | P1M1  | P1M0  | DC1B1  | DC1B0  | CCP1M3              | CCP1M2              | CCP1M1 | CCP1M0 | 0000 0000            | 0000 0000                       |

| CM1CON0                | C10N  | C1OUT | C10E   | C1POL  | _                   | C1R                 | C1CH1  | C1CH0  | 0000 -000            | 0000 -000                       |

| CM2CON0                | C2ON  | C2OUT | C2OE   | C2POL  |                     | C2R                 | C2CH1  | C2CH0  | 0000 -000            | 0000 -000                       |

| PORTC                  |       | _     | RC5    | RC4    | RC3                 | RC2                 | RC1    | RC0    | xx 00xx              | uu 00uu                         |

| TRISC                  | _     | _     | TRISC5 | TRISC4 | TRISC3              | TRISC2              | TRISC1 | TRISC0 | 11 1111              | 11 1111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by PORTC.

Note 1: PIC16F616/HV616 only.

NOTES:

# 6.12 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

# REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0                 | R/W-0                 | R/W-0   | R/W-0   | R/W-0   | R/W-0  | R/W-0  | R/W-0  |

|-----------------------|-----------------------|---------|---------|---------|--------|--------|--------|

| T1GINV <sup>(1)</sup> | TMR1GE <sup>(2)</sup> | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC | TMR1CS | TMR10N |

| bit 7                 |                       |         |         |         |        |        | bit 0  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7   | <b>T1GINV:</b> Timer1 Gate Invert bit <sup>(1)</sup><br>1 = Timer1 gate is active-high (Timer1 counts when gate is high)<br>0 = Timer1 gate is active-low (Timer1 counts when gate is low)                                  |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6   | TMR1GE: Timer1 Gate Enable bit <sup>(2)</sup> If TMR1ON = 0:         This bit is ignored         If TMR1ON = 1:         1 = Timer1 counting is controlled by the Timer1 Gate function         0 = Timer1 is always counting |

| bit 5-4 | <b>T1CKPS&lt;1:0&gt;:</b> Timer1 Input Clock Prescale Select bits<br>11 = 1:8 Prescale Value<br>10 = 1:4 Prescale Value<br>01 = 1:2 Prescale Value<br>00 = 1:1 Prescale Value                                               |

| bit 3   | T1OSCEN: LP Oscillator Enable Control bit<br><u>If INTOSC without CLKOUT oscillator is active:</u><br>1 = LP oscillator is enabled for Timer1 clock<br>0 = LP oscillator is off<br><u>Else:</u><br>This bit is ignored      |

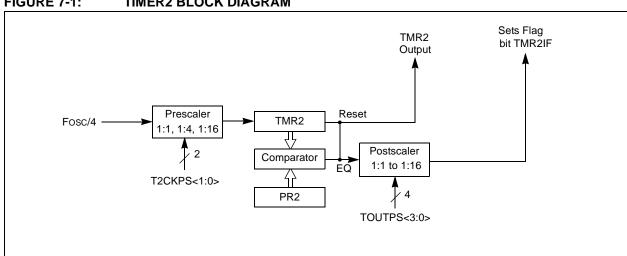

#### 7.0 **TIMER2 MODULE** (PIC16F616/16HV616 ONLY)

The Timer2 module is an 8-bit timer with the following features:

- 8-bit timer register (TMR2)

- 8-bit period register (PR2)

- Interrupt on TMR2 match with PR2

- Software programmable prescaler (1:1, 1:4, 1:16)

- Software programmable postscaler (1:1 to 1:16)

See Figure 7-1 for a block diagram of Timer2.

#### 7.1 **Timer2 Operation**

The clock input to the Timer2 module is the system instruction clock (Fosc/4). The clock is fed into the Timer2 prescaler, which has prescale options of 1:1, 1:4 or 1:16. The output of the prescaler is then used to increment the TMR2 register.

The values of TMR2 and PR2 are constantly compared to determine when they match. TMR2 will increment from 00h until it matches the value in PR2. When a match occurs, two things happen:

- TMR2 is reset to 00h on the next increment cycle.

- The Timer2 postscaler is incremented

The match output of the Timer2/PR2 comparator is then fed into the Timer2 postscaler. The postscaler has postscale options of 1:1 to 1:16 inclusive. The output of the Timer2 postscaler is used to set the TMR2IF interrupt flag bit in the PIR1 register.

| FIGURE 7-1: | <b>TIMER2 BLOCK DIAGRAM</b> |

|-------------|-----------------------------|

|             |                             |

The TMR2 and PR2 registers are both fully readable and writable. On any Reset, the TMR2 register is set to 00h and the PR2 register is set to FFh.

Timer2 is turned on by setting the TMR2ON bit in the T2CON register to a '1'. Timer2 is turned off by setting the TMR2ON bit to a '0'.

The Timer2 prescaler is controlled by the T2CKPS bits in the T2CON register. The Timer2 postscaler is controlled by the TOUTPS bits in the T2CON register. The prescaler and postscaler counters are cleared when:

- A write to TMR2 occurs.

- A write to T2CON occurs.

- Any device Reset occurs (Power-on Reset, MCLR) Reset, Watchdog Timer Reset, or Brown-out Reset).

Note: TMR2 is not cleared when T2CON is written.

#### **TABLE 8-2:** SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND **VOLTAGE REFERENCE MODULES**

| Name    | Bit 7  | Bit 6               | Bit 5                 | Bit 4  | Bit 3               | Bit 2               | Bit 1                 | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|--------|---------------------|-----------------------|--------|---------------------|---------------------|-----------------------|---------|----------------------|---------------------------------|

| ANSEL   | ANS7   | ANS6                | ANS5                  | ANS4   | ANS3 <sup>(1)</sup> | ANS2 <sup>(1)</sup> | ANS1                  | ANS0    | 1111 1111            | 1111 1111                       |

| CM1CON0 | C1ON   | C1OUT               | C1OE                  | C1POL  | C1SP                | C1R                 | C1CH1                 | C1CH0   | 0000 0000            | 0000 0000                       |

| CM2CON0 | C2ON   | C2OUT               | C2OE                  | C2POL  | C2SP                | C2R                 | C2CH1                 | C2CH0   | 0000 0000            | 0000 0000                       |

| CM2CON1 | MC10UT | MC2OUT              | _                     | T1ACS  | C1HYS               | C2HYS               | T1GSS                 | C2SYNC  | 00-0 0010            | 00-0 0010                       |

| INTCON  | GIE    | PEIE                | TOIE                  | INTE   | RAIE                | T0IF                | INTF                  | RAIF    | 0000 000x            | 0000 000x                       |

| PIE1    | _      | ADIE <sup>(1)</sup> | CCP1IE <sup>(1)</sup> | C2IE   | C1IE                | _                   | TMR2IE <sup>(1)</sup> | TMR1IE  | -000 0-00            | -000 0-00                       |

| PIR1    | _      | ADIF <sup>(1)</sup> | CCP1IF <sup>(1)</sup> | C2IF   | C1IF                | _                   | TMR2IF <sup>(1)</sup> | TMR1IF  | -000 0-00            | -000 0-00                       |

| PORTA   | _      | _                   | RA5                   | RA4    | RA3                 | RA2                 | RA1                   | RA0     | x0 x000              | x0 x000                         |

| PORTC   | —      | -                   | RC5                   | RC4    | RC3                 | RC2                 | RC1                   | RC0     | xx 00xx              | uu 00uu                         |

| SRCON0  | SR1    | SR0                 | C1SEN                 | C2REN  | PULSS               | PULSR               | —                     | SRCLKEN | 0000 00-0            | 0000 00-0                       |

| SRCON1  | SRCS1  | SRCS0               | _                     | _      | _                   | _                   | _                     | _       | 00                   | 00                              |

| TRISA   | —      | _                   | TRISA5                | TRISA4 | TRISA3              | TRISA2              | TRISA1                | TRISA0  | 11 1111              | 11 1111                         |

| TRISC   |        |                     | TRISC5                | TRISC4 | TRISC3              | TRISC2              | TRISC1                | TRISC0  | 1111 1111            | 1111 1111                       |

| VRCON   | C1VREN | C2VREN              | VRR                   | FVREN  | VR3                 | VR2                 | VR1                   | VR0     | 0000 0000            | 0000 0000                       |

Legend:

x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

Note

1:

PIC16F616/16HV616 only.

| FIGURE 9 | -2:        | ANA                                  | LOG-T         | O-DIG      | ITAL | CON | /ERSI |               |                       | CLES         |    |             |                             |  |

|----------|------------|--------------------------------------|---------------|------------|------|-----|-------|---------------|-----------------------|--------------|----|-------------|-----------------------------|--|

|          |            | TAD TAD1<br>↑<br>Conver<br>ding Capa | b9<br>sion St | b8<br>arts | b7   | b6  | b5    | b4            | b3                    | b2           | b1 | TAD11<br>b0 |                             |  |

|          | l<br>Set G | O/DONE                               | bit           |            |      |     |       | GO bi<br>ADIF | it is cle<br>bit is s | ared,<br>et, |    | 0           | ]<br>are loade<br>analog ir |  |

# 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an analog-to-digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

**Note:** The ADIF bit is set at the completion of every conversion, regardless of whether or not the ADC interrupt is enabled.

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the interrupt service routine.

Please see **Section 9.1.5** "Interrupts" for more information.

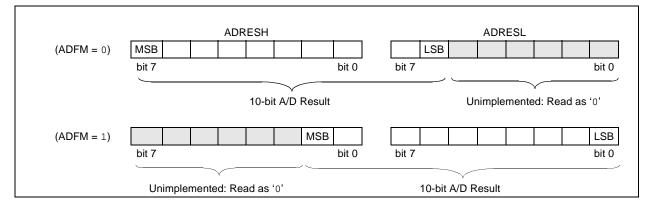

### FIGURE 9-3: 10-BIT A/D CONVERSION RESULT FORMAT

# 9.1.6 RESULT FORMATTING

The 10-bit A/D conversion result can be supplied in two formats, left justified or right justified. The ADFM bit of the ADCON0 register controls the output format.

Figure 9-4 shows the two output formats.

| Name                   | Bit 7       | Bit 6                                                                                          | Bit 5                 | Bit 4   | Bit 3   | Bit 2    | Bit 1                 | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------------------|-------------|------------------------------------------------------------------------------------------------|-----------------------|---------|---------|----------|-----------------------|-----------|----------------------|---------------------------------|

| CCP1CON <sup>(1)</sup> | P1M1        | P1M0                                                                                           | DC1B1                 | DC1B0   | CCP1M3  | CCP1M2   | CCP1M1                | CCP1M0    | 0000 0000            | 0000 0000                       |

| CCPR1L <sup>(1)</sup>  | Capture/Cor | mpare/PWM I                                                                                    | Register 1 Lo         | w Byte  |         |          |                       |           | xxxx xxxx            | uuuu uuuu                       |

| CCPR1H <sup>(1)</sup>  | Capture/Cor | mpare/PWM I                                                                                    | Register 1 Hig        | gh Byte |         |          |                       |           | xxxx xxxx            | uuuu uuuu                       |

| INTCON                 | GIE         | PEIE                                                                                           | T0IE                  | INTE    | RAIE    | T0IF     | INTF                  | RAIF      | 0000 0000            | 0000 0000                       |

| PIE1                   | _           | ADIE <sup>(1)</sup>                                                                            | CCP1IE <sup>(1)</sup> | C2IE    | C1IE    |          | TMR2IE <sup>(1)</sup> | TMR1IE    | -000 0-00            | 0000 0-00                       |

| PIR1                   | —           | ADIF <sup>(1)</sup>                                                                            | CCP1IF <sup>(1)</sup> | C2IF    | C1IF    | —        | TMR2IF <sup>(1)</sup> | TMR1IF    | -000 0-00            | 0000 0-00                       |

| T1CON                  | T1GINV      | TMR1GE                                                                                         | T1CKPS1               | T1CKPS0 | T1OSCEN | T1SYNC   | TMR1CS                | TMR10N    | 0000 0000            | uuuu uuuu                       |

| TMR1L                  | Holding Reg | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuu |                       |         |         |          |                       |           |                      | uuuu uuuu                       |

| TMR1H                  | Holding Reg | Holding Register for the Most Significant Byte of the 16-bit TMR1 Register xxxx xxxx uuuu uuu  |                       |         |         |          |                       | uuuu uuuu |                      |                                 |

| TRISA                  | —           | —                                                                                              | TRISA5                | TRISA4  | TRISA3  | TRISA2   | TRISA1                | TRISA0    | 11 1111              | 11 1111                         |

| TRISC                  | _           | _                                                                                              | TRISC5                | TRISC4  | TRISC3  | TRISC2   | TRISC1                | TRISC0    | 11 1111              | 11 1111                         |

|                        |             |                                                                                                |                       |         |         | <u> </u> |                       |           |                      |                                 |

### TABLE 10-3: SUMMARY OF REGISTERS ASSOCIATED WITH COMPARE

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture, Compare and PWM. Note 1: PIC16F616/16HV616 only.

NOTES:

# 12.0 SPECIAL FEATURES OF THE CPU

The PIC16F610/616/16HV610/616 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power-saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- Oscillator selection

- Sleep

- Code protection

- ID Locations

- In-Circuit Serial Programming<sup>™</sup>

The PIC16F610/616/16HV610/616 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Powerup Timer to provide at least a 64 ms Reset. With these three functions-on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-Down mode. The user can wake-up from Sleep through:

- External Reset

- Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

# 12.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

**Note:** Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See the *Memory Programming Specification* (DS41284) for more information.

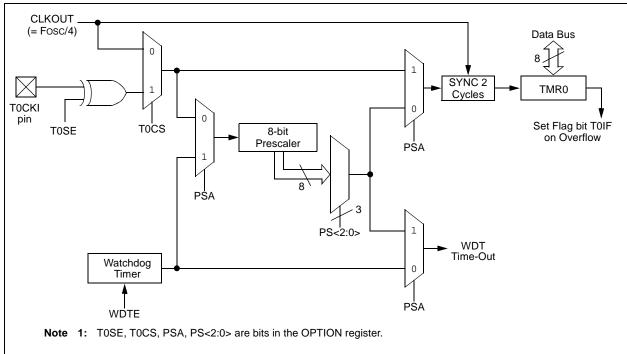

# 12.6 Watchdog Timer (WDT)

The Watchdog Timer is a free running, on-chip RC oscillator, which requires no external components. This RC oscillator is separate from the external RC oscillator of the CLKIN pin and INTOSC. That means that the WDT will run, even if the clock on the OSC1 and OSC2 pins of the device has been stopped (for example, by execution of a SLEEP instruction). During normal operation, a WDT Time-out generates a device Reset. If the device is in Sleep mode, a WDT Time-out causes the device to wake-up and continue with normal operation. The WDT can be permanently disabled by programming the Configuration bit, WDTE, as clear (Section 12.1 "Configuration Bits").

# 12.6.1 WDT PERIOD

The WDT has a nominal time-out period of 18 ms (with no prescaler). The time-out periods vary with temperature, VDD and process variations from part to part (see Table 15-4, Parameter 31). If longer time-out periods are desired, a prescaler with a division ratio of up to 1:128 can be assigned to the WDT under software control by writing to the OPTION register. Thus, time-out periods up to 2.3 seconds can be realized.

The CLRWDT and SLEEP instructions clear the WDT and the prescaler, if assigned to the WDT, and prevent it from timing out and generating a device Reset.

The  $\overline{\text{TO}}$  bit in the STATUS register will be cleared upon a Watchdog Timer Time-out.

#### 12.6.2 WDT PROGRAMMING CONSIDERATIONS

It should also be taken in account that under worstcase conditions (i.e., VDD = Min., Temperature = Max., Max. WDT prescaler) it may take several seconds before a WDT Time-out occurs.

### FIGURE 12-2: WATCHDOG TIMER BLOCK DIAGRAM

### TABLE 12-7: WDT STATUS

| Conditions                                   | WDT                          |  |  |

|----------------------------------------------|------------------------------|--|--|

| WDTE = 0                                     |                              |  |  |

| CLRWDT Command                               | Cleared                      |  |  |

| Exit Sleep + System Clock = EXTRC, INTRC, EC |                              |  |  |

| Exit Sleep + System Clock = XT, HS, LP       | Cleared until the end of OST |  |  |

| ADDLW            | Add literal and W                                                                                                          |

|------------------|----------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] ADDLW k                                                                                                          |

| Operands:        | $0 \leq k \leq 255$                                                                                                        |

| Operation:       | $(W) + k \to (W)$                                                                                                          |

| Status Affected: | C, DC, Z                                                                                                                   |

| Description:     | The contents of the W register<br>are added to the eight-bit literal 'k'<br>and the result is placed in the<br>W register. |

| BCF              | Bit Clear f                                                         |

|------------------|---------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ]BCF f,b                                             |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |

| Operation:       | $0 \rightarrow (f < b >)$                                           |

| Status Affected: | None                                                                |

| Description:     | Bit 'b' in register 'f' is cleared.                                 |

| ADDWF            | Add W and f                                                                                                                                                                        |  |  |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] ADDWF f,d                                                                                                                                                         |  |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                    |  |  |  |  |  |  |

| Operation:       | (W) + (f) $\rightarrow$ (destination)                                                                                                                                              |  |  |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                                                                           |  |  |  |  |  |  |

| Description:     | Add the contents of the W register<br>with register 'f'. If 'd' is '0', the<br>result is stored in the W register. If<br>'d' is '1', the result is stored back<br>in register 'f'. |  |  |  |  |  |  |

| BSF              | Bit Set f                                                           |  |  |

|------------------|---------------------------------------------------------------------|--|--|

| Syntax:          | [ <i>label</i> ] BSF f,b                                            |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$ |  |  |

| Operation:       | $1 \rightarrow (f < b >)$                                           |  |  |

| Status Affected: | None                                                                |  |  |

| Description:     | Bit 'b' in register 'f' is set.                                     |  |  |

| ANDLW            | AND literal with W                                                                                                     |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] ANDLW k                                                                                               |  |  |  |

| Operands:        | $0 \leq k \leq 255$                                                                                                    |  |  |  |

| Operation:       | (W) .AND. (k) $\rightarrow$ (W)                                                                                        |  |  |  |

| Status Affected: | Z                                                                                                                      |  |  |  |

| Description:     | The contents of W register are<br>AND'ed with the eight-bit literal<br>'k'. The result is placed in the W<br>register. |  |  |  |

| ANDWF            | AND W with f                                                                                                                                                    |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ label ] ANDWF f,d                                                                                                                                             |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                 |  |  |  |

| Operation:       | (W) .AND. (f) $\rightarrow$ (destination)                                                                                                                       |  |  |  |

| Status Affected: | Z                                                                                                                                                               |  |  |  |

| Description:     | AND the W register with register<br>'f'. If 'd' is '0', the result is stored in<br>the W register. If 'd' is '1', the<br>result is stored back in register 'f'. |  |  |  |

| BTFSC            | Bit Test f, Skip if Clear                                                                                                                                                                                                     |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] BTFSC f,b                                                                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ 0 \leq b \leq 7 \end{array}$                                                                                                                                                           |

| Operation:       | skip if (f <b>) = <math>0</math></b>                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                          |

| Description:     | If bit 'b' in register 'f' is '1', the next<br>instruction is executed.<br>If bit 'b' in register 'f' is '0', the next<br>instruction is discarded, and a NOP<br>is executed instead, making this a<br>two-cycle instruction. |

# 13.2 Instruction Descriptions

# 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit<sup>™</sup> 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

# 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

# 14.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 14.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 14.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

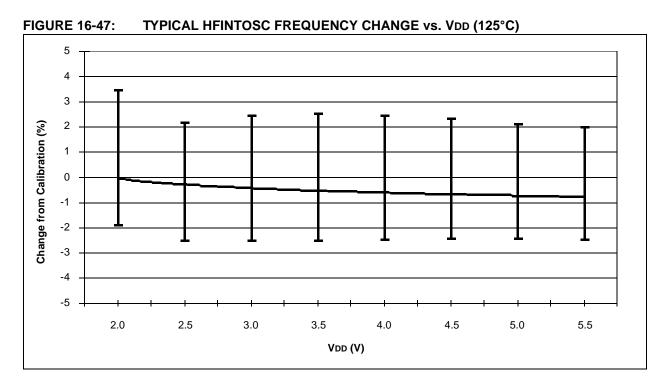

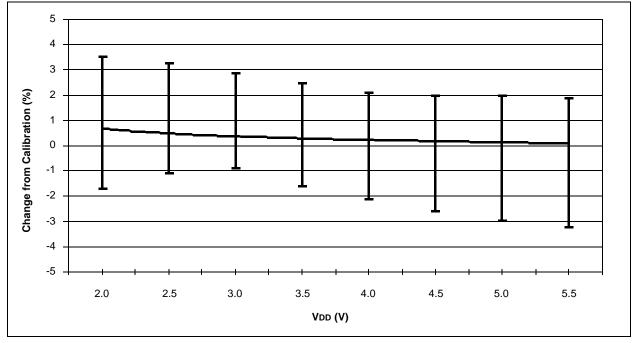

FIGURE 16-48: TYPICAL HFINTOSC FREQUENCY CHANGE vs. Vdd (-40°C)

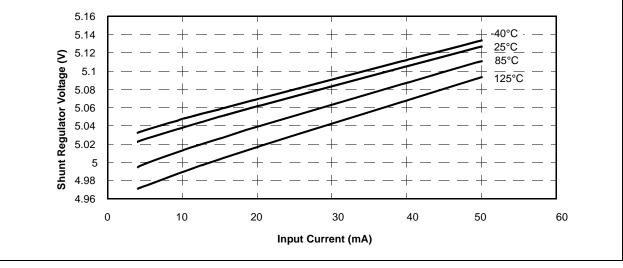

# 16-Lead Plastic Quad Flat, No Lead Package (ML) – 4x4x0.9 mm Body [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |          |      |      |

|------------------------|-------------|----------|------|------|

| Dimension Limits       |             | MIN      | NOM  | MAX  |

| Number of Pins         | Ν           | 16       |      |      |

| Pitch                  | е           | 0.65 BSC |      |      |

| Overall Height         | А           | 0.80     | 0.90 | 1.00 |

| Standoff               | A1          | 0.00     | 0.02 | 0.05 |

| Contact Thickness      | A3          | 0.20 REF |      |      |

| Overall Width          | Е           | 4.00 BSC |      |      |

| Exposed Pad Width      | E2          | 2.50     | 2.65 | 2.80 |

| Overall Length         | D           | 4.00 BSC |      |      |

| Exposed Pad Length     | D2          | 2.50     | 2.65 | 2.80 |

| Contact Width          | b           | 0.25     | 0.30 | 0.35 |

| Contact Length         | L           | 0.30     | 0.40 | 0.50 |

| Contact-to-Exposed Pad | К           | 0.20     | -    | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-127B

# WORLDWIDE SALES AND SERVICE

#### AMERICAS

Corporate Office 2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support: http://support.microchip.com Web Address: www.microchip.com

Atlanta Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Boston Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

**Cleveland** Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas** Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

Toronto Mississauga, Ontario, Canada Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

**China - Beijing** Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

**China - Chengdu** Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

**China - Hong Kong SAR** Tel: 852-2401-1200 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470 China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

**China - Shanghai** Tel: 86-21-5407-5533 Fax: 86-21-5407-5066

**China - Shenyang** Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

**China - Shenzhen** Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

**China - Wuhan** Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

**China - Xiamen** Tel: 86-592-2388138 Fax: 86-592-2388130

**China - Xian** Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

**China - Zhuhai** Tel: 86-756-3210040 Fax: 86-756-3210049

### ASIA/PACIFIC

India - Bangalore Tel: 91-80-3090-4444 Fax: 91-80-3090-4080

India - New Delhi Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

**Japan - Yokohama** Tel: 81-45-471- 6166 Fax: 81-45-471-6122

**Korea - Daegu** Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu Tel: 886-3-6578-300 Fax: 886-3-6578-370

**Taiwan - Kaohsiung** Tel: 886-7-536-4818 Fax: 886-7-536-4803

**Taiwan - Taipei** Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

**Thailand - Bangkok** Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

**Germany - Munich** Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Italy - Milan** Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen Tel: 31-416-690399 Fax: 31-416-690340

**Spain - Madrid** Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

**UK - Wokingham** Tel: 44-118-921-5869 Fax: 44-118-921-5820