# E·XFL

#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Not For New Designs                                                                                                 |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 4 Core, 32-Bit                                                                                                      |

| Speed                              | 1.0GHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | SATA 3Gbps (1)                                                                                                      |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -20°C ~ 105°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA, FCBGA                                                                                                    |

| Supplier Device Package            | 624-FCPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6q5eym10acr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Introduction

- 1. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz.

- 2. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

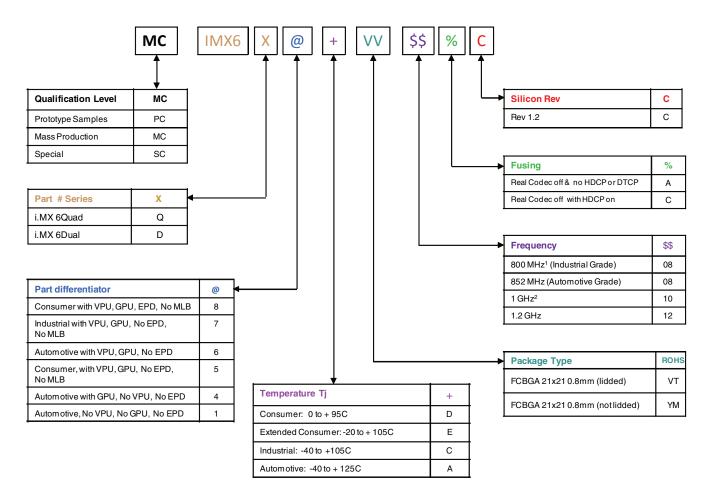

### Figure 1. Part Number Nomenclature—i.MX 6Quad and i.MX 6Dual

#### Introduction

# 1.2 Features

The i.MX 6Dual/6Quad processors are based on ARM Cortex-A9 MPCore<sup>™</sup> Platform, which has the following features:

- ARM Cortex-A9 MPCore 4xCPU Processor (with TrustZone)

- The core configuration is symmetric, where each core includes:

- 32 KByte L1 Instruction Cache

- 32 KByte L1 Data Cache

- Private Timer and Watchdog

- Cortex-A9 NEON MPE (Media Processing Engine) Co-processor

The ARM Cortex-A9 MPCore complex includes:

- General Interrupt Controller (GIC) with 128 interrupt support

- Global Timer

- Snoop Control Unit (SCU)

- 1 MB unified I/D L2 cache, shared by two/four cores

- Two Master AXI (64-bit) bus interfaces output of L2 cache

- Frequency of the core (including Neon and L1 cache) as per Table 7, "Operating Ranges," on page 23

- NEON MPE coprocessor

- SIMD Media Processing Architecture

- NEON register file with 32x64-bit general-purpose registers

- NEON Integer execute pipeline (ALU, Shift, MAC)

- NEON dual, single-precision floating point execute pipeline (FADD, FMUL)

- NEON load/store and permute pipeline

The memory system consists of the following components:

- Level 1 Cache—32 KB Instruction, 32 KB Data cache per core

- Level 2 Cache—Unified instruction and data (1 MByte)

- On-Chip Memory:

- Boot ROM, including HAB (96 KB)

- Internal multimedia / shared, fast access RAM (OCRAM, 256 KB)

- Secure/non-secure RAM (16 KB)

- External memory interfaces:

- 16-bit, 32-bit, and 64-bit DDR3-1066, LVDDR3-1066, and 1/2 LPDDR2-1066 channels, supporting DDR interleaving mode, for 2x32 LPDDR2-1066

- 8-bit NAND-Flash, including support for Raw MLC/SLC, 2 KB, 4 KB, and 8 KB page size, BA-NAND, PBA-NAND, LBA-NAND, OneNAND<sup>™</sup> and others. BCH ECC up to 40 bit.

- 16/32-bit NOR Flash. All EIMv2 pins are muxed on other interfaces.

- 16/32-bit PSRAM, Cellular RAM

| Block<br>Mnemonic | Block Name                      | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------|---------------------------------|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-2<br>(TZ)    | Watchdog<br>(TrustZone)         | Timer<br>Peripherals        | The TrustZone Watchdog (TZ WDOG) timer module protects against<br>TrustZone starvation by providing a method of escaping normal mode<br>and forcing a switch to the TZ mode. TZ starvation is a situation where<br>the normal OS prevents switching to the TZ mode. Such a situation is<br>undesirable as it can compromise the system's security. Once the TZ<br>WDOG module is activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer times out. Upon<br>a time-out, the TZ WDOG asserts a TZ mapped interrupt that forces<br>switching to the TZ mode. If it is still not served, the TZ WDOG asserts<br>a security violation signal to the CSU. The TZ WDOG module cannot be<br>programmed or deactivated by a normal mode Software. |

| EIM               | NOR-Flash /PSRAM<br>interface   | Connectivity<br>Peripherals | <ul> <li>The EIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| XTALOSC           | Crystal Oscillator<br>interface |                             | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 2. i.MX 6Dual/6Quad Modules List (continued) |

|----------------------------------------------------|

|----------------------------------------------------|

# 4.1.6 Low Power Mode Supply Currents

Table 11 shows the current core consumption (not including I/O) of i.MX 6Dual/6Quad processors in selected low power modes.

| Mode            | Test Conditions                                                                                                                                                 | Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Typical <sup>1</sup>                                  | Unit |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|------|

| WAIT            | ARM, SoC, and PU LDOs are set to 1.225 V                                                                                                                        | Supply         Typical <sup>1</sup> VDDARM_IN (1.4 V)         6           VDDSoC_IN (1.4 V)         23           VDDHIGH_IN (3.0 V)         3.7           Total         52           VDDARM_IN (1.4 V)         7.5           VDDSoC_IN (1.4 V)         22           VDDARM_IN (1.4 V)         22           VDDNSoC_IN (1.4 V)         22           VDDHIGH_IN (3.0 V)         3.7           Total         52           VDDSoC_IN (1.4 V)         7.5           VDDSoC_IN (1.4 V)         7.5           VDDSoC_IN (1.4 V)         13.5           VDDSoC_IN (1.4 V)         13.5           VDDSoC_IN (1.4 V)         3.7           Total         41           VDDSoC_IN (0.9 V)         0.1           VDDSoC_IN (0.9 V)         13           VDDHIGH_IN (3.0 V)         3.7           Total         22           VDDHIGH_IN (0.9 V)         0.1           VDDARM_IN (0.9 V)         0.1           VDDSoC_IN (0.9 V)         2           VDDHIGH_IN (3.0 V)         0.5 | mA                                                    |      |

|                 | HIGH LDO set to 2.5 V     Clocks are gated                                                                                                                      | VDDSoC_IN (1.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 23                                                    | mA   |

|                 | <ul> <li>DDR is in self refresh</li> <li>PLLs are active in bypass (24 MHz)</li> </ul>                                                                          | VDDHIGH_IN (3.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.7                                                   | mA   |

|                 | Supply voltages remain ON                                                                                                                                       | VDDSoC_IN (1.4 V)           VDDHIGH_IN (3.0 V)           Total           VDDARM_IN (1.4 V)           VDDSoC_IN (1.4 V)           VDDSoC_IN (1.4 V)           VDDHIGH_IN (3.0 V)           Total           VDDSoC_IN (1.4 V)           VDDRM_IN (3.0 V)           Total           VDDSoC_IN (1.4 V)           VDDHIGH_IN (3.0 V)           Total           VDDARM_IN (0.9 V)           VDDSoC_IN (0.9 V)           VDDSoC_IN (0.9 V)           VDDHIGH_IN (3.0 V)           Total                                                                                                                                                                                                                                                                                                                                                                     | 52                                                    | mW   |

| STOP_ON         | ARM LDO set to 0.9 V                                                                                                                                            | VDDARM_IN (1.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ | mA   |

|                 | <ul> <li>SoC and PU LDOs set to 1.225 V</li> <li>HIGH LDO set to 2.5 V</li> </ul>                                                                               | VDDSoC_IN (1.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 22                                                    | mA   |

|                 | <ul> <li>PLLs disabled</li> <li>DDR is in self refresh</li> </ul>                                                                                               | VDDHIGH_IN (3.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.7                                                   | mA   |

|                 |                                                                                                                                                                 | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 52                                                    | mW   |

| STOP_OFF        | ARM LDO set to 0.9 V                                                                                                                                            | VDDARM_IN (1.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 7.5                                                   | mA   |

|                 | <ul> <li>SoC LDO set to 1.225 V</li> <li>PU LDO is power gated</li> <li>HIGH LDO set to 2.5 V</li> <li>PLLs disabled</li> <li>DDR is in self refresh</li> </ul> | VDDSoC_IN (1.4 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13.5                                                  | mA   |

|                 |                                                                                                                                                                 | VDDHIGH_IN (3.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.7                                                   | mA   |

|                 |                                                                                                                                                                 | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 41                                                    | mW   |

| STANDBY         | ARM and PU LDOs are power gated                                                                                                                                 | VDDSoC_IN (1.4 V)         13.5           VDDHIGH_IN (3.0 V)         3.7           Total         41           power gated         VDDARM_IN (0.9 V)         0.1           V         VDDSoC_IN (0.9 V)         13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 0.1                                                   | mA   |

|                 | <ul> <li>SoC LDO is in bypass</li> <li>HIGH LDO is set to 2.5 V</li> </ul>                                                                                      | VDDSoC_IN (0.9 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 13                                                    | mA   |

|                 | <ul><li>PLLs are disabled</li><li>Low voltage</li></ul>                                                                                                         | VDDHIGH_IN (3.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 3.7                                                   | mA   |

|                 | Well Bias ON     XTAL is enabled                                                                                                                                | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 22                                                    | mW   |

| Deep Sleep Mode | ARM and PU LDOs are power gated                                                                                                                                 | VDDARM_IN (0.9 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0.1                                                   | mA   |

| (DSM)           | <ul> <li>SoC LDO is in bypass</li> <li>HIGH LDO is set to 2.5 V</li> </ul>                                                                                      | VDDSoC_IN (0.9 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 2                                                     | mA   |

|                 | <ul><li>PLLs are disabled</li><li>Low voltage</li></ul>                                                                                                         | VDDHIGH_IN (3.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0.5                                                   | mA   |

|                 | <ul><li>Well Bias ON</li><li>XTAL and bandgap are disabled</li></ul>                                                                                            | Total                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3.4                                                   | mW   |

Table 11. Stop Mode Current and Power Consumption

The typical values shown here are for information only and are not guaranteed. These values are average values measured on a worst-case wafer at 25°C.

1

# 4.8.2 DDR I/O Output Buffer Impedance

The LPDDR2 interface fully complies with JESD209-2B LPDDR2 JEDEC standard release June, 2009. The DDR3 interface fully complies with JESD79-3D DDR3 JEDEC standard release April, 2008.

Table 33 shows DDR I/O output buffer impedance of i.MX 6Dual/6Quad processors.

|                            |        |                                                                                | Тур                                              |                                                  |      |

|----------------------------|--------|--------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------|

| Parameter                  | Symbol | Test Conditions                                                                | NVCC_DRAM=1.5 V<br>(DDR3)<br>DDR_SEL=11          | NVCC_DRAM=1.2 V<br>(LPDDR2)<br>DDR_SEL=10        | Unit |

| Output Driver<br>Impedance | Rdrv   | Drive Strength (DSE) =<br>000<br>001<br>010<br>011<br>100<br>101<br>110<br>111 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Hi-Z<br>240<br>120<br>80<br>60<br>48<br>40<br>34 | Ω    |

Table 33. DDR I/O Output Buffer Impedance

Note:

1. Output driver impedance is controlled across PVTs using ZQ calibration procedure.

2. Calibration is done against 240 W external reference resistor.

3. Output driver impedance deviation (calibration accuracy) is ±5% (max/min impedance) across PVTs.

# 4.8.3 LVDS I/O Output Buffer Impedance

The LVDS interface complies with TIA/EIA 644-A standard. See, TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits" for details.

# 4.9 System Modules Timing

This section contains the timing and electrical parameters for the modules in each i.MX 6Dual/6Quad processor.

# 4.9.1 Reset Timings Parameters

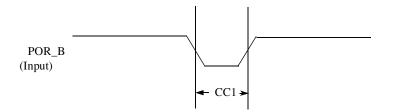

Figure 8 shows the reset timing and Table 34 lists the timing parameters.

Figure 8. Reset Timing Diagram

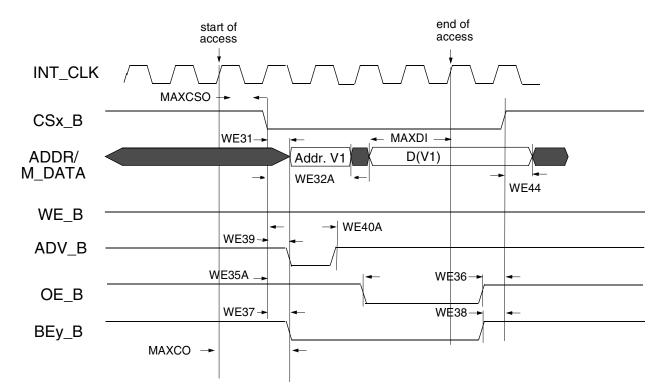

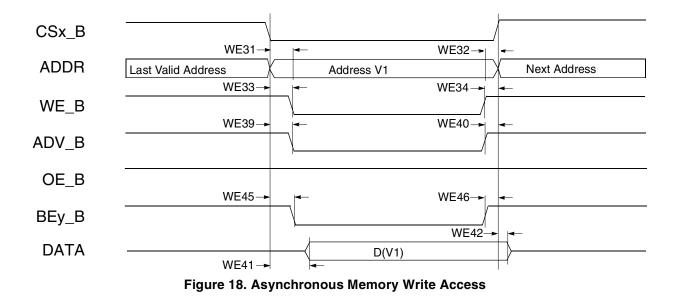

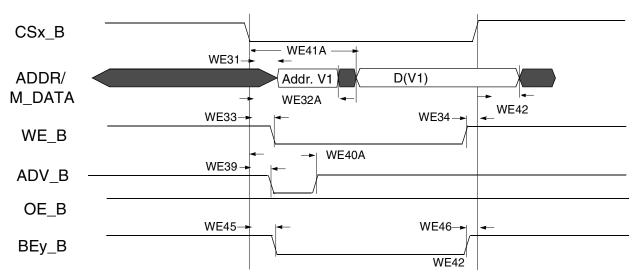

Figure 19. Asynchronous A/D Muxed Write Access

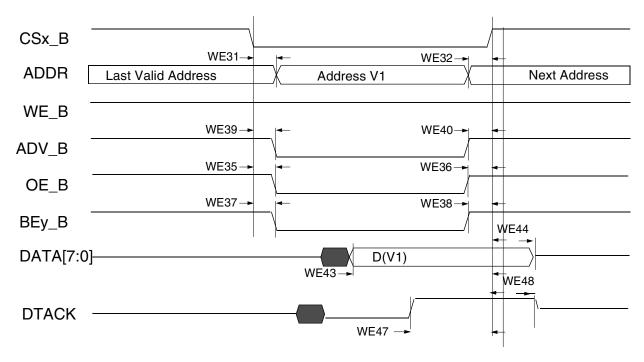

Figure 20. DTACK Read Access (DAP=0)

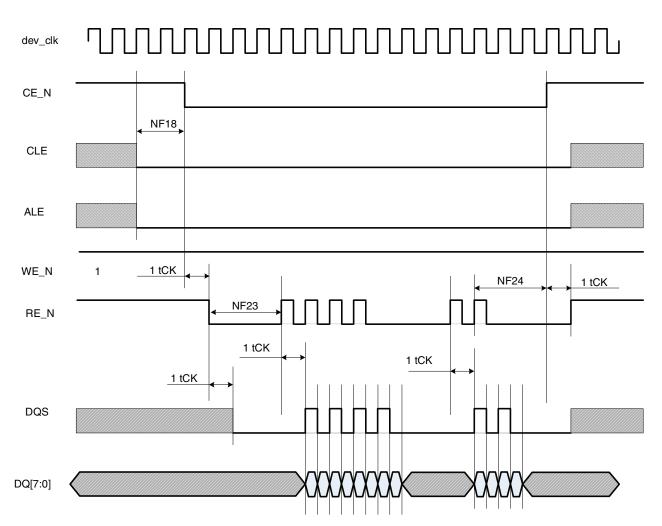

Figure 38. Samsung Toggle Mode Data Read Timing

| ID   | Parameter                     | Symbol | Timin<br>T = GPMI Clo | Unit      |    |

|------|-------------------------------|--------|-----------------------|-----------|----|

|      |                               |        | Min.                  | Ain. Max. |    |

| NF18 | CE# access time               | tCE    | CE_DELAY*tCK          | —         | ns |

| NF19 | CE# hold time                 | tCH    | 0.5 *tCK              | —         | ns |

| NF20 | Command/address DQ setup time | tCAS   | 0.5*tCK               | —         | ns |

| NF21 | Command/address DQ hold time  | tCAH   | 0.5*tCK               | —         | ns |

| NF22 | clock period                  | tCK    | 7.5                   |           | ns |

| NF23 | preamble delay                | tPRE   | (PRE_DELAY+1)*tCK     | _         | ns |

| NF24 | postamble delay               | tPOST  | POST_DELAY*tCK        | —         | ns |

| NF25 | CLE and ALE setup time        | tCALS  | 0.5*tCK               | —         | ns |

| NF26 | CLE and ALE hold time         | tCALH  | 0.5*tCK               | —         | ns |

Table 48. Samsung Toggle Mode Timing Parameters

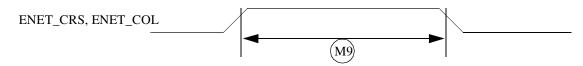

# 4.11.5.1.3 MII Asynchronous Inputs Signal Timing (ENET\_CRS and ENET\_COL)

Figure 48 shows MII asynchronous input timings. Table 57 describes the timing parameter (M9) shown in the figure.

Figure 48. MII Async Inputs Timing Diagram

| Table 57. MII Asynchronous | Inputs | Signal | Timing |

|----------------------------|--------|--------|--------|

|----------------------------|--------|--------|--------|

| ID              | Characteristic                           | Min. | Max. | Unit               |

|-----------------|------------------------------------------|------|------|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5  |      | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

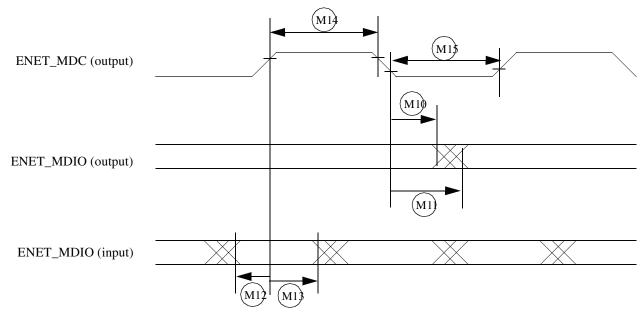

### 4.11.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 49 shows MII asynchronous input timings. Table 58 describes the timing parameters (M10–M15) shown in the figure.

Figure 49. MII Serial Management Channel Timing Diagram

| ID  | Characteristic                                                             | Min. | Max. | Unit            |

|-----|----------------------------------------------------------------------------|------|------|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (min. propagation delay) | 0    | _    | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (max. propagation delay)   | _    | 5    | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                            | 18   | _    | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                             | 0    |      | ns              |

| M14 | ENET_MDC pulse width high                                                  | 40%  | 60%  | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                   | 40%  | 60%  | ENET_MDC period |

### Table 58. MII Serial Management Channel Timing

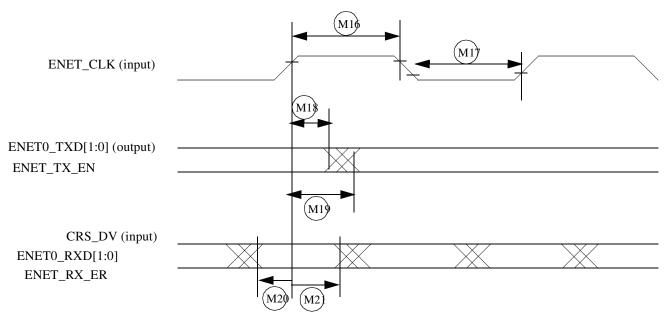

### 4.11.5.2 RMII Mode Timing

In RMII mode, ENET\_CLK is used as the REF\_CLK, which is a 50 MHz ± 50 ppm continuous reference clock. ENET\_RX\_EN is used as the CRS\_DV in RMII. Other signals under RMII mode include ENET\_TX\_EN, ENET0\_TXD[1:0], ENET0\_RXD[1:0] and ENET\_RX\_ER.

Figure 50 shows RMII mode timings. Table 59 describes the timing parameters (M16–M21) shown in the figure.

Figure 50. RMII Mode Signal Timing Diagram

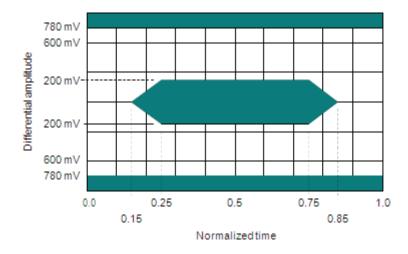

Figure 58. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

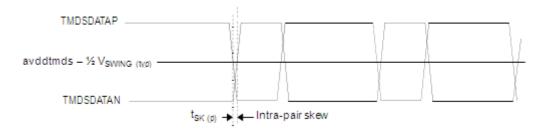

Figure 59. Intra-Pair Skew Definition

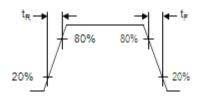

### Figure 61. TMDS Output Signals Rise and Fall Time Definition

-

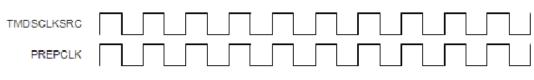

### Figure 62. PREPCLK Frequencies

### **Table 62. Switching Characteristics**

| Symbol         | Parameter                               | Conditions                                                              | Min. | Тур. | Max.   | Unit |

|----------------|-----------------------------------------|-------------------------------------------------------------------------|------|------|--------|------|

|                | ТМ                                      | DS Drivers Specifications                                               |      |      |        |      |

| —              | Maximum serial data rate                | _                                                                       | _    | _    | 3.4    | Gbps |

| F<br>TMDSCLK   | TMDSCLK frequency                       | On TMDSCLKP/N outputs                                                   | 25   |      | 340    | MHz  |

| P<br>TMDSCLK   | TMDSCLK period                          | RL = 50 Ω<br>See Figure 57.                                             | 2.94 | —    | 40     | ns   |

| t<br>CDC       | TMDSCLK duty cycle                      | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 57. | 40   | 50   | 60     | %    |

| t<br>CPH       | TMDSCLK high time                       | RL = 50 Ω<br>See Figure 57.                                             | 4    | 5    | 6      | UI   |

| t<br>CPL       | TMDSCLK low time                        | RL = 50 Ω<br>See Figure 57.                                             | 4    | 5    | 6      | UI   |

| _              | TMDSCLK jitter <sup>1</sup>             | RL = 50 Ω                                                               | —    |      | 0.25   | UI   |

| t<br>SK(p)     | Intra-pair (pulse) skew                 | RL = 50 Ω<br>See Figure 59.                                             | —    | -    | 0.15   | UI   |

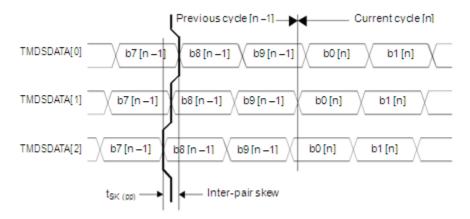

| t<br>SK(pp)    | Inter-pair skew                         | RL = 50 Ω<br>See Figure 60.                                             | —    | -    | 1      | UI   |

| t <sub>R</sub> | Differential output signal rise<br>time | 20–80%<br>RL = 50 Ω<br>See Figure 61.                                   | 75   | _    | 0.4 UI | ps   |

| t <sub>F</sub> | Differential output signal fall time    | 20–80%<br>RL = 50 $\Omega$<br>See Figure 61.                            | 75   | _    | 0.4 UI | ps   |

|                | Differential signal overshoot           | Referred to 2x V <sub>SWING</sub>                                       | _    | _    | 15     | %    |

### Table 67 shows timing characteristics of signals presented in Figure 68 and Figure 69.

| ID   | Parameter                      | Symbol | Value                                 | Description                                                                                                                                                                                                                                                                                                      | Unit |

|------|--------------------------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| IP5  | Display interface clock period | Tdicp  | (1)                                   | Display interface clock. IPP_DISP_CLK                                                                                                                                                                                                                                                                            | ns   |

| IP6  | Display pixel clock period     | Tdpcp  | DISP_CLK_PER_PIXEL<br>X Tdicp         | Time of translation of one pixel to display,<br>DISP_CLK_PER_PIXEL—number of pixel<br>components in one pixel (1.n). The<br>DISP_CLK_PER_PIXEL is virtual<br>parameter to define display pixel clock<br>period.<br>The DISP_CLK_PER_PIXEL is received by<br>DC/DI one access division to <b>n</b><br>components. | ns   |

| IP7  | Screen width time              | Tsw    | (SCREEN_WIDTH)<br>× Tdicp             | interface clocks. horizontal blanking<br>included.<br>The SCREEN_WIDTH should be built by<br>suitable DI's counter <sup>2</sup> .                                                                                                                                                                                |      |

| IP8  | HSYNC width time               | Thsw   | (HSYNC_WIDTH)                         | HSYNC_WIDTH—Hsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                     |      |

| IP9  | Horizontal blank interval 1    | Thbi1  | BGXP × Tdicp                          | BGXP—width of a horizontal blanking<br>before a first active data in a line (in<br>interface clocks). The BGXP should be built<br>by suitable DI's counter.                                                                                                                                                      |      |

| IP10 | Horizontal blank interval 2    | Thbi2  | (SCREEN_WIDTH –<br>BGXP – FW) × Tdicp | <ul> <li>Width a horizontal blanking after a last</li> </ul>                                                                                                                                                                                                                                                     |      |

| IP12 | Screen height                  | Tsh    | (SCREEN_HEIGHT)<br>× Tsw              | SCREEN_HEIGHT— screen height in lines<br>with blanking.<br>The SCREEN_HEIGHT is a distance<br>between 2 VSYNCs.<br>The SCREEN_HEIGHT should be built by<br>suitable DI's counter.                                                                                                                                | ns   |

| IP13 | VSYNC width                    | Tvsw   | VSYNC_WIDTH                           | VSYNC_WIDTH—Vsync width in DI_CLK<br>with 0.5 DI_CLK resolution. Defined by DI's<br>counter.                                                                                                                                                                                                                     | ns   |

| IP14 | Vertical blank interval 1      | Tvbi1  | BGYP × Tsw                            | BGYP—width of first Vertical<br>blanking interval in line. The BGYP should<br>be built by suitable DI's counter.                                                                                                                                                                                                 | ns   |

| IP15 | Vertical blank interval 2      | Tvbi2  | (SCREEN_HEIGHT –<br>BGYP – FH) × Tsw  | Width of second vertical blanking interval in line. The FH should be built by suitable DI's counter.                                                                                                                                                                                                             | ns   |

### Table 67. Synchronous Display Interface Timing Characteristics (Pixel Level)

<sup>2</sup> Display interface clock down time

$$\Gamma dicd = \frac{1}{2} \left( T_{diclk} \times ceil \left[ \frac{2 \times DISP_CLK_DOWN}{DI_CLK_PERIOD} \right] \right)$$

<sup>3</sup> Display interface clock up time where CEIL(X) rounds the elements of X to the nearest integers towards infinity.

$$Tdicu = \frac{1}{2} \left( T_{diclk} \times ceil \left[ \frac{2 \times DISP\_CLK\_UP}{DI\_CLK\_PERIOD} \right] \right)$$

# 4.11.11 LVDS Display Bridge (LDB) Module Parameters

The LVDS interface complies with TIA/EIA 644-A standard. For more details, see TIA/EIA STANDARD 644-A, "Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits."

| Parameter                           | Symbol              | Test Condition                                                                                                                                     | Min  | Max   | Units |

|-------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Differential Voltage Output Voltage | V <sub>OD</sub>     | 100 $\Omega$ Differential load                                                                                                                     | 250  | 450   | mV    |

| Output Voltage High                 | Voh                 | 100 $\Omega$ differential load<br>(0 V Diff—Output High Voltage static)                                                                            | 1.25 | 1.6   | mV    |

| Output Voltage Low                  | Vol                 | 100 $\Omega$ differential load<br>(0 V Diff—Output Low Voltage static)                                                                             | 0.9  | 1.25  | mV    |

| Offset Static Voltage               | V <sub>OS</sub>     | Two 49.9 $\Omega$ resistors in series between N-P terminal, with output in either Zero or One state, the voltage measured between the 2 resistors. | 1.15 | 1.375 | V     |

| VOS Differential                    | V <sub>OSDIFF</sub> | Difference in $V_{OS}$ between a One and a Zero state                                                                                              | -50  | 50    | mV    |

| Output short circuited to GND       | ISA ISB             | With the output common shorted to GND                                                                                                              | -24  | 24    | mA    |

| VT Full Load Test                   | VTLoad              | $100\Omega$ Differential load with a 3.74 k $\Omega$ load between GND and I/O supply voltage                                                       | 247  | 454   | mV    |

Table 69. LVDS Display Bridge (LDB) Electrical Specification

### 4.11.12 MIPI D-PHY Timing Parameters

This section describes MIPI D-PHY electrical specifications, compliant with MIPI CSI-2 version 1.0, D-PHY specification Rev. 1.0 (for MIPI sensor port x4 lanes) and MIPI DSI Version 1.01, and D-PHY specification Rev. 1.0 (and also DPI version 2.0, DBI version 2.0, DSC version 1.0a at protocol layer) (for MIPI display port x2 lanes).

### 4.11.12.1 Electrical and Timing Information

| Symbol | Parameters                                                   | Test Conditions                                               | MIN | ТҮР | МАХ  | Unit |

|--------|--------------------------------------------------------------|---------------------------------------------------------------|-----|-----|------|------|

|        | Input DC Specifications - Apply to CLKP/N and DATAP/N inputs |                                                               |     |     |      |      |

| VI     | Input signal voltage range                                   | Transient voltage range is<br>limited from -300 mV to 1600 mV | -50 | _   | 1350 | mV   |

| L <sub>S</sub> | Equivalent wire bond series inductance |    |     | 1.5  | nH |

|----------------|----------------------------------------|----|-----|------|----|

| R <sub>S</sub> | Equivalent wire bond series resistance |    |     | 0.15 | Ω  |

| RL             | Load Resistance                        | 80 | 100 | 125  | Ω  |

#### Table 71. Electrical and Timing Information

# 4.11.12.6 High-Speed Clock Timing

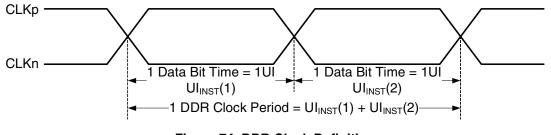

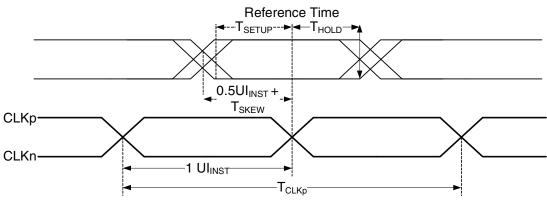

### Figure 74. DDR Clock Definition

### 4.11.12.7 Forward High-Speed Data Transmission Timing

The timing relationship of the DDR Clock differential signal to the Data differential signal is shown in Figure 75:

Figure 75. Data to Clock Timing Definitions

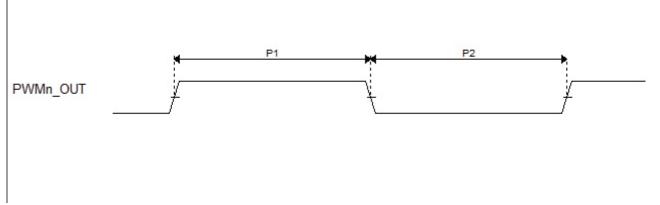

### Figure 86. PWM Timing

### Table 73. PWM Output Timing Parameters

| ID | Parameter                   | Min | Мах     | Unit |

|----|-----------------------------|-----|---------|------|

|    | PWM Module Clock Frequency  | 0   | ipg_clk | MHz  |

| P1 | PWM output pulse width high | 15  |         | ns   |

| P2 | PWM output pulse width low  | 15  |         | ns   |

### 4.11.16 SATA PHY Parameters

This section describes SATA PHY electrical specifications.

### 4.11.16.1 Transmitter and Receiver Characteristics

The SATA PHY meets or exceeds the electrical compliance requirements defined in the SATA specifications.

### NOTE

The tables in the following sections indicate any exceptions to the SATA specification or aspects of the SATA PHY that exceed the standard, as well as provide information about parameters not defined in the standard.

The following subsections provide values obtained from a combination of simulations and silicon characterization.

## 4.11.20.2.3 UART IrDA Mode Timing

The following subsections give the UART transmit and receive timings in IrDA mode.

### **UART IrDA Mode Transmitter**

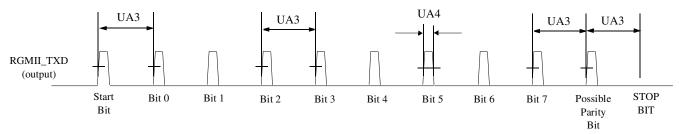

Figure 99 depicts the UART IrDA mode transmit timing, with 8 data bit/1 stop bit format. Table 86 lists the transmit timing characteristics.

Figure 99. UART IrDA Mode Transmit Timing Diagram

### Table 86. IrDA Mode Transmit Timing Parameters

| ID  | Parameter                      | Symbol                | Min                                         | Мах                                             | Unit |

|-----|--------------------------------|-----------------------|---------------------------------------------|-------------------------------------------------|------|

| UA3 | Transmit Bit Time in IrDA mode | t <sub>TIRbit</sub>   | $1/F_{baud_rate}^1 - T_{ref_clk}^2$         | 1/F <sub>baud_rate</sub> + T <sub>ref_clk</sub> | —    |

| UA4 | Transmit IR Pulse Duration     | t <sub>TIRpulse</sub> | $(3/16)^{*}(1/F_{baud_rate}) - T_{ref_clk}$ | $(3/16)^{*}(1/F_{baud_rate}) + T_{ref_clk}$     | —    |

<sup>1</sup>  $F_{baud_rate}$ : Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

<sup>2</sup> T<sub>ref clk</sub>: The period of UART reference clock *ref\_clk* (*ipg\_perclk* after RFDIV divider).

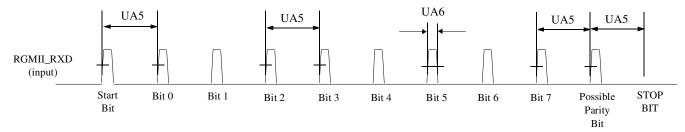

### **UART IrDA Mode Receiver**

Figure 100 depicts the UART IrDA mode receive timing, with 8 data bit/1 stop bit format. Table 87 lists the receive timing characteristics.

Figure 100. UART IrDA Mode Receive Timing Diagram

Table 87. IrDA Mode Receive Timing Parameters

| ID  | Parameter                                  | Symbol                | Min                                        | Мах                                                       | Unit |

|-----|--------------------------------------------|-----------------------|--------------------------------------------|-----------------------------------------------------------|------|

| UA5 | Receive Bit Time <sup>1</sup> in IrDA mode | t <sub>RIRbit</sub>   | $1/F_{baud_rate}^2 - 1/(16*F_{baud_rate})$ | 1/F <sub>baud_rate</sub> + 1/(16*F <sub>baud_rate</sub> ) | —    |

| UA6 | Receive IR Pulse Duration                  | t <sub>RIRpulse</sub> | 1.41 μs                                    | (5/16)*(1/F <sub>baud_rate</sub> )                        | —    |

<sup>1</sup> The UART receiver can tolerate 1/(16\*F<sub>baud\_rate</sub>) tolerance in each bit. But accumulation tolerance in one frame must not exceed 3/(16\*F<sub>baud\_rate</sub>).

<sup>2</sup> F<sub>baud\_rate</sub>: Baud rate frequency. The maximum baud rate the UART can support is (*ipg\_perclk* frequency)/16.

### Package Information and Contact Assignments

| Я            | ٩            | z             | Μ            |              | ¥            | <b>,</b>     |

|--------------|--------------|---------------|--------------|--------------|--------------|--------------|

| GPIO_17      | CSI0_PIXCLK  | CSI0_DAT4     | CSI0_DAT10   | CSI0_DAT13   | HDMI_HPD     | HDMI_REF     |

| GPIO_16      | CSI0_DAT5    | CSI0_VSYNC    | CSI0_DAT12   | GND          | HDMI_DDCCEC  | GND          |

| GPI0_7       | CSI0_DATA_EN | CSI0_DAT7     | CSI0_DAT11   | CSI0_DAT17   | HDMI_D2M     | HDMI_D1M     |

| GPIO_5       | CSI0_MCLK    | CSI0_DAT6     | CSI0_DAT14   | CSI0_DAT16   | HDMI_D2P     | HDMI_D1P     |

| GPIO_8       | GPIO_19      | CSI0_DAT9     | CSI0_DAT15   | GND          | HDMI_D0M     | HDMI_CLKM    |

| GPIO_4       | GPIO_18      | CSI0_DAT8     | CSI0_DAT18   | CSI0_DAT19   | HDMI_D0P     | HDMI_CLKP    |

| GPIO_3       | NVCC_GPIO    | NVCC_CSI      | нал_іман     | HDMI_VP      | NVCC_MIPI    | NVCC_JTAG    |

| GND          | GND          | GND           | GND          | GND          | GND          | GND          |

| VDDARM23_IN  | VDDARM23_IN  | VDDARM23_IN   | VDDARM23_IN  | VDDARM23_IN  | VDDARM23_IN  | VDDHIGH_IN   |

| VDDSOC_CAP   | GND          | GND           | GND          | GND          | GND          | VDDHIGH_CAP  |

| VDDARM23_CAP | VDDARM23_CAP | VDDARM23_CAP  | VDDARM23_CAP | VDDARM23_CAP | VDDARM23_CAP | VDDARM23_CAP |

| GND          | GND          | VDD_CACHE_CAP | GND          | GND          | GND          | GND          |

| VDDARM_CAP   | VDDARM_CAP   | VDDARM_CAP    | VDDARM_CAP   | VDDARM_CAP   | VDDARM_CAP   | VDDARM_CAP   |

| VDDARM_IN    | VDDARM_IN    |               |              | VDDARM_IN    | VDDARM_IN    | VDDARM_IN    |

| GND          | GND          | GND           | GNÐ          | GND          | GND          | GND          |

| VDDSOC_IN    | VDDSOC_IN    |               | VDDSOC_IN    |              |              | VDDSOC_IN    |

| GND          | VDDPU_CAP    | VDDPU_CAP     | VDDPU_CAP    | VDDPU_CAP    | VDDPU_CAP    | VDDPU_CAP    |

| NVCC_DRAM    | GND          | GND           | GND          | GND          | GND          | GND          |

| NVCC_ENET    | NVCC_LCD     | DI0_DISP_CLK  |              | NVCC_EIM1    | NVCC_EIMO    | EIM_D29      |

| DISP0_DAT13  | DISP0_DAT4   |               | EIM_DA11     | EIM_DA0      | EIM_RW       | EIM_D30      |

| DISP0_DAT10  | DISP0_DAT3   | D10_PIN15     | EIM_DA9      | EIM_DA2      | EIM_EBO      | EIM_A23      |

| DISP0_DAT8   | DISP0_DAT1   | EIM_BCLK      | EIM_DA10     | EIM_DA4      | EIM_LBA      | EIM_A18      |

| DISP0_DAT6   | DISP0_DAT2   | EIM_DA14      | EIM_DA13     | EIM_DA5      | EIM_EB1      | EIM_CS1      |

| DISP0_DAT7   | DISP0_DAT0   | EIM_DA15      | EIM_DA12     | EIM_DA8      | EIM_DA3      | EIM_OE       |

| DISP0_DAT5   | DI0_PIN4     | DIO_PIN2      | EIM_WAIT     | EIM_DA7      | EIM_DA6      | EIM_DA1      |

### Table 95. 21 x 21 mm, 0.8 mm Pitch Ball Map (continued)

### **Revision History**

| Rev.<br>Number | Date    | Substantive Change(s)   |

|----------------|---------|-------------------------|

| Rev. 0         | 09/2012 | Initial public release. |

### Table 98. i.MX 6Dual/6Quad Datasheet Document Revision History (continued)

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address: freescale.com/SalesTermsandConditions.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARM Cortex<sup>TM</sup>-A9 is a trademark of ARM Limited.

© 2012 Freescale Semiconductor, Inc. All rights reserved.

Document Number: IMX6DQCEC Rev. 1 11/2012