#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 66MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI                      |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                             |

| Number of I/O              | 48                                                                               |

| Program Memory Size        | 160KB (160K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 12K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 19x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-LQFP Exposed Pad                                                              |

| Supplier Device Package    | PG-LQFP-64-22                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xe162fl20f66laakxuma1 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Summary of Features**

### 1.1 Device Types

The following XE162xL device types are available and can be ordered through Infineon's direct and/or distribution channels.

| Derivative <sup>1)</sup> | Flash<br>Memory <sup>2)</sup> | PSRAM<br>DSRAM <sup>3)</sup> | Capt./Comp.<br>Modules | ADC <sup>4)</sup><br>Chan. | Interfaces <sup>4)</sup>       |

|--------------------------|-------------------------------|------------------------------|------------------------|----------------------------|--------------------------------|

| XE162FL-12FxL            | 96 Kbytes                     | 4 Kbytes<br>6 Kbytes         | CC2<br>CCU60/3         | 19                         | 2 CAN Nodes,<br>4 Serial Chan. |

| XE162HL-12FxL            | 96 Kbytes                     | 4 Kbytes<br>6 Kbytes         | CC2<br>CCU60/3         | 19                         | 4 Serial Chan.                 |

| XE162FL-20FxL            | 160 Kbytes                    | 4 Kbytes<br>6 Kbytes         | CC2<br>CCU60/3         | 19                         | 2 CAN Nodes,<br>4 Serial Chan. |

| XE162HL-20FxL            | 160 Kbytes                    | 4 Kbytes<br>6 Kbytes         | CC2<br>CCU60/3         | 19                         | 4 Serial Chan.                 |

Table 1

Synopsis of XE162xL Device Types

1) x is a placeholder for available speed grade in MHz. Can be 66 or 80.

2) Specific information about the on-chip Flash memory in Table 3.

3) All derivatives additionally provide 2 Kbytes DPRAM.

4) Specific information about the available channels in Table 5.

### **General Device Information**

| Pin | Symphol          |        |      |                                                |

|-----|------------------|--------|------|------------------------------------------------|

| -   | Symbol           | Ctrl.  | Туре | Function                                       |

| 38  | P2.10            | O0 / I | St/B | Bit 10 of Port 2, General Purpose Input/Output |

|     | U0C1_DOUT        | 01     | St/B | USIC0 Channel 1 Shift Data Output              |

| -   | U0C0_SELO<br>3   | 02     | St/B | USIC0 Channel 0 Select/Control 3 Output        |

|     | CC2_CC23         | O3 / I | St/B | CAPCOM2 CC23IO Capture Inp./ Compare Out.      |

|     | U0C1_DX0E        | I      | St/B | USIC0 Channel 1 Shift Data Input               |

|     | CAPINA           | I      | St/B | GPT12E Register CAPREL Capture Input           |

| 39  | P2.11            | O0 / I | St/B | Bit 11 of Port 2, General Purpose Input/Output |

| -   | U0C0_SELO<br>2   | 01     | St/B | USIC0 Channel 0 Select/Control 2 Output        |

|     | U0C1_SELO<br>2   | 02     | St/B | USIC0 Channel 1 Select/Control 2 Output        |

|     | U1C1_DX2A        | I      | St/B | USIC1 Channel 1 Shift Control Input            |

| 40  | P2.12            | O0 / I | St/B | Bit 12 of Port 2, General Purpose Input/Output |

|     | U0C0_SELO<br>4   | 01     | St/B | USIC0 Channel 0 Select/Control 4 Output        |

| -   | U0C1_SELO<br>3   | 02     | St/B | USIC0 Channel 1 Select/Control 3 Output        |

| -   | U1C1_SCLK<br>OUT | O3     | St/B | USIC1 Channel 1 Shift Clock Output             |

|     | U1C1_DX1A        | I      | St/B | USIC1 Channel 1 Shift Clock Input              |

| 41, | P2.13            | O0 / I | St/B | Bit 13 of Port 2, General Purpose Input/Output |

| Ī   | U1C1_DOUT        | O1     | St/B | USIC1 Channel 1 Shift Data Output              |

|     | CCU63_COU<br>T60 | 02     | St/B | CCU63 Channel 0 Output                         |

|     | U1C1_DX0B        | I      | St/B | USIC1 Channel 1 Shift Data Input               |

|     |                  |        | St/B | USIC1 Channel 0 Shift Data Input               |

### **General Device Information**

| PinSymbolCtrl.TypeFunction58P10.1000 / ISt/BBit 10 of Port 10, General Purpose Input/Output100C0_SEL001St/BUSIC0 Channel 0 Select/Control 0 Output6002St/BCCU60 Channel 3 Output16302St/BUSIC1 Channel 0 Shift Data Output100C0_DUT03St/BUSIC0 Channel 0 Shift Control Input100C0_DX2CISt/BUSIC0 Channel 0 Shift Control Input100C1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.1100 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLK01St/BUSIC1 Channel 0 Shift Clock OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock Input7MS_BISt/BUSIC1 Channel 0 Shift Clock Input7MS_BISt/BUSIC1 Channel 0 Shift Clock Input60P10.1200 / ISt/BUSIC1 Channel 0 Shift Data Output61U1C0_DDUT01St/BUSIC1 Channel 0 Shift Data Output61VIC0_DOUT02St/BUSIC1 Channel 0 Shift Data Output61VIC0_DOUT02St/BUSIC0 Channel 0 Shift Data Output6201 / ISt/BUSIC1 Channel 0 Shift Data Output63VIC0_DOUT02St/BUSIC0 Channel 0 Shift Data Output64U1C0_DDUT01St/BDAP1/JTAG Test Data Output65VIC0_AOHSt/BDAP1/JTAG Test Data Output66<                                                                                                                                                                                                                                                                                                                                                               | Table | e 6 Pin De | finitior | ns and | Functions (cont'd)                              |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|----------|--------|-------------------------------------------------|

| U0C0_SELO<br>0O1St/BUSIC0 Channel 0 Select/Control 0 OutputCCU60_COU<br>T63O2St/BCCU60 Channel 3 OutputU1C0_DOUTO3St/BUSIC1 Channel 0 Shift Data OutputU0C0_DX2CISt/BUSIC0 Channel 0 Shift Control InputTDLBISt/BUSIC0 Channel 1 Shift Clock InputU0C1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.11O0/ISt/BUSIC1 Channel 0 Shift Clock OutputU1C0_SCLK<br>OUTO1St/BUSIC1 Channel 0 Shift Clock OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BCAN Node 1 Receive Data Input001O1/1St/BUSIC1 Channel 0 Shift Data Output000_DOUTO2St/BUSIC0 Channel 0 Shift Data Output000_DOUTO2St/BUSIC0 Channel 2 Output60P10.12O0 /ISt/BCCU63 Channel 2 Output61St/BDAP1/JTAG Test Data OutputCCU63_COU762C0ISt/BDAP1/JTAG Test Data Output762I/OHSt/                                                                                                                                                                                                                                                                                                                                                                  | Pin   | Symbol     | Ctrl.    | Туре   | Function                                        |

| 0         CCU60_COU         Q2         St/B         CCU60 Channel 3 Output           T63         VIC0_DOUT         Q3         St/B         USIC1 Channel 0 Shift Data Output           U0C0_DX2C         I         St/B         USIC0 Channel 0 Shift Control Input           TDL_B         I         St/B         USIC0 Channel 0 Shift Control Input           U0C1_DX1A         I         St/B         USIC0 Channel 1 Shift Clock Input           59         P10.11         O0 /I         St/B         USIC1 Channel 0 Shift Clock Output           U1C0_SCLK         O1         St/B         USIC1 Channel 0 Shift Clock Input           BRKOUT         O2         St/B         OCDS Break Signal Output           U1C0_DX1D         I         St/B         USIC1 Channel 0 Shift Clock Input           TMS_B         I         St/B         USIC1 Channel 0 Shift Clock Input           TMS_B         I         St/B         USIC1 Channel 0 Shift Clock Input           TMS_B         I         St/B         CAN Node 1 Receive Data Input           U1C0_DOUT         O1         St/B         USIC1 Channel 0 Shift Data Output           U1C0_DOUT         O2         St/B         USIC0 Channel 2 Output           G0         P10.12         O0 /I         St/B </td <td>58</td> <td>P10.10</td> <td>O0 / I</td> <td>St/B</td> <td>Bit 10 of Port 10, General Purpose Input/Output</td> | 58    | P10.10     | O0 / I   | St/B   | Bit 10 of Port 10, General Purpose Input/Output |

| T63Image: Constraint of the systemU1C0_DOUTO3St/BUSIC1 Channel 0 Shift Data OutputU0C0_DX2CISt/BUSIC0 Channel 0 Shift Control InputTDI_BISt/BJTAG Test Data InputU0C1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.11O0 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLKO1St/BUSIC1 Channel 0 Shift Clock OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock Input0011St/BUSIC1 Channel 0 Shift Data Output0100 / ISt/BUSIC1 Channel 0 Shift Data Output02DOUTO2St/BUSIC0 Channel 0 Shift Data Output00OUSt/BCCU63 Channel 2 Output00CU63_COUO3St/BCCU63 Channel 2 Output100NOHSt/BSPD Input/OutputC0ISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0DISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                        |       | _          | O1       | St/B   | USIC0 Channel 0 Select/Control 0 Output         |

| U0C0_DX2CISt/BUSIC0 Channel 0 Shift Control InputTDI_BISt/BJTAG Test Data InputU0C1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.11O0 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLKO1St/BUSIC1 Channel 0 Shift Clock OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BJTAG Test Mode Selection InputRxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BUSIC1 Channel 0 Shift Data OutputU1C0_DOUTO1St/BUSIC0 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputT62TDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                               |       |            | O2       | St/B   | CCU60 Channel 3 Output                          |

| TDI_BISt/BJTAG Test Data InputU0C1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.11O0 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLK<br>OUTO1St/BUSIC1 Channel 0 Shift Clock OutputU1C0_DX1DO2St/BOCDS Break Signal OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputRxDC1BISt/BUSIC1 Channel 0 Shift Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | U1C0_DOUT  | O3       | St/B   | USIC1 Channel 0 Shift Data Output               |

| UOC1_DX1AISt/BUSIC0 Channel 1 Shift Clock Input59P10.11O0 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLK<br>OUTO1St/BUSIC1 Channel 0 Shift Clock OutputBRKOUTO2St/BOCDS Break Signal OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputRxDC1BISt/BJTAG Test Mode Selection Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU1C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputO0ISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | U0C0_DX2C  | I        | St/B   | USIC0 Channel 0 Shift Control Input             |

| 59P10.11O0 / ISt/BBit 11 of Port 10, General Purpose Input/OutputU1C0_SCLK<br>OUTO1St/BUSIC1 Channel 0 Shift Clock OutputBRKOUTO2St/BOCDS Break Signal OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BUSIC1 Channel 0 Shift Clock InputRxDC1BISt/BJTAG Test Mode Selection Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BUSIC0 Channel 0 Shift Data InputU0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | TDI_B      | I        | St/B   | JTAG Test Data Input                            |

| U1C0_SCLK<br>OUTO1St/BUSIC1 Channel 0 Shift Clock OutputBRKOUTO2St/BOCDS Break Signal OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BJTAG Test Mode Selection InputRxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |       | U0C1_DX1A  | I        | St/B   | USIC0 Channel 1 Shift Clock Input               |

| OUTOUTO2St/BOCDS Break Signal OutputBRKOUTO2St/BOCDS Break Signal OutputU1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BJTAG Test Mode Selection InputRxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 59    | P10.11     | O0 / I   | St/B   | Bit 11 of Port 10, General Purpose Input/Output |

| U1C0_DX1DISt/BUSIC1 Channel 0 Shift Clock InputTMS_BISt/BJTAG Test Mode Selection InputRxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | _          | O1       | St/B   | USIC1 Channel 0 Shift Clock Output              |

| TMS_BISt/BJTAG Test Mode Selection InputRxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BUSIC0 Channel 0 Shift Data InputU0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       | BRKOUT     | O2       | St/B   | OCDS Break Signal Output                        |

| RxDC1BISt/BCAN Node 1 Receive Data Input60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputCOISt/BSPD Input/OutputC0ISt/BUSIC0 Channel 0 Shift Data InputU0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | U1C0_DX1D  | I        | St/B   | USIC1 Channel 0 Shift Clock Input               |

| 60P10.12O0 / ISt/BBit 12 of Port 10, General Purpose Input/OutputU1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputT62TDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       | TMS_B      | I        | St/B   | JTAG Test Mode Selection Input                  |

| U1C0_DOUTO1St/BUSIC1 Channel 0 Shift Data OutputU0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputT62TDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | RxDC1B     | I        | St/B   | CAN Node 1 Receive Data Input                   |

| U0C0_DOUTO2St/BUSIC0 Channel 0 Shift Data OutputCCU63_COUO3St/BCCU63 Channel 2 OutputT62TDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 60    | P10.12     | O0 / I   | St/B   | Bit 12 of Port 10, General Purpose Input/Output |

| CCU63_COU<br>T62O3St/BCCU63 Channel 2 OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | U1C0_DOUT  | 01       | St/B   | USIC1 Channel 0 Shift Data Output               |

| T62DAP1/JTAG Test Data OutputTDO_AOHSt/BDAP1/JTAG Test Data OutputSPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | U0C0_DOUT  | 02       | St/B   | USIC0 Channel 0 Shift Data Output               |

| SPD_0I/OHSt/BSPD Input/OutputC0ISt/BConfiguration Pin 0U0C0_DX0DISt/BUSIC0 Channel 0 Shift Data InputU1C0_DX0CISt/BUSIC1 Channel 0 Shift Data InputU1C0_DX1EISt/BUSIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | _          | O3       | St/B   | CCU63 Channel 2 Output                          |

| C0       I       St/B       Configuration Pin 0         U0C0_DX0D       I       St/B       USIC0 Channel 0 Shift Data Input         U1C0_DX0C       I       St/B       USIC1 Channel 0 Shift Data Input         U1C0_DX1E       I       St/B       USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | TDO_A      | ОН       | St/B   | DAP1/JTAG Test Data Output                      |

| U0C0_DX0D       I       St/B       USIC0 Channel 0 Shift Data Input         U1C0_DX0C       I       St/B       USIC1 Channel 0 Shift Data Input         U1C0_DX1E       I       St/B       USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | SPD_0      | I/OH     | St/B   | SPD Input/Output                                |

| U1C0_DX0C     I     St/B     USIC1 Channel 0 Shift Data Input       U1C0_DX1E     I     St/B     USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | C0         | I        | St/B   | Configuration Pin 0                             |

| U1C0_DX1E I St/B USIC1 Channel 0 Shift Clock Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | U0C0_DX0D  | I        | St/B   | USIC0 Channel 0 Shift Data Input                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | U1C0_DX0C  | I        | St/B   | USIC1 Channel 0 Shift Data Input                |

| 61         XTAL2         O         Sp/M         Crystal Oscillator Amplifier Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       | U1C0_DX1E  | I        | St/B   | USIC1 Channel 0 Shift Clock Input               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 61    | XTAL2      | 0        | Sp/M   | Crystal Oscillator Amplifier Output             |

#### **General Device Information**

| Pin                    | Symbol            | Ctrl. | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

|------------------------|-------------------|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 8,<br>28,<br>42,<br>56 | V <sub>DDPB</sub> | -     | PS/B | <b>Digital Pad Supply Voltage for Domain B</b><br>Connect decoupling capacitors to adjacent $V_{\text{DDP}}/V_{\text{SS}}$ pin pairs as close as possible to the pin                                                                                                                                                                                                                                   |  |  |  |  |

| 1, 33                  | V <sub>SS</sub>   | -     | PS/  | <b>Digital Ground</b><br>All $V_{SS}$ pins must be connected to the ground-line<br>or ground-plane.<br>Note: Also the exposed pad is connected<br>internally to $V_{SS}$ . To improve the EMC<br>behaviour, it is recommended to connect the<br>exposed pad to the board ground.<br>For thermal aspects, please refer to the<br>Data Sheet. Board layout examples are<br>given in an application note. |  |  |  |  |

# Table 6 Pin Definitions and Functions (cont'd)

# 3.5 Interrupt System

The architecture of the XE162xL supports several mechanisms for fast and flexible response to service requests; these can be generated from various sources internal or external to the microcontroller. Any of these interrupt requests can be programmed to be serviced by the Interrupt Controller or by the Peripheral Event Controller (PEC).

Using a standard interrupt service the current program execution is suspended and a branch to the interrupt vector table is performed. With the PEC just one cycle is 'stolen' from the current CPU activity to perform the PEC service. A PEC service implies a single byte or word data transfer between any two memory locations with an additional increment of either the PEC source pointer, the destination pointer, or both. An individual PEC transfer counter is implicitly decremented for each PEC service except when performing in the continuous transfer mode. When this counter reaches zero, a standard interrupt is performed to the corresponding source-related vector location. PEC services are particularly well suited to supporting the transmission or reception of blocks of data. The XE162xL has eight PEC channels, each with fast interrupt-driven data transfer capabilities.

With a minimum interrupt response time of 7/11<sup>1)</sup> CPU clocks, the XE162xL can react quickly to the occurrence of non-deterministic events.

### Interrupt Nodes and Source Selection

The interrupt system provides 64 physical nodes with separate control register containing an interrupt request flag, an interrupt enable flag and an interrupt priority bit field. Most interrupt sources are assigned to a dedicated node. A particular subset of interrupt sources shares a set of nodes. The source selection can be programmed using the interrupt source selection (ISSR) registers.

### External Request Unit (ERU)

A dedicated External Request Unit (ERU) is provided to route and preprocess selected on-chip peripheral and external interrupt requests. The ERU features 4 programmable input channels with event trigger logic (ETL) a routing matrix and 4 output gating units (OGU). The ETL features rising edge, falling edge, or both edges event detection. The OGU combines the detected interrupt events and provides filtering capabilities depending on a programmable pattern match or miss.

### Trap Processing

The XE162xL provides efficient mechanisms to identify and process exceptions or error conditions that arise during run-time, the so-called 'Hardware Traps'. A hardware trap causes an immediate system reaction similar to a standard interrupt service (branching

<sup>1)</sup> Depending if the jump cache is used or not.

# 3.8 Capture/Compare Units CCU6x

The XE162xL types feature the CCU60 and CCU63 units.

CCU6 is a high-resolution capture and compare unit with application-specific modes. It provides inputs to start the timers synchronously, an important feature in devices with several CCU6 modules.

The module provides two independent timers (T12, T13), that can be used for PWM generation, especially for AC motor control. Additionally, special control modes for block commutation and multi-phase machines are supported.

### Timer 12 Features

- Three capture/compare channels, where each channel can be used either as a capture or as a compare channel.

- Supports generation of a three-phase PWM (six outputs, individual signals for highside and low-side switches)

- 16-bit resolution, maximum count frequency = peripheral clock

- Dead-time control for each channel to avoid short circuits in the power stage

- Concurrent update of the required T12/13 registers

- Center-aligned and edge-aligned PWM can be generated

- Single-shot mode supported

- Many interrupt request sources

- Hysteresis-like control mode

- Automatic start on a HW event (T12HR, for synchronization purposes)

### **Timer 13 Features**

- One independent compare channel with one output

- 16-bit resolution, maximum count frequency = peripheral clock

- Can be synchronized to T12

- · Interrupt generation at period match and compare match

- Single-shot mode supported

- Automatic start on a HW event (T13HR, for synchronization purposes)

### Additional Features

- Block commutation for brushless DC drives implemented

- Position detection via Hall sensor pattern

- Automatic rotational speed measurement for block commutation

- Integrated error handling

- Fast emergency stop without CPU load via external signal (CTRAP)

- Control modes for multi-channel AC drives

- Output levels can be selected and adapted to the power stage

The RTC module can be used for different purposes:

- System clock to determine the current time and date

- Cyclic time-based interrupt, to provide a system time tick independent of CPU frequency and other resources

- 48-bit timer for long-term measurements

- Alarm interrupt at a defined time

# 3.11 A/D Converters

For analog signal measurement, a 12-bit A/D converters (ADC0) with 19 multiplexed input channels and a sample and hold circuit have been integrated on-chip. Conversions use the successive approximation method. The sample time (to charge the capacitors) and the conversion time are programmable so that they can be adjusted to the external circuit. The A/D converters can also operate in 8-bit and 10-bit conversion mode, further reducing the conversion time.

Several independent conversion result registers, selectable interrupt requests, and highly flexible conversion sequences provide a high degree of programmability to meet the application requirements.

For applications that require more analog input channels, external analog multiplexers can be controlled automatically. For applications that require fewer analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converters of the XE162xL support two types of request sources which can be triggered by several internal and external events.

- Parallel requests are activated at the same time and then executed in a predefined sequence.

- Queued requests are executed in a user-defined sequence.

In addition, the conversion of a specific channel can be inserted into a running sequence without disturbing that sequence. All requests are arbitrated according to the priority level assigned to them.

Data reduction features reduce the number of required CPU access operations allowing the precise evaluation of analog inputs (high conversion rate) even at a low CPU speed. Result data can be reduced by limit checking or accumulation of results. Two cascadable filters build the hardware to generate a configurable moving average.

The Peripheral Event Controller (PEC) can be used to control the A/D converters or to automatically store conversion results to a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer. Each A/D converter contains eight result registers which can be concatenated to build a result FIFO. Wait-for-read mode can be enabled for each result register to prevent the loss of conversion data.

In order to decouple analog inputs from digital noise and to avoid input trigger noise, those pins used for analog input can be disconnected from the digital input stages. This can be selected for each pin separately with the Port x Digital Input Disable registers.

The Auto-Power-Down feature of the A/D converters minimizes the power consumption when no conversion is in progress.

Broken wire detection for each channel and a multiplexer test mode provide information to verify the proper operation of the analog signal sources (e.g. a sensor system).

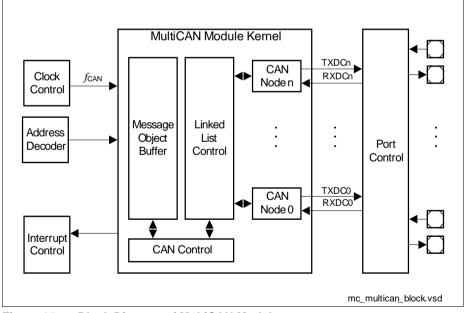

### 3.13 MultiCAN Module

The MultiCAN module contains two independently operating CAN nodes with Full-CAN functionality which are able to exchange Data and Remote Frames using a gateway function. Transmission and reception of CAN frames is handled in accordance with CAN specification V2.0 B (active). Each CAN node can receive and transmit standard frames with 11-bit identifiers as well as extended frames with 29-bit identifiers.

The two CAN nodes share a common set of message objects. Each message object can be individually allocated to either of the CAN nodes. Besides serving as a storage container for incoming and outgoing frames, message objects can be combined to build gateways between the CAN nodes or to set up a FIFO buffer.

The message objects are organized in double-chained linked lists, where each CAN node has its own list of message objects. A CAN node stores frames only into message objects that are allocated to its own message object list and it transmits only messages belonging to this message object list. A powerful, command-driven list controller performs all message object list operations.

Figure 11 Block Diagram of MultiCAN Module

### **MultiCAN Features**

- CAN functionality conforming to CAN specification V2.0 B active for each CAN node (compliant to ISO 11898)

- Independent CAN nodes

- Set of independent message objects (shared by the CAN nodes)

- Dedicated control registers for each CAN node

- Data transfer rate up to 1 Mbit/s, individually programmable for each node

- · Flexible and powerful message transfer control and error handling capabilities

- Full-CAN functionality for message objects:

- Can be assigned to one of the CAN nodes

- Configurable as transmit or receive objects, or as message buffer FIFO

- Handle 11-bit or 29-bit identifiers with programmable acceptance mask for filtering

- Remote Monitoring Mode, and frame counter for monitoring

- Automatic Gateway Mode support

- 16 individually programmable interrupt nodes

- Analyzer mode for CAN bus monitoring

### 3.14 System Timer

The System Timer consists of a programmable prescaler and two concatenated timers (10 bits and 6 bits). Both timers can generate interrupt requests. The clock source can be selected and the timers can also run during power reduction modes.

Therefore, the System Timer enables the software to maintain the current time for scheduling functions or for the implementation of a clock.

### 3.15 Window Watchdog Timer

The Window Watchdog Timer is one of the fail-safe mechanisms which have been implemented to prevent the controller from malfunctioning for longer periods of time.

The Window Watchdog Timer is always enabled after an application reset of the chip. It can be disabled and enabled at any time by executing the instructions DISWDT and ENWDT respectively. The software has to service the Window Watchdog Timer before it overflows. If this is not the case because of a hardware or software failure, the Window Watchdog Timer overflows, generating a reset request.

The Window Watchdog Timer has a 'programmable window boundary', it disallows refresh during the Window Watchdog Timer's count-up. A refresh during this window-boundary will cause the Window Watchdog Timer to also generate a reset request.

The Window Watchdog Timer is a 16-bit timer clocked with either the system clock or the independent wake-up oscillator clock, divided by 16,384 or 256. The Window Watchdog Timer register is set to a prespecified reload value (stored in WDTREL) in order to allow further variation of the monitored time interval. Each time it is serviced by the application software, the Window Watchdog Timer is reloaded.

When clocked by  $f_{\rm SYS}$  = 80 MHz, time intervals between 12.5 ns and 13.4 s can be monitored.

When clocked by  $f_{\rm WU}$  = 500 kHz, time intervals between 2.0 µs and 2147.5 s can be monitored.

The default Watchdog Timer interval after power-up is 0.13 s (@  $f_{WII}$  = 500 kHz).

### 3.16 Clock Generation

The Clock Generation Unit can generate the system clock signal  $f_{SYS}$  for the XE162xL from a number of external or internal clock sources:

- External clock signals with pad voltage or core voltage levels

- External crystal or resonator using the on-chip oscillator

- On-chip clock source for operation without crystal/resonator

- Wake-up clock (ultra-low-power) to further reduce power consumption

The programmable on-chip PLL with multiple prescalers generates a clock signal for maximum system performance from standard crystals, a clock input signal, or from the on-chip clock source. See also **Section 4.7.2**.

The Oscillator Watchdog (OWD) generates an interrupt if the crystal oscillator frequency falls below a certain limit or stops completely. In this case, the system can be supplied with an emergency clock to enable operation even after an external clock failure.

All available clock signals can be output on the EXTCLK pin.

# 4 Electrical Parameters

The operating range for the XE162xL is defined by its electrical parameters. For proper operation the specified limits must be respected when integrating the device in its target environment.

### 4.1 General Parameters

These parameters are valid for all subsequent descriptions, unless otherwise noted.

| Parameter                                                       | Symbol                  | Values |      |                        | Unit | Note /                             |

|-----------------------------------------------------------------|-------------------------|--------|------|------------------------|------|------------------------------------|

|                                                                 |                         | Min.   | Тур. | Max.                   |      | Test Condition                     |

| Output current on a pin when high value is driven               | I <sub>OH</sub> SR      | -15    | -    | -                      | mA   |                                    |

| Output current on a pin when low value is driven                | I <sub>OL</sub> SR      | -      | -    | 15                     | mA   |                                    |

| Overload current                                                | $I_{\rm OV}{\rm SR}$    | -5     | _    | 5                      | mA   | 1)                                 |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -      | -    | 50                     | mA   | 1)                                 |

| Junction Temperature                                            | $T_{\sf J}{\sf SR}$     | -40    | -    | 150                    | °C   |                                    |

| Storage Temperature                                             | $T_{\rm ST}{ m SR}$     | -65    | _    | 150                    | °C   |                                    |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | -0.5   | -    | 6.0                    | V    |                                    |

| Voltage on any pin with respect to ground (Vss)                 | $V_{\rm IN}{\rm SR}$    | -0.5   | -    | V <sub>DDP</sub> + 0.5 | V    | $V_{\rm IN} \leq V_{\rm DDP(max)}$ |

Table 12

Absolute Maximum Rating Parameters

Overload condition occurs if the input voltage V<sub>IN</sub> is out of the absolute maximum rating range. In this case the current must be limited to the listed values by design measures.

Note: Stresses above the values listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for an extended time may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DDP}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DDP}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

### Table 13 Operating Conditions (cont'd)

| Parameter                                                       | Symbol                  |      | Values                    | 5                         | Unit | Note /                                                              |

|-----------------------------------------------------------------|-------------------------|------|---------------------------|---------------------------|------|---------------------------------------------------------------------|

|                                                                 |                         | Min. | Тур.                      | Max.                      |      | Test Condition                                                      |

| Overload current coupling factor for digital I/O pins           | K <sub>OVD</sub><br>CC  | -    | 1.0 x<br>10 <sup>-2</sup> | 3.0 x<br>10 <sup>-2</sup> |      | <i>I</i> <sub>OV</sub> < 0 mA; not<br>subject to<br>production test |

|                                                                 |                         | -    | 1.0 x<br>10 <sup>-4</sup> | 5.0 x<br>10 <sup>-3</sup> |      | $I_{\rm OV}$ > 0 mA; not<br>subject to<br>production test           |

| Absolute sum of overload currents                               | $\Sigma  I_{OV} $<br>SR | -    | -                         | 30                        | mA   | not subject to production test                                      |

| Digital core supply voltage for domain M <sup>8)</sup>          | $V_{ m DDIM}$ CC        | -    | 1.5                       | -                         | V    |                                                                     |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$    | 3.0  | -                         | 5.5                       | V    |                                                                     |

| Digital ground voltage                                          | $V_{\rm SS}{\rm SR}$    | -    | 0                         | -                         | V    |                                                                     |

To ensure the stability of the voltage regulators the EVRs must be buffered with ceramic capacitors. Separate buffer capacitors with the recomended values shall be connected as close as possible to each V<sub>DDIM</sub> pin to keep the resistance of the board tracks below 2 Ohm. Connect all V<sub>DDIM</sub> pins together. The minimum capacitance value is required for proper operation under all conditions (e.g. temperature). Higher values slightly increase the startup time.

- 2) Use one Capacitor for each pin.

- This is the reference load. For bigger capacitive loads, use the derating factors listed in the PAD properties section.

- 4) The timing is valid for pin drivers operating in default current mode (selected after reset). Reducing the output current may lead to increased delays or reduced driving capability (C<sub>1</sub>).

- 5) The operating frequency range may be reduced for specific device types. This is indicated in the device designation (...FxxL). 66 MHz devices are marked ...F66L.

- 6) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range: V<sub>OV</sub> > V<sub>IHmax</sub> (I<sub>OV</sub> > 0) or V<sub>OV</sub> < V<sub>ILmin</sub> ((I<sub>OV</sub> < 0). The absolute sum of input overload currents on all pins may not exceed 50 mA. The supply voltages must remain within the specified limits. Proper operation under overload conditions depends on the application. Overload conditions must not occur on pin XTAL1.</p>

- 7) An overload current ( $I_{OV}$ ) through a pin injects a certain error current ( $I_{INJ}$ ) into the adjacent pins. This error current adds to the respective pins leakage current ( $I_{OZ}$ ). The amount of error current depends on the overload current and is defined by the overload coupling factor  $K_{OV}$ . The polarity of the injected error current is inverse compared to the polarity of the overload current that produces it. The total current through a pin is  $|I_{TOT}| = |I_{OZ}|$

- + ( $|I_{OV}|$  K<sub>OV</sub>). The additional error current may distort the input voltage on analog inputs.

8) Value is controlled by on-chip regulator.

### 4.2 Voltage Range definitions

The XE162xL timing depends on the supply voltage. If such a dependency exists the timing values are given for 2 voltage areas commonly used. The voltage areas are defined in the following tables.

#### Table 14Upper Voltage Range Definition

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|----------------|

|                                                                 |                      | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 4.5  | 5.0    | 5.5  | V    |                |

### Table 15 Lower Voltage Range Definition

| Parameter                                                       | Symbol               |      | Values |      | Unit | Note /         |

|-----------------------------------------------------------------|----------------------|------|--------|------|------|----------------|

|                                                                 |                      | Min. | Тур.   | Max. |      | Test Condition |

| Digital supply voltage for<br>IO pads and voltage<br>regulators | $V_{\rm DDP}{ m SR}$ | 3.0  | 3.3    | 4.5  | V    |                |

### 4.2.1 Parameter Interpretation

The parameters listed in the following include both the characteristics of the XE162xL and its demands on the system. To aid in correctly interpreting the parameters when evaluating them for a design, they are marked accordingly in the column "Symbol":

CC (Controller Characteristics):

The logic of the XE162xL provides signals with the specified characteristics.

### SR (System Requirement):

The external system must provide signals with the specified characteristics to the XE162xL.

- 2) This parameter includes the sample time (also the additional sample time specified by STC), the time to determine the digital result and the time to load the result register with the conversion result. Values for the basic clock t<sub>ADCI</sub> depend on programming.

- The broken wire detection delay against V<sub>AGND</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 500 μs. Result below 10% (66<sub>H</sub>)

- 4) The broken wire detection delay against V<sub>AREF</sub> is measured in numbers of consecutive precharge cycles at a conversion rate of not more than 10 μs. This function is influenced by leakage current, in particular at high temperature. Result above 80% (332<sub>µ</sub>)

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

| Parameter                                               | Symbol                     |      | Values | 5    | Unit     | Note /<br>Test Condition                   |

|---------------------------------------------------------|----------------------------|------|--------|------|----------|--------------------------------------------|

|                                                         |                            | Min. | Тур.   | Max. |          |                                            |

| Input resistance of the selected analog channel         | R <sub>AIN</sub> CC        | -    | 0.9    | 1.5  | kOh<br>m | not subject to<br>production test          |

| Input resistance of the reference input                 | R <sub>AREF</sub><br>CC    | -    | 0.5    | 1    | kOh<br>m | not subject to<br>production test          |

| Differential Non-Linearity<br>Error <sup>2)3)4)5)</sup> | EA <sub>DNL</sub>  <br>CC  | -    | 2.5    | 5.0  | LSB      |                                            |

| Gain Error <sup>2)3)4)5)</sup>                          | EA <sub>GAIN</sub>  <br>CC | -    | 2.5    | 6.0  | LSB      |                                            |

| Integral Non-<br>Linearity <sup>2)3)4)5)</sup>          | EA <sub>INL</sub>  <br>CC  | -    | 2.0    | 4.0  | LSB      |                                            |

| Offset Error <sup>2)3)4)5)</sup>                        | EA <sub>OFF</sub>  <br>CC  | -    | 2.0    | 4.0  | LSB      |                                            |

| Analog clock frequency                                  | $f_{\rm ADCI}{\rm SR}$     | 2    | -      | 20   | MHz      | Std. reference input ( $V_{\text{AREF}}$ ) |

|                                                         |                            | 2    | -      | 17.5 | MHz      | Alt. reference<br>input (CH0)              |

| Total Unadjusted Error <sup>3)4)</sup>                  | TUE <br>CC                 | -    | 2.5    | 5.5  | LSB      | 6)7)                                       |

| Wakeup time from analog powerdown, fast mode            | t <sub>WAF</sub> CC        | -    | -      | 7.0  | μS       |                                            |

| Wakeup time from analog powerdown, slow mode            | t <sub>WAS</sub> CC        | _    | -      | 11.5 | μS       |                                            |

### Table 21 ADC Parameters for Upper Voltage Range

# 4.7.3 External Clock Input Parameters

These parameters specify the external clock generation for the XE162xL. The clock can be generated in two ways:

- By connecting a crystal or ceramic resonator to pins XTAL1/XTAL2.

- By supplying an **external clock signal**. This clock signal can be supplied either to pin XTAL1 (core voltage domain) or to pin CLKIN1 (IO voltage domain).

If connected to CLKIN1, the input signal must reach the defined input levels  $V_{\rm IL}$  and  $V_{\rm IH}$ . If connected to XTAL1, a minimum amplitude  $V_{\rm AX1}$  (peak-to-peak voltage) is sufficient for the operation of the on-chip oscillator.

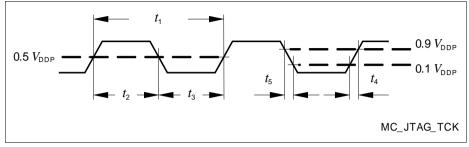

Note: The given clock timing parameters  $(t_1 \dots t_4)$  are only valid for an external clock input signal.

Note: Operating Conditions apply.

| Parameter                                      | Symbol                  |                                    | Values | 5    | Unit | Note /                                                                      |

|------------------------------------------------|-------------------------|------------------------------------|--------|------|------|-----------------------------------------------------------------------------|

|                                                |                         | Min.                               | Тур.   | Max. |      | Test Condition                                                              |

| Oscillator frequency                           | $f_{\rm OSC}{\rm SR}$   | 4                                  | _      | 40   | MHz  | Input= Clock<br>Signal                                                      |

|                                                |                         | 4                                  | _      | 16   | MHz  | Input= Crystal<br>or Resonator                                              |

| XTAL1 input current absolute value             | I <sub>IL</sub>   CC    | -                                  | _      | 20   | μA   |                                                                             |

| Input clock high time                          | t <sub>1</sub> SR       | 6                                  | -      | _    | ns   |                                                                             |

| Input clock low time                           | t <sub>2</sub> SR       | 6                                  | -      | _    | ns   |                                                                             |

| Input clock rise time                          | t <sub>3</sub> SR       | _                                  | 8      | 8    | ns   |                                                                             |

| Input clock fall time                          | t <sub>4</sub> SR       | -                                  | 8      | 8    | ns   |                                                                             |

| Input voltage amplitude on XTAL1 <sup>1)</sup> | $V_{\rm AX1}  {\rm SR}$ | $0.3 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | $f_{OSC} \ge 4 \text{ MHz};$<br>$f_{OSC} \le 16 \text{ MHz}$                |

|                                                |                         | $0.4 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | $f_{\text{OSC}} \ge$ 16 MHz;<br>$f_{\text{OSC}} \le$ 25 MHz                 |

|                                                |                         | $0.5 	ext{ x}$<br>$V_{	ext{DDIM}}$ | -      | -    | V    | $f_{\text{OSC}} \ge 25 \text{ MHz};$<br>$f_{\text{OSC}} \le 40 \text{ MHz}$ |

| Input voltage range limits for signal on XTAL1 | $V_{\rm IX1}$ SR        | -1.7 +<br>V <sub>DDIM</sub>        | -      | 1.7  | V    | 2)                                                                          |

Table 29

External Clock Input Characteristics

The amplitude voltage V<sub>AX1</sub> refers to the offset voltage V<sub>OFF</sub>. This offset voltage must be stable during the operation and the resulting voltage peaks must remain within the limits defined by V<sub>IX1</sub>.

#### **Electrical Parameters**

| Table 31 | Standard Pad Parameters for Lower Voltage Range (cont'd) |

|----------|----------------------------------------------------------|

|----------|----------------------------------------------------------|

| Parameter                                         | Symbol                  | Values |      |                                   | Unit | Note /                                                                                                            |

|---------------------------------------------------|-------------------------|--------|------|-----------------------------------|------|-------------------------------------------------------------------------------------------------------------------|

|                                                   |                         | Min.   | Тур. | Max.                              |      | Test Condition                                                                                                    |

| Nominal output driver<br>current (absolute value) | I <sub>Onom</sub><br>CC | -      | -    | 0.8                               | mA   | Driver_Strength<br>= Medium                                                                                       |