Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                       |

|----------------------------|-----------------------------------------------------------------------|

| Product Status             | Obsolete                                                              |

| Core Processor             | XA                                                                    |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 30MHz                                                                 |

| Connectivity               | EBI/EMI, I²C, UART/USART                                              |

| Peripherals                | PWM, WDT                                                              |

| Number of I/O              | 32                                                                    |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | ROMIess                                                               |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 1K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 5.5V                                                           |

| Data Converters            | A/D 8x8b                                                              |

| Oscillator Type            | External                                                              |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 68-LCC (J-Lead)                                                       |

| Supplier Device Package    | 68-PLCC (24.18x24.18)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/pxas30kfa-512 |

|                            |                                                                       |

XA-S3

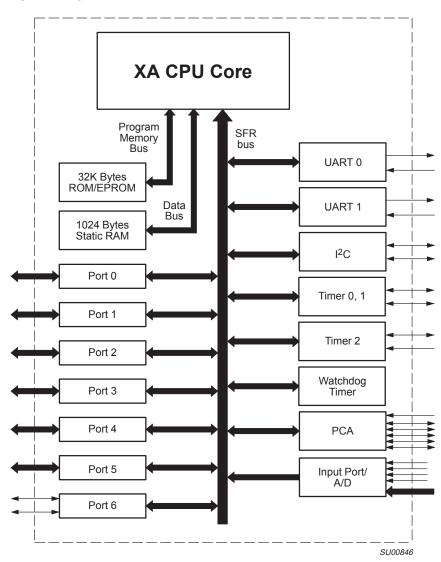

## **BLOCK DIAGRAM**

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V),  $I^2C$ , 2 UARTs, 16 MB address range

XA-S3

## **PIN DESCRIPTIONS**

| MUEMONIO                | PIN NU                     | IMBER                        | TVDE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------|----------------------------|------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MNEMONIC                | PLCC                       | LQFP                         | TYPE | NAME AND FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| V <sub>SS</sub>         | 1, 20, 55                  | 12, 13,<br>53, 54,<br>69, 70 | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| $V_{DD}$                | 2, 21, 54                  | 14, 15,<br>51, 52,<br>71, 72 | Ι    | Power Supply: This is the power supply voltage for normal, idle, and power down operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

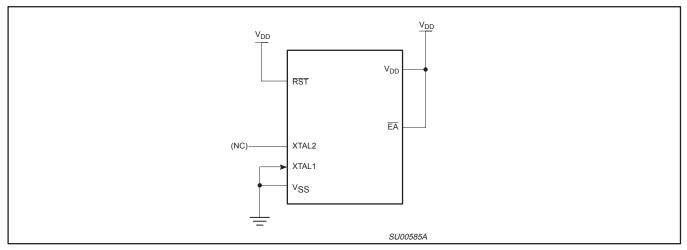

| RST                     | 50                         | 47                           | _    | <b>Reset:</b> A low on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor to begin execution at the address contained in the reset vector.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| RSTOUT                  | 19                         | 11                           | 0    | <b>Reset Output:</b> This pin outputs a low whenever the XA-S3 processor is reset for any reason. This includes an external reset via the RST pin, watchdog reset, and the RESET instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| ALE/PROG                | 47                         | 44                           | I/O  | Address Latch Enable/Program Pulse: A high output on the ALE pin signals external circuitry to latch the address portion of the multiplexed address/data bus. A pulse on ALE occurs only when it is needed in order to process a bus cycle.                                                                                                                                                                                                                                                                                                                                                                                                    |

| PSEN                    | 48                         | 45                           | 0    | <b>Program Store Enable:</b> The read strobe for external program memory. When the microcontroller accesses external program memory, PSEN is driven low in order to enable memory devices. PSEN is only active when external code accesses are performed.                                                                                                                                                                                                                                                                                                                                                                                      |

| EA/WAIT/V <sub>PP</sub> | 22                         | 16                           | 1    | External Access/Bus Wait: The EA input determines whether the internal program memory of the microcontroller is used for code execution. The value on the EA pin is latched as the external reset input is released and applies during later execution. When latched as a 0, external program memory is used exclusively. When latched as a 1, internal program memory will be used up to its limit, and external program memory used above that point. After reset is released, this pin takes on the function of bus WAIT input. If WAIT is asserted high during an external bus access, that cycle will be extended until WAIT is released. |

| XTAL1                   | 68                         | 68                           | I    | Crystal 1: Input to the inverting amplifier used in the oscillator circuit and input to the internal clock generator circuits.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| XTAL2                   | 67                         | 67                           | I    | Crystal 2: Output from the oscillator amplifier.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| CLKOUT                  | 49                         | 46                           | 0    | Clock Output: This pin outputs a buffered version of the internal CPU clock. The clock output may be used in conjunction with the external bus to synchronize WAIT state generators, etc. The clock output may be disabled by software.                                                                                                                                                                                                                                                                                                                                                                                                        |

| $AV_DD$                 | 33                         | 28, 29                       | I    | Analog Power Supply: Positive power supply input for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| AV <sub>SS</sub>        | 34                         | 30, 31                       | Ι    | Analog Ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AV <sub>REF+</sub>      | 32                         | 27                           | _    | A/D Positive Reference Voltage: High end reference for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| AV <sub>REF</sub> _     | 31                         | 26                           | Ι    | A/D Negative Reference Voltage: Low end reference for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.0 – P0.7             | 45, 46,<br>51–53,<br>56–58 | 42, 43,<br>48–50,<br>55–57   | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. Port 0 latches have 1s written to them and are configured in the quasi-bidirectional mode during reset. The operation of port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to the section on I/O port configuration and the DC Electrical Characteristics for details.                                                                                                                                                                                                         |

|                         |                            |                              |      | When the external program/data bus is used, Port 0 becomes the multiplexed low data/instruction byte and address lines 4 through 11.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V-5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

|                  | Bit Addressable |           | MSB                       |        |       |       |       |       |        |

|------------------|-----------------|-----------|---------------------------|--------|-------|-------|-------|-------|--------|

| Reset Value: 00h |                 |           | ADCS6                     | ADCS5  | ADCS4 | ADCS3 | ADCS2 | ADCS1 | ADCS0  |

| BIT              | SYMBOL          | FUNCTIO   | N                         |        |       |       |       |       |        |

| ADCS.7           | ADCS7           | A/D chann | el 7 selec                | t bit. |       |       |       |       |        |

| ADCS.6           | ADCS6           | A/D chann | el 6 selec                | t bit. |       |       |       |       |        |

| ADCS.5           | ADCS5           | A/D chann | el 5 selec                | t bit. |       |       |       |       |        |

| ADCS.4           | ADCS4           | A/D chann | A/D channel 4 select bit. |        |       |       |       |       |        |

| ADCS.3           | ADCS3           | A/D chann | el 3 selec                | t bit. |       |       |       |       |        |

| ADCS.2           | ADCS2           | A/D chann | A/D channel 2 select bit. |        |       |       |       |       |        |

| ADCS.1           | ADCS1           | A/D chann | A/D channel 1 select bit. |        |       |       |       |       |        |

| ADCS.0           | ADCS0           | A/D chann | el 0 selec                | t bit. |       |       |       |       | SU0093 |

Figure 2. A/D Channel Select Register (ADCS)

| ADCFG Address:4B9h Not bit Addressable Reset Value: 00h |        | MSB LSB                                                           |                          |  |  |  |  |

|---------------------------------------------------------|--------|-------------------------------------------------------------------|--------------------------|--|--|--|--|

|                                                         |        |                                                                   | A/D Timing Configuration |  |  |  |  |

| ВІТ                                                     | SYMBOL | FUNCTION                                                          |                          |  |  |  |  |

| ADCFG.7                                                 | _      | Reserved for future use. Should not be set to 1                   | by user programs.        |  |  |  |  |

| ADCFG.6                                                 | _      | Reserved for future use. Should not be set to 1                   | by user programs.        |  |  |  |  |

| ADCFG.5                                                 | _      | Reserved for future use. Should not be set to 1                   | by user programs.        |  |  |  |  |

| ADCFG.4                                                 | _      | Reserved for future use. Should not be set to 1 by user programs. |                          |  |  |  |  |

| ADCFG.3-0                                               | ADCFG  | A/D timing configuration (see text and table).                    |                          |  |  |  |  |

|                                                         |        | ,                                                                 | SU00940                  |  |  |  |  |

Figure 3. A/D Timing Configuration Register (ADCFG)

## Table 2. A/D Timing Configuration

| ADOFO 2 A              | Max. Oscillator | Conv        | ersion Time               | Sampling Time |  |

|------------------------|-----------------|-------------|---------------------------|---------------|--|

| ADCFG.3-0              | Frequency (MHz) | Osc. Clocks | μ <b>sec at max. Osc.</b> | (Osc. Clocks) |  |

| 0h (0000)              | 6.66            | 72          | 10.81                     | 4             |  |

| 1h (0001)              | 10              | 76          | 7.6                       | 6             |  |

| 2h (0010)              | 11.11           | 80          | 7.2                       | 8             |  |

| 3h (0011)              | 13.33           | 96          | 7.2                       | 8             |  |

| 4h (0100)              | 16.66           | 100         | 6.0                       | 10            |  |

| 5h (0101)              | 20              | 104         | 5.2                       | 12            |  |

| 6h (0110) <sup>1</sup> | 20              | 116         | 5.8                       | 24            |  |

| 7h (0111)              | 22.2            | 108         | 4.86                      | 14            |  |

| 8h (1000)              | 23.3            | 124         | 5.32                      | 14            |  |

| 9h (1001)              | 26.6            | 128         | 4.81                      | 16            |  |

| Ah (1010)              | 30              | 132         | 4.4                       | 18            |  |

| Bh (1011) <sup>1</sup> | 30              | 146         | 4.87                      | 32            |  |

| Ch (1100)              | -               | 136         | 4.25                      | 20            |  |

| Dh (1101)              | -               | 152         | 4.56                      | 20            |  |

| Eh (1110)              | -               | 172         | 4.7                       | 22            |  |

| Fh (1111)              | -               | 176         | 4.4                       | 24            |  |

### NOTE:

1. These settings provide additional A/D input sampling time, in order to allow accurate readings with a higher external sourceimpedance.

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V-5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

Table 3. A/D Timing Configuration for 10-bit Mode

| ADCFG.3-0 | Max. Oscillator | Conv        | ersion Time               | Sampling Time |  |

|-----------|-----------------|-------------|---------------------------|---------------|--|

| ADCFG.3-0 | Frequency (MHz) | Osc. Clocks | μ <b>sec at max. Osc.</b> | (Osc. Clocks) |  |

| 0h (0000) | 6.66            | 88          | 13.21                     | 4             |  |

| 1h (0001) | 8               | 92          | 9.2                       | 6             |  |

| 2h (0010) | 8               | 96          | 8.64                      | 8             |  |

| 3h (0011) | 12              | 116         | 8.7                       | 8             |  |

| 4h (0100) | 12              | 120         | 7.2                       | 10            |  |

| 5h (0101) | 12              | 124         | 6.2                       | 12            |  |

| 6h (0110) | 12              | 136         | 6.8                       | 24            |  |

| 7h (0111) | 12              | 128         | 5.77                      | 14            |  |

| 8h (1000) | 13              | 148         | 6.35                      | 14            |  |

| 9h (1001) | 13              | 152         | 5.71                      | 16            |  |

| Ah (1010) | 13              | 156         | 5.2                       | 18            |  |

| Bh (1011) | 13              | 170         | 5.67                      | 32            |  |

| Ch (1100) | 13              | 160         | 5.0                       | 20            |  |

| Dh (1101) | 16              | 180         | 5.41                      | 20            |  |

| Eh (1110) | 20              | 204         | 5.57                      | 22            |  |

| Fh (1111) | 20              | 208         | 5.2                       | 24            |  |

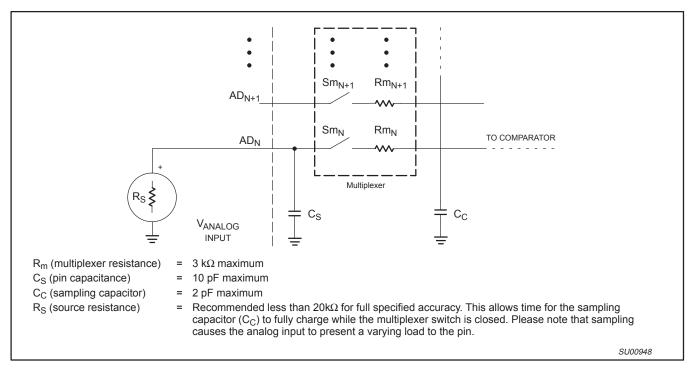

## A/D Inputs

In order to obtain accurate measurements with the A/D Converter, the source drive must be sufficient to adequately charge the sampling capacitor during the sampling time. Figure 4 shows the equivalent resistance and capacitance related to the A/D inputs. A/D timing configurations indicated in Table 1 allow for full A/D

accuracy (according to the A/D specifications) assuming a source resistance of less than or equal to  $20k\Omega$ . Larger source resistances may be accommodated by increasing the sampling time with a different A/D timing configuration.

Figure 4. A/D Input: Equivalent Circuit

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

#### XA-S3 Timer/Counters

The XA-S3 has three general purpose counter/timers, two of which may also be used as baud rate generators for either or both of the UARTs.

#### Timer 0 and 1

These are identical to the standard XA-G3 timer 0 and 1.

#### Timer 2

This is identical to the standard XA-G3 timer 2.

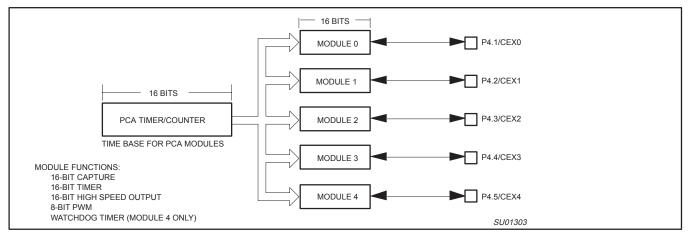

## **Programmable Counter Array (PCA)**

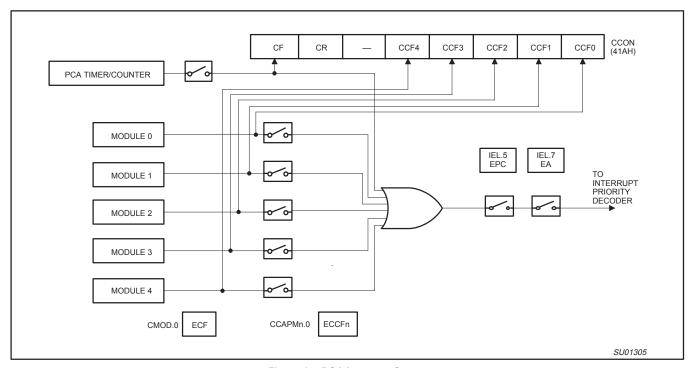

The Programmable Counter Array available on the XA-S3 is a special 16-bit Timer that has five 16-bit capture/compare modules associated with it. Each of the modules can be programmed to operate in one of four modes: rising and/or falling edge capture, software timer, high-speed output, or pulse width modulator. Each module has a pin associated with it in port 1. Module 0 is connected to P4.1(CEX0), module 1 to P4.2(CEX1), etc. The basic PCA configuration is shown in Figure 7.

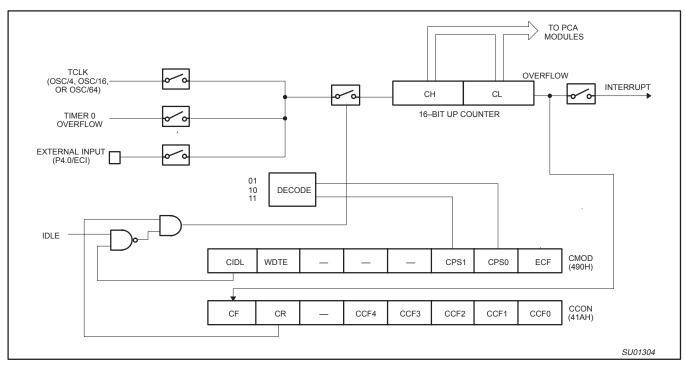

The PCA timer is a common time base for all five modules and can be programmed to run at: the TCLK rate (Osc/4, Osc/16, or Osc/64), the Timer 0 overflow, or the input on the ECI pin (P4.0). When the ECI input is used, the falling edge clocks the PCA counter. The timer count source is determined from the CPS1 and CPS0 bits in the CMOD SFR as follows (see Figure 10):

#### CPS1 CPS0 PCA Timer Count Source

- 0 X TCLK (Osc/4, Osc/16, or Osc/64)

- 1 0 Timer 0 overflow

- 1 1 ECI (PCA External Clock Input (max rate = Osc/4)

In the CMOD SFR are three additional bits associated with the PCA. They are CIDL which allows the PCA to stop during idle mode, WDTE which enables or disables the watchdog function on module 4, and ECF which when set causes an interrupt and the PCA overflow flag CF (in the CCON SFR) to be set when the PCA timer overflows. These functions are shown in Figure 8. In addition, each PCA module may generate a separate interrupt.

The watchdog timer function is implemented in module 4 (see Figure 17).

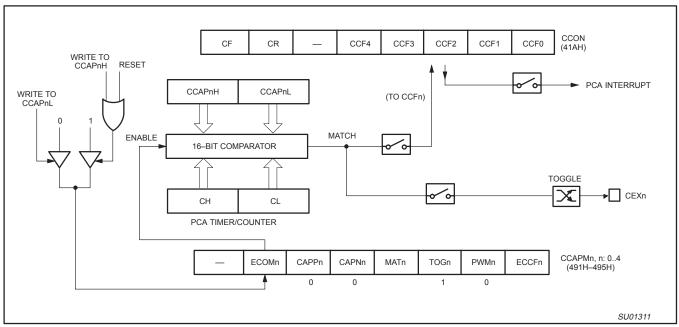

The CCON SFR contains the run control bit for the PCA and the flags for the PCA timer (CF) and each module (refer to Figure 11). To run the PCA the CR bit (CCON.6) must be set by software. The PCA is shut off by clearing this bit. The CF bit (CCON.7) is set when the PCA counter overflows and an interrupt will be generated if the ECF bit in the CMOD register is set, The CF bit can only be cleared by software. Bits 0 through 4 of the CCON register are the flags for the modules (bit 0 for module 0, bit 1 for module 1, etc.) and are set by hardware when either a match or a capture occurs. These flags also can only be cleared by software. The PCA interrupt system shown in Figure 9.

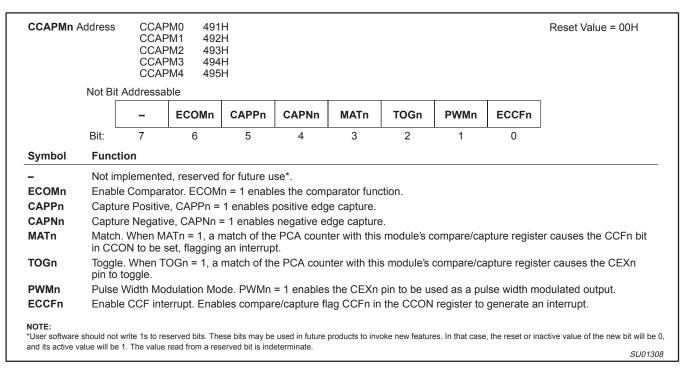

Each module in the PCA has a special function register associated with it. These registers are: CCAPM0 for module 0, CCAPM1 for module 1, etc. (see Figure 12). The registers contain the bits that control the mode that each module will operate in. The ECCF bit (CCAPMn.0 where n=0, 1, 2, 3, or 4 depending on the module) enables the CCF flag in the CCON SFR to generate an interrupt when a match or compare occurs in the associated module. PWM (CCAPMn.1) enables the pulse width modulation mode. The TOG bit (CCAPMn.2) when set causes the CEX output associated with the module to toggle when there is a match between the PCA counter and the module's capture/compare register. The match bit MAT (CCAPMn.3) when set will cause the CCFn bit in the CCON register to be set when there is a match between the PCA counter and the module's capture/compare register.

The next two bits CAPN (CCAPMn.4) and CAPP (CCAPMn.5) determine the edge that a capture input will be active on. The CAPN bit enables the negative edge, and the CAPP bit enables the positive edge. If both bits are set both edges will be enabled and a capture will occur for either transition. The last bit in the register ECOM (CCAPMn.6) when set enables the comparator function. Figure 13 shows the CCAPMn settings for the various PCA functions.

There are two additional registers associated with each of the PCA modules. They are CCAPnH and CCAPnL and these are the registers that store the 16-bit count when a capture occurs or a compare should occur. When a module is used in the PWM mode these registers are used to control the duty cycle of the output.

Figure 7. Programmable Counter Array (PCA)

Figure 8. PCA Timer/Counter

Figure 9. PCA Interrupt System

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

Figure 12. CCAPMn: PCA Modules Compare/Capture Registers

| _ | ECOMn | CAPPn | CAPNn | MATn | TOGn | PWMn | ECCFn | MODULE FUNCTION                                   |

|---|-------|-------|-------|------|------|------|-------|---------------------------------------------------|

| Х | 0     | 0     | 0     | 0    | 0    | 0    | 0     | No operation                                      |

| Х | Х     | 1     | 0     | 0    | 0    | 0    | Х     | 16-bit capture by a positive-edge trigger on CEXn |

| Х | Х     | 0     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a negative trigger on CEXn      |

| Х | Х     | 1     | 1     | 0    | 0    | 0    | Х     | 16-bit capture by a transition on CEXn            |

| Х | 1     | 0     | 0     | 1    | 0    | 0    | Х     | 16-bit Software Timer                             |

| Х | 1     | 0     | 0     | 1    | 1    | 0    | Х     | 16-bit High Speed Output                          |

| Х | 1     | 0     | 0     | 0    | 0    | 1    | 0     | 8-bit PWM                                         |

| Х | 1     | 0     | 0     | 1    | Х    | 0    | Х     | Watchdog Timer                                    |

Figure 13. PCA Module Modes (CCAPMn Register)

## **PCA Capture Mode**

To use one of the PCA modules in the capture mode either one or both of the CCAPM bits CAPN and CAPP for that module must be set. The external CEX input for the module (on port 1) is sampled for a transition. When a valid transition occurs the PCA hardware loads the value of the PCA counter registers (CH and CL) into the module's capture registers (CCAPnL and CCAPnH). If the CCFn bit for the module in the CCON SFR and the ECCFn bit in the CCAPMn SFR are set then an interrupt will be generated. Refer to Figure 14.

### 16-bit Software Timer Mode

The PCA modules can be used as software timers by setting both the ECOM and MAT bits in the modules CCAPMn register. The PCA timer will be compared to the module's capture registers and when a match occurs an interrupt will occur if the CCFn (CCON SFR) and the ECCFn (CCAPMn SFR) bits for the module are both set (see Figure 15).

## **High Speed Output Mode**

In this mode the CEX output (on port 4) associated with the PCA module will toggle each time a match occurs between the PCA

counter and the module's capture registers. To activate this mode the TOG, MAT, and ECOM bits in the module's CCAPMn SFR must be set (see Figure 16).

#### **Pulse Width Modulator Mode**

All of the PCA modules can be used as PWM outputs. Figure 17 shows the PWM function. The frequency of the output depends on the source for the PCA timer. All of the modules will have the same frequency of output because they all share the PCA timer. The duty cycle of each module is independently variable using the module's capture register CCAPLn. When the value of the PCA CL SFR is less than the value in the module's CCAPLn SFR the output will be low, when it is equal to or greater than the output will be high. When CL overflows from FF to 00, CCAPLn is reloaded with the value in CCAPHn. the allows updating the PWM without glitches. The PWM and ECOM bits in the module's CCAPMn register must be set to enable the PWM mode.

Figure 16. PCA High Speed Output Mode

Figure 17. PCA PWM Mode

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

```

INIT_WATCHDOG:

MOV CCAPM4, #4CH

; Module 4 in compare mode

MOV CCAP4L, #0FFH

; Write to low byte first

MOV CCAP4H, #0FFH

; Before PCA timer counts up to

; FFFF Hex, these compare values

; must be changed

OR CMOD, #40H

; Set the WDTE bit to enable the

; watchdog timer without changing

; the other bits in CMOD

; Main program goes here, but CALL WATCHDOG periodically.

WATCHDOG:

; Hold off interrupts

CLR EA

MOV CCAP4L, #00

; Next compare value is within

; 255 counts of the current PCA

MOV CCAP4H, CH

SETB EA

; timer value

RET

```

Figure 19. PCA Watchdog Timer Initialization Code

## Watchdog Timer

This is a standard XA-G3 watchdog timer. This watchdog timer always comes up running at reset. The watchdog acts the same on EPROM, ROM, and ROMless parts, as in the XA-G3.

#### **UARTS**

Standard XA-S3 UART0 and UART1 with double buffered transmit register. A flag has been added to SnSTAT that is set if any of the status flags (BRn, FEn, or OEn) is set for the corresponding UART channel. This allows polling for UART errors quickly at the interrupt service routine. Baud rate sources may be timer 1 or timer 2.

The XA-S3 includes 2 UART ports that are compatible with the enhanced UART used on the XA-G3.

The UART has separate interrupt vectors for each UART's transmit and receive functions. The UART transmitter has been double buffered, allowing packed transmission of data with no gaps between bytes and less critical interrupt service routine timing. A break detect function has been added to the UART. This operates independently of the UART itself and provides a start-of-break status bit that the program may test. An Overrun Error flag allows detection of missed characters in the received data stream. The double buffered UART transmitter may require some software changes if code is used that was written for the original XA-G3 single buffered UART.

Each UART baud rate is determined by either a fixed division of the oscillator (in UART modes 0 and 2) or by the timer 1 or timer 2 overflow rate (in UART modes 1 and 3).

Timer 1 defaults to clock both UART0 and UART1. Timer 2 can be programmed to clock either UART0 through T2CON (via bits R0CLK and T0CLK) or UART1 through T2MOD (via bits R1CLK and T1CLK). In this case, the UART not clocked by T2 could use T1 as the clock source.

The serial port receive and transmit registers are both accessed at Special Function Register SnBUF. Writing to SnBUF loads the

transmit register, and reading SnBUF accesses a physically separate receive register.

The serial port can operate in 4 modes:

**Mode 0: Serial I/O expansion mode.** Serial data enters and exits through RxDn. TxDn outputs the shift clock. 8 bits are transmitted/received (LSB first). (The baud rate is fixed at 1/16 the oscillator frequency.)

**Mode 1: Standard 8-bit UART mode.** 10 bits are transmitted (through TxDn) or received (through RxDn): a start bit (0), 8 data bits (LSB first), and a stop bit (1). On receive, the stop bit goes into RB8 in Special Function Register SnCON. The baud rate is variable.

Mode 2: Fixed rate 9-bit UART mode. 11 bits are transmitted (through TxD) or received (through RxD): start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). On Transmit, the 9th data bit (TB8\_n in SnCON) can be assigned the value of 0 or 1. Or, for example, the parity bit (P, in the PSW) could be moved into TB8\_n. On receive, the 9th data bit goes into RB8\_n in Special Function Register SnCON, while the stop bit is ignored. The baud rate is programmable to 1/32 of the oscillator frequency.

**Mode 3: Standard 9-bit UART mode.** 11 bits are transmitted (through TxDn) or received (through RxDn): a start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that uses SnBUF as a destination register. Reception is initiated in Mode 0 by the condition  $RI_n = 0$  and  $REN_n = 1$ . Reception is initiated in the other modes by the incoming start bit if  $REN_n = 1$ .

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

#### 8-BIT MODE A/D CONVERTER DC ELECTRICAL CHARACTERISTICS

$T_{amb}$  = 0 to +70°C for commercial,  $T_{amb}$  = -40 to +85°C for industrial, unless otherwise specified.

| OVMBOL           | DADAMETED                                                  | TEGT CONDITIONS                | LI                    |                       |      |

|------------------|------------------------------------------------------------|--------------------------------|-----------------------|-----------------------|------|

| SYMBOL           | PARAMETER                                                  | TEST CONDITIONS                | MIN                   | MAX                   | UNIT |

| $AV_{DD}$        | Analog supply voltage                                      |                                | 2.7                   | 3.3                   | V    |

| Al <sub>DD</sub> | Analog supply current (operating)                          | Port 5 = 0 to AV <sub>DD</sub> |                       | 2.5                   | mA   |

| Al <sub>ID</sub> | Analog supply current (Idle mode)                          |                                |                       | 2.5                   | μΑ   |

| Al <sub>PD</sub> | Analog supply current (Power-Down mode)                    | Commercial temperature range   |                       | 100                   | μΑ   |

|                  |                                                            | Industrial temperature range   |                       | 150                   | μА   |

| AV <sub>IN</sub> | Analog input voltage                                       |                                | AV <sub>SS</sub> -0.2 | AV <sub>DD</sub> +0.2 | V    |

| R <sub>REF</sub> | Resistance between V <sub>REF+</sub> and V <sub>REF-</sub> |                                | 125                   | 225                   | kΩ   |

| C <sub>IA</sub>  | Analog input capacitance                                   |                                |                       | 15                    | pF   |

| DL <sub>e</sub>  | Differential non-linearity <sup>1, 2, 3</sup>              |                                |                       | ±1                    | LSB  |

| IL <sub>e</sub>  | Integral non-linearity <sup>1, 4</sup>                     |                                |                       | ±1                    | LSB  |

| OS <sub>e</sub>  | Offset error <sup>1, 5</sup>                               |                                |                       | ±2.5                  | LSB  |

| Ge               | Gain error <sup>1, 6</sup>                                 |                                |                       | ±1                    | %    |

| A <sub>e</sub>   | Absolute voltage error <sup>1, 7</sup>                     |                                |                       | ±3                    | LSB  |

| M <sub>CTC</sub> | Channel-to-channel matching                                |                                |                       | ±1                    | LSB  |

| Ct               | Crosstalk between inputs of port <sup>8</sup>              | 0 – 100 kHz                    |                       | -60                   | dB   |

#### NOTES:

1. Conditions:  $AV_{REF-} = 0 \text{ V}$ ;  $AV_{REF+} = 3.07 \text{ V}$ .

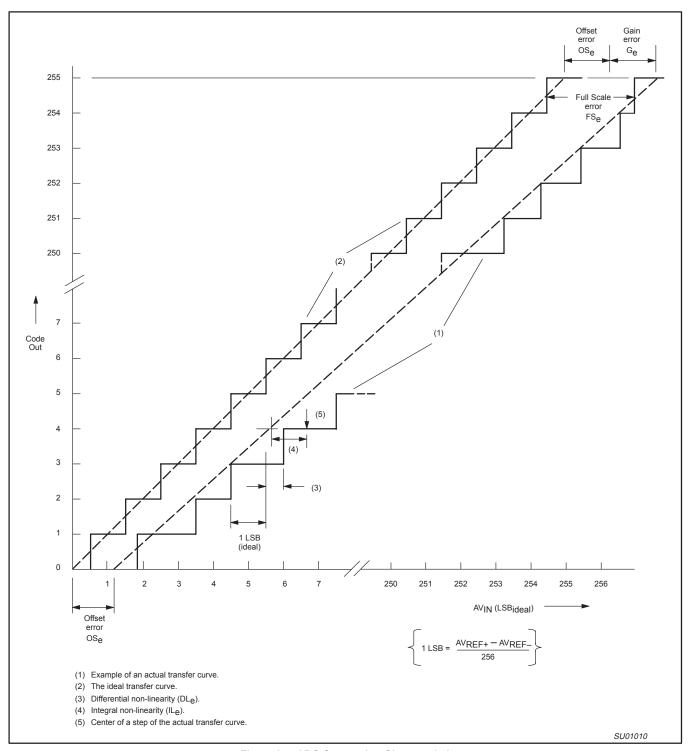

- 2. The differential non-linearity  $(\widehat{\mathsf{DL}}_{\mathsf{e}})$  is the difference between the actual step width and the ideal step width. See Figure 25.

- 3. The ADC is monotonic, there are no missing codes.

- The integral non-linearity (IL<sub>e</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See Figure 25.

- The offset error (OS<sub>e</sub>) is the absolute difference between the straight line which fits the actual transfer curve (after removing gain error), and the straight line which fits the ideal transfer curve. See Figure 25.

- 6. The gain error (G<sub>e</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve (after removing offset error), and the straight line which fits the ideal transfer curve. Gain error is constant at every point on the transfer curve. See Figure 25.

- The absolute voltage error (A<sub>e</sub>) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve.

- 8. This should be considered when both analog and digital signals are input simultaneously to Port 5. Parameter is guaranteed bydesign.

Figure 25. ADC Conversion Characteristic

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

## AC ELECTRICAL CHARACTERISTICS (3 V RANGE) (continued)

This set of parameters is referenced to the XA-S3 clock output.

| SYMBOL FIG         | FIGURE  | PARAMETER                                              | LIN | UNIT              |        |

|--------------------|---------|--------------------------------------------------------|-----|-------------------|--------|

| STWBUL             | FIGURE  | PARAMETER                                              | MIN | MAX               | וואט ך |

| Address C          | ycle    |                                                        |     |                   |        |

| t <sub>CHLH</sub>  | 26      | CLKOUT rising edge to ALE rising edge                  | _   | 15                | ns     |

| t <sub>CLLL</sub>  | 26      | CLKOUT falling edge to ALE falling edge                | -   | 11                | ns     |

| t <sub>CHAV</sub>  | 26      | CLKOUT rising edge to address valid                    | -   | 29                | ns     |

| t <sub>CHAX</sub>  | 26      | CLKOUT rising edge to address changing (hold time)     | 2   | -                 | ns     |

| Code Read          | l Cycle | •                                                      |     |                   |        |

| t <sub>CHPL</sub>  | 26      | CLKOUT rising edge to PSEN asserted                    | _   | 16                | ns     |

| tchph              | 26      | CLKOUT rising edge to PSEN de-asserted                 | _   | 15                | ns     |

| tıvch              | 26      | Instruction valid to CLKOUT rising edge (setup time)   | 30  | -                 | ns     |

| t <sub>CHIX</sub>  | 26      | CLKOUT rising edge to instruction changing (hold time) | 0   | -                 | ns     |

| t <sub>CHIZ</sub>  | 26      | CLKOUT rising edge to Bus 3-State (code read)          | -   | t <sub>C</sub> -8 | ns     |

| Data Read          | Cycle   |                                                        |     |                   |        |

| t <sub>CHRL</sub>  | 28      | CLKOUT rising edge to RD asserted                      | _   | 20                | ns     |

| tchrh              | 28      | CLKOUT rising edge to RD de-asserted                   | _   | 16                | ns     |

| t <sub>DVCH</sub>  | 28      | Data valid to CLKOUT rising edge (setup time)          | 28  | -                 | ns     |

| t <sub>CHDX</sub>  | 28      | CLKOUT rising edge to Data changing (hold time)        | 0   | -                 | ns     |

| t <sub>CHDZ</sub>  | 28      | CLKOUT rising edge to Bus 3-State (data read)          | -   | t <sub>C</sub> -8 | ns     |

| Data Write         | Cycle   | -                                                      |     |                   |        |

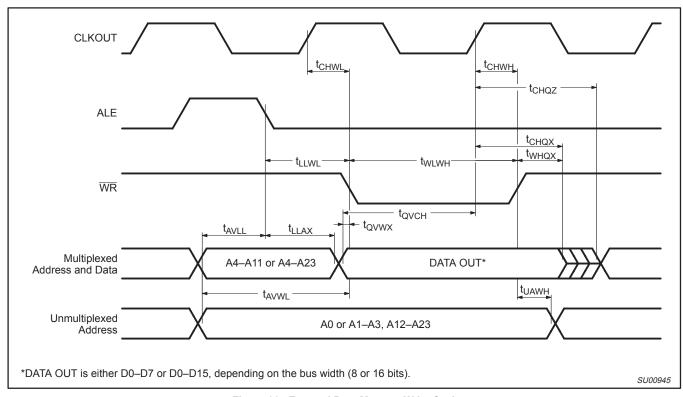

| t <sub>CHWL</sub>  | 30      | CLKOUT falling edge to WR asserted                     | _   | 19                | ns     |

| t <sub>CHWH</sub>  | 30      | CLKOUT rising edge to WR de-asserted                   | _   | 16                | ns     |

| tqvch              | 30      | Data valid to CLKOUT rising edge (setup time)          | 4   | _                 | ns     |

| t <sub>CHQX</sub>  | 30      | CLKOUT rising edge to Data changing (hold time)        | 0   | _                 | ns     |

| Wait Input         |         | •                                                      | -   | -                 |        |

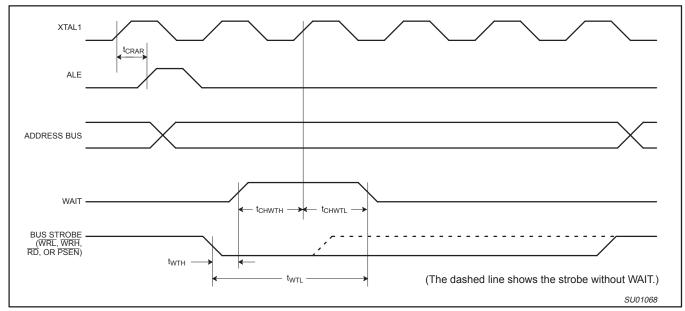

| t <sub>CHWTH</sub> | 31      | WAIT valid prior to CLKOUT rising edge <sup>8</sup>    | 30  | 4                 | ns     |

## NOTES:

- Load capacitance for all outputs = 50 pF.

- Variables V1 through V13 reflect programmable bus timing, which is programmed via the Bus Timing registers (BTRH and BTRL). Refer to the XA User Guide for details of the bus timing settings.

- V1) This variable represents the programmed width of the ALE pulse as determined by the ALEW bit in the BTRL register V1 = 0.5 if the ALEW bit = 0, and 1.5 if the ALEW bit = 1.

- V2) This variable represents the programmed width of the PSEN pulse as determined by the CR1 and CR0 bits or the CRA1, CRA0, and ALEW bits in the BTRL register.

- For a bus cycle with no ALE, V2 = 1 if CR1/0 = 00, 2 if CR1/0 = 01, 3 if CR1/0 = 10, and 4 if CR1/0 = 11. Note that during burst

mode code fetches, PSEN does not exhibit transitions at the boundaries of bus cycles. V2 still applies for the purpose of

determining peripheral timing requirements.

- For a bus cycle with an ALE, V2 = the total bus cycle duration (2 if CRA1/0 = 00, 3 if CRA1/0 = 01, 4 if CRA1/0 = 10, and 5 if CRA1/0 = 11) minus the number of clocks used by ALE (V1 + 0.5) = 2.

Example: if CRA1/0 = 10 and ALEW = 1, the V2 = 4 (1.5 + 0.5) = 2.

- V3) This variable represents the programmed length of an entire code read cycle **with** ALE. This time is determined by the CRA1 and CRA0 bits in the BTRL register. V3 = the total bus cycle duration (2 if CRA1/0 = 00, 3 if CRA1/0 = 01, 4 if CRA1/0 = 10, and 5 if CRA1/0 = 11).

- V4) This variable represents the programmed length of an entire code read cycle with **no** ALE. This time is determined by the CR1 and CR0 bits in the BTRL register. V4 = 1 if CR1/0 = 00, 2 if CR1/0 = 01, 3 if CR1/0 = 10, and 4 if CR1/0 = 11.

- V5) This variable represents the programmed length of an entire data read cycle with **no** ALE. This time is determined by the DR1 and DR0 bits in the BTRH register. V5 = 1 if DR1/0 = 00, 2 if DR1/0 = 01, 3 if DR1/0 = 10, and 4 if DR1/0 = 11.

- V6) This variable represents the programmed length of an entire data read cycle **with** ALE. The time is determined by the DRA1 and DRA0 bits in the BTRH register. V6 = the total bus cycle duration (2 if DRA1/0 = 00, 3 if DRA1/0 = 01, 4 if DRA1/0 = 10, and 5 if DRA1/0 = 11).

XA-S3

## **AC WAVEFORMS**

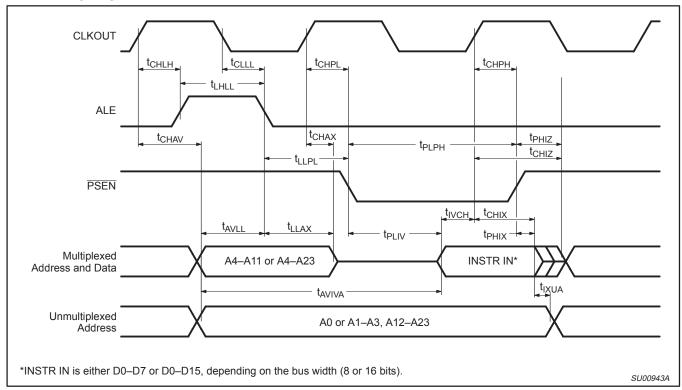

Figure 26. External Program Memory Read Cycle (ALE Cycle)

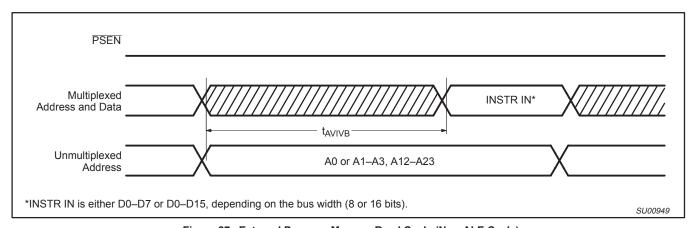

Figure 27. External Program Memory Read Cycle (Non-ALE Cycle)

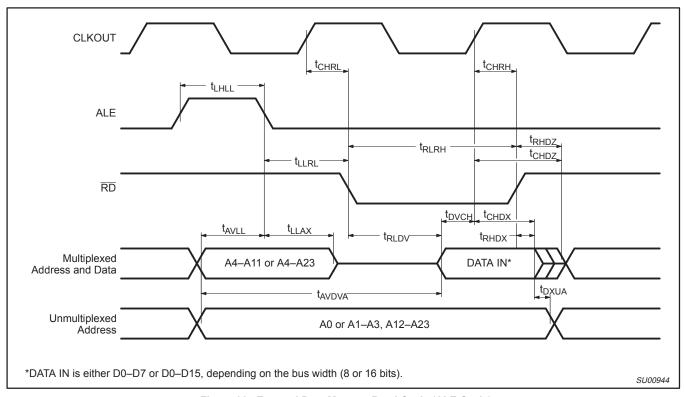

Figure 28. External Data Memory Read Cycle (ALE Cycle)

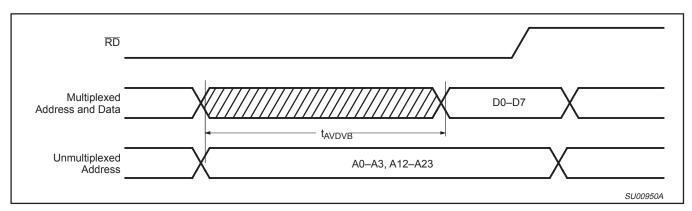

Figure 29. External Data Memory Read Cycle (Non-ALE Cycle)

Figure 30. External Data Memory Write Cycle

Figure 31. WAIT Signal Timing

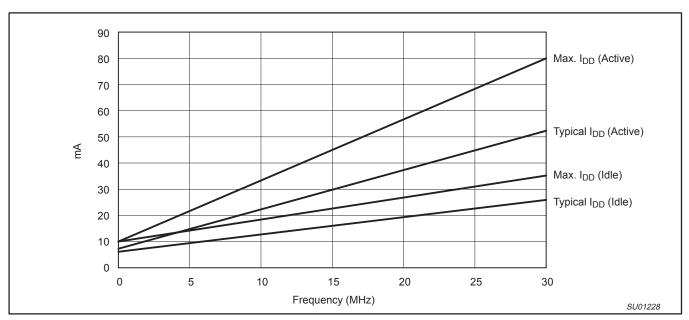

$\label{eq:Figure 37.} \ I_{DD} \ vs. \ Frequency$  Valid only within frequency specification of the device under test.

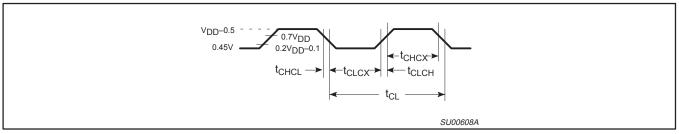

Figure 38. Clock Signal Waveform for  $I_{DD}$  Tests in Active and Idle Modes  $t_{CLCH}$  =  $t_{CHCL}$  = 5 ns

Figure 39.  $I_{DD}$  Test Condition, Power Down Mode All other pins are disconnected.  $V_{DD}$ =2 V to 5.5 V

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs, 16 MB address range

XA-S3

#### **EPROM CHARACTERISTICS**

The XA-S3 is programmed by using a modified Improved Quick-Pulse Programming™ algorithm. This algorithm is essentially the same as that used by 80C51 family EPROM parts. However different pins are used for many programming functions.

The XA-S3 contains three signature bytes that can be read and used by an EPROM programming system to identify the device. The signature bytes identify the device as an XA-S3 manufactured by Philips.

## **Security Bits**

With none of the security bits programmed the code in the program memory can be verified. When only security bit 1 is programmed, MOVC instructions executed from external program memory are disabled from fetching code bytes from the internal memory. All further programming of the EPROM is disabled. When security bits 1 and 2 are programmed, in addition to the above, verify mode is disabled. When all three security bits are programmed, all of the conditions above apply and all external program memory execution is disabled. (See Table 6.)

**Table 6. Program Security Bits**

| PF | PROGRAM LOCK BITS |     | rs  |                                                                                                                                                                      |

|----|-------------------|-----|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | SB1               | SB2 | SB3 | PROTECTION DESCRIPTION                                                                                                                                               |

| 1  | U                 | U   | U   | No Program Security features enabled.                                                                                                                                |

| 2  | Р                 | U   | U   | MOVC instructions executed from external program memory are disabled from fetching code bytes from internal memory and further programming of the EPROM is disabled. |

| 3  | Р                 | Р   | U   | Same as 2, also verify is disabled.                                                                                                                                  |

| 4  | Р                 | Р   | Р   | Same as 3, external execution is disabled. Internal data RAM is not accessible.                                                                                      |

#### NOTES:

- 1. P programmed. U unprogrammed.

- 2. Any other combination of the security bits is not defined.

## **ROM CODE SUBMISSION**

When submitting ROM code for the XA-S3, the following must be specified:

- 1. 32k byte user ROM data

- 2. ROM security bits.

| ADDRESS        | CONTENT | BIT(S) | COMMENT                                                           |

|----------------|---------|--------|-------------------------------------------------------------------|

| 0000H to 7FFFH | DATA    | 7:0    | User ROM Data                                                     |

| 8020H          | SEC     | 0      | ROM Security Bit 1                                                |

| 8020H          | SEC     | 1      | ROM Security Bit 2<br>0 = enable security<br>1 = disable security |

| 8020H          | SEC     | 3      | ROM Security Bit 3<br>0 = enable security<br>1 = disable security |

<sup>™</sup>Trademark phrase of Intel Corporation.

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V),  $I^2C$ , 2 UARTs, 16 MB address range

XA-S3

## **NOTES**

XA 16-bit microcontroller 32 K/1 K OTP/ROM/ROMless, 8-channel 8-bit A/D, low voltage (2.7 V–5.5 V), I<sup>2</sup>C, 2 UARTs,16 MB address range

XA-S3

#### **DATA SHEET STATUS**

| DOCUMENT<br>STATUS <sup>(1)</sup> | PRODUCT<br>STATUS <sup>(2)</sup> | DEFINITION                                                                            |

|-----------------------------------|----------------------------------|---------------------------------------------------------------------------------------|

| Objective data sheet              | Development                      | This document contains data from the objective specification for product development. |

| Preliminary data sheet            | Qualification                    | This document contains data from the preliminary specification.                       |

| Product data sheet                | Production                       | This document contains the product specification.                                     |

#### **Notes**

- 1. Please consult the most recently issued document before initiating or completing a design.

- 2. The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### **DISCLAIMERS**

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction

of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

# **NXP Semiconductors**

## **Customer notification**

This data sheet was changed to reflect the new company name NXP Semiconductors. Changes to content include: Corrected SOT188-3 to SOT188-2; changed data sheet specification to Product; updated legal definitions and disclaimers.

#### **Contact information**

For additional information please visit: http://www.nxp.com

For sales offices addresses send e-mail to: salesaddresses@nxp.com

© NXP B.V. 2013

All rights are reserved. Reproduction in whole or in part is prohibited without the prior written consent of the copyright owner.

The information presented in this document does not form part of any quotation or contract, is believed to be accurate and reliable and may be changed without notice. No liability will be accepted by the publisher for any consequence of its use. Publication thereof does not convey nor imply any license under patent- or other industrial or intellectual property rights.

Printed in The Netherlands R05/10/pp54 Date of release: 2013 Sep 04 Document order number: 9397 750 07816