Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core Processore200z3Core Size32-Bit Single-CoreSpeed60MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)             | Details                    |                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed60MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory SizeIMB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)Converter Package100 + 00 + 00 + 00 + 00 + 00 + 00 + 00 | Product Status             | Active                                                                  |

| Speed60MHzConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)Number of LAB A A A A A A A A A A A A A A A A A A           | Core Processor             | e200z3                                                                  |

| ConnectivityCANbus, EBI/EMI, LINbus, SCI, SPI, UART/USARTPeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                      | Core Size                  | 32-Bit Single-Core                                                      |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O80Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                                               | Speed                      | 60MHz                                                                   |

| Number of I/O80Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                                                                            | Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI, UART/USART                           |

| Program Memory Size1MB (1M x 8)Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFP (24x24)                                                                                                                                                                           | Peripherals                | DMA, POR, PWM, WDT                                                      |

| Program Memory TypeFLASHEEPROM Size-RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                           | Number of I/O              | 80                                                                      |

| EEPROM Size-RAM Size64K × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                   | Program Memory Size        | 1MB (1M × 8)                                                            |

| RAM Size64K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                               | Program Memory Type        | FLASH                                                                   |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.25VData ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                              | EEPROM Size                | -                                                                       |

| Data ConvertersA/D 34x12bOscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                    | RAM Size                   | 64K x 8                                                                 |

| Oscillator TypeInternalOperating Temperature-40°C ~ 125°C (TA)Mounting TypeSurface MountPackage / Case176-LQFPSupplier Device Package176-LQFP (24x24)                                                                                                                                                                                                                                                                                             | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.25V                                                            |

| Operating Temperature     -40°C ~ 125°C (TA)       Mounting Type     Surface Mount       Package / Case     176-LQFP       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                           | Data Converters            | A/D 34x12b                                                              |

| Mounting Type     Surface Mount       Package / Case     176-LQFP       Supplier Device Package     176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                              | Oscillator Type            | Internal                                                                |

| Package / Case 176-LQFP<br>Supplier Device Package 176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                               | Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Supplier Device Package 176-LQFP (24x24)                                                                                                                                                                                                                                                                                                                                                                                                          | Mounting Type              | Surface Mount                                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Package / Case             | 176-LQFP                                                                |

| Purchase URL https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5633mf2mlu60                                                                                                                                                                                                                                                                                                                                                              | Supplier Device Package    | 176-LQFP (24x24)                                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5633mf2mlu60 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1 Addendum List for Revision 9

Table 1. MPC5634M Rev 9 Addendum

| Location                                                                        | Description                                                                                                                                         |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Section 4.11, "Temperature<br>Sensor Electrical<br>Characteristics",<br>Page 81 | In "Temperature Sensor Electrical Characteristics" table, update the Min and Max value of<br>"Accuracy" parameter to -20°C and +20°C, respectively. |

# 2 Revision History

Table 2 provides a revision history for this datasheet addendum document.

### Table 2. Revision History Table

| Rev. Number | Substantive Changes | Date of Release |

|-------------|---------------------|-----------------|

| 1.0         | Initial release.    | 12/2014         |

#### How to Reach Us:

Home Page: freescale.com

Web Support: freescale.com/support Information in this document is provided solely to enable system and software implementers to use Freescale products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document.

Freescale reserves the right to make changes without further notice to any products herein. Freescale makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. Freescale does not convey any license under its patent rights nor the rights of others. Freescale sells products pursuant to standard terms and conditions of sale, which can be found at the following address:freescale.com/SalesTermsandConditions.

Freescale, the Freescale logo, AltiVec, C-5, CodeTest, CodeWarrior, ColdFire, C-Ware, Energy Efficient Solutions logo, Kinetis, mobileGT, PowerQUICC, Processor Expert, QorlQ, Qorivva, StarCore, Symphony, and VortiQa are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. Airfast, BeeKit, BeeStack, ColdFire+, CoreNet, Flexis, MagniV, MXC, Platform in a Package, QorlQ Qonverge, QUICC Engine, Ready Play, SafeAssure, SMARTMOS, TurboLink, Vybrid, and Xtrinsic are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners. © 2014 Freescale Semiconductor, Inc.

Document Number: MPC5634M\_AD Rev. 1.0 01/2015

Overview

The flash memory provides the following features:

- Supports a 64-bit data bus for instruction fetch, CPU loads and DMA access. Byte, halfword, word and doubleword reads are supported. Only aligned word and doubleword writes are supported.

- Fetch Accelerator

- Architected to optimize the performance of the flash with the CPU to provide single cycle random access to the flash up to 80 MHz system clock speed

- Configurable read buffering and line prefetch support

- Four line read buffers (128 bits wide) and a prefetch controller

- · Hardware and software configurable read and write access protections on a per-master basis

- Interface to the flash array controller is pipelined with a depth of one, allowing overlapped accesses to proceed in parallel for interleaved or pipelined flash array designs

- Configurable access timing allowing use in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (0-31 additional cycles) allowing use for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page size of 128 bits (four words)

- ECC with single-bit correction, double-bit detection

- Program page size of 64 bits (two words)

- ECC single-bit error corrections are visible to software

- Minimum program size is two consecutive 32-bit words, aligned on a 0-modulo-8 byte address, due to ECC

- Embedded hardware program and erase algorithm

- Erase suspend

- Shadow information stored in non-volatile shadow block

- Independent program/erase of the shadow block

## 2.2.10 SRAM

The MPC5634M SRAM module provides a general-purpose up to 94 KB memory block. The SRAM controller includes these features:

- · Supports read/write accesses mapped to the SRAM memory from any master

- 32 KB or 24 KB block powered by separate supply for standby operation

- Byte, halfword, word and doubleword addressable

- ECC performs single-bit correction, double-bit detection on 32-bit data element

## 2.2.11 BAM

The BAM (Boot Assist Module) is a block of read-only memory that is programmed once by Freescale and is identical for all MPC5634M MCUs. The BAM program is executed every time the MCU is powered-on or reset in normal mode. The BAM supports different modes of booting. They are:

- Booting from internal flash memory

- Serial boot loading (A program is downloaded into RAM via eSCI or the FlexCAN and then executed)

- Booting from external memory on calibration bus

The BAM also reads the reset configuration half word (RCHW) from internal flash memory and configures the MPC5634M hardware accordingly. The BAM provides the following features:

• Sets up MMU to cover all resources and mapping all physical address to logical addresses with minimum address translation

#### Overview

- SCK to PCS delay

- Delay between frames

- Programmable serial frame size of 4 to 16 bits, expandable with software control

- Continuously held chip select capability

- 6 Peripheral Chip Selects, expandable to 64 with external demultiplexer

- Deglitching support for up to 32 Peripheral Chip Selects with external demultiplexer

- DMA support for adding entries to TX FIFO and removing entries from RX FIFO:

- TX FIFO is not full (TFFF)

- RX FIFO is not empty (RFDF)

- 6 Interrupt conditions:

- End of queue reached (EOQF)

- TX FIFO is not full (TFFF)

- Transfer of current frame complete (TCF)

- Attempt to transmit with an empty Transmit FIFO (TFUF)

- RX FIFO is not empty (RFDF)

- FIFO Underrun (slave only and SPI mode, the slave is asked to transfer data when the TxFIFO is empty)

- FIFO Overrun (serial frame received while RX FIFO is full)

- Modified transfer formats for communication with slower peripheral devices

- Continuous Serial Communications Clock (SCK)

- Power savings via support for Stop Mode

- Enhanced DSI logic to implement a 32-bit Timed Serial Bus (TSB) configuration, supporting the Microsecond Channel downstream frame format

The DSPIs also support these features unique to the DSI and CSI configurations:

- 2 sources of the serialized data:

- eTPU\_A and eMIOS output channels

- Memory-mapped register in the DSPI

- Destinations for the deserialized data:

- eTPU\_A and eMIOS input channels

- SIU External Interrupt Request inputs

- Memory-mapped register in the DSPI

- Deserialized data is provided as Parallel Output signals and as bits in a memory-mapped register

- Transfer initiation conditions:

- Continuous

- Edge sensitive hardware trigger

- Change in data

- · Pin serialization/deserialization with interleaved SPI frames for control and diagnostics

- Continuous serial communications clock

- Support for parallel and serial chaining of up to four DSPI blocks

## 2.2.16 eSCI

The enhanced serial communications interface (eSCI) allows asynchronous serial communications with peripheral devices and other MCUs. It includes special support to interface to Local Interconnect Network (LIN) slave devices. The eSCI block provides the following features:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- Independent interrupt source for each channel

- Counter can be stopped in debug mode

# 2.2.19 Software Watchdog Timer (SWT)

The Software Watchdog Timer (SWT) is a second watchdog module to complement the standard Power Architecture watchdog integrated in the CPU core. The SWT is a 32-bit modulus counter, clocked by the system clock or the crystal clock, that can provide a system reset or interrupt request when the correct software key is not written within the required time window.

The following features are implemented:

- 32-bit modulus counter

- Clocked by system clock or crystal clock

- Optional programmable watchdog window mode

- Can optionally cause system reset or interrupt request on timeout

- · Reset by writing a software key to memory mapped register

- Enabled out of reset

- Configuration is protected by a software key or a write-once register

## 2.2.20 Debug features

### 2.2.20.1 Nexus port controller

The NPC (Nexus Port Controller) block provides real-time development support capabilities for the MPC5634MPower Architecture-based MCU in compliance with the IEEE-ISTO 5001-2003 standard. This development support is supplied for MCUs without requiring external address and data pins for internal visibility. The NPC block is an integration of several individual Nexus blocks that are selected to provide the development support interface for MPC5634M. The NPC block interfaces to the host processor (e200z335), eTPU, and internal buses to provide development support as per the IEEE-ISTO 5001-2003 standard. The development support provided includes program trace and run-time access to the MCUs internal memory map and access to the Power Architecture and eTPU internal registers during halt. The Nexus interface also supports a JTAG only mode using only the JTAG pins. MPC5634Min the production 144 LQFP supports a 3.3 V reduced (4-bit wide) Auxiliary port. These Nexus port pins can also be used as 5 V I/O signals to increase usable I/O count of the device. When using this Nexus port as IO, Nexus trace is still possible using VertiCal calibration. In the VertiCal calibration package, the full 12-bit Auxiliary port is available.

### NOTE

In the VertiCal package, the full Nexus Auxiliary port shares balls with the addresses of the calibration bus. Therefore multiplexed address/data bus mode must be used for the calibration bus when using full width Nexus trace in VertiCal assembly.

The following features are implemented:

- 5-pin JTAG port (JCOMP, TDI, TDO, TMS, and TCK)

- Always available in production package

- Supports both JTAG Boundary Scan and debug modes

- 3.3 V interface

- Supports Nexus class 1 features

- Supports Nexus class 3 read/write feature

- 9-pin Reduced Port interface in 144 LQFP production package

- Alternate function as IO

- 5 V (in GPIO or alternate function mode), 3.3 V (in Nexus mode) interface

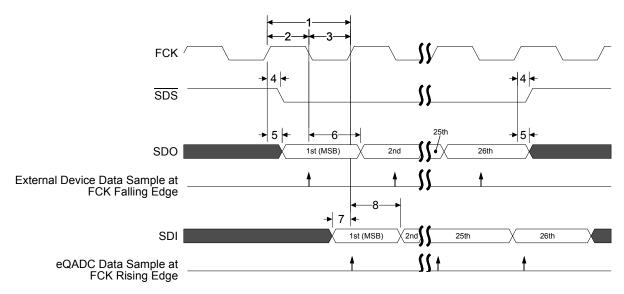

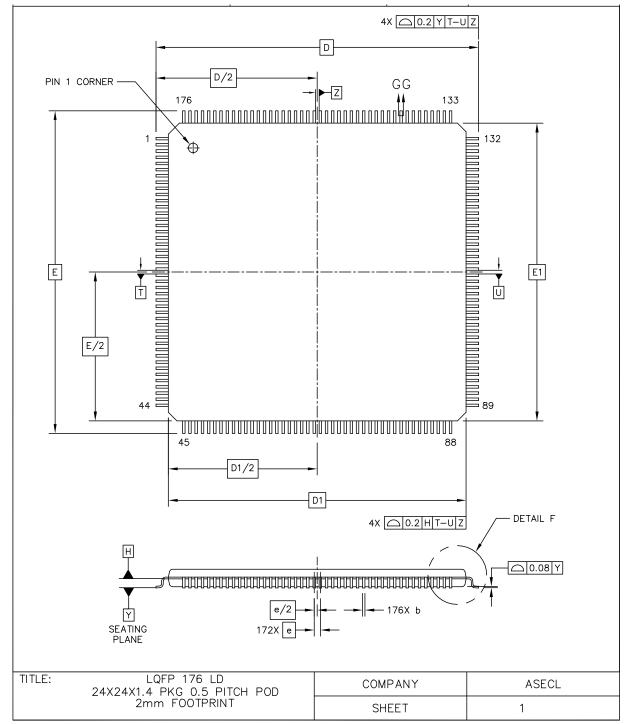

# 3 Pinout and signal description

This section contains the pinouts for all production packages for the MPC5634M family of devices. Please note the following:

- Pins labeled "NC" are to be left unconnected. Any connection to an external circuit or voltage may cause unpredictable device behavior or damage.

- Pins labeled "NIC" have no internal connection.

# 3.1 144 LQFP pinout

Figure 2 shows the pinout for the 144-pin LQFP.

| 1 |   |  |

|---|---|--|

|   | _ |  |

|   |   |  |

### Table 2. MPC563xM signal properties (continued)

|                                      |                                                                                 | Pad                                       |                              |             |                                    |                          | Francisco ( Oto to                             | Pin No.     |                  |                 |

|--------------------------------------|---------------------------------------------------------------------------------|-------------------------------------------|------------------------------|-------------|------------------------------------|--------------------------|------------------------------------------------|-------------|------------------|-----------------|

| Name                                 | Function <sup>1</sup>                                                           | Config.<br>Register<br>(PCR) <sup>2</sup> | PCR PA<br>Field <sup>3</sup> | l/O<br>Type | Voltage <sup>4</sup> /<br>Pad Type | Reset State <sup>5</sup> | Function / State —<br>After Reset <sup>6</sup> | 144<br>LQFP | 176<br>LQFP      | 208 MAPB<br>GA  |

| AN[13]<br>MA[1]<br>ETPU_A[21]<br>SDO | Single Ended Analog Input<br>Mux Address<br>ETPU_A Ch.<br>eQADC Serial Data Out | PCR[216]                                  | 011<br>010<br>100<br>000     | <br>0<br>0  | VDDEH7                             | I /                      | AN[13] / –                                     | 118         | 147              | B12             |

| AN[14]<br>MA[2]<br>ETPU_A[27]<br>SDI | Single Ended Analog Input<br>Mux Address<br>ETPU_A Ch.<br>eQADC Serial Data In  | PCR[217]                                  | 011<br>010<br>100<br>000     | <br>0<br>   | VDDEH7                             | I /                      | AN[14] / –                                     | 117         | 146              | C12             |

| AN[15]<br>FCK<br>ETPU_A[29]          | Single Ended Analog Input<br>eQADC Free Running Clock<br>ETPU_A Ch.             | PCR[218]                                  | 011<br>010<br>000            | <br>0<br>0  | VDDEH7                             | I /                      | AN[15] / –                                     | 116         | 145              | C13             |

| AN[16]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] /                                        | 3           | 3                | C6              |

| AN[17]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 2           | 2                | C4              |

| AN[18]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] /                                        | 1           | 1                | D5              |

| AN[21]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 144         | 173              | B4              |

| AN[22]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 132         | 161              | B8              |

| AN[23]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / —                    | AN[x] /                                        | 131         | 160              | C9              |

| AN[24]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 130         | 159              | D8              |

| AN[25]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 129         | 158              | B9              |

| AN[27]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] /                                        | 128         | 157              | A10             |

| AN[28]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] /                                        | 127         | 156              | B10             |

| AN[30]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / —                    | AN[x] /                                        | 126         | 155              | D9              |

| AN[31]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / —                    | AN[x] /                                        | 125         | 154              | D10             |

| AN[32]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] / -                                      | 124         | 153              | C10             |

| AN[33]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] / -                                      | 123         | 152              | C11             |

| AN[34]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / –                    | AN[x] / -                                      | 122         | 151              | C5              |

| AN[35]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | l / –                    | AN[x] / -                                      | 121         | 150              | D11             |

| AN[36]                               | Single Ended Analog Input                                                       | —                                         | —                            | I           | VDDA                               | I / –                    | AN[x] / -                                      | —           | 174 <sup>7</sup> | F4 <sup>8</sup> |

| AN[37]                               | Single Ended Analog Input                                                       | _                                         | _                            | Ι           | VDDA                               | l / –                    | AN[x] / –                                      | _           | 175 <sup>7</sup> | E3 <sup>8</sup> |

49

- <sup>9</sup> The GPIO functions on GPIO[206] and GPIO[207] can be selected as trigger functions in the SIU for the ADC by making the proper selections in the SIU\_ETISR and SIU\_ISEL3 registers in the SIU.

- <sup>10</sup> Some signals in this section are available only on calibration package.

- <sup>11</sup> These pins are only available in the 496 CSP/MAPBGA calibration/development package.

- <sup>12</sup> On the calibration package, the Nexus function on this pin is enabled when the NEXUSCFG pin is high and Nexus is configured to full port mode. On the 176-pin and 208-pin packages, the Nexus function on this pin is enabled permanently. Do not connect the Nexus MDO or MSEO pins directly to a power supply or ground.

- <sup>13</sup> In the calibration package, the I/O segment containing this pin is called VDDE12.

- <sup>14</sup> 208-ball BGA package only

- <sup>15</sup> When configured as Nexus (208-pin package or calibration package with NEXUSCFG=1), and JCOMP is asserted during reset, MDO[0] is driven high until the crystal oscillator becomes stable, at which time it is then negated.

- <sup>16</sup> The function of this pin is Nexus when NEXUSCFG is high.

- <sup>17</sup> High when the pin is configured to Nexus, low otherwise.

- <sup>18</sup> O/Low for the calibration with NEXUSCFG=0; I/Up otherwise.

- <sup>19</sup> ALT\_ADDR/Low for the calibration package with NEXUSCFG=0; EVTI/Up otherwise.

- <sup>20</sup> In 176-pin and 208-pin packages, the Nexus function is disabled and the pin/ball has the secondary function

- <sup>21</sup> This signal is not available in the 176-pin and 208-pin packages.

- <sup>22</sup> The primary function is not selected via the PA field when the pin is a Nexus signal. Instead, it is activated by the Nexus controller.

- <sup>23</sup> TDI and TDO are required for JTAG operation.

- <sup>24</sup> The primary function is not selected via the PA field when the pin is a JTAG signal. Instead, it is activated by the JTAG controller.

- <sup>25</sup> The function and state of the CAN\_A and eSCI\_A pins after execution of the BAM program is determined by the BOOTCFG1 pin.

- <sup>26</sup> Connect an external 10K pull-up resistor to the SCI\_A\_RX pin to ensure that the pin is driven high during CAN serial boot.

- <sup>27</sup> For pins AN[0:7], during and just after POR negates, internal pull resistors can be enabled, resulting in as much as 4 mA of current draw. The pull resistors are disabled when the system clock propagates through the device.

- <sup>28</sup> ETPUA[24:29] are input and output. The input muxing is controlled by SIU\_ISEL8 register.

- <sup>29</sup> eTPU\_A[25] is an output only function.

- <sup>30</sup> Only the output channels of eTPU[8:9] are connected to pins.

- <sup>31</sup> The function after reset of the XTAL pin is determined by the value of the signal on the PLLCFG[1] pin. When bypass mode is chosen XTAL has no function and should be grounded.

- <sup>32</sup> The function after reset of the EXTAL\_EXTCLK pin is determined by the value of the signal on the PLLCFG[1] pin. If the EXTCLK function is chosen, the valid operating voltage for the pin is 1.62 V to 3.6 V. If the EXTAL function is chosen, the valid operating voltage is 3.3 V.

- <sup>33</sup> VSSPLL and VSSREG are connected to the same pin.

- <sup>34</sup> This pin is shared by two pads: VDDA\_AN, using pad\_vdde\_hv, and VDDA\_DIG, using pad\_vdde\_int\_hv.

- <sup>35</sup> This pin is shared by two pads: VSSA\_AN, using pad\_vsse\_hv, and VSSA\_DIG, using pad\_vsse\_int\_hv.

- <sup>36</sup> VDDEH1A, VDDEH1B, and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>37</sup> LVDS pins will not work at 3.3 V.

- <sup>38</sup> The VDDEH6 segment may be powered from 3.0 V to 5.0 V for mux address or SSI functions, but must meet the VDDA specifications of 4.5 V to 5.25 V for analog input function.

- <sup>8</sup> Internal structures hold the voltage greater than –1.0 V if the injection current limit of 2 mA is met.

- <sup>9</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- <sup>10</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>11</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- <sup>12</sup> Total injection current for all analog input pins must not exceed 15 mA.

- <sup>13</sup> Lifetime operation at these specification limits is not guaranteed.

- <sup>14</sup> Solder profile per CDF-AEC-Q100.

- <sup>15</sup> Moisture sensitivity per JEDEC test method A112.

# 4.3 Thermal characteristics

| Symbo               | ol | С | Parameter                                                   | Conditions              | Value | Unit |

|---------------------|----|---|-------------------------------------------------------------|-------------------------|-------|------|

| $R_{\thetaJA}$      | CC | D | Junction-to-Ambient, Natural Convection <sup>1</sup>        | Single layer board – 1s | 43    | °C/W |

| $R_{\thetaJA}$      | CC | D | Junction-to-Ambient, Natural Convection <sup>2</sup>        | Four layer board – 2s2p | 35    | °C/W |

| R <sub>0JMA</sub>   | CC | D | Junction-to-Ambient (@200 ft/min) <sup>2</sup>              | Single layer board –1s  | 34    | °C/W |

| R <sub>0JMA</sub>   | CC | D | Junction-to-Ambient (@200 ft/min) <sup>2</sup>              | Four layer board – 2s2p | 29    | °C/W |

| $R_{\theta JB}$     | CC | D | Junction-to-Board <sup>2</sup>                              |                         | 22    | °C/W |

| R <sub>0JCtop</sub> | CC | D | Junction-to-Case (Top) <sup>3</sup>                         |                         | 8     | °C/W |

| Ψ <sub>JT</sub>     | CC | D | Junction-to-Package Top, Natural<br>Convection <sup>4</sup> |                         | 2     | °C/W |

### Table 8. Thermal characteristics for 144-pin LQFP

<sup>1</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>2</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

<sup>3</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

<sup>4</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

# NP

#### **Electrical characteristics**

• B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

# 4.4 Electromagnetic Interference (EMI) characteristics

| Symbol    | Parameter        | Conditions                                                  | f <sub>OSC</sub> /f <sub>BUS</sub>                                                                                                                                                   | Frequency        | Level<br>(Typ) | Unit |

|-----------|------------------|-------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------|

| Radiated  | V <sub>EME</sub> | Device                                                      | Oscillator                                                                                                                                                                           | 150 kHz – 50 MHz | 26             | dBμV |

| Emissions |                  | Configuration, test<br>conditions and EM                    | Frequency = 8<br>MHz;                                                                                                                                                                | 50–150 MHz       | 24             |      |

|           |                  | testing per standard                                        | Oscillator         150 kHz – 50 MHz           Frequency = 8         50–150 MHz           MHz;         50–500 MHz           Id         System Bus           Iy         Frequency = 80 | 24               |                |      |

|           |                  | IEC61967-2; Supply<br>Voltage = 5.0V DC,                    |                                                                                                                                                                                      | 500–1000 MHz     | 21             |      |

|           |                  | Ambient<br>Temperature =<br>25°C, Worst-case<br>Orientation | Frequency<br>Modulation<br>Oscillator<br>Frequency = 8<br>MHz;<br>System Bus                                                                                                         | IEC Level        | К              | _    |

|           |                  |                                                             |                                                                                                                                                                                      |                  |                |      |

|           |                  |                                                             |                                                                                                                                                                                      | 150 kHz – 50 MHz | 20             | dBμV |

|           |                  |                                                             |                                                                                                                                                                                      | 50–150 MHz       | 19             |      |

|           |                  |                                                             |                                                                                                                                                                                      | 150–500 MHz      | 14             |      |

|           |                  |                                                             |                                                                                                                                                                                      | 500–1000 MHz     | 7              |      |

|           |                  |                                                             |                                                                                                                                                                                      | IEC Level        | L              | _    |

|           |                  |                                                             |                                                                                                                                                                                      |                  |                |      |

### Table 11. EMI testing specifications<sup>1</sup>

<sup>1</sup> IEC Classification Level: L = 24dBuV; K = 30dBuV.

# 4.5 Electromagnetic static discharge (ESD) characteristics

| Symbol |    | Parameter                                 | Conditions            | Value | Unit |

|--------|----|-------------------------------------------|-----------------------|-------|------|

| —      | SR | ESD for Human Body Model (HBM)            | —                     | 2000  | V    |

| R1     | SR | HBM circuit description                   | —                     | 1500  | Ω    |

| С      | SR |                                           | _                     | 100   | pF   |

| —      | SR | ESD for field induced charge Model (FCDM) | All pins              | 500   | V    |

|        |    |                                           | Corner pins           | 750   |      |

| —      | SR | Number of pulses per pin                  | Positive pulses (HBM) | 1     | —    |

|        |    |                                           | Negative pulses (HBM) | 1     | —    |

| —      | SR | Number of pulses                          | _                     | 1     | _    |

### Table 12. ESD ratings<sup>1,2</sup>

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements, which includes the complete DC parametric and functional testing at room temperature and hot temperature."

\_\_\_\_\_

| ID | Name                    |    | С | Parameter                                                                                         | Min               | Тур       | Max               | Unit | Notes                                                           |

|----|-------------------------|----|---|---------------------------------------------------------------------------------------------------|-------------------|-----------|-------------------|------|-----------------------------------------------------------------|

| 5b |                         | CC | Ρ | Nominal 3.3 V supply<br>internal regulator DC output<br>voltage variation after<br>power-on reset | Vdd33 –<br>7.5%   | Vdd33     | Vdd33 +<br>7%     | V    | With internal<br>load up<br>to ldd3p3                           |

| 5c | —                       | СС | D | Voltage regulator 3.3 V<br>output impedance at<br>maximum DC load                                 | _                 | _         | 2                 | Ω    |                                                                 |

| 5d | ldd3p3                  | СС | Ρ | Voltage regulator 3.3 V<br>maximum DC output<br>current                                           | 80                | —         | _                 | mA   |                                                                 |

| 5e | Vdd33 ILim <sup>6</sup> | СС | С | Voltage regulator 3.3 V DC current limit                                                          | —                 | 130       | —                 | mA   |                                                                 |

| 6  | Lvi3p3                  | CC | С | Nominal LVI for rising 3.3 V supply <sup>5</sup>                                                  | _                 | 3.090     | _                 | V    | The Lvi3p3<br>specs are also<br>valid for the<br>Vddeh LVI      |

| 6a | —                       | СС | С | Variation of LVI for rising<br>3.3 V supply at power-on<br>reset <sup>5</sup>                     | Lvi3p3–6%         | Lvi3p3    | Lvi3p3+6%         | V    | See note <sup>7</sup>                                           |

| 6b | _                       | СС | С | Variation of LVI for rising<br>3.3 V supply after power-on<br>reset <sup>5</sup>                  | Lvi3p3–3%         | Lvi3p3    | Lvi3p3+3%         | V    | See note 7                                                      |

| 6c | —                       | CC | С | Trimming step LVI 3.3 V <sup>5</sup>                                                              | _                 | 20        | _                 | mV   |                                                                 |

| 6d | Lvi3p3_h                | СС | С | LVI 3.3 V hysteresis <sup>5</sup>                                                                 | _                 | 60        | _                 | mV   |                                                                 |

| 7  | Por3.3V_r               | CC | С | Nominal POR for rising<br>3.3 V supply                                                            | _                 | 2.07      | _                 | V    | The 3.3V POR<br>specs<br>are also valid<br>for the<br>Vddeh POR |

| 7a | _                       | СС | С | Variation of POR for rising 3.3 V supply                                                          | Por3.3V_r–<br>35% | Por3.3V_r | Por3.3V_r+<br>35% | V    |                                                                 |

| 7b | Por3.3V_f               | СС | С | Nominal POR for falling<br>3.3 V supply                                                           | —                 | 1.95      | —                 | V    |                                                                 |

| 7c | _                       | СС | С | Variation of POR for falling 3.3 V supply                                                         | Por3.3V_f-<br>35% | Por3.3V_f | Por3.3V_f+<br>35% | V    |                                                                 |

| 8  | Lvi5p0                  | СС | С | Nominal LVI for rising 5 V<br>VDDREG supply <sup>5</sup>                                          | —                 | 4.290     | —                 | V    |                                                                 |

| 8a | _                       | СС | С | Variation of LVI for rising<br>5 V VDDREG supply at<br>power-on reset <sup>5</sup>                | Lvi5p0–6%         | Lvi5p0    | Lvi5p0+6%         | V    |                                                                 |

| 8b | _                       | СС | С | Variation of LVI for rising<br>5 V VDDREG supply<br>power-on reset <sup>5</sup>                   | Lvi5p0–3%         | Lvi5p0    | Lvi5p0+3%         | V    |                                                                 |

| 8c | —                       | СС | С | Trimming step LVI 5 V <sup>5</sup>                                                                | —                 | 20        | —                 | mV   |                                                                 |

| Sympol                                 |                                                               | с | Deremeter                                                                          | Conditions                                                                                                              | Value <sup>2</sup> |     |                        |      |

|----------------------------------------|---------------------------------------------------------------|---|------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--------------------|-----|------------------------|------|

| Symbol                                 |                                                               | C | Parameter                                                                          | Conditions                                                                                                              | min                | typ | max                    | Unit |

| I <sub>DDH1</sub>                      | CC                                                            | D | Operating current                                                                  | V <sub>DDEH1</sub>                                                                                                      | _                  | -   | See note <sup>23</sup> | mA   |

| I <sub>DDH6</sub><br>I <sub>DDH7</sub> |                                                               | D | V <sub>DDE</sub> <sup>23</sup> supplies @<br>80 MHz                                | V <sub>DDEH6</sub>                                                                                                      | _                  | -   |                        |      |

| I <sub>DD7</sub>                       |                                                               | D |                                                                                    | V <sub>DDEH7</sub>                                                                                                      | _                  | _   |                        |      |

| I <sub>DDH9</sub><br>I <sub>DD12</sub> |                                                               | D |                                                                                    | V <sub>DDE7</sub>                                                                                                       | _                  | -   |                        |      |

|                                        |                                                               | D |                                                                                    | V <sub>DDEH9</sub>                                                                                                      | _                  | -   |                        |      |

|                                        |                                                               | D |                                                                                    | V <sub>DDE12</sub>                                                                                                      | _                  | —   |                        |      |

| I <sub>ACT_S</sub>                     | CC                                                            | С | Slow/medium I/O weak                                                               | 3.0 V – 3.6 V                                                                                                           | 15                 | —   | 95                     | μA   |

|                                        |                                                               | Ρ | pull up/down current <sup>24</sup>                                                 | 4.75 V –<br>5.25 V                                                                                                      | 35                 | _   | 200                    |      |

| I <sub>ACT_F</sub>                     | CT_F CC D Fast I/O weak pull<br>up/down current <sup>24</sup> |   | Fast I/O weak pull<br>up/down current <sup>24</sup>                                | 1.62 V –<br>1.98 V                                                                                                      | 36                 | —   | 120                    | μA   |

|                                        |                                                               | D |                                                                                    | 2.25 V –<br>2.75 V                                                                                                      | 34                 | _   | 139                    |      |

|                                        | D                                                             |   |                                                                                    | 3.0 V – 3.6 V                                                                                                           | 42                 | _   | 158                    |      |

| I <sub>ACT_MV_PU</sub>                 | CC                                                            | С | Multi-voltage pad weak<br>pullup current                                           | V <sub>DDEH</sub> =<br>3.0–3.6 V <sup>10</sup> ,<br>pad_multv_hv,<br>all process<br>corners,<br>high swing<br>mode only | 10                 | _   | 75                     | μΑ   |

|                                        |                                                               | Ρ |                                                                                    | 4.75 V –<br>5.25 V                                                                                                      | 25                 | _   | 200                    |      |

| I <sub>ACT_MV_PD</sub>                 | СС                                                            | С | Multivoltage pad weak<br>pulldown current                                          | V <sub>DDEH</sub> =<br>3.0–3.6 V <sup>10</sup> ,<br>pad_multv_hv,<br>all process<br>corners,<br>high swing<br>mode only | 10                 | _   | 60                     | μA   |

|                                        |                                                               | Ρ |                                                                                    | 4.75 V –<br>5.25 V                                                                                                      | 25                 | -   | 200                    |      |

| I <sub>INACT_D</sub>                   | СС                                                            | Р | I/O input leakage<br>current <sup>25</sup>                                         | —                                                                                                                       | -2.5               | _   | 2.5                    | μA   |

| I <sub>IC</sub>                        | СС                                                            | Т | DC injection current<br>(per pin)                                                  | —                                                                                                                       | -1.0               | _   | 1.0                    | mA   |

| I <sub>INACT_A</sub>                   | CC                                                            | Ρ | Analog input current,<br>channel off, AN[0:7],<br>AN38, AN39 <sup>26</sup>         | —                                                                                                                       | -250               | _   | 250                    | nA   |

|                                        |                                                               | Ρ | Analog input current,<br>channel off, all other<br>analog pins (ANx) <sup>26</sup> | —                                                                                                                       | -150               | -   | 150                    |      |

| Symbol                      |    | с                                                             | Parameter                                                         | Conditions               |      | Value <sup>2</sup> |     | Unit |

|-----------------------------|----|---------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|------|--------------------|-----|------|

|                             |    |                                                               | Farameter                                                         | Conditions               | min  | typ                | max |      |

| CL                          | CC | D                                                             | Load capacitance (fast I/O) <sup>27</sup>                         | DSC(PCR[8:9<br>]) = 0b00 | —    | _                  | 10  | pF   |

|                             |    | D                                                             | -                                                                 | DSC(PCR[8:9<br>]) = 0b01 |      | _                  | 20  |      |

|                             |    | D                                                             |                                                                   | DSC(PCR[8:9<br>]) = 0b10 | —    | _                  | 30  |      |

|                             |    | D                                                             |                                                                   | DSC(PCR[8:9<br>]) = 0b11 | —    | _                  | 50  |      |

| C <sub>IN</sub>             | СС | D                                                             | Input capacitance<br>(digital pins)                               | —                        | —    | _                  | 7   | pF   |

| C <sub>IN_A</sub>           | CC | D                                                             | Input capacitance<br>(analog pins)                                | _                        | _    | _                  | 10  | pF   |

| C <sub>IN_M</sub>           | CC | D                                                             | Input capacitance<br>(digital and analog<br>pins <sup>28</sup> )  | _                        | —    | -                  | 12  | pF   |

| R <sub>PUPD200K</sub>       | CC | Ρ                                                             | Weak Pull-Up/Down<br>Resistance <sup>29,30</sup><br>200 kΩ Option | —                        | 130  | _                  | 280 | kΩ   |

| R <sub>PUPDMATCH</sub>      | CC | С                                                             | 200KΩ Option                                                      |                          | -2.5 |                    | 2.5 | %    |

| R <sub>PUPD100K</sub>       | CC | Ρ                                                             | Weak Pull-Up/Down<br>Resistance <sup>29,30</sup><br>100 kΩ Option | _                        | 65   | _                  | 140 | kΩ   |

| R <sub>PUPDMATCH</sub>      | CC | С                                                             | 100KΩ Option                                                      |                          | -2.5 |                    | 2.5 | %    |

| R <sub>PUPD5K</sub>         | CC | D                                                             | Weak Pull-Up/Down<br>Resistance <sup>29</sup><br>5 kΩ Option      | 5 V ± 5%<br>supply       | 1.4  | _                  | 7.5 | kΩ   |

| $T_A (T_L \text{ to } T_H)$ | SR | SR — Operating temperature —<br>range - ambient<br>(packaged) |                                                                   | -40.0                    | —    | 125.0              | °C  |      |

| —                           | SR | -                                                             | Slew rate on power supply pins                                    | _                        | —    | -                  | 50  | V/ms |

| Table 22. DC electrical specifications | <sup>1</sup> (continued) |

|----------------------------------------|--------------------------|

|----------------------------------------|--------------------------|

<sup>1</sup> These specifications are design targets and subject to change per device characterization.

<sup>2</sup> TBD: To Be Defined.

- $^3$  V<sub>DDE</sub> must be lower than V<sub>RC33</sub>, otherwise there is additional leakage on pins supplied by V<sub>DDE</sub>.

- <sup>4</sup> These specifications apply when  $V_{RC33}$  is supplied externally, after disabling the internal regulator ( $V_{DDREG} = 0$ ).

- <sup>5</sup> ADC is functional with 4 V  $\leq$  V<sub>DDA</sub>  $\leq$  4.75 V but with derated accuracy. This means the ADC will continue to function at full speed with no bad behavior, but the accuracy will be degraded.

- <sup>6</sup> Internal structures hold the input voltage less than V<sub>DDA</sub> + 1.0 V on all pads powered by V<sub>DDA</sub> supplies, if the maximum injection current specification is met (3 mA for all pins) and V<sub>DDA</sub> is within the operating voltage specifications.

<sup>7</sup> The V<sub>DDF</sub> supply is connected to V<sub>DD</sub> in the package substrate. This specification applies to calibration package devices only.

# 4.16.4 eMIOS timing

Table 39. eMIOS timing<sup>1</sup>

| \$ | ¥ | Symbol C          |    |   | Characteristic           | Min.<br>Value | Max.<br>Value | Unit             |

|----|---|-------------------|----|---|--------------------------|---------------|---------------|------------------|

|    | 1 | t <sub>MIPW</sub> | CC | D | eMIOS Input Pulse Width  | 4             | _             | t <sub>CYC</sub> |

| 2  | 2 | t <sub>MOPW</sub> | CC | D | eMIOS Output Pulse Width | 1             | _             | t <sub>CYC</sub> |

<sup>1</sup> eMIOS timing specified at  $f_{SYS}$  = 80 MHz,  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.25 V,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 50 pF with SRC = 0b00.

# 4.16.5 DSPI timing

|   |                   |        |                            |                                                                          | 40.0                      | MHz                       | 60 1                      | 60 MHz                    |                           | 80 MHz                      |            |  |      |

|---|-------------------|--------|----------------------------|--------------------------------------------------------------------------|---------------------------|---------------------------|---------------------------|---------------------------|---------------------------|-----------------------------|------------|--|------|

| # | Symi              | Symbol |                            | ymbol                                                                    |                           | Characteristic            | 401                       |                           |                           |                             | 00 1011 12 |  | Unit |

|   | ,                 |        |                            |                                                                          | Min.                      | Max.                      | Min.                      | Max.                      | Min.                      | Max.                        |            |  |      |

| 1 | t <sub>SCK</sub>  | CC     | D                          | SCK Cycle Time <sup>3,4</sup>                                            | 48.8 ns                   | 5.8 ms                    | 28.4 ns                   | 3.5 ms                    | 24.4 ns                   | 2.9 ms                      | _          |  |      |

| 2 | t <sub>csc</sub>  | СС     | D                          | PCS to SCK Delay <sup>5</sup>                                            | 46                        | —                         | 26                        | —                         | 22                        |                             | ns         |  |      |

| 3 | t <sub>ASC</sub>  | CC     | D                          | After SCK Delay <sup>6</sup>                                             | 45                        | _                         | 25                        |                           | 21                        | _                           | ns         |  |      |

| 4 | t <sub>SDC</sub>  | CC     | D                          | SCK Duty Cycle                                                           | (½t <sub>SC</sub> )–<br>2 | (½t <sub>SC</sub> )+<br>2 | (½t <sub>SC</sub> )–<br>2 | (½t <sub>SC</sub> )+<br>2 | (½t <sub>SC</sub> )–<br>2 | $\binom{1/2}{2} t_{SC} + 2$ | ns         |  |      |

| 5 | t <sub>A</sub>    | CC     | D                          | Slave Access Time<br>(SS active to SOUT<br>driven)                       | _                         | 25                        | —                         | 25                        | _                         | 25                          | ns         |  |      |

| 6 | t <sub>DIS</sub>  | CC     | D                          | Slave SOUT Disable<br>Time<br>(SS inactive to SOUT<br>High-Z or invalid) | —                         | 25                        | —                         | 25                        | —                         | 25                          | ns         |  |      |

| 7 | t <sub>PCSC</sub> | CC     | D                          | PCSx to PCSS time                                                        | 4                         | _                         | 4                         | _                         | 4                         | —                           | ns         |  |      |

| 8 | t <sub>PASC</sub> | CC     | D                          | PCSS to PCSx time                                                        | 5                         | _                         | 5                         |                           | 5                         | —                           | ns         |  |      |

| 9 | t <sub>SUI</sub>  | СС     | Data Setup Time for Inputs |                                                                          |                           |                           |                           |                           |                           |                             |            |  |      |

|   |                   |        | D                          | Master (MTFE = 0)                                                        | 20                        | _                         | 20                        | —                         | 20                        | —                           | ns         |  |      |

|   |                   |        | D                          | Slave                                                                    | 2                         | —                         | 2                         | —                         | 2                         | —                           |            |  |      |

|   |                   |        | D                          | Master (MTFE = 1,<br>CPHA = 0) <sup>7</sup>                              | -4                        | —                         | 6                         |                           | 8                         | _                           |            |  |      |

|   |                   |        | D                          | Master (MTFE = 1,<br>CPHA = 1)                                           | 20                        | —                         | 20                        | —                         | 20                        | —                           |            |  |      |

### Table 40. DSPI timing<sup>1,2</sup>

| #  | Sum              | hal | с | Characteristic                              | 40   | MHz          | 60 MHz     |      | 80 MHz |      | Unit |

|----|------------------|-----|---|---------------------------------------------|------|--------------|------------|------|--------|------|------|

| #  | Symbol           |     |   | Characteristic                              | Min. | Max.         | Min.       | Max. | Min.   | Max. | Omt  |

| 10 | t <sub>HI</sub>  | CC  |   |                                             | Da   | ita Hold Tii | me for Inp | uts  |        |      |      |

|    |                  |     | D | Master (MTFE = 0)                           | -4   |              | -4         |      | -4     | _    | ns   |

|    |                  |     | D | Slave                                       | 7    | —            | 7          | —    | 7      | _    |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA = 0) <sup>7</sup> | 45   | —            | 25         | _    | 21     | _    |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA = 1)              | -4   | _            | -4         |      | -4     | _    |      |

| 11 | t <sub>SUO</sub> | CC  |   |                                             | Dat  | a Valid (aff | ter SCK e  | dge) |        |      |      |

|    |                  |     | D | Master (MTFE = 0)                           | —    | 6            | —          | 6    | —      | 6    | ns   |

|    |                  |     | D | Slave                                       | —    | 25           | —          | 25   | —      | 25   |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA=0)                | —    | 45           | _          | 25   | _      | 21   |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA=1)                | —    | 6            | _          | 6    | _      | 6    |      |

| 12 | t <sub>HO</sub>  | CC  |   | Data Hold Time for Outputs                  |      |              |            |      |        |      | •    |

|    |                  |     | D | Master (MTFE = 0)                           | -5   | —            | -5         | —    | -5     | _    | ns   |

|    |                  |     | D | Slave                                       | 5.5  | _            | 5.5        |      | 5.5    |      |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA = 0)              | 8    | —            | 4          | —    | 3      | —    |      |

|    |                  |     | D | Master (MTFE = 1,<br>CPHA = 1)              | -5   | —            | -5         | —    | -5     |      |      |

### Table 40. DSPI timing<sup>1,2</sup> (continued)

<sup>1</sup> All DSPI timing specifications use the fastest slew rate (SRC = 0b11) on pad type M or MH. DSPI signals using pad types of S or SH have an additional delay based on the slew rate. DSPI timing is specified at VDDEH = 3.0–5.25 V, TA = TL to TH, and CL = 50 pF with SRC = 0b11.

<sup>2</sup> Speed is the nominal maximum frequency. Max speed is the maximum speed allowed including frequency modulation (FM). 42 MHz parts allow for 40 MHz system clock + 2% FM; 62 MHz parts allow for a 60 MHz system clock + 2% FM, and 82 MHz parts allow for 80 MHz system clock + 2% FM.

<sup>3</sup> The minimum DSPI Cycle Time restricts the baud rate selection for given system clock rate. These numbers are calculated based on two MPC5634M devices communicating over a DSPI link.

<sup>4</sup> The actual minimum SCK cycle time is limited by pad performance.

<sup>5</sup> The maximum value is programmable in DSPI\_CTARx[PSSCK] and DSPI\_CTARx[CSSCK].

<sup>6</sup> The maximum value is programmable in DSPI\_CTARx[PASC] and DSPI\_CTARx[ASC].

<sup>7</sup> This number is calculated assuming the SMPL\_PT bitfield in DSPI\_MCR is set to 0b10.

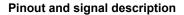

# 4.16.6 eQADC SSI timing

|   | CLOAD = 25pF on all outputs. Pad drive strength set to maximum. |    |   |                                                            |                                    |     |                                          |         |  |

|---|-----------------------------------------------------------------|----|---|------------------------------------------------------------|------------------------------------|-----|------------------------------------------|---------|--|

| # | # Symbol                                                        |    | С | Rating Min                                                 |                                    | Тур | Max                                      | Unit    |  |

| 1 | f <sub>FCK</sub>                                                | СС | D | FCK Frequency <sup>2, 3</sup>                              | 1/17 f <sub>SYS_CLK</sub>          |     | 1/2 f <sub>SYS_CLK</sub>                 | Hertz   |  |

| 1 | t <sub>FCK</sub>                                                | CC | D | FCK Period (t <sub>FCK</sub> = 1/ f <sub>FCK</sub> )       | 2 t <sub>SYS_CLK</sub>             |     | 17t <sub>SYS_CLK</sub>                   | seconds |  |

| 2 | t <sub>FCKHT</sub>                                              | СС | D | Clock (FCK) High Time                                      | $t_{\text{SYS}\_\text{CLK}} - 6.5$ |     | <sub>9*</sub> t <sub>SYS_CLK</sub> + 6.5 | ns      |  |

| 3 | t <sub>FCKLT</sub>                                              | СС | D | Clock (FCK) Low Time                                       | $t_{\text{SYS}\_\text{CLK}} - 6.5$ |     | <sub>8*</sub> t <sub>SYS_CLK</sub> + 6.5 | ns      |  |

| 4 | t <sub>SDS_LL</sub>                                             | СС | D | SDS Lead/Lag Time                                          | -7.5                               |     | +7.5                                     | ns      |  |

| 5 | t <sub>SDO_LL</sub>                                             | СС | D | SDO Lead/Lag Time                                          | -7.5                               |     | +7.5                                     | ns      |  |