# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                              |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | EC000                                                                 |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 8MHz                                                                  |

| Co-Processors/DSP               | -                                                                     |

| RAM Controllers                 | -                                                                     |

| Graphics Acceleration           | No                                                                    |

| Display & Interface Controllers | -                                                                     |

| Ethernet                        | -                                                                     |

| SATA                            | -                                                                     |

| USB                             | -                                                                     |

| Voltage - I/O                   | 5.0V                                                                  |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                     |

| Security Features               | -                                                                     |

| Package / Case                  | 68-LCC (J-Lead)                                                       |

| Supplier Device Package         | 68-PLCC (24.21x24.21)                                                 |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc000cei8 |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|           |    |      |       |      |    | 1     | BIT D<br>BYTE =  |                      | 5    |   |     |        |   |   |     |

|-----------|----|------|-------|------|----|-------|------------------|----------------------|------|---|-----|--------|---|---|-----|

|           |    |      |       | 7    | 6  | 5     | 4                | 3                    | 2    | 1 | 0   |        |   |   |     |

|           |    |      |       |      |    |       |                  |                      |      |   |     |        |   |   |     |

|           |    |      |       |      |    |       | NTEGEI<br>BYTE = |                      |      |   |     |        |   |   |     |

| 15        | 14 | 13   | 12    | 11   | 10 | 9     | 8                | 7                    | 6    | 5 | 4   | 3      | 2 | 1 | 0   |

| MSB       |    |      | BY    | TE 0 |    |       | LSB              |                      |      |   | BY  | TE 1   |   |   |     |

|           |    |      | BY    | TE 2 |    |       |                  |                      |      |   | BY  | TE 3   |   |   |     |

|           |    |      |       |      |    | 1\    | NORD =           | = 16 Bl <sup>-</sup> | rs   |   |     |        |   |   |     |

| 15        | 14 | 13   | 12    | 11   | 10 | 9     | 8                | 7                    | 6    | 5 | 4   | 3      | 2 | 1 | 0   |

| MSB       | 5  |      |       |      |    |       | WO               | RD 0                 |      |   |     |        |   |   | LSB |

|           |    |      |       |      |    |       | WO               | RD 1                 |      |   |     |        |   |   |     |

|           |    |      |       |      |    |       | WO               | RD 2                 |      |   |     |        |   |   |     |

|           |    | EVE  | N BYT | E    |    |       |                  |                      |      |   | ODE | ) BYTE |   |   |     |

| 7         | 6  | 5    | 4     | 3    | 2  | 1     | 0                | 7                    | 6    | 5 | 4   | 3      | 2 | 1 | 0   |

|           |    |      |       |      |    | 1 LON | ig wor           | RD = 32              | BITS |   |     |        |   |   |     |

| 15<br>MSB | 14 | 13   | 12    | 11   | 10 | 9     | 8                | 7                    | 6    | 5 | 4   | 3      | 2 | 1 | 0   |

| INI2R     |    | LONG | WORD  | 0 -  |    |       | HIGH             |                      | ?    |   |     |        |   |   |     |

|           |    | LONG | WORD  | U    |    |       | LOW              | ORDER                |      |   |     |        |   |   | LSB |

|           |    |      |       |      |    |       |                  |                      |      |   |     |        |   |   |     |

|           |    | LONG | WORD  | 1 -  |    |       |                  |                      |      |   |     | ·      |   |   |     |

|           |    | LONG | WOBD  | 2 -  |    |       |                  |                      |      |   |     |        |   |   |     |

|           |    | LONG | WORD  | 2    |    |       |                  |                      |      |   |     |        |   |   |     |

|           |    |      |       |      |    | 1 /   | ADDRI            |                      |      |   |     |        |   |   |     |

|     |    |     |        |     |    | 1 A | DDRES | S = 32 | BITS |   |   |   |   |   |     |

|-----|----|-----|--------|-----|----|-----|-------|--------|------|---|---|---|---|---|-----|

| 15  | 14 | 13  | 12     | 11  | 10 | 9   | 8     | 7      | 6    | 5 | 4 | 3 | 2 | 1 | 0   |

| MSB |    |     | RESS 0 | ) – |    |     | HIGH  |        | ۲    |   |   |   |   |   |     |

|     |    | NUU | NE00 0 | ,   |    |     | LOW   | ORDEF  | R    |   |   |   |   |   | LSB |

|     |    | ADD | RESS 1 | -   |    |     |       |        |      |   |   |   |   |   |     |

|     |    | ADD | RESS 2 | 2 - |    |     |       |        |      |   |   |   |   |   |     |

MSB = MOST SIGNIFICANT BIT LSB = LEAST SIGNIFICANT BIT

#### DECIMAL DATA

| 2 BINARY-CODED-DECIMAL DIGITS = 1 | BYTE |

|-----------------------------------|------|

|     |        |       |    |    |    | 0000 |     |   |     |     | - |   |     |     |   |

|-----|--------|-------|----|----|----|------|-----|---|-----|-----|---|---|-----|-----|---|

| 15  | 14     | 13    | 12 | 11 | 10 | 9    | 8   | 7 | 6   | 5   | 4 | 3 | 2   | 1   | 0 |

| MSD | )<br>E | BCD 0 |    |    | BC | :D 1 | LSD |   | BCI | D 2 |   |   | BCE | ) 3 |   |

|     | E      | BCD 4 |    |    | BC | D 5  |     |   | BCI | D 6 |   |   | BCE | )7  |   |

MSD = MOST SIGNIFICANT DIGIT

LSD = LEAST SIGNIFICANT DIGIT

#### Figure 2-6. Data Organization in Memory

MOTOROLA

#### M68000 8-/16-/32-BIT MICROPROCESSOR USER'S MANUAL

For More Information On This Product, Go to: www.freescale.com

| Opcode | Operation                                                                                                                                                                                                                                            | Syntax                                |

|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|

| RTE    | If supervisor state<br>then (SP) $\rightarrow$ SR; SP + 2 $\rightarrow$ SP; (SP) $\rightarrow$ PC;<br>SP + 4 $\rightarrow$ SP;<br>restore state and deallocate stack according to (SP)<br>else TRAP                                                  | RTE                                   |

| RTR    | $\begin{array}{l} (SP) \rightarrow CCR;  SP + 2 \rightarrow SP; \\ (SP) \rightarrow PC;  SP + 4 \rightarrow SP \end{array}$                                                                                                                          | RTR                                   |

| RTS    | $(SP) \rightarrow PC; SP + 4 \rightarrow SP$                                                                                                                                                                                                         | RTS                                   |

| SBCD   | $Destination_{10}-Source_{10}-X\toDestination$                                                                                                                                                                                                       | SBCD Dx,Dy<br>SBCD –(Ax),–(Ay)        |

| Scc    | If condition true then $1s \rightarrow Destination$ else $0s \rightarrow Destination$                                                                                                                                                                | Scc <ea></ea>                         |

| STOP   | If supervisor state then Immediate Data $\rightarrow$ SR; STOP else TRAP                                                                                                                                                                             | STOP # <data></data>                  |

| SUB    | Destination – Source $\rightarrow$ Destination                                                                                                                                                                                                       | SUB <ea>,Dn<br/>SUB Dn,<ea></ea></ea> |

| SUBA   | Destination – Source $\rightarrow$ Destination                                                                                                                                                                                                       | SUBA <ea>,An</ea>                     |

| SUBI   | Destination – Immediate Data $\rightarrow$ Destination                                                                                                                                                                                               | SUBI # <data>,<ea></ea></data>        |

| SUBQ   | Destination – Immediate Data $\rightarrow$ Destination                                                                                                                                                                                               | SUBQ # <data>,<ea></ea></data>        |

| SUBX   | Destination – Source – $X \rightarrow$ Destination                                                                                                                                                                                                   | SUBX Dx,Dy<br>SUBX –(Ax),–(Ay)        |

| SWAP   | Register [31:16] $\leftrightarrow$ Register [15:0]                                                                                                                                                                                                   | SWAP Dn                               |

| TAS    | Destination Tested $\rightarrow$ Condition Codes; 1 $\rightarrow$ bit 7 of Destination                                                                                                                                                               | TAS <ea></ea>                         |

| TRAP   | $\begin{array}{l} SSP-2 \rightarrow SSP; \mbox{ Format/Offset} \rightarrow (SSP); \\ SSP-4 \rightarrow SSP; \mbox{ PC} \rightarrow (SSP); \mbox{ SSP-2} \rightarrow SSP; \\ SR \rightarrow (SSP); \mbox{ Vector Address} \rightarrow PC \end{array}$ | TRAP # <vector></vector>              |

| TRAPV  | If V then TRAP                                                                                                                                                                                                                                       | TRAPV                                 |

| TST    | Destination Tested $\rightarrow$ Condition Codes                                                                                                                                                                                                     | TST <ea></ea>                         |

| UNLK   | An $\rightarrow$ SP; (SP) $\rightarrow$ An; SP + 4 $\rightarrow$ SP                                                                                                                                                                                  | UNLK An                               |

NOTE: d is direction, L or R.

# SECTION 3 SIGNAL DESCRIPTION

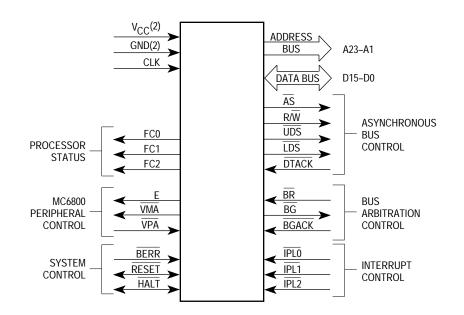

This section contains descriptions of the input and output signals. The input and output signals can be functionally organized into the groups shown in Figure 3-1 (for the MC68000, the MC68HC000 and the MC68010), Figure 3-2 (for the MC68HC001), Figure 3-3 (for the MC68EC000), Figure 3-4 (for the MC68008, 48-pin version), and Figure 3-5 (for the MC68008, 52-pin version). The following paragraphs provide brief descriptions of the signals and references (where applicable) to other paragraphs that contain more information about the signals.

#### NOTE

The terms **assertion** and **negation** are used extensively in this manual to avoid confusion when describing a mixture of "active-low" and "active-high" signals. The term assert or assertion is used to indicate that a signal is active or true, independently of whether that level is represented by a high or low voltage. The term negate or negation is used to indicate that a signal is inactive or false.

Figure 3-1. Input and Output Signals (MC68000, MC68HC000 and MC68010)

#### M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

#### Address Bus (A23–A0)

This 24-bit, unidirectional, three-state bus is capable of addressing 16 Mbytes of data. This bus provides the address for bus operation during all cycles except interrupt acknowledge cycles and breakpoint cycles. During interrupt acknowledge cycles, address lines A1, A2, and A3 provide the level number of the interrupt being acknowledged, and address lines A23–A4 and A0 are driven to logic high. In 16-Bit mode, A0 is always driven high.

#### MC68008 Address Bus

The unidirectional, three-state buses in the two versions of the **MC68008** differ from each other and from the other processor bus only in the number of address lines and the addressing range. The 20-bit address (A19–A0) of the 48-pin version provides a 1-Mbyte address space; the 52-pin version supports a 22-bit address (A21–A0), extending the address space to 4 Mbytes. During an interrupt acknowledge cycle, the interrupt level number is placed on lines A1, A2, and A3. Lines A0 and A4 through the most significant address line are driven to logic high.

### 3.2 DATA BUS (D15–D0; MC68008: D7–D0)

This bidirectional, three-state bus is the general-purpose data path. It is 16 bits wide in the all the processors except the **MC68008** which is 8 bits wide. The bus can transfer and accept data of either word or byte length. During an interrupt acknowledge cycle, the external device supplies the vector number on data lines D7–D0. The MC68EC000 and MC68HC001 use D7–D0 in 8-bit mode, and D15–D8 are undefined.

## 3.3 ASYNCHRONOUS BUS CONTROL

Asynchronous data transfers are controlled by the following signals: address strobe, read/write, upper and lower data strobes, and data transfer acknowledge. These signals are described in the following paragraphs.

#### Address Strobe (AS).

This three-state signal indicates that the information on the address bus is a valid address.

#### Read/Write ( $R/\overline{W}$ ).

This three-state signal defines the data bus transfer as a read or write cycle. The  $R/\overline{W}$  signal relates to the data strobe signals described in the following paragraphs.

### Upper And Lower Data Strobes (UDS, LDS).

These three-state signals and R/W control the flow of data on the data bus. Table 3-1 lists the combinations of these signals and the corresponding data on the bus. When the R/W line is high, the processor reads from the data bus. When the R/W line is low, the processor drives the data bus. In 8-bit mode,  $\overline{UDS}$  is always forced high and the LDS signal is used.

### **3.11 SIGNAL SUMMARY**

Table 3-4 summarizes the signals discussed in the preceding paragraphs.

|                              |                                                |              |                        | Н       | i-Z                  |

|------------------------------|------------------------------------------------|--------------|------------------------|---------|----------------------|

| Signal Name                  | Mnemonic                                       | Input/Output | Active State           | On HALT | On Bus<br>Relinquish |

| Address Bus                  | A0–A23                                         | Output       | High                   | Yes     | Yes                  |

| Data Bus                     | D0–D15                                         | Input/Output | High                   | Yes     | Yes                  |

| Address Strobe               | ĀS                                             | Output       | Low                    | No      | Yes                  |

| Read/Write                   | R/W                                            | Output       | Read-High<br>Write-Low | No      | Yes                  |

| Data Strobe                  | DS                                             | Output       | Low                    | No      | Yes                  |

| Upper and Lower Data Strobes | $\overline{\text{UDS}}, \overline{\text{LDS}}$ | Output       | Low                    | No      | Yes                  |

| Data Transfer Acknowledge    | DTACK                                          | Input        | Low                    | No      | No                   |

| Bus Request                  | BR                                             | Input        | Low                    | No      | No                   |

| Bus Grant                    | BG                                             | Output       | Low                    | No      | No                   |

| Bus Grant Acknowledge        | BGACK                                          | Input        | Low                    | No      | No                   |

| Interrupt Priority Level     | ĪPĒ0, ĪPĒ1,<br>ĪPĒ2                            | Input        | Low                    | No      | No                   |

| Bus Error                    | BERR                                           | Input        | Low                    | No      | No                   |

| Mode                         | MODE                                           | Input        | High                   | _       | -                    |

| Reset                        | RESET                                          | Input/Output | Low                    | No*     | No*                  |

| Halt                         | HALT                                           | Input/Output | Low                    | No*     | No*                  |

| Enable                       | E                                              | Output       | High                   | No      | No                   |

| Valid Memory Address         | VMA                                            | Output       | Low                    | No      | Yes                  |

| Valid Peripheral Address     | VPA                                            | Input        | Low                    | No      | No                   |

| Function Code Output         | FC0, FC1,<br>FC2                               | Output       | High                   | No      | Yes                  |

| Clock                        | CLK                                            | Input        | High                   | No      | No                   |

| Power Input                  | VCC                                            | Input        | _                      | _       | _                    |

| Ground                       | GND                                            | Input        | _                      |         | _                    |

| Table 3-4. | Signal | Summary |

|------------|--------|---------|

|------------|--------|---------|

\*Open drain.

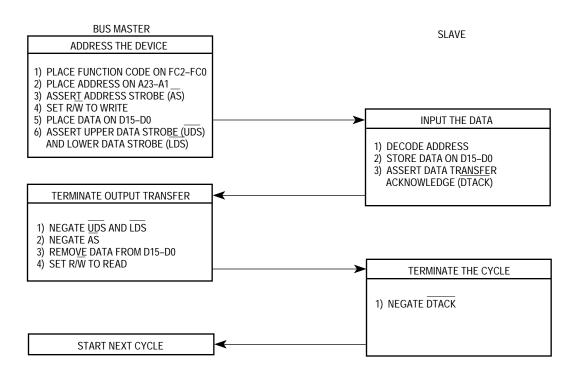

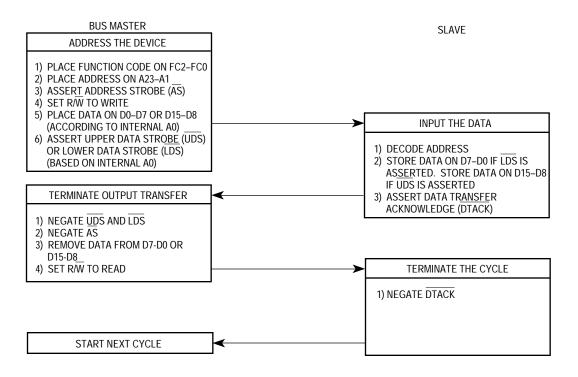

# SECTION 5 16-BIT BUS OPERATION

The following paragraphs describe control signal and bus operation for 16-bit bus operations during data transfer operations, bus arbitration, bus error and halt conditions, and reset operation. The 16-bit bus operation devices are the MC68000, MC68HC000, MC68010, and the MC68HC001 and MC68EC000 in 16-bit mode. The MC68HC001 and MC68EC000 select 16-bit mode by pulling mode high or leave it floating during reset.

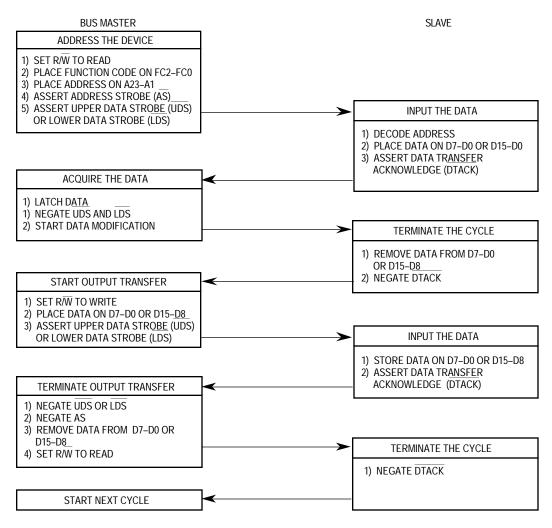

# **5.1 DATA TRANSFER OPERATIONS**

Transfer of data between devices involves the following signals:

- 1. Address bus A1 through highest numbered address line

- 2. Data bus D0 through D15

- 3. Control signals

The address and data buses are separate parallel buses used to transfer data using an asynchronous bus structure. In all cases, the bus master must deskew all signals it issues at both the start and end of a bus cycle. In addition, the bus master must deskew the acknowledge and data signals from the slave device.

The following paragraphs describe the read, write, read-modify-write, and CPU space cycles. The indivisible read-modify-write cycle implements interlocked multiprocessor communications. A CPU space cycle is a special processor cycle.

## 5.1.1 Read Cycle

During a read cycle, the processor receives either one or two bytes of data from the memory or from a peripheral device. If the instruction specifies a word or long-word operation, the MC68000, MC68HC000, MC68HC001, MC68EC000, or MC68010 processor reads both upper and lower bytes simultaneously by asserting both upper and lower data strobes. When the instruction specifies byte operation, the processor uses the internal A0 bit to determine which byte to read and issues the appropriate data strobe. When A0 equals zero, the upper data strobe is issued; when A0 equals one, the lower data strobe is issued. When the data is received, the processor internally positions the byte appropriately.

The word read-cycle flowchart is shown in Figure 5-1 and the byte read-cycle flowchart is shown in Figure 5-2. The read and write cycle timing is shown in Figure 5-3 and the word and byte read-cycle timing diagram is shown in Figure 5-4.

The word and byte write-cycle timing diagram and flowcharts in Figures 5-5, 5-6, and 5-7 applies directly to the MC68000, the MC68HC000, the MC68HC001 (in 16-bit mode), the MC68EC000 (in 16-bit mode), and the MC68010.

Figure 5-5. Word Write-Cycle Flowchart

STATE 7 On the falling edge of the clock entering S7, the processor negates  $\overline{AS}$ ,  $\overline{UDS}$ , or  $\overline{LDS}$ . As the clock rises at the end of S7, the processor places the address and data buses in the high-impedance state, and drives  $R/\overline{W}$  high. The device negates  $\overline{DTACK}$  or  $\overline{BERR}$  at this time.

### 5.1.3 Read-Modify-Write Cycle.

The read-modify-write cycle performs a read operation, modifies the data in the arithmetic logic unit, and writes the data back to the same address. The address strobe ( $\overline{AS}$ ) remains asserted throughout the entire cycle, making the cycle indivisible. The test and set (TAS) instruction uses this cycle to provide a signaling capability without deadlock between processors in a multiprocessing environment. The TAS instruction (the only instruction that uses the read-modify-write cycle) only operates on bytes. Thus, all read-modify-write cycles are byte operations. The read-modify-write flowchart shown in Figure 5-8 and the timing diagram in Figure 5-9, applies to the MC68000, the MC68HC000, the MC68HC001 (in 16-bit mode), the MC68EC000 (in 16-bit mode), and the MC68010.

Figure 5-8. Read-Modify-Write Cycle Flowchart

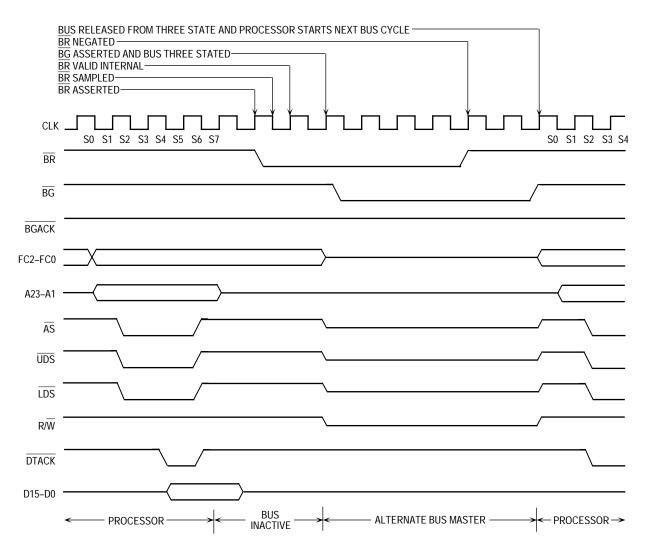

Figure 5-23. 2-Wire Bus Arbitration Timing Diagram—Bus Inactive

executing a reset instruction is ignored. Since the processor asserts the RESET signal for 124 clock cycles during execution of a reset instruction, an external reset should assert RESET for at least 132 clock periods.

# 5.6 THE RELATIONSHIP OF DTACK, BERR, AND HALT

To properly control termination of a bus cycle for a retry or a bus error condition, DTACK, BERR, and HALT should be asserted and negated on the rising edge of the processor clock. This relationship assures that when two signals are asserted simultaneously, the required setup time (specification #47, **Section 9 Electrical Characteristics**) for both of them is met during the same bus state. External circuitry should be designed to incorporate this precaution. A related specification, #48, can be ignored when DTACK, BERR, and HALT are asserted and negated on the rising edge of the processor clock.

The possible bus cycle termination can be summarized as follows (case numbers refer to Table 5-5).

| Normal Termination:    | $\overline{\text{DTACK}}$ is asserted. $\overline{\text{BERR}}$ and $\overline{\text{HALT}}$ remain negated (case 1).                                                                                                                                                    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Halt Termination:      | $\overline{\text{HALT}}$ is asserted coincident with or preceding $\overline{\text{DTACK}}$ , and $\overline{\text{BERR}}$ remains negated (case 2).                                                                                                                     |

| Bus Error Termination: | BERR is asserted in lieu of, coincident with, or preceding DTACK (case 3). In the MC68010, the late bus error also, BERR is asserted following DTACK (case 4). HALT remains negated and BERR is negated coincident with or after DTACK.                                  |

| Retry Termination:     | HALT and BERR asserted in lieu of, coincident with, or before DTACK (case 5). In the MC68010, the late retry also, BERR and HALT are asserted following DTACK (case 6). BERR is negated coincident with or after DTACK. HALT must be held at least one cycle after BERR. |

Table 5-1 shows the details of the resulting bus cycle termination in the M68000 microprocessors for various combinations of signal sequences.

| Case<br>No. | Control<br>Signal     |                | ted on<br>j Edge<br>tate | MC68000/MC68HC000/001<br>EC000/MC68008 Results                  | MC68010 Results                                                 |

|-------------|-----------------------|----------------|--------------------------|-----------------------------------------------------------------|-----------------------------------------------------------------|

|             |                       | Ν              | N+2                      |                                                                 |                                                                 |

| 1           | DTACK<br>BERR<br>HALT | A<br>NA<br>NA  | S<br>NA<br>X             | Normal cycle terminate and continue.                            | Normal cycle terminate and continue.                            |

| 2           | DTACK<br>BERR<br>HALT | A<br>NA<br>A/S | S<br>NA<br>S             | Normal cycle terminate and halt.<br>Continue when HALT negated. | Normal cycle terminate and halt.<br>Continue when HALT negated. |

| 3           | DTACK<br>BERR<br>HALT | X<br>A<br>NA   | X<br>S<br>NA             | Terminate and take bus error trap.                              | Terminate and take bus error trap.                              |

| 4           | DTACK<br>BERR<br>HALT | A<br>NA<br>NA  | S<br>A<br>NA             | Normal cycle terminate and continue.                            | Terminate and take bus error trap.                              |

| 5           | DTACK<br>BERR<br>HALT | X<br>A<br>A/S  | X<br>S<br>S              | Terminate and retry when HALT removed.                          | Terminate and retry when HALT removed.                          |

| 6           | DTACK<br>BERR<br>HALT | A<br>NA<br>NA  | S<br>A<br>A              | Normal cycle terminate and continue.                            | Terminate and retry when HALT removed.                          |

#### Table 5-1. DTACK, BERR, and HALT Assertion Results

LEGEND:

N — The number of the current even bus state (e.g., S4, S6, etc.)

- A Signal asserted in this bus state

- NA Signal not asserted in this bus state

- X Don't care

- S  $\,-\,$  Signal asserted in preceding bus state and remains asserted in this state

NOTE: All operations are subject to relevant setup and hold times.

The negation of  $\overline{\text{BERR}}$  and  $\overline{\text{HALT}}$  under several conditions is shown in Table 5-6. ( $\overline{\text{DTACK}}$  is assumed to be negated normally in all cases; for reliable operation, both  $\overline{\text{DTACK}}$  and  $\overline{\text{BERR}}$  should be negated when address strobe is negated).

### EXAMPLE A:

A system uses a watchdog timer to terminate accesses to unused address space. The timer asserts BERR after timeout (case 3).

### EXAMPLE B:

A system uses error detection on random-access memory (RAM) contents. The system designer may:

- 1. Delay DTACK until the data is verified. If data is invalid, return BERR and HALT simultaneously to retry the error cycle (case 5).

- 2. Delay DTACK until the data is verified. If data is invalid, return BERR at the same time as DTACK (case 3).

- 3. For an MC68010, return DTACK before data verification. If data is invalid, assert BERR and HALT to retry the error cycle (case 6).

A signed divide (DIVS) or unsigned divide (DIVU) instruction forces an exception if a division operation is attempted with a divisor of zero.

### 6.3.6 Illegal and Unimplemented Instructions

Illegal instruction is the term used to refer to any of the word bit patterns that do not match the bit pattern of the first word of a legal M68000 instruction. If such an instruction is fetched, an illegal instruction exception occurs. Motorola reserves the right to define instructions using the opcodes of any of the illegal instructions. Three bit patterns always force an illegal instruction trap on all M68000-Family-compatible microprocessors. The patterns are: \$4AFA, \$4AFB, and \$4AFC. Two of the patterns, \$4AFA and \$4AFB, are reserved for Motorola system products. The third pattern, \$4AFC, is reserved for customer use (as the take illegal instruction trap (ILLEGAL) instruction).

#### NOTE

In addition to the previously defined illegal instruction opcodes, the MC68010 defines eight breakpoint (BKPT) instructions with the bit patterns \$4848–\$484F. These instructions cause the processor to enter illegal instruction exception processing as usual. However, a breakpoint acknowledge bus cycle, in which the function code lines (FC2–FC0) are high and the address lines are all low, is also executed before the stacking operations are performed. The processor does not accept or send any data during this cycle. Whether the breakpoint acknowledge cycle is terminated with a DTACK, BERR, or VPA signal, the processor continues with the illegal instruction processing. The purpose of this cycle is to provide a software breakpoint that signals to external hardware when it is executed.

Word patterns with bits 15–12 equaling 1010 or 1111 are distinguished as unimplemented instructions, and separate exception vectors are assigned to these patterns to permit efficient emulation. Opcodes beginning with bit patterns equaling 1111 (line F) are implemented in the MC68020 and beyond as coprocessor instructions. These separate vectors allow the operating system to emulate unimplemented instructions in software.

Exception processing for illegal instructions is similar to that for traps. After the instruction is fetched and decoding is attempted, the processor determines that execution of an illegal instruction is being attempted and starts exception processing. The exception stack frame for group 2 is then pushed on the supervisor stack, and the illegal instruction vector is fetched.

protect memory contents from erroneous accesses. Only an external reset operation can restart a halted processor.

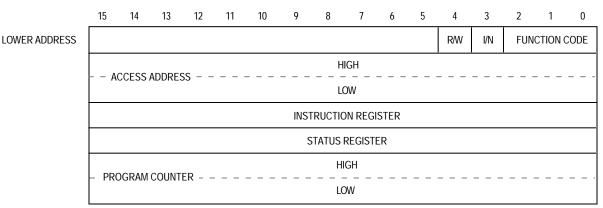

R/W (Read/Write): Write=0, Read=1. I/N (Instruction/Not): Instruction=0, Not=1

#### Figure 6-7. Supervisor Stack Order for Bus or Address Error Exception

**6.3.9.2 BUS ERROR (MC68010)**. Exception processing for a bus error follows a slightly different sequence than the sequence for group 1 and 2 exceptions. In addition to the four steps executed during exception processing for all other exceptions, 22 words of additional information are placed on the stack. This additional information describes the internal state of the processor at the time of the bus error and is reloaded by the RTE instruction to continue the instruction that caused the error. Figure 6-8 shows the order of the stacked information.

|                            |                 | Destination     |                 |                 |                 |                        |                  |                  |                  |  |  |  |  |

|----------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|------------------------|------------------|------------------|------------------|--|--|--|--|

| Source                     | Dn              | An              | (An)            | (An)+           | –(An)           | (d <sub>16</sub> , An) | (dგ, An, Xn)*    | (xxx).W          | (xxx).L          |  |  |  |  |

| Dn                         | <b>8</b> (2/0)  | <b>8</b> (2/0)  | <b>16</b> (2/2) | <b>16</b> (2/2) | <b>16</b> (2/2) | <b>24</b> (4/2)        | <b>26</b> (4/2)  | <b>24</b> (4/2)  | <b>32</b> (6/2)  |  |  |  |  |

| An                         | <b>8</b> (2/0)  | <b>8</b> (2/0)  | <b>16</b> (2/2) | <b>16</b> (2/2) | <b>16</b> (2/2) | <b>24</b> (4/2)        | <b>26</b> (4/2)  | <b>24</b> (4/2)  | <b>32</b> (6/2)  |  |  |  |  |

| (An)                       | <b>16</b> (4/0) | <b>16</b> (4/0) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>32</b> (6/2)        | <b>34</b> (6/2)  | <b>32</b> (6/2)  | <b>40</b> (8/2)  |  |  |  |  |

| (An)+                      | <b>16</b> (4/0) | <b>16</b> (4/0) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>32</b> (6/2)        | <b>34</b> (6/2)  | <b>32</b> (6/2)  | <b>40</b> (8/2)  |  |  |  |  |

| –(An)                      | <b>18</b> (4/0) | <b>18</b> (4/0) | <b>26</b> (4/2) | <b>26</b> (4/2) | <b>26</b> (4/2) | <b>34</b> (6/2)        | <b>32</b> (6/2)  | <b>34</b> (6/2)  | <b>42</b> (8/2)  |  |  |  |  |

| (d <sub>16</sub> , An)     | <b>24</b> (6/0) | <b>24</b> (6/0) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>40</b> (8/2)        | <b>42</b> (8/2)  | <b>40</b> (8/2)  | <b>48</b> (10/2) |  |  |  |  |

| (d g, An, Xn)*             | <b>26</b> (6/0) | <b>26</b> (6/0) | <b>34</b> (6/2) | <b>34</b> (6/2) | <b>34</b> (6/2) | <b>42</b> (8/2)        | <b>44</b> (8/2)  | <b>42</b> (8/2)  | <b>50</b> (10/2) |  |  |  |  |

| (xxx).W                    | <b>24</b> (6/0) | <b>24</b> (6/0) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>40</b> (8/2)        | <b>42</b> (8/2)  | <b>40</b> (8/2)  | <b>48</b> (10/2) |  |  |  |  |

| (xxx).L                    | <b>32</b> (8/0) | <b>32</b> (8/0) | <b>40</b> (8/2) | <b>40</b> (8/2) | <b>40</b> (8/2) | <b>48</b> (10/2)       | <b>50</b> (10/2) | <b>48</b> (10/2) | <b>56</b> (12/2) |  |  |  |  |

| (d <sub>16</sub> , PC)     | <b>24</b> (6/0) | <b>24</b> (6/0) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>32</b> (6/2) | <b>40</b> (8/2)        | <b>42</b> (8/2)  | <b>40</b> (8/2)  | <b>48</b> (10/2) |  |  |  |  |

| (d <sub>8</sub> , PC, Xn)* | <b>26</b> (6/0) | <b>26</b> (6/0) | <b>34</b> (6/2) | <b>34</b> (6/2) | <b>34</b> (6/2) | <b>42</b> (8/2)        | <b>44</b> (8/2)  | <b>42</b> (8/2)  | <b>50</b> (10/2) |  |  |  |  |

| # <data></data>            | <b>16</b> (4/0) | <b>16</b> (4/0) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>24</b> (4/2) | <b>32</b> (6/2)        | <b>34</b> (6/2)  | <b>32</b> (6/2)  | <b>40</b> (8/2)  |  |  |  |  |

Table 7-3. Move Word Instruction Execution Times

\*The size of the index register (Xn) does not affect execution time.

|                            | Destination      |                  |                  |                  |                  |                        |                  |                  |                  |  |  |  |  |

|----------------------------|------------------|------------------|------------------|------------------|------------------|------------------------|------------------|------------------|------------------|--|--|--|--|

| Source                     | Dn               | An               | (An)             | (An)+            | –(An)            | (d <sub>16</sub> , An) | (dგ, An, Xn)*    | (xxx).W          | (xxx).L          |  |  |  |  |

| Dn                         | 8(2/0)           | 8(2/0)           | <b>24</b> (2/4)  | <b>24</b> (2/4)  | <b>24</b> (2/4)  | <b>32</b> (4/4)        | <b>34</b> (4/4)  | <b>32</b> (4/4)  | <b>40</b> (6/4)  |  |  |  |  |

| An                         | 8(2/0)           | 8(2/0)           | <b>24</b> (2/4)  | <b>24</b> (2/4)  | <b>24</b> (2/4)  | <b>32</b> (4/4)        | <b>34</b> (4/4)  | <b>32</b> (4/4)  | <b>40</b> (6/4)  |  |  |  |  |

| (An)                       | 24(6/0)          | 24(6/0)          | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>48</b> (8/4)        | <b>50</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4) |  |  |  |  |

| (An)+                      | <b>24</b> (6/0)  | <b>24</b> (6/0)  | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>48</b> (8/4)        | <b>50</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4) |  |  |  |  |

| –(An)                      | <b>26</b> (6/0)  | <b>26</b> (6/0)  | <b>42</b> (6/4)  | <b>42</b> (6/4)  | <b>42</b> (6/4)  | <b>50</b> (8/4)        | <b>52</b> (8/4)  | <b>50</b> (8/4)  | <b>58</b> (10/4) |  |  |  |  |

| (d <sub>16</sub> , An)     | <b>32</b> (8/0)  | <b>32</b> (8/0)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4)       | <b>58</b> (10/4) | <b>56</b> (10/4) | <b>64</b> (12/4) |  |  |  |  |

| (d g, An, Xn)*             | <b>34</b> (8/0)  | <b>34</b> (8/0)  | <b>50</b> (8/4)  | <b>50</b> (8/4)  | <b>50</b> (8/4)  | <b>58</b> (10/4)       | <b>60</b> (10/4) | <b>58</b> (10/4) | <b>66</b> (12/4) |  |  |  |  |

| (xxx).W                    | <b>32</b> (8/0)  | <b>32</b> (8/0)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4)       | <b>58</b> (10/4) | <b>56</b> (10/4) | <b>64</b> (12/4) |  |  |  |  |

| (xxx).L                    | <b>40</b> (10/0) | <b>40</b> (10/0) | <b>56</b> (10/4) | <b>56</b> (10/4) | <b>56</b> (10/4) | <b>64</b> (12/4)       | <b>66</b> (12/4) | <b>64</b> (12/4) | <b>72</b> (14/4) |  |  |  |  |

| (d <sub>16</sub> , PC)     | <b>32</b> (8/0)  | <b>32</b> (8/0)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4)       | <b>58</b> (10/4) | <b>56</b> (10/4) | <b>64</b> (12/4) |  |  |  |  |

| (d <sub>8</sub> , PC, Xn)* | <b>34</b> (8/0)  | <b>34</b> (8/0)  | <b>50</b> (8/4)  | <b>50</b> (8/4)  | <b>50</b> (8/4)  | <b>58</b> (10/4)       | <b>60</b> (10/4) | <b>58</b> (10/4) | <b>66</b> (12/4) |  |  |  |  |

| # <data></data>            | <b>24</b> (6/0)  | <b>24</b> (6/0)  | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>40</b> (6/4)  | <b>48</b> (8/4)        | <b>50</b> (8/4)  | <b>48</b> (8/4)  | <b>56</b> (10/4) |  |  |  |  |

Table 7-4. Move Long Instruction Execution Times

\*The size of the index register (Xn) does not affect execution time.

## 7.3 STANDARD INSTRUCTION EXECUTION TIMES

The numbers of clock periods shown in Table 7-5 indicate the times required to perform the operations, store the results, and read the next instruction. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, and the number of write cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

#### For More Information On This Product, Go to: www.freescale.com

| Instruction   | Size              | Register           | Memory           | Register→<br>Destination** | Source**→<br>Register |

|---------------|-------------------|--------------------|------------------|----------------------------|-----------------------|

| ANDI to CCR   | _                 | <b>16</b> (2/0)    | _                | _                          |                       |

| ANDI to SR    | _                 | <b>16</b> (2/0)    | _                | _                          |                       |

| СНК           | _                 | <b>8</b> (1/0)+    | _                | _                          |                       |

| EORI to CCR   | _                 | <b>16</b> (2/0)    | _                | _                          |                       |

| EORI to SR    | _                 | <b>16</b> (2/0)    | —                | _                          | _                     |

| EXG           | _                 | <b>6</b> (1/0)     | _                | _                          | _                     |

| EXT           | Word              | <b>4</b> (1/0)     | _                | _                          |                       |

|               | Long              | <b>4</b> (1/0)     | —                | _                          | _                     |

| LINK          | —                 | <b>16</b> (2/2)    | —                | —                          | _                     |

| MOVE from CCR | _                 | <b>4</b> (1/0)     | 8(1/1)+*         | _                          |                       |

| MOVE to CCR   | —                 | <b>12</b> (2/0)    | <b>12</b> (2/0)+ | _                          | _                     |

| MOVE from SR  | —                 | <b>4</b> (1/0)     | 8(1/1)+*         | _                          | —                     |

| MOVE to SR    | —                 | <b>12</b> (2/0)    | <b>12</b> (2/0)+ | _                          | _                     |

| MOVE from USP | —                 | <b>6</b> (1/0)     | —                | —                          | —                     |

| MOVE to USP   | —                 | <b>6</b> (1/0)     | —                | —                          | _                     |

| MOVEC         | —                 | _                  | —                | <b>10</b> (2/0)            | <b>12</b> (2/0)       |

| MOVEP         | Word              | _                  | —                | 16(2/2)                    | <b>16</b> (4/0)       |

|               | Long              | _                  | —                | <b>24</b> (2/4)            | <b>24</b> (6/0)       |

| NOP           | —                 | <b>4</b> (1/0)     | —                | —                          | —                     |

| ORI to CCR    | —                 | <b>16</b> (2/0)    | —                | —                          | —                     |

| ORI to SR     | —                 | <b>16</b> (2/0)    | _                | —                          | —                     |

| RESET         | —                 | <b>130</b> (1/0)   | —                | —                          | —                     |

| RTD           | —                 | <b>16</b> (4/0)    | —                | —                          | —                     |

| RTE           | Short             | <b>24</b> (6/0)    | _                | —                          | —                     |

|               | Long, Retry Read  | <b>112</b> (27/10) | —                | —                          | —                     |

|               | Long, Retry Write | <b>112</b> (26/1)  | —                | —                          | —                     |

|               | Long, No Retry    | <b>110</b> (26/0)  | _                | —                          | _                     |

| RTR           | —                 | <b>20</b> (5/0)    |                  | —                          | _                     |

| RTS           |                   | <b>16</b> (4/0)    |                  | _                          |                       |

| STOP          | —                 | <b>4</b> (0/0)     | _                | —                          | _                     |

| SWAP          | —                 | <b>4</b> (1/0)     |                  | —                          | _                     |

| TRAPV         | _                 | <b>4</b> (1/0)     | _                | _                          | _                     |

| UNLK          | _                 | <b>12</b> (3/0)    | _                | _                          | _                     |

#### Table 9-18. Miscellaneous Instruction Execution Times

+Add effective address calculation time.

+Use nonfetching effective address calculation time.

\*\*Source or destination is a memory location for the MOVEP instruction and a control register for the MOVEC instruction.

9-12

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

MOTOROLA

#### For More Information On This Product, Go to: www.freescale.com

| Package | T <sub>A</sub> Range                        | <sup>θ</sup> Jc<br>(°C/W) | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Min. | Tj (°C)<br>@ T <sub>A</sub> Min. | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Max. | T <sub>J</sub> (°C)<br>@ T <sub>A</sub> Max. |

|---------|---------------------------------------------|---------------------------|---------------------------------------------|----------------------------------|---------------------------------------------|----------------------------------------------|

| L/LC    | 0°C to 70°C<br>-40°C to 85°C<br>0°C to 85°C | 15<br>15<br>15            | 1.5<br>1.7<br>1.5                           | 23<br>-14<br>23                  | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103                             |

| Р       | 0°C to 70°C                                 | 15                        | 1.5                                         | 23                               | 1.2                                         | 88                                           |

| R/RC    | 0°C to 70°C<br>-40°C to 85°C<br>0°C to 85°C | 15<br>15<br>15            | 1.5<br>1.7<br>1.5                           | 23<br>-14<br>23                  | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103                             |

| FN      | 0°C to 70°C                                 | 25                        | 1.5                                         | 38                               | 1.2                                         | 101                                          |

# Table 10-1. Power Dissipation and Junction Temperature vs Temperature $(\theta J C = \theta J A)$

NOTE: Table does not include values for the MC68000 12F.

Does not apply to the MC68HC000, MC68HC001, and MC68EC000.

# Table 10-2. Power Dissipation and Junction Temperature vs Temperature ( ${}^{\theta}JC \neq {}^{\theta}JC$ )

| Package | T <sub>A</sub> Range                        | <sup>θ</sup> JA<br>(°C/W) | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Min. | T <sub>J</sub> (°C)<br>@ T <sub>A</sub> Min. | P <sub>D</sub> (W)<br>@ T <sub>A</sub> Max. | T <sub>J</sub> (°C)<br>@ T <sub>A</sub> Max. |

|---------|---------------------------------------------|---------------------------|---------------------------------------------|----------------------------------------------|---------------------------------------------|----------------------------------------------|

| L/LC    | 0°C to 70°C<br>-40°C to 85°C<br>0°C to 85°C | 30<br>30<br>30            | 1.5<br>1.7<br>1.5                           | 23<br>-14<br>23                              | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103                             |

| Р       | 0°C to 70°C                                 | 30                        | 1.5                                         | 23                                           | 1.2                                         | 88                                           |

| R/RC    | 0°C to 70°C<br>-40°C to 85°C<br>0°C to 85°C | 33<br>33<br>33            | 1.5<br>1.7<br>1.5                           | 23<br>-14<br>23                              | 1.2<br>1.2<br>1.2                           | 88<br>103<br>103                             |

| FN      | 0°C to 70°C                                 | 40                        | 1.5                                         | 38                                           | 1.2                                         | 101                                          |

NOTE: Table does not include values for the MC68000 12F.

Does not apply to the MC68HC000, MC68HC001, and MC68EC000.

Values for thermal resistance presented in this manual, unless estimated, were derived using the procedure described in Motorola Reliability Report 7843 "Thermal Resistance Measurement Method for MC68XXX Microcomponent Devices" and are provided for design purposes only. Thermal measurements are complex and dependent on procedure and setup. User-derived values for thermal resistance may differ.

## **10.4 CMOS CONSIDERATIONS**

The MC68HC000, MC68HC001, and MC68EC000, with it significantly lower power consumption, has other considerations. The CMOS cell is basically composed of two complementary transistors (a P channel and an N channel), and only one transistor is turned on while the cell is in the steady state. The active P-channel transistor sources current when the output is a logic high and presents a high impedance when the output is logic low. Thus, the overall result is extremely low power consumption because no power

### 10.6 MC68000/68008/68010 DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub>=5.0 VDC $\pm 5\%$ ; GND=0 VDC; T<sub>A</sub>=T<sub>L</sub> TO T<sub>H</sub>)

| Characteristic                                                                                                                                                                                                                                                                       | Symbol             | Min                          | Max                      | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------------------------------|--------------------------|------|

| Input High Voltage                                                                                                                                                                                                                                                                   | VIH                | 2.0                          | VCC                      | V    |

| Input Low Voltage                                                                                                                                                                                                                                                                    | VIL                | GND-0.3                      | 0.8                      | V    |

| Input Leakage Current     BERR, BGACK, BR, DTACK, CLK, IPL0—IPL2, VPA       @ 5.25 V     HALT, RESET                                                                                                                                                                                 | ١N                 |                              | 2.5<br>20                | μA   |

| Three-State (Off State) Input Current $\overline{\text{AS}}$ , A1—A23, D0—D15, FC0—FC2,@ 2.4 V/0.4 V $\overline{\text{LDS}}$ , R/ $\overline{\text{W}}$ , $\overline{\text{UDS}}$ , $\overline{\text{VMA}}$                                                                          | ITSI               |                              | 20                       | μA   |

| $ \begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                | VOH                | V <sub>CC</sub> -0.75<br>2.4 | <br>2.4                  | V    |

| Output Low Voltage         HALT           (I <sub>OL</sub> = 1.6 mA)         HALT           (I <sub>OL</sub> = 3.2 mA)         A1—A23, BG, FC0-FC2           (I <sub>OL</sub> = 5.0 mA)         RESET           (I <sub>OL</sub> = 5.3 mA)         E, AS, D0—D15, LDS, R/W, UDS, VMA | V <sub>OL</sub>    |                              | 0.5<br>0.5<br>0.5<br>0.5 | V    |

| Power Dissipation (see POWER CONSIDERATIONS)                                                                                                                                                                                                                                         | P <sub>D</sub> *** | _                            | _                        | W    |

| Capacitance (V <sub>in</sub> =0 V, T <sub>A</sub> =25°C, Frequency=1 MHz)**                                                                                                                                                                                                          | C <sub>in</sub>    | _                            | 20.0                     | pF   |

| Load Capacitance HALT<br>All Others                                                                                                                                                                                                                                                  | CL                 |                              | 70<br>130                | pF   |

\*With external pullup resistor of 1.1  $\Omega$ .

\*\*Capacitance is periodically sampled rather than 100% tested.

\*\*\*During normal operation, instantaneous V<sub>CC</sub> current requirements may be as high as 1.5 A.

### 10.12 AC ELECTRICAL SPECIFICATIONS — BUS ARBITRATION (VCC=5.0

VDC±5%; GND=0 VDC, T<sub>A</sub>=T<sub>L</sub> TO T<sub>H</sub>; See Figure s 10-7 – 10-11) (Applies To All Processors Except The MC68EC000)

| Num              | Characteristic                                                                                                                                | 8 N | /Hz*        | 10 1 | MHz*        | 12.5 | MHz*        |     | 7 MHz<br>2F | 16  | MHz         | 20 N | ſHz⁼        | Unit        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|------|-------------|------|-------------|-----|-------------|-----|-------------|------|-------------|-------------|

|                  |                                                                                                                                               | Min | Max         | Min  | Max         | Min  | Max         | Min | Max         | Min | Max         | Min  | Max         |             |

| 7                | Clock High to Address, Data<br>Bus High Impedance<br>(Maximum)                                                                                |     | 80          |      | 70          |      | 60          |     | 50          |     | 50          | _    | 42          | ns          |

| 16               | Clock High to Control Bus<br>High Impedance                                                                                                   | -   | 80          | —    | 70          | —    | 60          | _   | 50          | —   | 50          | —    | 42          | ns          |

| 33               | Clock High to BG Asserted                                                                                                                     | —   | 62          | _    | 50          | _    | 40          | 0   | 40          | 0   | 30          | 0    | 25          | ns          |

| 34               | Clock High to BG Negated                                                                                                                      | -   | 62          | _    | 50          |      | 40          | 0   | 40          | 0   | 30          | 0    | 25          | ns          |

| 35               | BR Asserted to BG Asserted                                                                                                                    | 1.5 | 3.5         | 1.5  | 3.5         | 1.5  | 3.5         | 1.5 | 3.5         | 1.5 | 3.5         | 1.5  | 3.5         | Clks        |

| 36 <sup>1</sup>  | BR Negated to BG Negated                                                                                                                      | 1.5 | 3.5         | 1.5  | 3.5         | 1.5  | 3.5         | 1.5 | 3.5         | 1.5 | 3.5         | 1.5  | 3.5         | Clks        |

| 37               | BGACK Asserted to BG<br>Negated                                                                                                               | 1.5 | 3.5         | 1.5  | 3.5         | 1.5  | 3.5         | 1.5 | 3.5         | 1.5 | 3.5         | 1.5  | 3.5         | Clks        |

| 37A <sup>2</sup> | BGACK Asserted to BR<br>Negated                                                                                                               | 20  | 1.5<br>Clks | 20   | 1.5<br>Clks | 20   | 1.5<br>Clks | 10  | 1.5<br>Clks | 10  | 1.5<br>Clks | 10   | 1.5<br>Clks | Clks/<br>ns |

| 38               | BG Asserted to Control,<br>Address, Data Bus High<br>Impedance (AS Negated)                                                                   |     | 80          |      | 70          |      | 60          | _   | 50          | _   | 50          | _    | 42          | ns          |

| 39               | BG Width Negated                                                                                                                              | 1.5 |             | 1.5  | _           | 1.5  |             | 1.5 | _           | 1.5 | _           | 1.5  | _           | Clks        |

| 46               | BGACK Width Low                                                                                                                               | 1.5 |             | 1.5  | _           | 1.5  |             | 1.5 | _           | 1.5 | —           | 1.5  | _           | Clks        |

| 47               | Asynchronous Input Setup<br>Time                                                                                                              | 10  | —           | 10   | _           | 10   | —           | 5   | —           | 5   | —           | 5    | _           | ns          |

| 57               | $\begin{array}{c} \overline{BGACK} \text{ Negated to } \overline{AS}, \overline{DS}, \\ \overline{R}/\overline{W} \text{ Driven} \end{array}$ | 1.5 | —           | 1.5  | —           | 1.5  | —           | 1.5 | —           | 1.5 | —           | 1.5  |             | Clks        |

| 57A              | BGACK Negated to FC, VMA                                                                                                                      | 1   | —           | 1    | —           | 1    | —           | 1   | —           | 1   | —           | 1    |             | Clks        |

| 58 <sup>1</sup>  | $\overline{BR}$ Negated to $\overline{AS}$ , $\overline{DS}$ , $R/\overline{W}$ Driven                                                        | 1.5 | —           | 1.5  | —           | 1.5  | —           | 1.5 | —           | 1.5 | —           | 1.5  | _           | Clks        |

| 58A <sup>1</sup> | BR Negated to FC, VMA<br>Driven                                                                                                               | 1   | —           | 1    | —           | 1    | —           | 1   | —           | 1   |             | 1    | —           | Clks        |

\*These specifications represent improvement over previously published specifications for the 8-, 10-, and 12.5-MHz MC68000 and are valid only for product bearing date codes of 8827 and later.

\*\* Applies only to the MC68HC000 and MC68HC001.

NOTES:

- 1. Setup time for the synchronous inputs BGACK, IPL0-IPL2, and VPA guarantees their recognition at the next falling edge of the clock.

- 2. BR need fall at this time only in order to insure being recognized at the end of the bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 volt and a high voltage of 2.0 volts, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall will be lienar between 0.8 volt and 2.0 volts.

- 4. The processor will negate BG and begin driving the bus again if external arbitration logic negates BR before asserting BGACK.

- 5. The minimum value must be met to guarantee proper operation. If the maximum value is exceeded, BG may be reasserted.

NOTES:

- 1. Setup time for the asynchronous inputs IPL2–IPL0 and AVEC (#47) guarantees their recognition at the next falling edge of the clock.

- 2. BR need fall at this time only to insure being recognized at the end of the bus cycle.

- 3. Timing measurements are referenced to and from a low voltage of 0.8 V and a high voltage of 2.0 V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is linear between 0.8 V and 2.0 V.

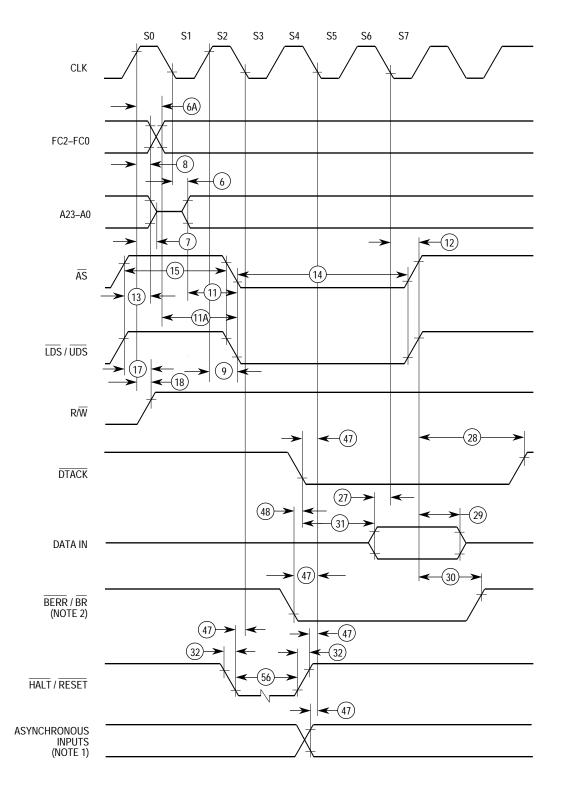

#### Figure 10-12. MC68EC000 Read Cycle Timing Diagram

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL For More Information On This Product, Go to: www.freescale.com interrupt service routine can be located anywhere within the supervisor program address space because the user assigns the vectors in the vector table.

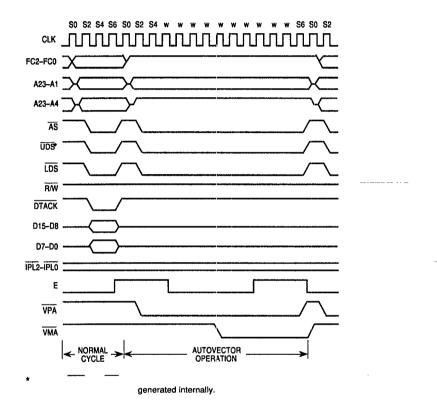

Since VMA is asserted during an autovector operation, care should be taken to prevent an unintended access to the device. An unintended access could occur if the peripheral address were on the address bus during the autovector operation.

Figure B-6. Autovector Operation Timing Diagram

B