# E·XFL

#### NXP USA Inc. - MC68HC000CRC10 Datasheet

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Obsolete                                                               |

|---------------------------------|------------------------------------------------------------------------|

| Core Processor                  | EC000                                                                  |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                         |

| Speed                           | 10MHz                                                                  |

| Co-Processors/DSP               | -                                                                      |

| RAM Controllers                 | -                                                                      |

| Graphics Acceleration           | No                                                                     |

| Display & Interface Controllers | -                                                                      |

| Ethernet                        | -                                                                      |

| SATA                            | -                                                                      |

| USB                             | -                                                                      |

| Voltage - I/O                   | 5.0V                                                                   |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                      |

| Security Features               | -                                                                      |

| Package / Case                  | 68-BCPGA                                                               |

| Supplier Device Package         | 68-PGA (26.92x26.92)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc68hc000crc10 |

|                                 |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## LIST OF ILLUSTRATIONS (Continued)

| Figure<br>Number | Title                                                      | Page<br>Number |

|------------------|------------------------------------------------------------|----------------|

| 5-15             | 3-Wire Bus Arbitration Timing Diagram                      |                |

|                  | (NA to 48-Pin MC68008 and MC68EC000                        | 5-13           |

| 5-16             | 2-Wire Bus Arbitration Timing Diagram                      | 5-14           |

| 5-17             | External Asynchronous Signal Synchronization               | 5-16           |

| 5-18             | Bus Arbitration Unit State Diagrams                        |                |

| 5-19             | 3-Wire Bus Arbitration Timing Diagram—Processor Active     | 5-18           |

| 5-20             | 3-Wire Bus Arbitration Timing Diagram—Bus Active           | 5-19           |

| 5-21             | 3-Wire Bus Arbitration Timing Diagram—Special Case         |                |

| 5-22             | 2-Wire Bus Arbitration Timing Diagram—Processor Active     | 5-21           |

| 5-23             | 2-Wire Bus Arbitration Timing Diagram—Bus Active           |                |

| 5-24             | 2-Wire Bus Arbitration Timing Diagram—Special Case         | 5-23           |

| 5-25             | Bus Error Timing Diagram                                   |                |

| 5-26             | Delayed Bus Error Timing Diagram (MC68010)                 | 5-25           |

| 5-27             | Retry Bus Cycle Timing Diagram                             |                |

| 5-28             | Delayed Retry Bus Cycle Timing Diagram                     | 5-27           |

| 5-29             | Halt Operation Timing Diagram                              | 5-28           |

| 5-30             | Reset Operation Timing Diagram                             | 5-29           |

| 5-31             | Fully Asynchronous Read Cycle                              | 5-32           |

| 5-32             | Fully Asynchronous Write Cycle                             | 5-33           |

| 5-33             | Pseudo-Asynchronous Read Cycle                             | 5-34           |

| 5-34             | Pseudo-Asynchronous Write Cycle                            |                |

| 5-35             | Synchronous Read Cycle                                     |                |

| 5-36             | Synchronous Write Cycle                                    | 5-38           |

| 5-37             | Input Synchronizers                                        | 5-38           |

| 6-1              | Exception Vector Format                                    |                |

| 6-2              | Peripheral Vector Number Format                            |                |

| 6-3              | Address Translated from 8-Bit Vector Number                |                |

| 6-4              | Exception Vector Address Calculation (MC68010)             | 6-5            |

| 6-5              | Group 1 and 2 Exception Stack Frame                        |                |

| 6-6              | MC68010 Stack Frame                                        |                |

| 6-7              | Supervisor Stack Order for Bus or Address Error Exception  | 6-17           |

| 6-8              | Exception Stack Order (Bus and Address Error)              |                |

| 6-9              | Special Status Word Format                                 | 6-19           |

| 10-1             | MC68000 Power Dissipation (PD) vs Ambient Temperature (TA) |                |

| 10-2             | Drive Levels and Test Points for AC Specifications         |                |

| 10-3             | Clock Input Timing Diagram                                 |                |

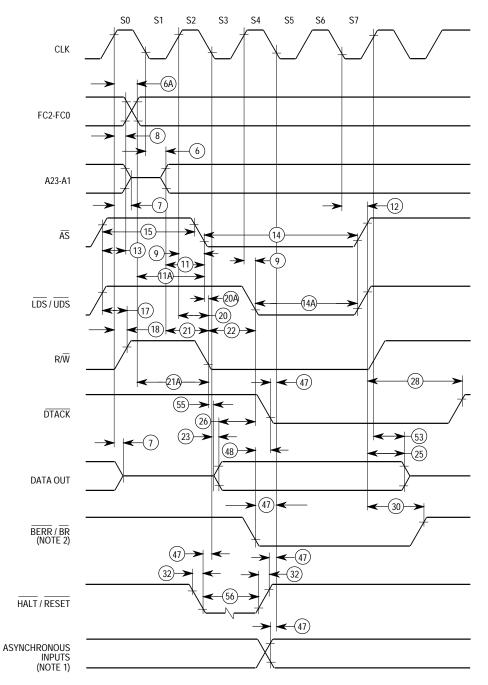

| 10-4             | Read Cycle Timing Diagram                                  |                |

| 10-5             | Write Cycle Timing Diagram                                 |                |

| 10-6             | MC68000 to M6800 Peripheral Timing Diagram (Best Case)     | 10-16          |

## LIST OF TABLES

| Table<br>Number                                                                                             | Title                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Page<br>Number                                                                           |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 2-1                                                                                                         | Data Addressing Modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 2-4                                                                                      |

| 2-2                                                                                                         | Instruction Set Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2-11                                                                                     |

| 3-1<br>3-2<br>3-3<br>3-4                                                                                    | Data Strobe Control of Data Bus<br>Data Strobe Control of Data Bus (MC68008)<br>Function Code Output<br>Signal Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 3-5<br>3-9                                                                               |

| 5-1                                                                                                         | DTACK, BERR, and HALT Assertion Results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5-31                                                                                     |

| 6-1<br>6-2<br>6-3<br>6-4                                                                                    | Reference Classification<br>Exception Vector Assignment<br>Exception Grouping and Priority<br>MC68010 Format Code                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 6-7<br>6-9                                                                               |

| 7-1<br>7-2<br>7-3<br>7-4<br>7-5<br>7-6<br>7-7<br>7-8<br>7-9<br>7-10<br>7-11<br>7-12<br>7-13<br>7-14<br>7-15 | Effective Address Calculation Times<br>Move Byte Instruction Execution Times<br>Move Word Instruction Execution Times<br>Move Long Instruction Execution Times<br>Standard Instruction Execution Times<br>Immediate Instruction Execution Times<br>Single Operand Instruction Execution Times<br>Shift/Rotate Instruction Execution Times<br>Bit Manipulation Instruction Execution Times<br>Ornditional Instruction Execution Times<br>JMP, JSR, LEA, PEA, and MOVEM Instruction Execution Times<br>Multiprecision Instruction Execution Times<br>Miscellaneous Instruction Execution Times<br>Move Peripheral Instruction Execution Times<br>Exception Processing Instruction Execution Times | 7-2<br>7-3<br>7-3<br>7-4<br>7-5<br>7-6<br>7-6<br>7-6<br>7-7<br>7-7<br>7-8<br>7-9<br>7-10 |

| 8-1<br>8-2<br>8-3<br>8-4                                                                                    | Effective Address Calculation Times<br>Move Byte Instruction Execution Times<br>Move Word Instruction Execution Times<br>Move Long Instruction Execution Times                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8-2<br>8-3                                                                               |

| Opcode           | Operation                                                                                                                                                                                                                                                                                                                                   | Syntax                                                                                      |

|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|

| DIVS             | Destination/Source $\rightarrow$ Destination                                                                                                                                                                                                                                                                                                | DIVS.W <ea>,Dn <math>32/16 \rightarrow 16r:16q</math></ea>                                  |

| DIVU             | Destination/Source $\rightarrow$ Destination                                                                                                                                                                                                                                                                                                | DIVU.W <ea>,Dn 32/16 → 16r:16q</ea>                                                         |

| EOR              | Source $\oplus$ Destination $\rightarrow$ Destination                                                                                                                                                                                                                                                                                       | EOR Dn, <ea></ea>                                                                           |

| EOR              |                                                                                                                                                                                                                                                                                                                                             | · · · · · · · · · · · · · · · · · · ·                                                       |

|                  | Immediate Data $\oplus$ Destination $\rightarrow$ Destination                                                                                                                                                                                                                                                                               | EORI # <data>,<ea></ea></data>                                                              |

| EORI to CCR      |                                                                                                                                                                                                                                                                                                                                             | EORI # <data>,CCR</data>                                                                    |

| EORI to SR       | If supervisor state then Source $\oplus$ SR $\rightarrow$ SR else TRAP                                                                                                                                                                                                                                                                      | EORI # <data>,SR</data>                                                                     |

| EXG              | Rx ↔ Ry                                                                                                                                                                                                                                                                                                                                     | EXG Dx,Dy<br>EXG Ax,Ay<br>EXG Dx,Ay<br>EXG Ay,Dx                                            |

| EXT              | Destination Sign-Extended $\rightarrow$ Destination                                                                                                                                                                                                                                                                                         | EXT.W Dn extend byte to word<br>EXT.L Dn extend word to long word                           |

| ILLEGAL          | $\begin{array}{l} \text{SSP}-2 \rightarrow \text{SSP}; \text{ Vector Offset} \rightarrow (\text{SSP});\\ \text{SSP}-4 \rightarrow \text{SSP}; \text{PC} \rightarrow (\text{SSP});\\ \text{SSP}-2 \rightarrow \text{SSP}; \text{SR} \rightarrow (\text{SSP});\\ \text{Illegal Instruction Vector Address} \rightarrow \text{PC} \end{array}$ | ILLEGAL                                                                                     |

| JMP              | Destination Address $\rightarrow$ PC                                                                                                                                                                                                                                                                                                        | JMP <ea></ea>                                                                               |

| JSR              | SP – 4 $\rightarrow$ SP; PC $\rightarrow$ (SP)<br>Destination Address $\rightarrow$ PC                                                                                                                                                                                                                                                      | JSR <ea></ea>                                                                               |

| LEA              | $\langle ea \rangle \rightarrow An$                                                                                                                                                                                                                                                                                                         | LEA <ea>,An</ea>                                                                            |

| LINK             | $SP - 4 \rightarrow SP; An \rightarrow (SP)$<br>$SP \rightarrow An, SP + d \rightarrow SP$                                                                                                                                                                                                                                                  | LINK An, # <displacement></displacement>                                                    |

| LSL,LSR          | Destination Shifted by <count> <math>\rightarrow</math> Destination</count>                                                                                                                                                                                                                                                                 | LSd <sup>1</sup> Dx,Dy<br>LSd <sup>1</sup> # <data>,Dy<br/>LSd<sup>1</sup> <ea></ea></data> |

| MOVE             | Source $\rightarrow$ Destination                                                                                                                                                                                                                                                                                                            | MOVE <ea>,<ea></ea></ea>                                                                    |

| MOVEA            | Source $\rightarrow$ Destination                                                                                                                                                                                                                                                                                                            | MOVEA <ea>,An</ea>                                                                          |

| MOVE from<br>CCR | $CCR \rightarrow Destination$                                                                                                                                                                                                                                                                                                               | MOVE CCR, <ea></ea>                                                                         |

| MOVE to<br>CCR   | Source $\rightarrow$ CCR                                                                                                                                                                                                                                                                                                                    | MOVE <ea>,CCR</ea>                                                                          |

| MOVE from<br>SR  | $SR \rightarrow Destination$<br>If supervisor state<br>then $SR \rightarrow Destination$<br>else TRAP (MC68010 only)                                                                                                                                                                                                                        | MOVE SR, <ea></ea>                                                                          |

| MOVE to SR       | If supervisor state then Source $\rightarrow$ SR else TRAP                                                                                                                                                                                                                                                                                  | MOVE <ea>,SR</ea>                                                                           |

| Table 2-2. Instructi | on Set Summary | (Sheet 2 of 4) |

|----------------------|----------------|----------------|

|----------------------|----------------|----------------|

#### Address Bus (A23–A0)

This 24-bit, unidirectional, three-state bus is capable of addressing 16 Mbytes of data. This bus provides the address for bus operation during all cycles except interrupt acknowledge cycles and breakpoint cycles. During interrupt acknowledge cycles, address lines A1, A2, and A3 provide the level number of the interrupt being acknowledged, and address lines A23–A4 and A0 are driven to logic high. In 16-Bit mode, A0 is always driven high.

#### MC68008 Address Bus

The unidirectional, three-state buses in the two versions of the **MC68008** differ from each other and from the other processor bus only in the number of address lines and the addressing range. The 20-bit address (A19–A0) of the 48-pin version provides a 1-Mbyte address space; the 52-pin version supports a 22-bit address (A21–A0), extending the address space to 4 Mbytes. During an interrupt acknowledge cycle, the interrupt level number is placed on lines A1, A2, and A3. Lines A0 and A4 through the most significant address line are driven to logic high.

### 3.2 DATA BUS (D15–D0; MC68008: D7–D0)

This bidirectional, three-state bus is the general-purpose data path. It is 16 bits wide in the all the processors except the **MC68008** which is 8 bits wide. The bus can transfer and accept data of either word or byte length. During an interrupt acknowledge cycle, the external device supplies the vector number on data lines D7–D0. The MC68EC000 and MC68HC001 use D7–D0 in 8-bit mode, and D15–D8 are undefined.

## 3.3 ASYNCHRONOUS BUS CONTROL

Asynchronous data transfers are controlled by the following signals: address strobe, read/write, upper and lower data strobes, and data transfer acknowledge. These signals are described in the following paragraphs.

#### Address Strobe (AS).

This three-state signal indicates that the information on the address bus is a valid address.

#### Read/Write ( $R/\overline{W}$ ).

This three-state signal defines the data bus transfer as a read or write cycle. The  $R/\overline{W}$  signal relates to the data strobe signals described in the following paragraphs.

#### Upper And Lower Data Strobes (UDS, LDS).

These three-state signals and R/W control the flow of data on the data bus. Table 3-1 lists the combinations of these signals and the corresponding data on the bus. When the R/W line is high, the processor reads from the data bus. When the R/W line is low, the processor drives the data bus. In 8-bit mode,  $\overline{UDS}$  is always forced high and the LDS signal is used.

### **3.6 SYSTEM CONTROL**

The system control inputs are used to reset the processor, to halt the processor, and to signal a bus error to the processor. The outputs reset the external devices in the system and signal a processor error halt to those devices. The three system control signals are described in the following paragraphs.

#### Bus Error (BERR)

This input signal indicates a problem in the current bus cycle. The problem may be the following:

- 1. No response from a device.

- 2. No interrupt vector number returned.

- 3. An illegal access request rejected by a memory management unit.

- 4. Some other application-dependent error.

Either the processor retries the bus cycle or performs exception processing, as determined by interaction between the bus error signal and the halt signal.

#### Reset (RESET)

The external assertion of this bidirectional signal along with the assertion of  $\overline{HALT}$  starts a system initialization sequence by resetting the processor. The processor assertion of RESET (from executing a RESET instruction) resets all external devices of a system without affecting the internal state of the processor. To reset both the processor and the external devices, the RESET and HALT input signals must be asserted at the same time.

#### Halt (HALT)

An input to this bidirectional signal causes the processor to stop bus activity at the completion of the current bus cycle. This operation places all control signals in the inactive state and places all three-state lines in the high-impedance state (refer to Table 3-4).

When the processor has stopped executing instructions (in the case of a double bus fault condition, for example), the  $\overline{HALT}$  line is driven by the processor to indicate the condition to external devices.

#### Mode (MODE) (MC68HC001/68EC000)

The MODE input selects between the 8-bit and 16-bit operating modes. If this input is grounded at reset, the processor will come out of reset in the 8-bit mode. If this input is tied high or floating at reset, the processor will come out of reset in the 16-bit mode. This input should be changed only at reset and must be stable two clocks after RESET is negated. Changing this input during normal operation may produce unpredictable results.

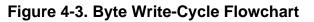

Figure 4-4. Write-Cycle Timing Diagram

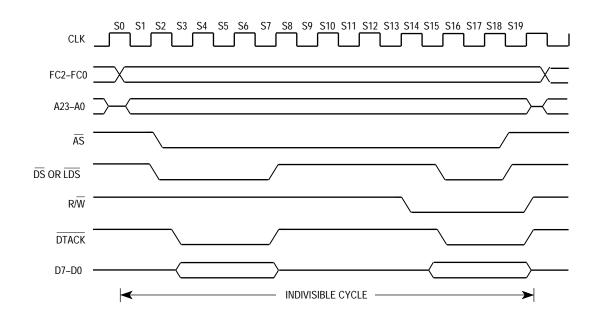

#### Figure 4-6. Read-Modify-Write Cycle Timing Diagram

The descriptions of the read-modify-write cycle states are as follows:

- STATE 0 The read cycle starts in S0. The processor places valid function codes on FC2–FC0 and drives R/W high to identify a read cycle.

- STATE 1 Entering S1, the processor drives a valid address on the address bus.

- STATE 2 On the rising edge of S2, the processor asserts  $\overline{AS}$  and  $\overline{LDS}$ , or  $\overline{DS}$ .

- STATE 3 During S3, no bus signals are altered.

- STATE 4 During S4, the processor waits for a cycle termination signal (DTACK or BERR) or VPA, an M6800 peripheral signal. When VPA is asserted during S4, the cycle becomes a peripheral cycle (refer to **Appendix B M6800 Peripheral Interface**). If neither termination signal is asserted before the falling edge at the end of S4, the processor inserts wait states (full clock cycles) until either DTACK or BERR is asserted.

- STATE 5 During S5, no bus signals are altered.

- STATE 6 During S6, data from the device are driven onto the data bus.

- STATE 7 On the falling edge of the clock entering S7, the processor accepts data from the device and negates  $\overline{LDS}$ , and  $\overline{DS}$ . The device negates  $\overline{DTACK}$  or  $\overline{BERR}$  at this time.

STATES 8-11

The bus signals are unaltered during S8–S11, during which the arithmetic logic unit makes appropriate modifications to the data.

bus request signal. When no acknowledge is received before the bus request signal is negated, the processor continues the use of the bus.

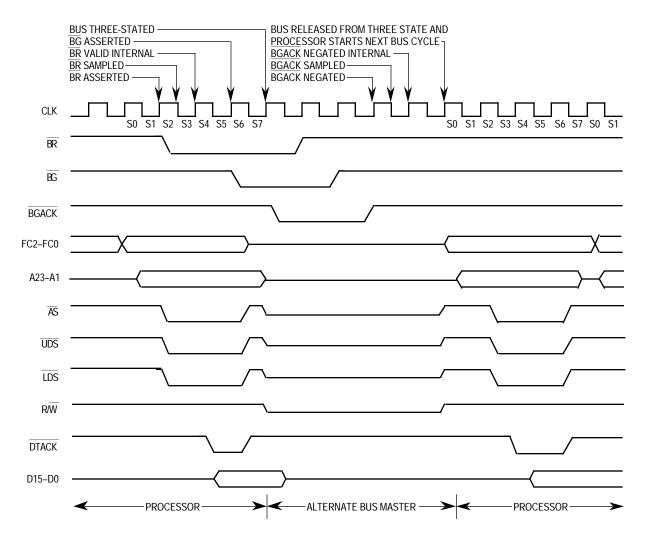

### 5.2.2 Receiving The Bus Grant

The processor asserts  $\overline{BG}$  as soon as possible. Normally, this process immediately follows internal synchronization, except when the processor has made an internal decision to execute the next bus cycle but has not yet asserted  $\overline{AS}$  for that cycle. In this case,  $\overline{BG}$  is delayed until  $\overline{AS}$  is asserted to indicate to external devices that a bus cycle is in progress.

BG can be routed through a daisy-chained network or through a specific priority-encoded network. Any method of external arbitration that observes the protocol can be used.

### 5.2.3 Acknowledgment Of Mastership (3-Wire Bus Arbitration Only)

Upon receiving BG, the requesting device waits until AS, DTACK, and BGACK are negated before asserting BGACK. The negation of AS indicates that the previous bus master has completed its cycle. (No device is allowed to assume bus mastership while AS is asserted.) The negation of BGACK indicates that the previous master has released the bus. The negation of DTACK indicates that the previous slave has terminated the connection to the previous master. (In some applications, DTACK might not be included in this function; general-purpose devices would be connected using AS only.) When BGACK is asserted, the asserting device is bus master until it negates BGACK. BGACK should not be negated until after the bus cycle(s) is complete. A device relinquishes control of the bus by negating BGACK.

The bus request from the granted device should be negated after  $\overline{BGACK}$  is asserted. If another bus request is pending,  $\overline{BG}$  is reasserted within a few clocks, as described in **5.3 Bus Arbitration Control**. The processor does not perform any external bus cycles before reasserting  $\overline{BG}$ .

### **5.3 BUS ARBITRATION CONTROL**

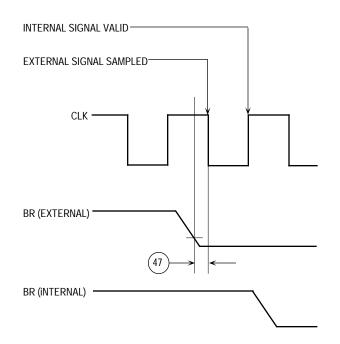

All asynchronous bus arbitration signals to the processor are synchronized before being used internally. As shown in Figure 5-17, synchronization requires a maximum of one cycle of the system clock, assuming that the asynchronous input setup time (#47, defined in **Section 10 Electrical Characteristic**) has been met. The input asynchronous signal is sampled on the falling edge of the clock and is valid internally after the next falling edge.

Figure 5-17. External Asynchronous Signal Synchronization

Bus arbitration control is implemented with a finite-state machine. State diagram (a) in Figure 5-18 applies to all processors using 3-wire bus arbitration and state diagram (b) applies to processors using 2-wire bus arbitration, in which BGACK is permanently negated internally or externally. The same finite-state machine is used, but it is effectively a two-state machine because BGACK is always negated.

In Figure 5-18, input signals R and A are the internally synchronized versions of  $\overline{BR}$  and  $\overline{BGACK}$ . The  $\overline{BG}$  output is shown as G, and the internal three-state control signal is shown as T. If T is true, the address, data, and control buses are placed in the high-impedance state when  $\overline{AS}$  is negated. All signals are shown in positive logic (active high), regardless of their true active voltage level. State changes (valid outputs) occur on the next rising edge of the clock after the internal signal is valid.

A timing diagram of the bus arbitration sequence during a processor bus cycle is shown in Figure 5-19. The bus arbitration timing while the bus is inactive (e.g., the processor is performing internal operations for a multiply instruction) is shown in Figure 5-20.

When a bus request is made after the MPU has begun a bus cycle and before  $\overline{AS}$  has been asserted (S0), the special sequence shown in Figure 5-21 applies. Instead of being asserted on the next rising edge of clock,  $\overline{BG}$  is delayed until the second rising edge following its internal assertion.

Figure 5-19. 3-Wire Bus Arbitration Timing Diagram—Processor Active

### 6.3.7 Privilege Violations

To provide system security, various instructions are privileged. An attempt to execute one of the privileged instructions while in the user mode causes an exception. The privileged instructions are as follows:

AND Immediate to SR EOR Immediate to SR MOVE to SR (68010 only) MOVE from SR (68010 only) MOVEC (68010 only) MOVES (68010 only) MOVE USP OR Immediate to SR RESET RTE STOP

Exception processing for privilege violations is nearly identical to that for illegal instructions. After the instruction is fetched and decoded and the processor determines that a privilege violation is being attempted, the processor starts exception processing. The status register is copied; the supervisor mode is entered; and tracing is turned off. The vector number is generated to reference the privilege violation vector, and the current program counter and the copy of the status register are saved on the supervisor stack. If the processor is an MC68010, the format/offset word is also saved. The saved value of the program counter is the address of the first word of the instruction causing the privilege violation. Finally, instruction execution commences at the address in the privilege violation exception vector.

## 6.3.8 Tracing

To aid in program development, the M68000 Family includes a facility to allow tracing following each instruction. When tracing is enabled, an exception is forced after each instruction is executed. Thus, a debugging program can monitor the execution of the program under test.

The trace facility is controlled by the T bit in the supervisor portion of the status register. If the T bit is cleared (off), tracing is disabled and instruction execution proceeds from instruction to instruction as normal. If the T bit is set (on) at the beginning of the execution of an instruction, a trace exception is generated after the instruction is completed. If the instruction is not executed because an interrupt is taken or because the instruction is illegal or privileged, the trace exception does not occur. The trace exception also does not occur if the instruction is aborted by a reset, bus error, or address error exception. If the instruction is executed and an interrupt is pending on completion, the trace exception is processed before the interrupt exception. During the execution of the instruction, if an exception is forced by that instruction, the trace exception for the instruction exception occurs before that of the trace exception.

As an extreme illustration of these rules, consider the arrival of an interrupt during the execution of a TRAP instruction while tracing is enabled. First, the trap exception is processed, then the trace exception, and finally the interrupt exception. Instruction execution resumes in the interrupt handler routine.

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

#### For More Information On This Product, Go to: www.freescale.com

## SECTION 7 8-BIT INSTRUCTION EXECUTION TIMES

This section contains listings of the instruction execution times in terms of external clock (CLK) periods for the MC68008 and MC68HC001/MC68EC000 in 8-bit mode. In this data, it is assumed that both memory read and write cycles consist of four clock periods. A longer memory cycle causes the generation of wait states that must be added to the total instruction times.

The number of bus read and write cycles for each instruction is also included with the timing data. This data is shown as

n(r/w)

where:

n is the total number of clock periods r is the number of read cycles w is the number of write cycles

For example, a timing number shown as 18(3/1) means that 18 clock periods are required to execute the instruction. Of the 18 clock periods, 12 are used for the three read cycles (four periods per cycle). Four additional clock periods are used for the single write cycle, for a total of 16 clock periods. The bus is idle for two clock periods during which the processor completes the internal operations required for the instruction.

#### NOTE

The total number of clock periods (n) includes instruction fetch and all applicable operand fetches and stores.

## 7.1 OPERAND EFFECTIVE ADDRESS CALCULATION TIMES

Table 7-1 lists the numbers of clock periods required to compute the effective addresses for instructions. The totals include fetching any extension words, computing the address, and fetching the memory operand. The total number of clock periods, the number of read cycles, and the number of write cycles (zero for all effective address calculations) are shown in the previously described format.

#### For More Information On This Product, Go to: www.freescale.com

### 7.7 BIT MANIPULATION INSTRUCTION EXECUTION TIMES

Table 7-9 lists the timing data for the bit manipulation instructions. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, and the number of write cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

|             |              | Dynamic          |                  | Sta              | tic              |

|-------------|--------------|------------------|------------------|------------------|------------------|

| Instruction | Size         | Register         | Memory           | Register         | Memory           |

| BCHG        | Byte<br>Long | <b>12</b> (2/0)* | <b>12</b> (2/1)+ | <b>20</b> (4/0)* | <b>20</b> (4/1)+ |

| BCLR        | Byte<br>Long | <b>14</b> (2/0)* | <b>12</b> (2/1)+ | <b>22</b> (4/0)* | <b>20</b> (4/1)+ |

| BSET        | Byte<br>Long | <b>12</b> (2/0)* | <b>12</b> (2/1)+ | <b>20</b> (4/0)* | <b>20</b> (4/1)+ |

| BTST        | Byte<br>Long | <b>10</b> (2/0)  | <b>8</b> (2/0)+  | <b>18</b> (4/0)  | <b>16</b> (4/0)+ |

Table 7-9. Bit Manipulation Instruction Execution Times

+Add effective address calculation time.

\* Indicates maximum value; data addressing mode only.

### **7.8 CONDITIONAL INSTRUCTION EXECUTION TIMES**

Table 7-10 lists the timing data for the conditional instructions. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, and the number of write cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

| Instruction | Displacement        | Trap or Branch<br>Taken            | Trap or Branch<br>Not Taken        |

|-------------|---------------------|------------------------------------|------------------------------------|

| Bcc         | Byte<br>Word        | <b>18</b> (4/0)<br><b>18</b> (4/0) | <b>12</b> (2/0)<br><b>20</b> (4/0) |

| BRA         | Byte<br>Word        | <b>18</b> (4/0)<br><b>18</b> (4/0) | _                                  |

| BSR         | Byte<br>Word        | <b>34</b> (4/4)<br><b>34</b> (4/4) | _                                  |

| DBcc        | CC True<br>CC False | <b>18</b> (4/0)                    | <b>20</b> (4/0)<br><b>26</b> (6/0) |

| СНК         | _                   | <b>68</b> (8/6)+*                  | <b>14</b> (2/0)                    |

| TRAP        | _                   | <b>62</b> (8/6)                    | _                                  |

| TRAPV       | —                   | <b>66</b> (10/6)                   | <b>8</b> (2/0)                     |

Table 7-10. Conditional Instruction Execution Times

+Add effective address calculation time for word operand.

\* Indicates maximum base value.

the handler routine. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, and the number of write cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

| Exception           | Periods          |

|---------------------|------------------|

| Address Error       | <b>50</b> (4/7)  |

| Bus Error           | <b>50</b> (4/7)  |

| CHK Instruction     | <b>40</b> (4/3)+ |

| Divide by Zero      | <b>38</b> (4/3)+ |

| Illegal Instruction | <b>34</b> (4/3)  |

| Interrupt           | <b>44</b> (5/3)* |

| Privilege Violation | <b>34</b> (4/3)  |

| RESET **            | <b>40</b> (6/0)  |

| Trace               | <b>34</b> (4/3)  |

| TRAP Instruction    | <b>34</b> (4/3)  |

| TRAPV Instruction   | <b>34</b> (5/3)  |

# Table 8-14. Exception ProcessingExecution Times

+ Add effective address calculation time.

\* The interrupt acknowledge cycle is assumed to take four clock periods.

\*\* Indicates the time from when RESET and HALT are first sampled as negated to when instruction execution starts.

### 9.1 OPERAND EFFECTIVE ADDRESS CALCULATION TIMES

Table 9-1 lists the numbers of clock periods required to compute the effective addresses for instructions. The totals include fetching any extension words, computing the address, and fetching the memory operand. The total number of clock periods, the number of read cycles, and the number of write cycles (zero for all effective address calculations) are shown in the previously described format.

|                                               |                                                                                            | Byte                              | , Word                           | Lo                                 | ong                              |

|-----------------------------------------------|--------------------------------------------------------------------------------------------|-----------------------------------|----------------------------------|------------------------------------|----------------------------------|

|                                               | Addressing Mode                                                                            | Fetch                             | No Fetch                         | Fetch                              | No Fetch                         |

|                                               | Register                                                                                   |                                   |                                  |                                    |                                  |

| Dn<br>An                                      | Data Register Direct<br>Address Register Direct                                            | <b>0</b> (0/0)<br><b>0</b> (0/0)  | -                                | <b>0</b> (0/0)<br><b>0</b> (0/0)   | _                                |

|                                               | Memory                                                                                     |                                   |                                  |                                    |                                  |

| (An)<br>(An)+                                 | Address Register Indirect<br>Address Register Indirect with Postincrement                  | <b>4</b> (1/0)<br><b>4</b> (1/0)  | <b>2</b> (0/0)<br><b>4</b> (0/0) | <b>8</b> (2/0)<br><b>8</b> (2/0)   | <b>2</b> (0/0)<br><b>4</b> (0/0) |

| –(An)<br>(d <sub>16</sub> , An)               | Address Register Indirect with Predecrement<br>Address Register Indirect with Displacement | <b>6</b> (1/0)<br><b>8</b> (2/0)  | <b>4</b> (0/0)<br><b>4</b> (0/0) | <b>10</b> (2/0)<br><b>12</b> (3/0) | <b>4</b> (0/0)<br><b>4</b> (1/0) |

| (d გ, An, Xn)*<br>(xxx).W                     | Address Register Indirect with Index<br>Absolute Short                                     | <b>10</b> (2/0)<br><b>8</b> (2/0) | <b>8</b> (1/0)<br><b>4</b> (1/0) | <b>14</b> (3/0)<br><b>12</b> (3/0) | <b>8</b> (1/0)<br><b>4</b> (1/0) |

| (xxx).L<br>(d <sub>16</sub> , PC)             | Absolute Long<br>Program Counter Indirect with Displacement                                | <b>12</b> (3/0)<br><b>8</b> (2/0) | <b>8</b> (2/0)                   | <b>16</b> (4/0)<br><b>12</b> (3/0) | <b>8</b> (2/0)                   |

| (d <sub>8</sub> , PC, Xn)*<br># <data></data> | Program Counter Indirect with Index<br>Immediate                                           | <b>10</b> (2/0)<br><b>4</b> (1/0) |                                  | <b>14</b> (3/0)<br><b>8</b> (2/0)  |                                  |

| Table 9-1. E | Effective | Address | Calculation | Times |

|--------------|-----------|---------|-------------|-------|

|--------------|-----------|---------|-------------|-------|

\*The size of the index register (Xn) does not affect execution time.

## 9.2 MOVE INSTRUCTION EXECUTION TIMES

Tables 9-2, 9-3, 9-4, and 9-5 list the numbers of clock periods for the move instructions. The totals include instruction fetch, operand reads, and operand writes. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format.

### 9.4 IMMEDIATE INSTRUCTION EXECUTION TIMES

The numbers of clock periods shown in Table 9-8 include the times to fetch immediate operands, perform the operations, store the results, and read the next operation. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

In Tables 9-8, the following notation applies:

- # Immediate operand

- Dn Data register operand

- An Address register operand

- M Memory operand

#### Table 9-8. Immediate Instruction Execution Times

| Instruction | Size       | op #, Dn        | op #, An        | ор #, М          |

|-------------|------------|-----------------|-----------------|------------------|

| ADDI        | Byte, Word | <b>8</b> (2/0)  | —               | <b>12</b> (2/1)+ |

|             | Long       | <b>14</b> (3/0) | _               | <b>20</b> (3/2)+ |

| ADDQ        | Byte, Word | <b>4</b> (1/0)  | <b>4</b> (1/0)* | <b>8</b> (1/2)+  |

|             | Long       | <b>8</b> (1/0)  | <b>8</b> (1/1)  | <b>12</b> (1/2)+ |

| ANDI        | Byte, Word | <b>8</b> (2/0)  | _               | <b>12</b> (2/1)+ |

|             | Long       | <b>14</b> (3/0) | —               | <b>20</b> (3/1)+ |

| CMPI        | Byte, Word | <b>8</b> (2/0)  | —               | <b>8</b> (2/0)+  |

|             | Long       | <b>12</b> (3/0) | _               | <b>12</b> (3/0)+ |

| EORI        | Byte, Word | <b>8</b> (2/0)  | —               | <b>12</b> (2/1)+ |

|             | Long       | <b>14</b> (3/0) | —               | <b>20</b> (3/2)+ |

| MOVEQ       | Long       | <b>4</b> (1/0)  | _               | _                |

| ORI         | Byte, Word | <b>8</b> (2/0)  | _               | <b>12</b> (2/1)+ |

|             | Long       | <b>14</b> (3/0) | _               | <b>20</b> (3/2)+ |

| SUBI        | Byte, Word | <b>8</b> (2/0)  | _               | <b>12</b> (2/1)+ |

|             | Long       | <b>14</b> (3/0) | _               | <b>20</b> (3/2)+ |

| SUBQ        | Byte, Word | <b>4</b> (1/0)  | <b>4</b> (1/0)* | <b>8</b> (1/1)+  |

|             | Long       | <b>8</b> (1/0)  | <b>8</b> (1/0)  | <b>12</b> (1/2)+ |

+Add effective address calculation time.

\*Word only.

## 9.5 SINGLE OPERAND INSTRUCTION EXECUTION TIMES

Tables 9-9, 9-10, and 9-11 list the timing data for the single operand instructions. The total number of clock periods, the number of read cycles, and the number of write cycles are shown in the previously described format. The number of clock periods, the number of read cycles, and the number of write cycles, respectively, must be added to those of the effective address calculation where indicated by a plus sign (+).

MOTOROLA

#### For More Information On This Product, Go to: www.freescale.com

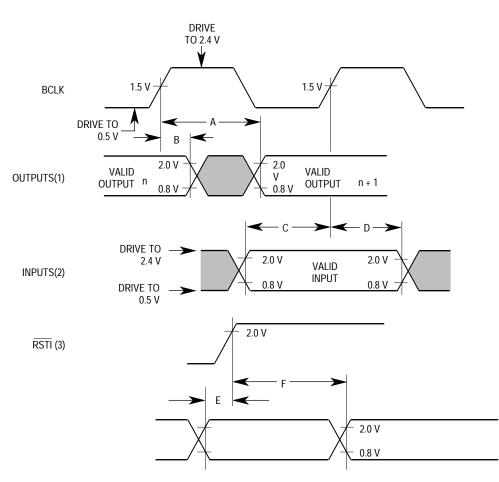

NOTES:

- 1. This output timing is applicable to all parameters specified relative to the rising edge of the clock.

- 2. This input timing is applicable to all parameters specified relative to the rising edge of the clock.

- 3. This timing is applicable to all parameters specified relative to the negation of the RESET signal.

LEGEND:

- A. Maximum output delay specification.

- B. Minimum output hold time.

- C. Minimum input setup time specification.

- D. Minimum input hold time specification.

- E. Mode select setup time to RESET negated.

- F. Mode select hold time from RESET negated.

#### Figure 10-2. Drive Levels and Test Points for AC Specifications

## **10.7 DC ELECTRICAL CHARACTERISTICS** ( $V_{CC}$ = 5.0 VDC±5%; GND=0 VDC; $T_A$ = $T_L$

| TO T <sub>H</sub> ) (Applies To All Processors | Except The MC68EC000) |

|------------------------------------------------|-----------------------|

|------------------------------------------------|-----------------------|

|                                                                                                                                                                        | Characteristic                                                                                                                                                                                                                                                               | Symbol          | Min                   | Max                                  | Unit    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------|--------------------------------------|---------|

| Input High Voltage                                                                                                                                                     |                                                                                                                                                                                                                                                                              | VIH             | 2.0                   | VCC                                  | V       |

| Input Low Voltage                                                                                                                                                      |                                                                                                                                                                                                                                                                              | VIL             | GND-0.3               | 0.8                                  | V       |

| Input Leakage Current<br>@ 5.25 V                                                                                                                                      | BERR, BGACK, BR, DTACK, CLK, IPLO—IPL2, VPA<br>MODE, HALT, RESET                                                                                                                                                                                                             | <sup>I</sup> IN | —                     | 2.5<br>20                            | μΑ      |

| Three-State (Off State) I<br>@ 2.4 V/0.4 V                                                                                                                             | nput Current $\overline{AS}$ , A0—A23, D0—D15,<br>FC0–FC2, $\overline{LDS}$ , R/ $\overline{W}$ , $\overline{UDS}$ , $\overline{VMA}$                                                                                                                                        | ITSI            | —                     | 20                                   | μA      |

| Output High Voltage                                                                                                                                                    | E, $\overline{AS}$ , A0–A23, $\overline{BG}$ , D0–D15,<br>FC0–FC2, $\overline{LDS}$ , R/ $\overline{W}$ , $\overline{UDS}$ , $\overline{VMA}$                                                                                                                                | ∨он             | V <sub>CC</sub> -0.75 | _                                    | V       |

| Output Low Voltage<br>$(I_{OL} = 1.6 \text{ mA})$<br>$(I_{OL} = 3.2 \text{ mA})$<br>$(I_{OL} = 5.0 \text{ mA})$<br>$(I_{OL} = 5.3 \text{ mA})$<br>Current Dissipation* | $\overrightarrow{HALT}$ $A0 - A23, \overrightarrow{BG}, FC0-FC2$ $\overrightarrow{RESET}$ $E, \overrightarrow{AS}, D0 - D15, \overrightarrow{LDS}, R/\overline{W}, \overrightarrow{UDS}, \overrightarrow{VMA}$ $f = 8 \text{ MHz}$ $f = 10 \text{ MHz}$ $f = 10 \text{ MHz}$ | V <sub>OL</sub> |                       | 0.5<br>0.5<br>0.5<br>0.5<br>25<br>30 | V<br>mA |

|                                                                                                                                                                        | f = 12.5 MHz<br>f = 16.67 MHz<br>f = 20 MHz                                                                                                                                                                                                                                  |                 |                       | 35<br>50<br>70                       |         |

| Power Dissipation                                                                                                                                                      | f = 8 MHz<br>f = 10 MHz<br>f = 12.5 MHz<br>f = 16.67 MHz<br>f = 20 MHz                                                                                                                                                                                                       | PD              | —                     | 0.13<br>0.16<br>0.19<br>0.26<br>0.38 | W       |

| Capacitance (V <sub>in</sub> = 0 V,                                                                                                                                    | T <sub>A</sub> =25°C, Frequency=1 MHz)**                                                                                                                                                                                                                                     | C <sub>in</sub> |                       | 20.0                                 | pF      |

| Load Capacitance                                                                                                                                                       | HALT<br>All Others                                                                                                                                                                                                                                                           | CL              |                       | 70<br>130                            | pF      |

\* Current listed are with no loading.

\*\* Capacitance is periodically sampled rather than 100% tested.

## 10.8 AC ELECTRICAL SPECIFICATIONS — CLOCK TIMING (See Figure 10-3)

(Applies To All Processors Except The MC68EC000)

| Num | Characteristic                                                 | 8 MHz*   |            | 10 MHz*  |            | 12.5 MHz* |            | 16.67 MHz<br>12F |              | 16 MHz   |              | 20 MHZ** |              | Unit |

|-----|----------------------------------------------------------------|----------|------------|----------|------------|-----------|------------|------------------|--------------|----------|--------------|----------|--------------|------|

|     |                                                                | Min      | Max        | Min      | Max        | Min       | Max        | Min              | Max          | Min      | Max          | Min      | Max          |      |

|     | Frequency of Operation                                         | 4.0      | 8.0        | 4.0      | 10.0       | 4.0       | 12.5       | 8.0              | 16.7         | 8.0      | 16.7         | 8.0      | 20.0         | MHz  |

| 1   | Cycle Time                                                     | 125      | 250        | 100      | 250        | 80        | 250        | 60               | 125          | 60       | 125          | 50       | 125          | ns   |

| 2,3 | Clock Pulse Width<br>(Measured from 1.5 V to 1.5<br>V for 12F) | 55<br>55 | 125<br>125 | 45<br>45 | 125<br>125 | 35<br>35  | 125<br>125 | 27<br>27         | 62.5<br>62.5 | 27<br>27 | 62.5<br>62.5 | 21<br>21 | 62.5<br>62.5 | ns   |

| 4,5 | Clock Rise and Fall Times                                      |          | 10<br>10   |          | 10<br>10   |           | 5<br>5     |                  | 5<br>5       |          | 5<br>5       |          | 4<br>4       | ns   |

\*These specifications represent an improvement over previously published specifications for the 8-, 10-, and 12.5-

MHz MC68000 and are valid only for product bearing date codes of 8827 and later.

\*\*This frequency applies only to MC68HC000 and MC68EC000 parts.

- NOTES:

1. Timing measurements are referenced to and from a low voltage of 0.8 V and a high voltage of 2.0 V, unless otherwise noted. The voltage swing through this range should start outside and pass through the range such that the rise or fall is linear between 0.8 V and 2.0 V.

2. Because of loading variations, R/W may be valid after AS even though both are initiated by the rising edge of S2 (specification #20A).

#### Figure 10-5. Write Cycle Timing Diagram

(Applies To All Processors Except The MC68EC000)

#### M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL For More Information On This Product, Go to: www.freescale.com

MOTOROLA

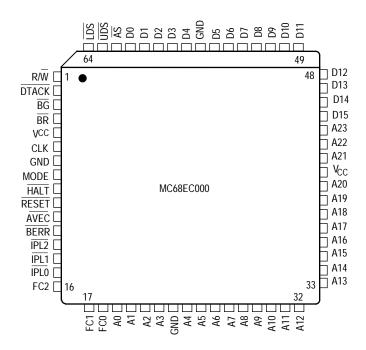

### **11.2 PACKAGE DIMENSIONS**

| Case Package          | 68000 | 68008 | 68010 | 68HC000 | 68HC001 | 68EC000 |

|-----------------------|-------|-------|-------|---------|---------|---------|

| 740-03 L Suffix       |       | ~     |       |         |         |         |

| 767-02 P Suffix       |       | >     |       |         |         |         |

| 746-01 LC Suffix      | ~     |       | ~     | ~       |         |         |

| 754-01 R and P Suffix | ~     |       | ~     | ~       |         |         |

| 765A-05 RC Suffix     | ~     |       | ~     | ~       | ~       |         |

| 778-02 FN Suffix      |       | ~     |       |         |         |         |

| 779-02 FN Suffix      |       |       |       | ~       |         | ~       |

| 779-01 FN Suffix      | ~     |       | ~     |         | ~       |         |

| 847-01 FC Suffix      |       |       |       | ~       |         |         |

| 840B-01 FU Suffix     |       |       |       |         |         | ~       |