Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | e200z4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 84                                                                     |

| Program Memory Size        | 3MB (3M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | ·                                                                      |

| RAM Size                   | 192K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                          |

| Data Converters            | A/D 40x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 176-LQFP                                                               |

| Supplier Device Package    | 176-LQFP (24x24)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5643af0mlu2 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

and 128- and 256-bit read data interfaces to flash memory. The module contains a prefetch controller which prefetches sequential lines of data from the flash array into the buffers. Prefetch buffer hits allow no-wait responses.

The flash memory provides the following features:

- Supports a 64-bit data bus for instruction fetch, CPU loads and DMA access. Byte, halfword, word and doubleword reads are supported. Only aligned word and doubleword writes are supported.

- Fetch Accelerator

- Architected to optimize the performance of the flash

- Configurable read buffering and line prefetch support

- Four-entry 256-bit wide line read buffer

- Prefetch controller

- · Hardware and software configurable read and write access protections on a per-master basis

- Interface to the flash array controller pipelined with a depth of one, allowing overlapped accesses to proceed in parallel for interleaved or pipelined flash array designs

- Configurable access timing usable in a wide range of system frequencies

- Multiple-mapping support and mapping-based block access timing (0-31 additional cycles) usable for emulation of other memory types

- Software programmable block program/erase restriction control

- Erase of selected block(s)

- Read page size of 128 bits (four words)

- ECC with single-bit correction, double-bit detection

- Program page size of 128 bits (four words) to accelerate programming

- ECC single-bit error corrections are visible to software

- Minimum program size is two consecutive 32-bit words, aligned on a 0-modulo-8 byte address, due to ECC

- Embedded hardware program and erase algorithm

- Erase suspend, program suspend and erase-suspended program

- Shadow information stored in non-volatile shadow block

- Independent program/erase of the shadow block

# 1.4.9 BAM

The BAM (Boot Assist Module) is a block of read-only memory that is programmed once by Freescale and is identical for all MPC5644A MCUs. The BAM program is executed every time the MCU is powered-on or reset in normal mode. The BAM supports different modes of booting. They are:

- Booting from internal flash memory

- Serial boot loading (A program is downloaded into RAM via eSCI or the FlexCAN and then executed)

- Booting from external memory on external bus

The BAM also reads the reset configuration half word (RCHW) from internal flash memory and configures the MPC5644A hardware accordingly. The BAM provides the following features:

- Sets up MMU to cover all resources and mapping of all physical addresses to logical addresses with minimum address translation

- Sets up MMU to allow user boot code to execute as either Power Architecture embedded category (default) or as Freescale VLE code

- Location and detection of user boot code

- Automatic switch to serial boot mode if internal flash is blank or invalid

- Supports user programmable 64-bit password protection for serial boot mode

- Supports serial bootloading via FlexCAN bus and eSCI using Freescale protocol

### MPC5644A Microcontroller Data Sheet, Rev. 7

- Supports serial bootloading via FlexCAN bus and eSCI with auto baud rate sensing

- Supports serial bootloading of either Power Architecture code (default) or Freescale VLE code

- Supports booting from calibration bus interface

- Supports censorship protection for internal flash memory

- Provides an option to enable the core watchdog timer

- Provides an option to disable the system watchdog timer

# 1.4.10 eMIOS

The eMIOS timer module provides the capability to generate or measure events in hardware.

The eMIOS module features include:

- Twenty-four 24-bit wide channels

- 3 channels' internal timebases can be shared between channels

- 1 Timebase from eTPU2 can be imported and used by the channels

- Global enable feature for all eMIOS and eTPU timebases

- Dedicated pin for each channel (not available on all package types)

Each channel (0–23) supports the following functions:

- General-purpose input/output (GPIO)

- Single-action input capture (SAIC)

- Single-action output compare (SAOC)

- Output pulse-width modulation buffered (OPWMB)

- Input period measurement (IPM)

- Input pulse-width measurement (IPWM)

- Double-action output compare (DAOC)

- Modulus counter buffered (MCB)

- Output pulse width and frequency modulation buffered (OPWFMB)

# 1.4.11 eTPU2

The eTPU2 is an enhanced co-processor designed for timing control. Operating in parallel with the host CPU, the eTPU2 processes instructions and real-time input events, performs output waveform generation, and accesses shared data without host intervention. Consequently, for each timer event, the host CPU setup and service times are minimized or eliminated. A powerful timer subsystem is formed by combining the eTPU2 with its own instruction and data RAM. High-level assembler/compiler and documentation allows customers to develop their own functions on the eTPU2.

MPC5644A devices feature the second generation of the eTPU, called eTPU2. Enhancements of the eTPU2 over the standard eTPU include:

- The Timer Counter (TCR1), channel logic and digital filters (both channel and the external timer clock input [TCRCLK]) now have an option to run at full system clock speed or system clock / 2.

- Channels support unordered transitions: transition 2 can now be detected before transition 1. Related to this enhancement, the transition detection latches (TDL1 and TDL2) can now be independently negated by microcode.

- A new User Programmable Channel Mode has been added: the blocking, enabling, service request and capture characteristics of this channel mode can be programmed via microcode.

- Microinstructions now provide an option to issue Interrupt and Data Transfer requests selected by channel. They can also be requested simultaneously at the same instruction.

- Channel Flags 0 and 1 can now be tested for branching, in addition to selecting the entry point.

- Channel digital filters can be bypassed.

- 64-bit Censorship password register

- If the external tool writes a 64-bit password that matches the Serial Boot password stored in the internal flash shadow row, Censorship is disabled until the next system reset.

# **1.4.27** Development Trigger Semaphore (DTS)

MPC5644A devices include a system development feature, the Development Trigger Semaphore (DTS) module, that enables software to signal an external tool by driving a persistent (affected only by reset or an external tool) signal on an external device pin. There is a variety of ways this module can be used, including as a component of an external real-time data acquisition system

# 1.5 MPC5644A series architecture

# 1.5.1 Block diagram

Figure 1 shows a top-level block diagram of the MPC5644A series.

# MPC5644A Microcontroller Data Sheet, Rev. 7

|   | 1           | 2          | 3       | 4        | 5    | 6     | 7     | 8    | 9    | 10      | 11   |

|---|-------------|------------|---------|----------|------|-------|-------|------|------|---------|------|

| A | VSS         | VDD        | AN16    | AN17     | AN37 | VDDA1 | VSSA1 | AN23 | AN25 | VRH     | VRL  |

| В | VRC33       | VSS        | VDD     | AN18     | AN36 | AN21  | AN4   | AN5  | AN24 | REFBYPC | AN30 |

| С | AN11        | AN9<br>ANX | VSS     | VDD      | AN20 | AN0   | AN1   | AN6  | AN7  | AN27    | AN29 |

| D | AN10<br>ANY | AN39       | AN38    | VSS      | VDD  | AN19  | AN2   | AN3  | AN22 | AN26    | AN28 |

| E | AN8<br>ANW  | VSSA0      | VDDA0   | VSTBY    |      |       |       |      |      |         |      |

| F | МСКО        | VRCCTL     | MDO0    | VDDREG   |      |       |       |      |      |         |      |

| G | CS0         | MDO1       | MDO2    | MDO3     |      |       |       |      |      |         |      |

| н | CS1         | CS2        | OE      | CS3      |      |       |       |      |      |         |      |

| J | WE1         | WE0        | BDIP    | RD_WR    |      |       |       |      | VSS  | VSS     | VSS  |

| к | ETPUA31     | TA         | TS      | VDDEH1AB |      |       |       |      | VSS  | VSS     | VSS  |

| L | ETPUA27     | ETPUA26    | ETPUA29 | ETPUA30  |      |       |       |      | VSS  | VSS     | VSS  |

Figure 4. 324-pin TEPBGA package ballmap (northwest, viewed from above)

# MPC5644A Microcontroller Data Sheet, Rev. 7

## Table 3. MPC5644A signal properties (continued)

|                               |                                                   | Р                   | PCR                      |                  | I/O               | Voltage <sup>5</sup> / | Sta          | tus <sup>7</sup> |     | Package pin # |     |  |

|-------------------------------|---------------------------------------------------|---------------------|--------------------------|------------------|-------------------|------------------------|--------------|------------------|-----|---------------|-----|--|

| Name                          | Function <sup>1</sup>                             | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | Туре              | Pad Type <sup>6</sup>  | During Reset | After<br>Reset   | 176 | 208           | 324 |  |

| DATA5<br>ADDR21<br>GPIO[33]   | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 33               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | —   | _             | Y6  |  |

| DATA6<br>ADDR22<br>GPIO[34]   | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 34               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | -   | _             | W6  |  |

| DATA7<br>ADDR23<br>GPIO[35]   | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 35               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | —   | _             | AB7 |  |

| DATA8<br>ADDR24<br>GPIO[36]   | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 36               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | _   | _             | AA7 |  |

| DATA9<br>ADDR25<br>GPIO[37]   | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 37               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | _   | _             | Y7  |  |

| DATA10<br>ADDR26<br>GPIO[38]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 38               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | —   | _             | W7  |  |

| DATA11<br>ADDR27<br>GPIO[39]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 39               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | _   | _             | AB8 |  |

| DATA12<br>ADDR28<br>GPIO[40]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 40               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | _   | _             | AA8 |  |

| DATA13<br>ADDR29<br>GPIO[41]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 41               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | —   | _             | Y8  |  |

| DATA14<br>ADDR30<br>GPIO[42]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 42               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | -   | —             | W9  |  |

| DATA15<br>ADDR31<br>GPIO[43]  | External data bus<br>External address bus<br>GPIO | P<br>A1<br>G        | 001<br>010<br>000        | 43               | I/O<br>I/O<br>I/O | VDDE5<br>Fast          | — / Up       | — / Up           | -   | —             | Y9  |  |

| RD_ <del>WR</del><br>GPIO[62] | External read/write<br>GPIO                       | P<br>G              | 01<br>00                 | 62               | I/O<br>I/O        | VDDE2<br>Fast          | — / Up       | — / Up           | -   | _             | J4  |  |

## Table 3. MPC5644A signal properties (continued)

|                                                               |                                                                                     | Р                   | PCR                      |                  | I/O                  | Voltage <sup>5</sup> / | Sta           | tus <sup>7</sup> | Package pin # |     |      |

|---------------------------------------------------------------|-------------------------------------------------------------------------------------|---------------------|--------------------------|------------------|----------------------|------------------------|---------------|------------------|---------------|-----|------|

| Name                                                          | Function <sup>1</sup>                                                               | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | Туре                 | Pad Type <sup>6</sup>  | During Reset  | After<br>Reset   | 176           | 208 | 324  |

| EMIOS11<br>DSPI_D_PCS[4]<br>RCH3_C<br>GPIO[190]               | eMIOS channel<br>DSPI D peripheral chip select<br>Reaction channel 3C<br>GPIO       | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 190              | I/O<br>O<br>I/O      | VDDEH4<br>Medium       | — /<br>WKPCFG | — /<br>WKPCFG    | 75            | R8  | AB15 |

| EMIOS12<br>DSPI_C_SOUT<br>ETPUA27_O <sup>8</sup><br>GPIO[191] | eMIOS channel<br>DSPI C data output<br>eTPU A channel (output only)<br>GPIO         | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 191              | I/O<br>O<br>O<br>I/O | VDDEH4<br>Medium       | — /<br>WKPCFG | — /<br>WKPCFG    | 76            | N10 | AB16 |

| EMIOS13<br>DSPI_D_SOUT<br>GPIO[192]                           | eMIOS channel<br>DSPI D data output<br>GPIO                                         | P<br>A1<br>G        | 01<br>10<br>00           | 192              | I/O<br>O<br>I/O      | VDDEH4<br>Medium       | — /<br>WKPCFG | — /<br>WKPCFG    | 77            | Т8  | AA16 |

| EMIOS14<br>RQ[0]<br>ETPUA29_0 <sup>8</sup><br>GPIO[193]       | eMIOS channel<br>External interrupt request<br>eTPU A channel (output only)<br>GPIO | P<br>A1<br>A2<br>G  | 001<br>010<br>100<br>000 | 193              | I/O<br>I<br>O<br>I/O | VDDEH4<br>Slow         | — / Down      | — / Down         | 78            | R9  | Y16  |

| <u>=MI</u> OS15<br>RQ[1]<br>GPIO[194]                         | eMIOS channel<br>External interrupt request<br>GPIO                                 | P<br>A1<br>G        | 01<br>10<br>00           | 194              | I/O<br>I<br>I/O      | VDDEH4<br>Slow         | — / Down      | — / Down         | 79            | Т9  | W16  |

| EMIOS16<br>GPIO[195]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 195              | I/O<br>I/O           | VDDEH4<br>Slow         | — / Up        | — / Up           | -             | —   | W17  |

| EMIOS17<br>GPIO[196]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 196              | I/O<br>I/O           | VDDEH4<br>Slow         | — / Up        | — / Up           | -             | —   | Y17  |

| EMIOS18<br>GPIO[197]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 197              | I/O<br>I/O           | VDDEH4<br>Slow         | — / Up        | — / Up           | -             | _   | AA17 |

| EMIOS19<br>GPIO[198]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 198              | I/O<br>I/O           | VDDEH4<br>Slow         | — /<br>WKPCFG | — /<br>WKPCFG    | 1 -           | -   | AB17 |

| EMIOS20<br>GPIO[199]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 199              | I/O<br>I/O           | VDDEH4<br>Slow         | — /<br>WKPCFG | — /<br>WKPCFG    | -             | -   | AB18 |

| EMIOS21<br>GPIO[200]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 200              | I/O<br>I/O           | VDDEH4<br>Slow         | — /<br>WKPCFG | — /<br>WKPCFG    | -             | _   | AA18 |

| EMIOS22<br>GPIO[201]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 201              | I/O<br>I/O           | VDDEH4<br>Slow         | — / Down      | — / Down         | -             | -   | Y18  |

| EMIOS23<br>GPIO[202]                                          | eMIOS channel<br>GPIO                                                               | P<br>G              | 01<br>00                 | 202              | I/O<br>I/O           | VDDEH4<br>Slow         | — / Down      | — / Down         | 80            | R11 | W18  |

7

|         |                       | Р                   | PCR                      |                  |             | Malta - 5 /                                     | Sta          | tus <sup>7</sup> | Package pin #                                                                               |                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                      |

|---------|-----------------------|---------------------|--------------------------|------------------|-------------|-------------------------------------------------|--------------|------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Name    | Function <sup>1</sup> | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | l/O<br>Type | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup> | During Reset | After<br>Reset   | 176                                                                                         | 208                                                                                                                                                                            | 324                                                                                                                                                                                                                                                                                                                  |

| VDDEH7  | I/O Supply Input      | _                   |                          | _                | I           | 3.3 V - 5.0 V                                   | 1/—          | VDDEH7           | _                                                                                           | D12                                                                                                                                                                            | B22, C21,<br>D15, D20,<br>E19, F19,<br>H19, J14                                                                                                                                                                                                                                                                      |

| VDDEH7A | I/O Supply Input      | -                   |                          | _                | I           | 3.3 V - 5.0 V                                   | I <i>/</i> — | VDDEH7A          | 125                                                                                         | —                                                                                                                                                                              | —                                                                                                                                                                                                                                                                                                                    |

| VDDEH7B | I/O Supply Input      | -                   |                          | —                | I           | 3.3 V - 5.0 V                                   | I / —        | VDDEH7B          | 138                                                                                         | -                                                                                                                                                                              | _                                                                                                                                                                                                                                                                                                                    |

| VSS     | Ground                | _                   |                          |                  | I           |                                                 | 1/           | VSS              | 15,<br>29,<br>43,<br>57,<br>72,<br>90,<br>94,<br>96,<br>108,<br>115,<br>127,<br>133,<br>140 | B2, B15,<br>C3, C14,<br>D4, D13,<br>G7, G8,<br>G9,<br>G10,<br>H7, H8,<br>H9, H10,<br>J7, J8,<br>J9, J10,<br>K7,<br>K8, K9,<br>K10,<br>M16,<br>N4, N13,<br>P3, P14,<br>R2, R15, | A1, A22, B2,<br>B21, C3, C20<br>D4, D17, D19<br>F21, H21, J9,<br>J10, J11, J12,<br>J13, K9, K10,<br>K11, K12,<br>K13, K14, L9,<br>L10, L11, L12<br>L13, L14, L21<br>M11, M12,<br>M13, M14,<br>N9, N10, N12<br>N13, N14,<br>N21, P9, P10,<br>P12, P13,<br>P14, T19,<br>T21, T22, W4<br>Y3, Y20,<br>AA21, AB1,<br>AB22 |

Table 3. MPC5644A signal properties (continued)

<sup>1</sup> For each pin in the table, each line in the Function column is a separate function of the pin. For all I/O pins the selection of primary pin function or secondary function or GPIO is done in the SIU except where explicitly noted. See the Signal details table for a description of each signal.

<sup>2</sup> The P/A/G column indicates the position a signal occupies in the muxing order for a pin—Primary, Alternate 1, Alternate 2, Alternate 3, or GPIO. Signals are selected by setting the PA field value in the appropriate PCR register in the SIU module. The PA field values are as follows: P - 0b0001, A1 - 0b0010, A2 - 0b0100, A3 - 0b1000, or G - 0b0000. Depending on the register, the PA field size can vary in length. For PA fields having fewer than four bits, remove the appropriate number of leading zeroes from these values.

<sup>3</sup> The Pad Configuration Register (PCR) PA field is used by software to select pin function.

<sup>4</sup> Values in the PCR No. column refer to registers in the System Integration Unit (SIU). The actual register name is "SIU\_PCR" suffixed by the PCR number. For example, PCR[190] refers to the SIU register named SIU\_PCR190.

56

- <sup>5</sup> The VDDE and VDDEH supply inputs are broken into segments. Each segment of slow I/O pins (VDDEH) may have a separate supply in the 3.3 V to 5.0 V range (-10%/+5%). Each segment of fast I/O (VDDE) may have a separate supply in the 1.8 V to 3.3 V range (+/- 10%).

- <sup>6</sup> See Table 4 for details on pad types.

- <sup>7</sup> The Status During Reset pin is sampled after the internal POR is negated. Prior to exiting POR, the signal has a high impedance. Terminology is O - output, I - input, Up - weak pull up enabled, Down - weak pull down enabled, Low - output driven low, High - output driven high. A dash for the function in this column denotes that both the input and output buffer are turned off. The signal name to the left or right of the slash indicates the pin is enabled.

- <sup>8</sup> Output only.

- <sup>9</sup> When used as ETRIG, this pin must be configured as an input. For GPIO it can be configured either as an input or output.

- <sup>10</sup> Maximum frequency is 50 kHz.

- <sup>11</sup> The SIU\_PCR219 register is unusual in that it controls pads for two separate device pins: GPIO[219] and MCKO. See the MPC5644A Microcontroller Reference Manual (SIU chapter) for details.

- <sup>12</sup> Multivoltage pads are automatically configured in low swing mode when a JTAG or Nexus function is selected, otherwise they are high swing.

- <sup>13</sup> On 176 LQFP and 208 MAPBGA packages, this pin is tied low internally.

- <sup>14</sup> Nexus multivoltage pads default to 5 V operation until the Nexus module is enabled.

- <sup>15</sup> EVTO should be clamped to 3.3 V to prevent possible damage to external tools that only support 3.3 V.

- <sup>16</sup> Do not connect pin directly to a power supply or ground.

- <sup>17</sup> This signal name is used to support legacy naming.

- <sup>18</sup> During and just after POR negates, internal pull resistors can be enabled, resulting in as much as 4 mA of current draw. The pull resistors are disabled when the system clock propagates through the device.

- <sup>19</sup> For pins AN12-AN15, if the analog features are used the VDDEH7 input pins should be tied to VDDA because that segment must meet the VDDA specification to support analog input function.

- <sup>20</sup> Do not use VRC33 to drive external circuits.

- <sup>21</sup> VDDA0 and VDDA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VDDA.

- <sup>22</sup> VSSA0 and VSSA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VSSA.

- <sup>23</sup> VDDE2 and VDDE3 are shorted together in all production packages.

- <sup>24</sup> VDDE2 and VDDE3 are shorted together in all production packages.

- <sup>25</sup> VDDEH1A, VDDEH1B, and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>26</sup> VDDEH4, VDDEH4A, VDDEH4B, and VDDEH4AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>27</sup> VDDEH6, VDDEH6A, VDDEH6B, and VDDEH6AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

### Table 4. Pad types

| Pad Type              | Name         | I/O Voltage Range                                                 |

|-----------------------|--------------|-------------------------------------------------------------------|

| Slow                  | pad_ssr_hv   | 3.0V - 5.5 V                                                      |

| Medium                | pad_msr_hv   | 3.0 V - 5.5 V                                                     |

| Fast                  | pad_fc       | 3.0 V - 3.6 V                                                     |

| MultiV <sup>1,2</sup> | pad_multv_hv | 3.0 V - 5.5 V (high swing mode)<br>3.0 V - 3.6 V (low swing mode) |

| Analog                | pad_ae_hv    | 0.0 - 5.5 V                                                       |

| LVDS                  | pad_lo_lv    | _                                                                 |

Multivoltage pads are automatically configured in low swing mode when a JTAG or Nexus function is selected, otherwise they are high swing.

VDDEH7 supply cannot be below 4.5 V when in low-swing mode.

### Signal details 2.5

| Signal                                 | Module or Function                      | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKOUT                                 | Clock Generation                        | MPC5644A clock output for the external/calibration bus interface                                                                                                                                                                                                                                                                                                                            |

| ENGCLK                                 | Clock Generation                        | Clock for external ASIC devices                                                                                                                                                                                                                                                                                                                                                             |

| EXTAL                                  | Clock Generation                        | Input pin for an external crystal oscillator or an external clock source based on the value driven on the PLLREF pin at reset.                                                                                                                                                                                                                                                              |

| PLLREF                                 | Clock Generation<br>Reset/Configuration | <ul> <li>PLLREF is used to select whether the oscillator operates in xtal mode or external reference mode from reset. PLLREF=0 selects external reference mode. On the 324BGA package, PLLREF is bonded to the ball used for PLLCFG[0] for compatibility with MPC55xx devices .</li> <li>For the 176-pin QFP and 208-ball BGA packages: 0: External reference clock is selected.</li> </ul> |

|                                        |                                         | 1: XTAL oscillator mode is selected<br>For the 324 ball BGA package:<br>If RSTCFG is 0:<br>0: External reference clock is selected.<br>1: XTAL oscillator mode is selected.<br>If RSTCFG is 1, XTAL oscillator mode is selected.                                                                                                                                                            |

| XTAL                                   | Clock Generation                        | Crystal oscillator input                                                                                                                                                                                                                                                                                                                                                                    |

| DSPI_B_SCK_LVDS-<br>DSPI_B_SCK_LVDS+   | DSPI                                    | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                                                                                                                                                                                             |

| DSPI_B_SOUT_LVDS-<br>DSPI_B_SOUT_LVDS+ | DSPI                                    | LVDS pair used for DSPI_B TSB mode transmission                                                                                                                                                                                                                                                                                                                                             |

| DSPI_C_SCK_LVDS-<br>DSPI_C_SCK_LVDS+   | DSPI                                    | LVDS pair used for DSPI_C TSB mode transmission                                                                                                                                                                                                                                                                                                                                             |

### Table 5. Signal details

\_\_\_\_\_

| Signal                                                                                                                                | Module or Function | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO[0:3]<br>GPIO[8:43]<br>GPIO[62:65]<br>GPIO[68:70]<br>GPIO[75:145]<br>GPIO[179:204]<br>GPIO[208:213]<br>GPIO[219]<br>GPIO[244:245] | SIU - GPIO         | Configurable general purpose I/O pins. Each GPIO input and<br>output is separately controlled by an 8-bit input (GPDI) or output<br>(GPDO) register. Additionally, each GPIO pins is configured<br>using a dedicated SIU_PCR register.<br>The GPIO pins are generally multiplexed with other I/O pin<br>functions.<br>See The MPC5644A Microcontroller Reference Manual for more<br>information.                                                                                                                                                                                                                                       |

| RESET                                                                                                                                 | SIU - Reset        | The RESET pin is an active low input. The RESET pin is<br>asserted by an external device during a power-on or external<br>reset. The internal reset signal asserts only if the RESET pin<br>asserts for 10 clock cycles. Assertion of the RESET pin while the<br>device is in reset causes the reset cycle to start over.<br>The RESET pin has a glitch detector which detects spikes<br>greater than two clock cycles in duration that fall below the<br>switch point of the input buffer logic of the VDDEH input pins.<br>The switch point lies between the maximum VIL and minimum<br>VIH specifications for the VDDEH input pins. |

| RSTCFG                                                                                                                                | SIU - Reset        | <ul> <li>Used to enable or disable the PLLREF and the BOOTCFG[0:1] configuration signals.</li> <li>0: Get configuration information from BOOTCFG[0:1] and PLLREF</li> <li>1: Use default configuration of booting from internal flash with crystal clock source</li> <li>Note: For the 176-pin QFP and 208-ball BGA packages RSTCFG is always 0, so PLLREF and BOOTCFG signals are used.</li> </ul>                                                                                                                                                                                                                                    |

| RSTOUT                                                                                                                                | SIU - Reset        | The $\overline{\text{RSTOUT}}$ pin is an active low output that uses a push/pull configuration. The $\overline{\text{RSTOUT}}$ pin is driven to the low state by the MCU for all internal and external reset sources. There is a delay between initiation of the reset and the assertion of the RSTOUT pin.                                                                                                                                                                                                                                                                                                                            |

<sup>1</sup> Do not connect pin directly to a power supply or ground.

- $^{6}\,$  All functional non-supply I/O pins are clamped to V\_{SS} and V\_{DDE}, or V\_{DDEH}.

- <sup>7</sup> AC signal overshoot and undershoot of up to 2.0 V of the input voltages is permitted for an accumulative duration of 60 hours over the complete lifetime of the device (injection current not limited for this duration).

- <sup>8</sup> Internal structures hold the voltage greater than –1.0 V if the injection current limit of 2 mA is met.

- <sup>9</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDEH</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDEH</sub> is within the operating voltage specifications.

- <sup>10</sup> Internal structures hold the input voltage less than the maximum voltage on all pads powered by V<sub>DDE</sub> supplies, if the maximum injection current specification is met (2 mA for all pins) and V<sub>DDE</sub> is within the operating voltage specifications.

- <sup>11</sup> Total injection current for all pins (including both digital and analog) must not exceed 25 mA.

- <sup>12</sup> Total injection current for all analog input pins must not exceed 15 mA.

- <sup>13</sup> Solder profile per IPC/JEDEC J-STD-020D.

- <sup>14</sup> Moisture sensitivity per JEDEC test method A112.

# 3.3 Thermal characteristics

| Symbo               | ol | С | Parameter                                                   | Conditions                                  | Value | Unit |

|---------------------|----|---|-------------------------------------------------------------|---------------------------------------------|-------|------|

| $R_{\theta JA}$     | CC | D | Junction-to-Ambient, Natural Convection <sup>2</sup>        | Single layer board - 1s                     | 38    | °C/W |

| $R_{\thetaJA}$      | CC | D | Junction-to-Ambient, Natural Convection <sup>2</sup>        | Four layer board - 2s2p                     | 31    | °C/W |

| R <sub>0JMA</sub>   | CC | D | Junction-to-Moving-Air, Ambient <sup>2</sup>                | 200 ft./min., single layer<br>board - 1s    | 30    | °C/W |

| R <sub>θJMA</sub>   | CC | D | Junction-to-Moving-Air, Ambient <sup>2</sup>                | at 200 ft./min., four layer<br>board - 2s2p | 25    | °C/W |

| $R_{\theta JB}$     | CC | D | Junction-to-Board <sup>3</sup>                              |                                             | 20    | °C/W |

| R <sub>0JCtop</sub> | CC | D | Junction-to-Case <sup>4</sup>                               |                                             | 5     | °C/W |

| $\Psi_{JT}$         | CC | D | Junction-to-Package Top, Natural<br>Convection <sup>5</sup> |                                             | 2     | °C/W |

### Table 9. Thermal characteristics for 176-pin QFP<sup>1</sup>

<sup>1</sup> Thermal characteristics are targets based on simulation that are subject to change per device characterization.

- <sup>4</sup> Junction-to-Case at the top of the package determined using MIL-STD 883 Method 1012.1. The cold plate temperature is used for the case temperature. Reported value includes the thermal resistance of the interface layer.

- <sup>5</sup> Thermal characterization parameter indicating the temperature difference between the package top and the junction temperature per JEDEC JESD51-2. When Greek letters are not available, the thermal characterization parameter is written as Psi-JT.

<sup>&</sup>lt;sup>2</sup> Junction-to-Ambient Thermal Resistance determined per JEDEC JESD51-3 and JESD51-6. Thermal test board meets JEDEC specification for this package.

<sup>&</sup>lt;sup>3</sup> Junction-to-Board thermal resistance determined per JEDEC JESD51-8. Thermal test board meets JEDEC specification for the specified package.

| ID Name |          |    |   | Parameter                                                                         | Min              | Тур     | Мах              | Unit | Notes |

|---------|----------|----|---|-----------------------------------------------------------------------------------|------------------|---------|------------------|------|-------|

| 8a      | _        | СС | С | Variation of LVI for rising<br>5 V V <sub>DDREG</sub> supply at<br>power-on reset | Lvi5p0 -<br>6%   | Lvi5p0  | Lvi5p0 +<br>6%   | V    |       |

| 8b      | _        | СС | С | Variation of LVI for rising<br>5 V V <sub>DDRE</sub> G supply<br>power-on reset   | Lvi5p0 -<br>3%   | Lvi5p0  | Lvi5p0 +<br>3%   | V    |       |

| 8c      | _        | CC | С | Trimming step LVI 5 V                                                             | _                | 20      | _                | mV   |       |

| 8d      | Lvi5p0_h | CC | С | LVI 5 V hysteresis                                                                | _                | 60      | _                | mV   |       |

| 9       | Por5V_r  | СС | С | Nominal POR for rising 5 V<br>V <sub>DDREG</sub> supply                           | _                | 2.67    | -                | V    |       |

| 9a      | _        | СС | С | Variation of POR for rising $5 \text{ V V}_{\text{DDREG}}$ supply                 | Por5V_r<br>- 35% | Por5V_r | Por5V_r<br>+ 50% | V    |       |

| 9b      | Por5V_f  | СС | С | Nominal POR for falling 5 V<br>V <sub>DDREG</sub> supply                          | _                | 2.47    | —                | V    |       |

| 9c      | —        | СС | С | Variation of POR for falling $5 \text{ V V}_{\text{DDREG}}$ supply                | Por5V_f<br>- 35% | Por5V_f | Por5V_f<br>+ 50% | V    |       |

| Table 15. PMC | Electrical | Characteristics | (continued) |

|---------------|------------|-----------------|-------------|

|               |            |                 | (           |

<sup>1</sup> Using external ballast transistor.

<sup>2</sup> Min range is extended to 10% since Lvi1p2 is reprogrammed from 1.2 V to 1.16 V after power-on reset.

<sup>3</sup> LVI for falling supply is calculated as LVI rising – LVI hysteresis.

<sup>4</sup> Lvi1p2 tracks DC target variation of internal Vdd regulator. Minimum and maximum Lvi1p2 correspond to minimum and maximum Vdd DC target respectively.

<sup>5</sup> Minimum loading (<10 mA) for reading trim values from flash, powering internal RC oscillator, and IO consumption during POR.

<sup>6</sup> No external load is allowed, except for use as a reference for an external tool.

<sup>7</sup> This value is valid only when the internal regulator is bypassed. When the internal regulator is enabled, the maximum external load allowed on the Nexus pads is 30 pF at 40 MHz.

<sup>8</sup> Lvi3p3 tracks DC target variation of internal Vdd33 regulator. Minimum and maximum Lvi3p3 correspond to minimum and maximum Vdd33 DC target respectively.

# 3.6.1 Voltage regulator controller (V<sub>RC</sub>) electrical specifications

### Table 16. VRC electrical specifications

| Symbol            | Parameter                                                                                                             |                    | Min. | Max. | Units |

|-------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------|------|------|-------|

| L                 | Current can be sourced by V <sub>RCCTL</sub> at Tj:                                                                   | 25 °C              | TBD  | _    | mA    |

| VRCCTL            |                                                                                                                       | 150 °C             | TBD  | _    | mA    |

|                   | Required gain at Tj:<br>I <sub>DD</sub> ÷ I <sub>VRCCTL</sub> (f <sub>sys</sub> = f <sub>MAX</sub> ) <sup>1,3,4</sup> | – 40 °C            | TBD  | _    | _     |

| BETA <sup>2</sup> | $I_{DD} \div I_{VRCCTL} (t_{sys} = t_{MAX})^{-1,0,+1}$                                                                | 25 °C              | TBD  |      | —     |

|                   |                                                                                                                       | 150 <sup>o</sup> C | TBD  | TBD  | _     |

<sup>1</sup>  $I_{VRCCTL}$  is measured at the following conditions:  $V_{DD}$  = 1.35 V,  $V_{RC33}$  = 3.1 V,  $V_{VRCCTL}$  = 2.2 V.

| External Network<br>Parameter | Min    | Тур    | Мах    | Comment                                                                                      |

|-------------------------------|--------|--------|--------|----------------------------------------------------------------------------------------------|

| Re                            | 0.252Ω | 0.280Ω | 0.308Ω | +/-10%                                                                                       |

| Creg                          |        | 10µF   |        | It depends on external Vreg.                                                                 |

| Сс                            | 5μF    | 10µF   | 13.5μF | X7R, -50%/+35%                                                                               |

| Rc                            | 1.1Ω   |        | 5.6Ω   | May or may not be<br>required. It depends<br>on the allowable<br>power dissipation of<br>T1. |

| Table 17. MPC5644A External network spec | ecification |

|------------------------------------------|-------------|

|------------------------------------------|-------------|

# 3.6.3 Recommended power transistors

The following NPN transistors are recommended for use with the on-chip voltage regulator controller: ON Semiconductor<sup>TM</sup> BCP68T1 or NJD2873 as well as Philips Semiconductor<sup>TM</sup> BCP68. The collector of the external transistor is preferably connected to the same voltage supply source as the output stage of the regulator.

| Symbol              | Parameter                               | Value                   | Unit |

|---------------------|-----------------------------------------|-------------------------|------|

| h <sub>FE</sub> (β) | DC current gain (Beta)                  | 60 – 550                | —    |

| P <sub>D</sub>      | Absolute minimum power dissipation      | >1.0<br>(1.5 preferred) | W    |

| I <sub>CMaxDC</sub> | Minimum peak collector current          | 1.0                     | А    |

| VCE <sub>SAT</sub>  | Collector-to-emitter saturation voltage | 200 – 600 <sup>1</sup>  | mV   |

| $V_{BE}$            | Base-to-emitter voltage                 | 0.4 – 1.0               | V    |

| Table 18. Recommended operating characteristics | Table 18. | Recommended | operating | characteristics |

|-------------------------------------------------|-----------|-------------|-----------|-----------------|

|-------------------------------------------------|-----------|-------------|-----------|-----------------|

<sup>1</sup> Adjust resistor at bipolar transistor collector for 3.3 V/5.0 V to avoid VCE < VCE<sub>SAT</sub>.

# 3.7 Power up/down sequencing

There is no power sequencing required among power sources during power up and power down, in order to operate within specification.

Although there are no power up/down sequencing requirements to prevent issues such as latch-up or excessive current spikes the state of the I/O pins during power up/down varies according to Table 19 for all pins with fast pads, and Table 20 for all pins with medium, slow, and multi-voltage pads.

| V <sub>DDE</sub> | V <sub>RC33</sub> V <sub>DD</sub> |                 | Pad State      |

|------------------|-----------------------------------|-----------------|----------------|

| LOW              | х                                 | х               | LOW            |

| V <sub>DDE</sub> | LOW                               | х               | HIGH           |

| V <sub>DDE</sub> | V <sub>RC33</sub>                 | LOW             | HIGH IMPEDANCE |

| V <sub>DDE</sub> | V <sub>RC33</sub>                 | V <sub>DD</sub> | FUNCTIONAL     |

Table 19. Power sequence pin states (fast pads)

| <u> </u>                                | Symbol |   | Deverator                                                     | Conditions             |                        | Value |                        | 11   |

|-----------------------------------------|--------|---|---------------------------------------------------------------|------------------------|------------------------|-------|------------------------|------|

| Symbo                                   |        | С | Parameter                                                     | Conditions             | min                    | typ   | max                    | Unit |

| V <sub>DDREG</sub>                      | SR     | _ | Voltage regulator supply voltage                              | _                      | 4.75                   | _     | 5.25                   | V    |

| V <sub>DDPLL</sub>                      | SR     | _ | Clock synthesizer operating voltage                           | _                      | 1.14                   | _     | 1.32                   | V    |

| V <sub>SSPLL</sub> –<br>V <sub>SS</sub> | SR     | — | V <sub>SSPLL</sub> to V <sub>SS</sub><br>differential voltage | _                      | -100                   | _     | 100                    | mV   |

| $V_{IL_S}$                              | CC     | С | Slow/medium I/O pad<br>input low voltage                      | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _     | 0.35*V <sub>DDEH</sub> | V    |

|                                         |        | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 0.40*V <sub>DDEH</sub> |      |

| $V_{IL_F}$                              | CC     | С | Fast pad I/O input low voltage                                | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _     | 0.35*V <sub>DDE</sub>  | V    |

|                                         |        | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 0.40*V <sub>DDE</sub>  |      |

| V <sub>IL_LS</sub>                      | CC     | С | Multi-voltage I/O pad<br>input low voltage in                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _     | 0.8                    | V    |

|                                         |        | Ρ | Low-swing-mode <sup>5,6,7,</sup><br>8                         | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 1.1                    |      |

| $V_{IL_{HS}}$                           | СС     | С | Multi-voltage pad I/O input low voltage in                    | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _     | 0.35 V <sub>DDEH</sub> | V    |

|                                         |        | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 0.4 V <sub>DDEH</sub>  |      |

| V <sub>IH_S</sub>                       | СС     | С | Slow/medium pad I/O input high voltage <sup>9</sup>           | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 | V    |

|                                         |        | Ρ |                                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 |      |

| $V_{IH_F}$                              | СС     | С | Fast I/O input high voltage                                   | Hysteresis<br>enabled  | 0.65 V <sub>DDE</sub>  | _     | V <sub>DDE</sub> +0.3  | V    |

|                                         |        | Ρ |                                                               | Hysteresis<br>disabled | 0.58 V <sub>DDE</sub>  | _     | V <sub>DDE</sub> +0.3  |      |

| V <sub>IH_LS</sub>                      | СС     | С | Multi-voltage pad I/O input high voltage in                   | Hysteresis<br>enabled  | 2.5                    | _     | V <sub>DDEH</sub> +0.3 | V    |

|                                         |        | Ρ | low-swing-mode <sup>5,6,7,8</sup>                             | Hysteresis<br>disabled | 2.2                    | _     | V <sub>DDEH</sub> +0.3 |      |

| V <sub>IH_HS</sub>                      | CC     | С | Multi-voltage I/O input high voltage in                       | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 | V    |

|                                         |        | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | —     | V <sub>DDEH</sub> +0.3 |      |

| Table 21. DC electrical specifications (con | tinued) |

|---------------------------------------------|---------|

|---------------------------------------------|---------|

| Symbol                                     |    |   | _                                                      | Conditions                                                |     | Value |                        |      |

|--------------------------------------------|----|---|--------------------------------------------------------|-----------------------------------------------------------|-----|-------|------------------------|------|

| Symbol                                     |    | С | Parameter                                              | Conditions                                                | min | typ   | max                    | Unit |

| IDDSTBY                                    | CC | Т | Operating current<br>0.95-1.2 V                        | V <sub>STBY</sub> at<br>55 °C                             |     | 35    | 100                    | μA   |

|                                            |    | Т | Operating current<br>2–5.5 V                           | V <sub>STBY</sub> at<br>55 °C                             |     | 45    | 110                    | μA   |

| I <sub>DDSTBY27</sub>                      | СС | Р | Operating current<br>0.95-1.2 V                        | V <sub>STBY</sub> 27 <sup>o</sup> C                       |     | 25    | 90                     | μA   |

|                                            |    | Р | Operating current<br>2-5.5 V                           | V <sub>STBY</sub> 27 °C                                   |     | 35    | 100                    | μA   |

| I <sub>DDSTBY150</sub>                     | сс | Р | Operating current<br>0.95-1.2 V                        | V <sub>STBY</sub><br>150 °C                               | _   | 790   | 2000                   | μΑ   |

|                                            |    | Ρ | Operating current<br>2–5.5 V                           | V <sub>STBY</sub> at<br>150 °C                            | —   | 760   | 2000                   | μA   |

| I <sub>DDPLL</sub>                         | CC | Ρ | Operating current<br>1.2 V supplies                    | V <sub>DDPLL</sub> ,<br>80 MHz,<br>V <sub>DD</sub> =1.2 V | —   |       | 15                     | mA   |

| I <sub>DDSLOW</sub><br>I <sub>DDSTOP</sub> | СС | Ρ | V <sub>DD</sub> low-power mode<br>operating current at | Slow<br>mode <sup>10</sup>                                | _   |       | 90                     | mA   |

|                                            |    | Ρ | 1.32 V                                                 | Stop mode <sup>11</sup>                                   | _   |       | 75                     |      |

| I <sub>DD33</sub>                          | СС | С | Operating current<br>3.3 V supplies                    | V <sub>RC33</sub> <sup>1,12</sup>                         | _   |       | 60                     | mA   |

| I <sub>DDA</sub>                           | СС | Ρ | Operating current                                      | V <sub>DDA</sub>                                          | _   | —     | 30.0                   | mA   |

| I <sub>REF</sub><br>I <sub>DDREG</sub>     |    | Ρ | 5.0 V supplies                                         | Analog<br>reference<br>supply<br>current<br>(transient)   | _   | _     | 1.0                    |      |

|                                            |    | С |                                                        | V <sub>DDREG</sub>                                        |     | _     | 70 <sup>13</sup>       |      |

| I <sub>DDH1</sub>                          | СС | D | Operating current                                      | V <sub>DDEH1</sub>                                        | _   | _     | See note <sup>14</sup> | mA   |

| I <sub>DDH4</sub><br>I <sub>DDH6</sub>     |    | D | V <sub>DDE</sub> <sup>14</sup> supplies                | V <sub>DDEH4</sub>                                        | _   | _     |                        |      |

| I <sub>DDH7</sub><br>I <sub>DD7</sub>      |    | D |                                                        | V <sub>DDEH6</sub>                                        | _   | _     |                        |      |

| I <sub>DDH9</sub>                          |    | D |                                                        | V <sub>DDEH7</sub>                                        |     |       |                        |      |

| I <sub>DD12</sub>                          |    | D |                                                        | V <sub>DDE7</sub>                                         |     |       |                        |      |

|                                            |    | D |                                                        | V <sub>DDEH9</sub>                                        | _   | _     |                        |      |

|                                            |    | D |                                                        | V <sub>DDE12</sub>                                        | _   | _     |                        |      |

# 3.16 AC specifications

# 3.16.1 Pad AC specifications

| Name                       |     | с   |           | elay (ns) <sup>2,3</sup><br>h-High /<br>o-Low | Rise/Fall E | Rise/Fall Edge (ns) <sup>3,4</sup> |                 | SRC/DSC         |

|----------------------------|-----|-----|-----------|-----------------------------------------------|-------------|------------------------------------|-----------------|-----------------|

|                            |     |     | Min       | Max                                           | Min         | Max                                |                 | MSB,LSB         |

| Medium <sup>5,6,7</sup>    | CC  | D   | 4.6/3.7   | 12/12                                         | 2.2/2.2     | 7/7                                | 50              | 11 <sup>8</sup> |

|                            |     |     | 1         |                                               | N/A         |                                    |                 | 10 <sup>9</sup> |

|                            | CC  | D   | 12/13     | 28/34                                         | 5.6/6       | 15/15                              | 50              | 01              |

|                            | CC  | D   | 69/71     | 152/165                                       | 34/35       | 74/74                              | 50              | 00              |

| Slow <sup>7,10</sup>       | CC  | D   | 7.3/5.7   | 19/18                                         | 4.4/4.3     | 14/14                              | 50              | 11 <sup>8</sup> |

|                            | N/A |     |           |                                               |             |                                    |                 | 10 <sup>9</sup> |

|                            | CC  | D   | 26/27     | 61/69                                         | 13/13       | 34/34                              | 50              | 01              |

|                            | CC  | D   | 137/142   | 320/330                                       | 72/74       | 164/164                            | 50              | 00              |

| MultiV <sup>11</sup>       | CC  | D   | 4.1/3.6   | 10.3/8.9                                      | 3.28/2.98   | 8/8                                | 50              | 11 <sup>8</sup> |

| (High Swing Mode)          | N/A |     |           |                                               |             |                                    | 10 <sup>9</sup> |                 |

|                            | CC  | D   | 8.38/6.11 | 16/12.9                                       | 5.48/4.81   | 11/11                              | 50              | 01              |

|                            | CC  | D   | 61.7/10.4 | 92.2/24.3                                     | 42.0/12.2   | 63/63                              | 50              | 00              |

| MultiV<br>(Low Swing Mode) | СС  | D   | 2.31/2.34 | 7.62/6.33                                     | 1.26/1.67   | 6.5/4.4                            | 30              | 11 <sup>8</sup> |

| Fast <sup>12</sup>         | 1   | N/A |           |                                               |             |                                    |                 | •               |

| pad_i_hv <sup>13</sup>     | CC  | D   | 0.5/0.5   | 1.9/1.9                                       | 0.3/0.3     | ±1.5/1.5                           | 0.5             | N/A             |

| pull_hv                    | CC  | D   | NA        | 6000                                          |             | 5000/5000                          | 50              | N/A             |

### Table 35. Pad AC specifications (5.0 V)<sup>1</sup>

<sup>1</sup> These are worst case values that are estimated from simulation and not tested. The values in the table are simulated at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$

$^2\,$  This parameter is supplied for reference and is not guaranteed by design and not tested.

$^3\,$  Delay and rise/fall are measured to 20% or 80% of the respective signal.

- <sup>4</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

- <sup>5</sup> In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- <sup>6</sup> Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- <sup>7</sup> Output delay is shown in Figure 9. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- <sup>8</sup> Can be used on the tester.

- <sup>9</sup> This drive select value is not supported. If selected, it will be approximately equal to 11.

- <sup>10</sup> Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- <sup>11</sup> Selectable high/low swing IO pad with selectable slew in high swing mode only.

- <sup>12</sup> Fast pads are 3.3 V pads.

MPC5644A Microcontroller Data Sheet, Rev. 7

### 3.17 **AC timing**

### Reset and configuration pin timing 3.17.1

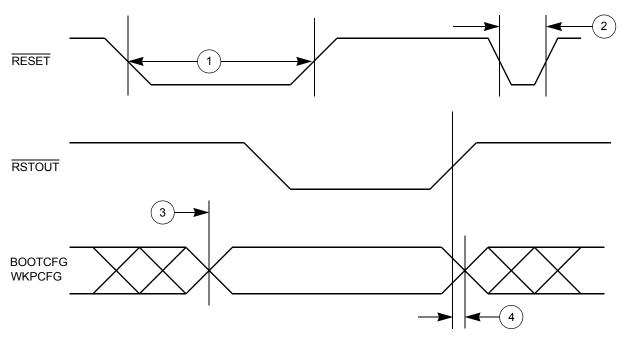

## Table 37. Reset and Configuration Pin Timing<sup>1</sup>

| # | Characteristic                                     | Symbol            | Min | Max | Unit             |

|---|----------------------------------------------------|-------------------|-----|-----|------------------|

| 1 | RESET Pulse Width <sup>2</sup>                     | t <sub>RPW</sub>  | 10  | —   | t <sub>cyc</sub> |

| 2 | RESET Glitch Detect Pulse Width                    | t <sub>GPW</sub>  | 2   | —   | t <sub>cyc</sub> |

| 3 | PLLREF, BOOTCFG, WKPCFG Setup Time to RSTOUT Valid | t <sub>RCSU</sub> | 10  | —   | t <sub>cyc</sub> |

| 4 | PLLREF, BOOTCFG, WKPCFG Hold Time to RSTOUT Valid  | t <sub>RCH</sub>  | 0   | _   | t <sub>cyc</sub> |

<sup>1</sup> Reset timing specified at:  $V_{DDEH} = 3.0 \text{ V}$  to 5.25 V,  $V_{DD} = 1.14 \text{ V}$  to 1.32 V,  $T_A = T_L$  to  $T_H$ . <sup>2</sup> RESET pulse width is measured from 50% of the falling edge to 50% of the rising edge.

Figure 10. Reset and Configuration Pin Timing

| #  | Symbol             |    | С | Characteristic                                                                 | Min. Value | Max. Value | Unit |

|----|--------------------|----|---|--------------------------------------------------------------------------------|------------|------------|------|

| 11 | t <sub>NTDIS</sub> | CC | D | TDI Data Setup Time                                                            | 5          | —          | ns   |

| 12 | t <sub>NTDIH</sub> | CC | D | TDI Data Hold Time                                                             | 25         | —          | ns   |

| 13 | t <sub>NTMSS</sub> | CC | D | TMS Data Setup Time                                                            | 5          | —          | ns   |

| 14 | t <sub>NTMSH</sub> | CC | D | TMS Data Hold Time                                                             | 25         | _          | ns   |

| 15 | _                  | CC | D | TDO propagation delay from falling edge of TCK                                 | —          | 19.5       | ns   |

| 16 | —                  | CC | D | TDO hold time with respect to TCK falling edge (minimum TDO propagation delay) | 5.25       | _          | ns   |

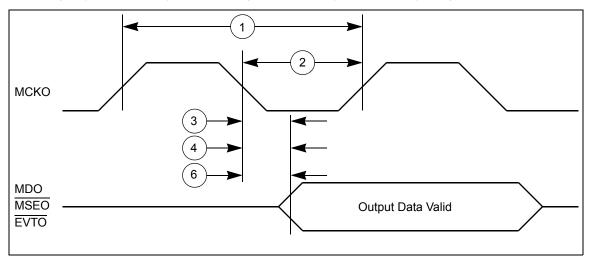

Table 39. Nexus debug port timing<sup>1</sup> (continued)

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V with multi-voltage pads programmed to Low-Swing mode,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

<sup>2</sup> Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

<sup>3</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

<sup>4</sup> This may require setting the MCO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

- <sup>5</sup> MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- <sup>6</sup> Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

- <sup>7</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

- <sup>8</sup> This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 15. Nexus output timing

|                                                                                                                                                                                                                                                        | MECHANICAL OUTLINES<br>DICTIONARY                                        |                              | DOCUMENT NO: 98ASS23840W |          |  |  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------------------|--------------------------|----------|--|--|--|--|--|--|

| <b>Treescale</b><br>serviconductor                                                                                                                                                                                                                     |                                                                          |                              | PAGE:                    | 1158     |  |  |  |  |  |  |

| © FREESCALE SEMICONDUCTOR, INC. ALL RIGHTS RESERVED.<br>ELECTRONIC VERSIONS ARE UNCONTROLLED EXCEPT WHEN ACCESSED<br>DIRECTLY FROM THE DOCUMENT CONTROL REPOSITORY. PRINTED VERSIONS<br>ARE UNCONTROLLED EXCEPT WHEN STAMPED "CONTROLLED COPY" IN RED. | DO NOT SCALE                                                             | THIS DRAWING                 | REV:                     | D        |  |  |  |  |  |  |

| NOTES:                                                                                                                                                                                                                                                 |                                                                          |                              |                          |          |  |  |  |  |  |  |

| 1. ALL DIMENSIONS IN MILLIME                                                                                                                                                                                                                           | TERS                                                                     |                              |                          |          |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                        | DIMENSIONING AND TOLERANCING PER ASME Y14.5M-1994.                       |                              |                          |          |  |  |  |  |  |  |

| $\land$                                                                                                                                                                                                                                                | MAXIMUM SOLDER BALL DIAMETER MEASURED PARALLEL TO DATUM A.               |                              |                          |          |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                        | DATUM A, THE SEATING PLANE, IS DETERMINED BY THE SPHERICAL CROWNS OF THE |                              |                          |          |  |  |  |  |  |  |

| SOLDER BALLS.                                                                                                                                                                                                                                          |                                                                          |                              |                          |          |  |  |  |  |  |  |

| DARALLELISM MEASUREMENT SHALL EXCLUDE ANY EFFECT OF MARK ON TOP SUF                                                                                                                                                                                    |                                                                          |                              |                          |          |  |  |  |  |  |  |