Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | e200z4                                                       |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 120MHz                                                       |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                            |

| Peripherals                | DMA, POR, PWM, WDT                                           |

| Number of I/O              | 84                                                           |

| Program Memory Size        | 3MB (3M x 8)                                                 |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 192K x 8                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                |

| Data Converters            | A/D 40x12b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 125°C (TA)                                           |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 176-LQFP                                                     |

| Supplier Device Package    | 176-LQFP (24x24)                                             |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=spc5643af0mlu2r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Supports serial bootloading via FlexCAN bus and eSCI with auto baud rate sensing

- Supports serial bootloading of either Power Architecture code (default) or Freescale VLE code

- Supports booting from calibration bus interface

- Supports censorship protection for internal flash memory

- Provides an option to enable the core watchdog timer

- Provides an option to disable the system watchdog timer

# 1.4.10 eMIOS

The eMIOS timer module provides the capability to generate or measure events in hardware.

The eMIOS module features include:

- Twenty-four 24-bit wide channels

- 3 channels' internal timebases can be shared between channels

- 1 Timebase from eTPU2 can be imported and used by the channels

- Global enable feature for all eMIOS and eTPU timebases

- Dedicated pin for each channel (not available on all package types)

Each channel (0–23) supports the following functions:

- General-purpose input/output (GPIO)

- Single-action input capture (SAIC)

- Single-action output compare (SAOC)

- Output pulse-width modulation buffered (OPWMB)

- Input period measurement (IPM)

- Input pulse-width measurement (IPWM)

- Double-action output compare (DAOC)

- Modulus counter buffered (MCB)

- Output pulse width and frequency modulation buffered (OPWFMB)

# 1.4.11 eTPU2

The eTPU2 is an enhanced co-processor designed for timing control. Operating in parallel with the host CPU, the eTPU2 processes instructions and real-time input events, performs output waveform generation, and accesses shared data without host intervention. Consequently, for each timer event, the host CPU setup and service times are minimized or eliminated. A powerful timer subsystem is formed by combining the eTPU2 with its own instruction and data RAM. High-level assembler/compiler and documentation allows customers to develop their own functions on the eTPU2.

MPC5644A devices feature the second generation of the eTPU, called eTPU2. Enhancements of the eTPU2 over the standard eTPU include:

- The Timer Counter (TCR1), channel logic and digital filters (both channel and the external timer clock input [TCRCLK]) now have an option to run at full system clock speed or system clock / 2.

- Channels support unordered transitions: transition 2 can now be detected before transition 1. Related to this enhancement, the transition detection latches (TDL1 and TDL2) can now be independently negated by microcode.

- A new User Programmable Channel Mode has been added: the blocking, enabling, service request and capture characteristics of this channel mode can be programmed via microcode.

- Microinstructions now provide an option to issue Interrupt and Data Transfer requests selected by channel. They can also be requested simultaneously at the same instruction.

- Channel Flags 0 and 1 can now be tested for branching, in addition to selecting the entry point.

- Channel digital filters can be bypassed.

etc. Each bit in the frame may be configured to serialize either eTPU channels, eMIOS channels or GPIO signals. The DSPI can be configured to serialize data to an external device that implements the Microsecond Bus protocol. There are three identical DSPI blocks on the MPC5644A MCU. The DSPI pins support 5 V logic levels or Low Voltage Differential Signalling (LVDS) to improve high speed operation.

DSPI module features include:

- Selectable LVDS pads working at 40 MHZ for SOUT and SCK pins for DSPI\_B and DSPI\_C

- 3 sources of serialized data: eTPU\_A, eMIOS output channels and memory-mapped register in the DSPI

- 4 destinations for descrialized data: eTPU\_A and eMIOS input channels, SIU external Interrupt input request, memory-mapped register in the DSPI

- 32-bit DSI and TSB modes require 32 PCR registers, 32 GPO and GPI registers in the SIU to select either GPIO, eTPU or eMIOS bits for serialization

- The DSPI Module can generate and check parity in a serial frame

# 1.4.15 eSCI

Three enhanced serial communications interface (eSCI) modules provide asynchronous serial communications with peripheral devices and other MCUs, and include support to interface to Local Interconnect Network (LIN) slave devices. Each eSCI block provides the following features:

- Full-duplex operation

- Standard mark/space non-return-to-zero (NRZ) format

- 13-bit baud rate selection

- Programmable 8-bit or 9-bit, data format

- Programmable 12-bit or 13-bit data format for Timed Serial Bus (TSB) configuration to support the Microsecond bus standard

- Automatic parity generation

- LIN support

- Autonomous transmission of entire frames

- Configurable to support all revisions of the LIN standard

- Automatic parity bit generation

- Double stop bit after bit error

- 10- or 13-bit break support

- Separately enabled transmitter and receiver

- Programmable transmitter output parity

- 2 receiver wake-up methods:

- Idle line wake-up

- Address mark wake-up

- Interrupt-driven operation with flags

- Receiver framing error detection

- Hardware parity checking

- 1/16 bit-time noise detection

- DMA support for both transmit and receive data

- Global error bit stored with receive data in system RAM to allow post processing of errors

# 1.4.16 FlexCAN

The MPC5644A MCU includes three controller area network (FlexCAN) blocks. The FlexCAN module is a communication controller implementing the CAN protocol according to Bosch Specification version 2.0B. The CAN protocol was designed to

- Optional programmable watchdog window mode

- Can optionally cause system reset or interrupt request on timeout

- · Reset by writing a software key to memory mapped register

- Enabled out of reset

- Configuration is protected by a software key or a write-once register

# 1.4.20 Cyclic redundancy check (CRC) module

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC features:

- Support for CRC-16-CCITT (x25 protocol):

- $X^{16} + X^{12} + X^5 + 1$

- Support for CRC-32 (Ethernet protocol):  $- X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

# 1.4.21 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the MPC5644A.

The sources of the ECC errors are:

- Flash

- SRAM

- Peripheral RAM (FlexRay, CAN, eTPU2 Parameter RAM)

# 1.4.22 External bus interface (EBI)

The MPC5644A device features an external bus interface that is available in 324 TEPBGA and calibration packages.

The EBI supports operation at frequencies of system clock /1, /2 and /4, with a maximum frequency support of 80 MHz. Customers running the device at 120 MHz or 132 MHz will use the /2 divider, giving an EBI frequency of 60 MHz or 66 MHz. Customers running the device at 80 MHz will be able to use the /1 divider to have the EBI run at the full 80 MHz frequency.

Features include:

- 1.8 V to 3.3 V  $\pm$  10% I/O (1.6 V to 3.6 V)

- Memory controller with support for various memory types

- 16-bit data bus, up to 22-bit address bus

- Pin muxing included to support 32-bit muxed bus

- Selectable drive strength

- Configurable bus speed modes

- Bus monitor

- Configurable wait states

# Table 3. MPC5644A signal properties (continued)

|                                                              |                                                                                                          | Р                        | PCR                                  |                  | I/O                  | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup> | Sta          | atus <sup>7</sup>    | Package pin # |     |      |  |

|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------|----------------------|-------------------------------------------------|--------------|----------------------|---------------|-----|------|--|

| Name                                                         | Function <sup>1</sup>                                                                                    | A<br>G <sup>2</sup>      | PA<br>Field <sup>3</sup>             | PCR <sup>4</sup> | 1/О<br>Туре          |                                                 | During Reset | After<br>Reset       | 176           | 208 | 324  |  |

| BOOTCFG[1]<br>IRQ[3]<br>ETRIG3<br>GPIO[212]                  | Boot Config. Input<br>External Interrupt Request<br>eQADC Trigger Input<br>GPIO                          | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 212              | <br> <br> /0         | VDDEH6<br>Slow                                  | — / Down     | BOOTCFG[1] /<br>Down | 85            | M15 | U21  |  |

| WKPCFG<br>NMI<br>DSPI_B_SOUT<br>GPI0[213]                    | Weak Pull Config. Input<br>Non-Maskable Interrupt<br>DSPI D data output<br>GPIO                          | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 213              | <br> <br> /0         | VDDEH6<br>Medium                                | — / Up       | WKPCFG / Up          | 86            | L15 | AA20 |  |

|                                                              |                                                                                                          |                          |                                      | Ext              | ernal B              | us Interface                                    |              |                      |               |     |      |  |

| CS[0]<br>ADDR[8]<br>GPIO[0]                                  | External chip selects<br>External address bus<br>GPIO                                                    | P<br>A1<br>G             | 01<br>10<br>00                       | 0                | 0<br>I/O<br>I/O      | VDDE2<br>Fast                                   | — / Up       | — / Up               | -             | _   | G1   |  |

| CS[1]<br>ADDR9<br>GPIO[1]                                    | External chip selects<br>External address bus<br>GPIO                                                    | P<br>A1<br>G             | 01<br>10<br>00                       | 1                | 0<br>I/O<br>I/O      | VDDE2<br>Fast                                   | — / Up       | — / Up               | -             | -   | H1   |  |

| CS[2]<br>ADDR10<br>WE[2]/BE[2]<br>CAL_WE[2]/BE[2]<br>GPI0[2] | External chip selects<br>External address bus<br>Write/byte enable<br>Cal. bus write/byte enable<br>GPIO | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 2                | 0<br>I/O<br>0<br>I/O | VDDE2<br>Fast                                   | — / Up       | — / Up               | _             | _   | H2   |  |

| CS[3]<br>ADDR11<br>WE[3]/BE[3]<br>CAL_WE[3]/BE[3]<br>GPIO[3] | External chip selects<br>External address bus<br>Write/byte enable<br>Cal bus write/byte enable<br>GPIO  | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 3                | 0<br>I/O<br>0<br>I/O | VDDE2<br>Fast                                   | — / Up       | — / Up               | -             | _   | H4   |  |

| ADDR12<br>GPIO[8]                                            | External address bus<br>GPIO                                                                             | P<br>G                   | 01<br>00                             | 8                | I/O<br>I/O           | VDDE3<br>Fast                                   | — / Up       | — / Up               | _             | —   | N2   |  |

| ADDR13<br>WE[2]<br>GPIO[9]                                   | External address bus<br>Write/byte enable<br>GPIO                                                        | P<br>A2<br>G             | 001<br>100<br>000                    | 9                | I/O<br>O<br>I/O      | VDDE3<br>Fast                                   | — / Up       | — / Up               | -             | _   | N1   |  |

| ADDR14<br>WE[3]<br>GPIO[10]                                  | External address bus<br>Write/byte enables<br>GPIO                                                       | P<br>A2<br>G             | 001<br>100<br>000                    | 10               | I/O<br>O<br>I/O      | VDDE3<br>Fast                                   | — / Up       | — / Up               | -             | _   | P1   |  |

| ADDR15<br>GPIO[11]                                           | External address bus<br>GPIO                                                                             | P<br>G                   | 01<br>00                             | 11               | I/O<br>I/O           | VDDE3<br>Fast                                   | — / Up       | — / Up               | -             | -   | P2   |  |

# Table 3. MPC5644A signal properties (continued)

|                              |                                                 | Р                   | PCR                      |                  | I/O        | Voltage <sup>5</sup> / | Sta          | itus <sup>7</sup> | Package pin # |     |     |  |

|------------------------------|-------------------------------------------------|---------------------|--------------------------|------------------|------------|------------------------|--------------|-------------------|---------------|-----|-----|--|

| Name                         | Function <sup>1</sup>                           | A<br>G <sup>2</sup> | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | Туре       | Pad Type <sup>6</sup>  | During Reset | After<br>Reset    | 176           | 208 | 324 |  |

| CAL_ADDR[17]<br>CAL_DATA[17] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | _   | —   |  |

| CAL_ADDR[18]<br>CAL_DATA[18] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>— / —</i>      | —             | _   | _   |  |

| CAL_ADDR[19]<br>CAL_DATA[19] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | —   | _   |  |

| CAL_ADDR[20]<br>CAL_DATA[20] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | —   | _   |  |

| CAL_ADDR[21]<br>CAL_DATA[21] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | —   | _   |  |

| CAL_ADDR[22]<br>CAL_DATA[22] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[23]<br>CAL_DATA[23] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[24]<br>CAL_DATA[24] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | —   | —   |  |

| CAL_ADDR[25]<br>CAL_DATA[25] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[26]<br>CAL_DATA[26] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[27]<br>CAL_DATA[27] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[28]<br>CAL_DATA[28] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             |     | —   |  |

| CAL_ADDR[29]<br>CAL_DATA[29] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | _   | —   |  |

| CAL_ADDR[30]<br>CAL_DATA[30] | Calibration address bus<br>Calibration data bus | P<br>A              | 01<br>10                 | 345              | I/O<br>I/O | VDDE12<br>Fast         |              | <i>—/—</i>        | —             | _   | —   |  |

| CAL_DATA[0]                  | Calibration data bus                            | Р                   | 01                       | 341              | I/O        | VDDE12<br>Fast         | — / Up       | — / Up            | —             | _   | —   |  |

| CAL_DATA[1]                  | Calibration data bus                            | Р                   | 01                       | 341              | I/O        | VDDE12<br>Fast         | — / Up       | — / Up            | -             | _   | —   |  |

# Table 3. MPC5644A signal properties (continued)

|                 |                               | Р                   | PCR<br>PA<br>Field <sup>3</sup> | <b>PCR<sup>4</sup></b><br>341 |             | Voltage <sup>5</sup> /<br>Pad Type <sup>6</sup><br>VDDE12<br>Fast | Stat         | tus <sup>7</sup> | Package pin # |     |     |

|-----------------|-------------------------------|---------------------|---------------------------------|-------------------------------|-------------|-------------------------------------------------------------------|--------------|------------------|---------------|-----|-----|

| Name            | Function <sup>1</sup>         | A<br>G <sup>2</sup> |                                 |                               | l/O<br>Type |                                                                   | During Reset | After<br>Reset   | 176           | 208 | 324 |

| CAL_DATA[2]     | Calibration data bus          | Р                   | 01                              |                               | I/O         |                                                                   | — / Up       | — / Up           | —             | _   | —   |

| CAL_DATA[3]     | Calibration data bus          | Ρ                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | _   | —   |

| CAL_DATA[4]     | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | —   |     |

| CAL_DATA[5]     | Calibration data bus          | Ρ                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | _   | —   |

| CAL_DATA[6]     | Calibration data bus          | Ρ                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | _   | —   |

| CAL_DATA[7]     | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | —   | —   |

| CAL_DATA[8]     | Calibration data bus          |                     | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | —   |     |

| CAL_DATA[9]     | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | —   |     |

| CAL_DATA[10]    | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | —             | —   |     |

| CAL_DATA[11]    | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | -             | —   |     |

| CAL_DATA[12]    | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | -             | —   |     |

| CAL_DATA[13]    | Calibration data bus          | Р                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | -             | _   | —   |

| CAL_DATA[14]    | Calibration data bus          | Ρ                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | -             | -   | —   |

| CAL_DATA[15]    | Calibration data bus          | Ρ                   | 01                              | 341                           | I/O         | VDDE12<br>Fast                                                    | — / Up       | — / Up           | -             | -   | —   |

| CAL_RD_WR       | Calibration read/write enable | Р                   | 01                              | 342                           | 0           | VDDE12<br>Fast                                                    |              | <i>/</i>         | -             | -   | —   |

| CAL_WE[0]/BE[0] | Calibration write/byte enable | Ρ                   | 01                              | 342                           | 0           | VDDE12<br>Fast                                                    |              | <i>/</i>         | -             | _   | —   |

# MPC5644A Microcontroller Data Sheet, Rev. 7

# Table 3. MPC5644A signal properties (continued)

|                                                                                                 |                                                                                                                        | Р                        | PCR                                  |                  | I/O                  | Voltage <sup>5</sup> /     | Sta           | atus <sup>7</sup> |     | Packag | je pin # |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------|----------------------|----------------------------|---------------|-------------------|-----|--------|----------|

| Name                                                                                            | Function <sup>1</sup>                                                                                                  | A<br>G <sup>2</sup>      | PA<br>Field <sup>3</sup>             | PCR <sup>4</sup> | Туре                 | Pad Type <sup>6</sup>      | During Reset  | After<br>Reset    | 176 | 208    | 324      |

| ETPUA0<br>ETPUA12_O <sup>8</sup><br>ETPUA19_O <sup>8</sup><br>GPIO[114]                         | eTPU A channel<br>eTPU A channel (output only)<br>eTPU A channel (output only)<br>GPIO                                 | P<br>A1<br>A2<br>G       | 001<br>010<br>100<br>000             | 114              | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow             | — /<br>WKPCFG | — /<br>WKPCFG     | 61  | N3     | Y12      |

| ETPUA1<br>ETPUA13_O <sup>8</sup><br>GPIO[115]                                                   | eTPU A channel<br>eTPU A channel (output only)<br>GPIO                                                                 | P<br>A1<br>G             | 01<br>10<br>00                       | 115              | I/O<br>O<br>I/O      | VDDEH4<br>Slow             | — /<br>WKPCFG | — /<br>WKPCFG     | 60  | M3     | W12      |

| ETPUA2<br>ETPUA14_O <sup>8</sup><br>GPIO[116]                                                   | eTPU A channel<br>eTPU A channel (output only)<br>GPIO                                                                 | P<br>A1<br>G             | 01<br>10<br>00                       | 116              | I/O<br>O<br>I/O      | VDDEH4<br>Slow             | — /<br>WKPCFG | — /<br>WKPCFG     | 59  | P2     | AA11     |

| ETPUA3<br>ETPUA15_O <sup>8</sup><br>GPIO[117]                                                   | eTPU A channel<br>eTPU A channel (output only)<br>GPIO                                                                 | P<br>A1<br>G             | 01<br>10<br>00                       | 117              | I/O<br>O<br>I/O      | VDDEH4<br>Slow             | — / WKPCFG    | GPIO / WKPCFG     | 58  | P1     | Y11      |

| ETPUA4<br>ETPUA16_O <sup>8</sup><br>FR_B_TX<br>GPIO[118]                                        | eTPU A channel<br>eTPU A channel (output only)<br>Flexray TX data channel B<br>GPIO                                    | P<br>A1<br>A3<br>G       | 0001<br>0010<br>1000<br>0000         | 118              | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow             | — /<br>WKPCFG | — /<br>WKPCFG     | 56  | N2     | W11      |

| ETPUA5<br>ETPUA17_0 <sup>8</sup><br>DSPI_B_SCK_LV<br>DS-<br>FR_B_TX_EN<br>GPI0[119]             | eTPU A channel<br>eTPU A channel (output only)<br>LVDS negative DSPI clock<br>Flexray TX data enable for ch. B<br>GPIO | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 119              | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow +<br>LVDS   | — /<br>WKPCFG | — /<br>WKPCFG     | 54  | M4     | AB11     |

| ETPUA6<br>ETPUA18_0 <sup>8</sup><br>DSPI_B_SCK_LV<br>DS+<br>FR_B_RX<br>GPI0[120]                | eTPU A channel<br>eTPU A channel (output only)<br>LVDS positive DSPI clock<br>Flexray RX data channel B<br>GPIO        | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 120              | I/O<br>O<br>I<br>I/O | VDDEH4<br>Medium +<br>LVDS | — /<br>WKPCFG | — /<br>WKPCFG     | 53  | L3     | AB10     |

| ETPUA7<br>ETPUA19_0 <sup>8</sup><br>DSPI_B_SOUT_L<br>VDS-<br>ETPUA6_0 <sup>8</sup><br>GPI0[121] | eTPU A channel<br>eTPU A channel (output only)<br>LVDS negative DSPI data out<br>eTPU A channel (output only)<br>GPIO  | P<br>A1<br>A2<br>A3<br>G | 0001<br>0010<br>0100<br>1000<br>0000 | 121              | I/O<br>O<br>O<br>I/O | VDDEH4<br>Slow +<br>LVDS   | — /<br>WKPCFG | — /<br>WKPCFG     | 52  | КЗ     | AA10     |

47

• B. Joiner and V. Adams, "Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling," Proceedings of SemiTherm, San Diego, 1999, pp. 212-220.

# **3.4 EMI (electromagnetic interference) characteristics**

| Symbol         | Parameter           | Conditions                          | Clocks                                                            | Frequency<br>Range | Level<br>(Max) | Unit |

|----------------|---------------------|-------------------------------------|-------------------------------------------------------------------|--------------------|----------------|------|

| Radiated       | V <sub>RE_TEM</sub> | V <sub>DDREG</sub> = 5.25 V;        | 16 MHz crystal                                                    | 150 kHz – 50 MHz   | 20             | dBμV |

| electric field | emissions,          | T <sub>A</sub> = 25 °C              | 40 MHz bus50 – 150 MHzNo PLL frequency<br>modulation150 – 500 MHz | 50 – 150 MHz       | 20             |      |

|                |                     | 150 kHz – 30 MHz<br>RBW 9 kHz, Step |                                                                   | 150 – 500 MHz      | 26             |      |

|                |                     | Size 5 kHz                          |                                                                   | 500 – 1000 MHz     | 26             |      |

|                |                     | 30 MHz – 1 GHz -                    |                                                                   | IEC Level          | К              | —    |

|                |                     | RBW 120 kHz, Step                   |                                                                   | SAE Level          | 3              | —    |

|                |                     | Size 80 kHz                         | 16 MHz crystal                                                    | 150 kHz– 50 MHz    | 13             | dBμV |

|                |                     |                                     | 40 MHz bus<br>±2% PLL                                             | 50 – 150 MHz       | 13             |      |

|                |                     |                                     | frequency<br>modulation                                           | 150 – 500 MHz      | 11             |      |

|                |                     |                                     | modulation                                                        | 500 – 1000 MHz     | 13             |      |

|                |                     |                                     |                                                                   | IEC Level          | L              | _    |

|                |                     |                                     |                                                                   | SAE Level          | 2              | —    |

#### Table 12. EMI Testing Specifications<sup>1</sup>

<sup>1</sup> EMI testing and I/O port waveforms per SAE J1752/3 issued 1995-03 and IEC 61967-2.

# 3.5 Electrostatic discharge (ESD) characteristics

# Table 13. ESD ratings<sup>1,2</sup>

| Symbol |    | Parameter                          | Conditions            | Value | Unit |

|--------|----|------------------------------------|-----------------------|-------|------|

| _      | SR | ESD for Human Body Model (HBM)     | —                     | 2000  | V    |

| R1     | SR | HBM circuit description            | —                     | 1500  | Ω    |

| С      | SR |                                    | —                     | 100   | pF   |

| _      | SR | ESD for field induced charge Model | All pins              | 500   | V    |

|        |    | (FDCM)                             | Corner pins           | 750   |      |

|        | SR | Number of pulses per pin           | Positive pulses (HBM) | 1     | —    |

|        |    |                                    | Negative pulses (HBM) | 1     | —    |

| _      | SR | Number of pulses                   | _                     | 1     | —    |

<sup>1</sup> All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

<sup>2</sup> Device failure is defined as: "If after exposure to ESD pulses, the device does not meet the device specification requirements, which includes the complete DC parametric and functional testing at room temperature and hot temperature."

# 3.6 Power management control (PMC) and power on reset (POR) electrical specifications

| ID | Nam    | e  |   | Parameter                                                                                                                                                                                      | Min               | Тур  | Max  | Unit |

|----|--------|----|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------|------|------|

| 1  | Jtemp  | SR |   | Junction temperature                                                                                                                                                                           | -40               | 27   | 150  | °C   |

| 2  | Vddreg | SR | — | PMC 5 V supply voltage V <sub>DDREG</sub>                                                                                                                                                      | 4.75              | 5    | 5.25 | V    |

| 3  | Vdd    | SR |   | Core supply voltage 1.2 V V <sub>DD</sub> when external regulator is used without disabling the internal regulator (PMC unit turned on, LVI monitor active) <sup>1</sup>                       | 1.26 <sup>2</sup> | 1.3  | 1.32 | V    |

| 3a | _      | SR |   | Core supply voltage 1.2 V V <sub>DD</sub> when external regulator is used with a disabled internal regulator (PMC unit turned-off, LVI monitor disabled)                                       | 1.14              | 1.2  | 1.32 | V    |

| 4  | lvdd   | SR | _ | Voltage regulator core supply maximum required DC output current                                                                                                                               | 400               | —    | _    | mA   |

| 5  | Vdd33  | SR | _ | Regulated 3.3 V supply voltage when external regulator is used without disabling the internal regulator (PMC unit turned-on, internal 3.3V regulator enabled, LVI monitor active) <sup>3</sup> | 3.3               | 3.45 | 3.6  | V    |

| 5a | _      | SR |   | Regulated 3.3 V supply voltage when external regulator is used with a disabled internal regulator (PMC unit turned-off, LVI monitor disabled)                                                  | 3                 | 3.3  | 3.6  | V    |

| 6  | _      | SR |   | Voltage regulator 3.3 V supply maximum required DC output current                                                                                                                              | 80                | —    |      | mA   |

#### Table 14. PMC Operating Conditions and External Regulators Supply Voltage

<sup>1</sup> An internal regulator controller can be used to regulate core supply.

$^2$  The minimum supply required for the part to exit reset and enter in normal run mode is 1.28 V.

<sup>3</sup> An internal regulator can be used to regulate 3.3 V supply.

| Current o                               |    | с | Domonotor                                                     | Conditions             |                        | Value |                        | l lució |

|-----------------------------------------|----|---|---------------------------------------------------------------|------------------------|------------------------|-------|------------------------|---------|

| Symbo                                   |    | C | Parameter                                                     | Conditions             | min                    | typ   | max                    | Unit    |

| V <sub>DDREG</sub>                      | SR | _ | Voltage regulator supply voltage                              | _                      | 4.75                   | _     | 5.25                   | V       |

| V <sub>DDPLL</sub>                      | SR | _ | Clock synthesizer operating voltage                           | _                      | 1.14                   | —     | 1.32                   | V       |

| V <sub>SSPLL</sub> –<br>V <sub>SS</sub> | SR | _ | V <sub>SSPLL</sub> to V <sub>SS</sub><br>differential voltage | _                      | -100                   | _     | 100                    | mV      |

| $V_{IL_S}$                              | CC | С | Slow/medium I/O pad<br>input low voltage                      | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | _     | 0.35*V <sub>DDEH</sub> | V       |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 0.40*V <sub>DDEH</sub> |         |

| $V_{IL_F}$                              | CC | С | Fast pad I/O input low voltage                                | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —     | 0.35*V <sub>DDE</sub>  | V       |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | —     | 0.40*V <sub>DDE</sub>  |         |

| $V_{IL\_LS}$                            | CC | С | Multi-voltage I/O pad                                         | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —     | 0.8                    | V       |

|                                         |    | Ρ | Low-swing-mode <sup>5,6,7,</sup><br>8                         | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 1.1                    |         |

| $V_{IL_{HS}}$                           | CC | С | Multi-voltage pad I/O<br>input low voltage in                 | Hysteresis<br>enabled  | V <sub>SS</sub> -0.3   | —     | 0.35 V <sub>DDEH</sub> | V       |

|                                         |    | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | V <sub>SS</sub> -0.3   | _     | 0.4 V <sub>DDEH</sub>  |         |

| $V_{IH_S}$                              | СС | С | Slow/medium pad I/O input high voltage <sup>9</sup>           | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 | V       |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 |         |

| $V_{IH_F}$                              | СС | С | Fast I/O input high voltage                                   | Hysteresis<br>enabled  | 0.65 V <sub>DDE</sub>  | _     | V <sub>DDE</sub> +0.3  | V       |

|                                         |    | Ρ |                                                               | Hysteresis<br>disabled | 0.58 V <sub>DDE</sub>  | _     | V <sub>DDE</sub> +0.3  |         |

| $V_{IH\_LS}$                            | CC | С | Multi-voltage pad I/O input high voltage in                   | Hysteresis<br>enabled  | 2.5                    | _     | V <sub>DDEH</sub> +0.3 | V       |

|                                         |    | Ρ | low-swing-mode <sup>5,6,7,8</sup>                             | Hysteresis<br>disabled | 2.2                    | _     | V <sub>DDEH</sub> +0.3 |         |

| V <sub>IH_HS</sub>                      | CC | С | Multi-voltage I/O input<br>high voltage in                    | Hysteresis<br>enabled  | 0.65 V <sub>DDEH</sub> |       | V <sub>DDEH</sub> +0.3 | V       |

|                                         |    | Ρ | high-swing-mode                                               | Hysteresis<br>disabled | 0.55 V <sub>DDEH</sub> | _     | V <sub>DDEH</sub> +0.3 |         |

| Table 21. DC electrical specifications (con | tinued) |

|---------------------------------------------|---------|

|---------------------------------------------|---------|

# 3.16 AC specifications

# 3.16.1 Pad AC specifications

| Name                       |    | с   |           | elay (ns) <sup>2,3</sup><br>h-High /<br>o-Low | Rise/Fall E | Edge (ns) <sup>3,4</sup> | Drive Load<br>(pF) | SRC/DSC         |  |  |

|----------------------------|----|-----|-----------|-----------------------------------------------|-------------|--------------------------|--------------------|-----------------|--|--|

|                            |    |     | Min       | Max                                           | Min         | Max                      |                    | MSB,LSB         |  |  |

| Medium <sup>5,6,7</sup>    | CC | D   | 4.6/3.7   | 12/12                                         | 2.2/2.2     | 7/7                      | 50                 | 11 <sup>8</sup> |  |  |

|                            |    |     | 1         |                                               | N/A         |                          |                    | 10 <sup>9</sup> |  |  |

|                            | CC | D   | 12/13     | 28/34                                         | 5.6/6       | 15/15                    | 50                 | 01              |  |  |

|                            | CC | D   | 69/71     | 152/165                                       | 34/35       | 74/74                    | 50                 | 00              |  |  |

| Slow <sup>7,10</sup>       | CC | D   | 7.3/5.7   | 19/18                                         | 4.4/4.3     | 14/14                    | 50                 | 11 <sup>8</sup> |  |  |

|                            |    | N/A |           |                                               |             |                          |                    |                 |  |  |

|                            | CC | D   | 26/27     | 61/69                                         | 13/13       | 34/34                    | 50                 | 01              |  |  |

|                            | CC | D   | 137/142   | 320/330                                       | 72/74       | 164/164                  | 50                 | 00              |  |  |

| MultiV <sup>11</sup>       | CC | D   | 4.1/3.6   | 10.3/8.9                                      | 3.28/2.98   | 8/8                      | 50                 | 11 <sup>8</sup> |  |  |

| (High Swing Mode)          |    | N/A |           |                                               |             |                          |                    |                 |  |  |

|                            | CC | D   | 8.38/6.11 | 16/12.9                                       | 5.48/4.81   | 11/11                    | 50                 | 01              |  |  |

|                            | CC | D   | 61.7/10.4 | 92.2/24.3                                     | 42.0/12.2   | 63/63                    | 50                 | 00              |  |  |

| MultiV<br>(Low Swing Mode) | СС | D   | 2.31/2.34 | 7.62/6.33                                     | 1.26/1.67   | 6.5/4.4                  | 30                 | 11 <sup>8</sup> |  |  |

| Fast <sup>12</sup>         | 1  | •   | •         |                                               | N/A         |                          | •                  | •               |  |  |

| pad_i_hv <sup>13</sup>     | CC | D   | 0.5/0.5   | 1.9/1.9                                       | 0.3/0.3     | ±1.5/1.5                 | 0.5                | N/A             |  |  |

| pull_hv                    | CC | D   | NA        | 6000                                          |             | 5000/5000                | 50                 | N/A             |  |  |

#### Table 35. Pad AC specifications (5.0 V)<sup>1</sup>

<sup>1</sup> These are worst case values that are estimated from simulation and not tested. The values in the table are simulated at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V,  $T_A$  =  $T_L$  to  $T_H$

$^2\,$  This parameter is supplied for reference and is not guaranteed by design and not tested.

$^3\,$  Delay and rise/fall are measured to 20% or 80% of the respective signal.

- <sup>4</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

- <sup>5</sup> In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- <sup>6</sup> Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

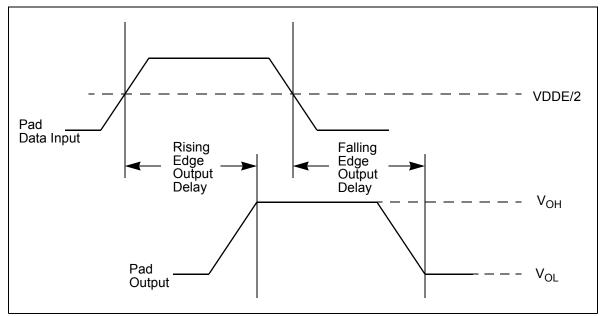

- <sup>7</sup> Output delay is shown in Figure 9. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- <sup>8</sup> Can be used on the tester.

- <sup>9</sup> This drive select value is not supported. If selected, it will be approximately equal to 11.

- <sup>10</sup> Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- <sup>11</sup> Selectable high/low swing IO pad with selectable slew in high swing mode only.

- <sup>12</sup> Fast pads are 3.3 V pads.

- <sup>2</sup> This parameter is supplied for reference and is not guaranteed by design and not tested.

- <sup>3</sup> Delay and rise/fall are measured to 20% or 80% of the respective signal.

- <sup>4</sup> This parameter is guaranteed by characterization before qualification rather than 100% tested.

- <sup>5</sup> In high swing mode, high/low swing pad Vol and Voh values are the same as those of the slew controlled output pads

- <sup>6</sup> Medium Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- <sup>7</sup> Output delay is shown in Figure 9. Add a maximum of one system clock to the output delay for delay with respect to system clock.

- <sup>8</sup> Can be used on the tester.

- <sup>9</sup> This drive select value is not supported. If selected, it will be approximately equal to 11.

- <sup>10</sup> Slow Slew-Rate Controlled Output buffer. Contains an input buffer and weak pullup/pulldown.

- <sup>11</sup> Selectable high/low swing IO pad with selectable slew in high swing mode only.

- <sup>12</sup> Stand alone input buffer. Also has weak pull-up/pull-down.

Figure 9. Pad output delay

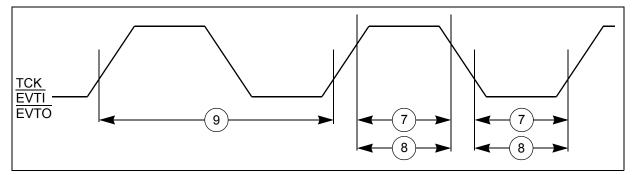

Figure 16. Nexus event trigger and test clock timings

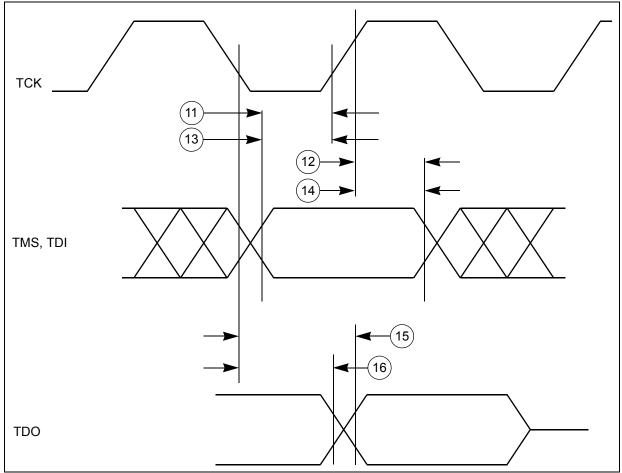

Figure 17. Nexus TDI, TMS, TDO timing

|                     |                                |                                  | l                           | Max. Operating           |                              |                       |

|---------------------|--------------------------------|----------------------------------|-----------------------------|--------------------------|------------------------------|-----------------------|

| Package             | Nexus Width                    | Nexus Routing                    | MDO[0:3]                    | MDO[4:11]                | CAL_MDO[4:1<br>1]            | Frequency             |

| 176 LQFP<br>208 BGA | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

| 324 BGA             | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

| 496 CSP             | Reduced port mode <sup>1</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | GPIO                     | GPIO                         | 40 MHz <sup>3</sup>   |

|                     | Full port<br>mode <sup>4</sup> | Route to MDO <sup>2</sup>        | Nexus Data Out<br>[0:3]     | Nexus Data Out<br>[4:11] | GPIO                         | 40 MHz <sup>5,6</sup> |

|                     |                                | Route to<br>CAL_MDO <sup>7</sup> | Cal Nexus Data<br>Out [0:3] | GPIO                     | Cal Nexus Data<br>Out [4:11] | 40 MHz <sup>3</sup>   |

#### Table 40. Nexus debug port operating frequency

<sup>1</sup> NPC\_PCR[FPM] = 0

<sup>2</sup> NPC\_PCR[NEXCFG] = 0

<sup>3</sup> The Nexus AUX port runs up to 40 MHz. Set NPC\_PCR[MCKO\_DIV] to divide-by-two if the system frequency is greater than 40 MHz.

<sup>4</sup> NPC\_PCR[FPM] = 1

<sup>5</sup> Set the NPC\_PCR[MCKO\_DIV] to divide by two if the system frequency is between 40 MHz and 80 MHz inclusive. Set the NPC\_PCR[MCKO\_DIV] to divide by four if the system frequency is greater than 80 MHz.

<sup>6</sup> Pad restrictions limit the Maximum Operation Frequency in these configurations

<sup>7</sup> NPC\_PCR[NEXCFG] = 1

# 3.17.4 External Bus Interface (EBI) and calibration bus interface timing

| Port<br>Width | Multiplexed<br>Mode | ADDR[12:15]<br>Pin Usage | ADDR[16:31]<br>Pin Usage   | DATA[0:15]<br>Pin Usage   | Max. Operating<br>Frequency |

|---------------|---------------------|--------------------------|----------------------------|---------------------------|-----------------------------|

| 16-bit        | Yes                 | ADDR[12:15]              | GPIO                       | ADDR[16:31]<br>DATA[0:15] | 66 MHz <sup>1</sup>         |

| 16-bit        | No                  | ADDR[12:15]              | ADDR[16:31]                | DATA[0:15]                | 33 MHz <sup>2,3</sup>       |

| 32-bit        | Yes                 | ADDR[12:15]              | ADDR[16:31]<br>DATA[16:31] | DATA[0:15]                | 33 MHz <sup>2,3</sup>       |

Table 41. External Bus Interface maximum operating frequency

<sup>1</sup> Set SIU\_ECCR[EBDF] to divide by two or divide by four if the system frequency is greater than 66 MHz.

<sup>2</sup> System Frequency must be  $\leq$ 132 MHz and SIU\_ECCR[EBDF] set to divide by four.

<sup>3</sup> Pad restrictions limit the maximum operating frequency.

#### Table 42. Calibration bus interface maximum operating frequency

| Port<br>Width | Multiplexed<br>Mode | CAL_ADDR[12:15]<br>Pin Usage | CAL_ADDR[16:30]<br>Pin Usage       | CAL_DATA[0:15]<br>Pin Usage       | Max. Operating<br>Frequency |

|---------------|---------------------|------------------------------|------------------------------------|-----------------------------------|-----------------------------|

| 16-bit        | Yes                 | GPIO                         | GPIO                               | CAL_ADDR[12:30]<br>CAL_DATA[0:15] | 66 MHz <sup>1</sup>         |

| 16-bit        | No                  | CAL_ADDR[12:15]              | CAL_ADDR[16:30]                    | CAL_DATA[0:15]                    | 66 MHz <sup>1</sup>         |

| 32-bit        | Yes                 | CAL_WE[2:3]<br>CAL_DATA[31]  | CAL_ADDR[16:30]<br>CAL_DATA[16:30] | CAL_ADDR[0:15]<br>CAL_DATA[0:15]  | 66 MHz <sup>1</sup>         |

<sup>1</sup> Set SIU\_ECCR[EBDF] to divide by two or divide by four if the system frequency is greater than 66 MHz

| Table 45. External bus interface (EDI) and cambration bus operation timing | Table 43. | External bus interface | (EBI | ) and calibration bus operation timing <sup>1</sup> |

|----------------------------------------------------------------------------|-----------|------------------------|------|-----------------------------------------------------|

|----------------------------------------------------------------------------|-----------|------------------------|------|-----------------------------------------------------|

| # | Sumh             |     | с | Characteristic                                                                                                                                                      | 66 MHz ( | ext. bus) <sup>2</sup> | Unit           | Notes                                                |  |

|---|------------------|-----|---|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|------------------------|----------------|------------------------------------------------------|--|

| # | Symb             | 100 | C | Characteristic                                                                                                                                                      | Min      | Max                    | Unit           | NOLES                                                |  |

| 1 | Т <sub>С</sub>   | CC  | Ρ | CLKOUT Period                                                                                                                                                       | 15.2     | —                      | ns             | Signals are<br>measured at 50%<br>V <sub>DDE</sub> . |  |

| 2 | t <sub>CDC</sub> | CC  | D | CLKOUT duty cycle                                                                                                                                                   | 45%      | 55%                    | Т <sub>С</sub> |                                                      |  |

| 3 | t <sub>CRT</sub> | CC  | D | CLKOUT rise time                                                                                                                                                    | —        | 3                      | ns             |                                                      |  |

| 4 | t <sub>CFT</sub> | CC  | D | CLKOUT fall time                                                                                                                                                    | —        | 3                      | ns             |                                                      |  |

| 5 | <sup>t</sup> сон | CC  | D | CLKOUT Posedge to Output Signal<br>Invalid or High Z(Hold Time)<br>• ADDR[8:31]<br>• CS[0:3]<br>• DATA[0:31]<br>• OE<br>• RD_WR<br>• <u>TS</u><br>• WE[0:3]/BE[0:3] | 1.3      |                        | ns             |                                                      |  |

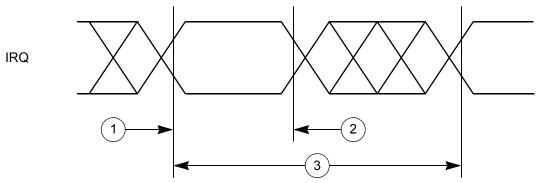

# 3.17.5 External interrupt timing (IRQ pin)

| # | Characteristic                     | Symbol            | Min | Max | Unit             |

|---|------------------------------------|-------------------|-----|-----|------------------|

| 1 | IRQ Pulse Width Low                | t <sub>IPWL</sub> | 3   | —   | t <sub>cyc</sub> |

| 2 | IRQ Pulse Width High               | t <sub>IPWH</sub> | 3   | —   | t <sub>cyc</sub> |

| 3 | IRQ Edge to Edge Time <sup>2</sup> | t <sub>ICYC</sub> | 6   | —   | t <sub>cyc</sub> |

| 3 | IRQ Edge to Edge Time <sup>2</sup> | 4                 | 6   | —   |                  |

Table 44. External interrupt timing<sup>1</sup>

<sup>1</sup> IRQ timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 3.0 V to 5.5 V,  $V_{DD33}$  and  $V_{DDSYN}$  = 3.0 V to 3.6 V,  $T_A = T_L$  to  $T_H$ .

<sup>2</sup> Applies when IRQ pins are configured for rising edge or falling edge events, but not both.

Figure 22. External Interrupt Timing

# 3.17.6 eTPU timing

#### Table 45. eTPU timing<sup>1</sup>

| # | Characteristic                  | Symbol            | Min            | Max | Unit             |

|---|---------------------------------|-------------------|----------------|-----|------------------|

| 1 | eTPU Input Channel Pulse Width  | t <sub>ICPW</sub> | 4              | _   | t <sub>cyc</sub> |

| 2 | eTPU Output Channel Pulse Width | t <sub>OCPW</sub> | 2 <sup>2</sup> |     | t <sub>cyc</sub> |

<sup>1</sup> eTPU timing specified at V<sub>DD</sub> = 1.08 V to 1.32 V, V<sub>DDEH</sub> = 3.0 V to 5.5 V, V<sub>DD33</sub> and V<sub>DDSYN</sub> = 3.0 V to 3.6 V,  $T_A = T_L$  to  $T_H$ , and  $C_L = 200$  pF with SRC = 0b00.

<sup>2</sup> This specification does not include the rise and fall times. When calculating the minimum eTPU pulse width, include the rise and fall times defined in the slew rate control fields (SRC) of the pad configuration registers (PCR).

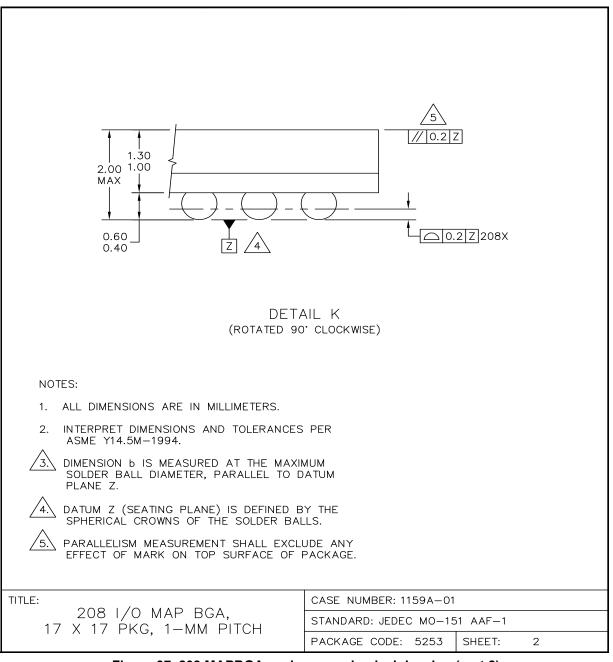

Figure 37. 208 MAPBGA package mechanical drawing (part 2)

| Revision | Date               | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|----------|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 2   | 11/2009            | Maximum device speed is 145 MHz (was 150 MHz)                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                    | 16-entry Memory Protection Unit (MPU). Was incorrectly listed as 8-entry.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|          |                    | Feature details section added                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                    | Changes to signal summary table: <ul> <li>Added ANY function to AN[10]</li> <li>Added ANW function to AN[8]</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                           |

|          |                    | Changes to 208 ball BGA ballmap:<br>• A12 is AN12-SDS (was AN12)<br>• A15 is VRC33 (was VDD33)<br>• B12 is AN13-SDO (was AN13)<br>• C12 is AN14SDI (was AN14)<br>• C13 is AN15-FCK (was AN15)<br>• D1 is VRC33 (was VDD33)<br>• F13 is VDDEH6AB (was VDDEH6)<br>• H13 is GPIO99 (was PCSA3)<br>• J15 is GPIO98 (was PCSA2)<br>• K4 is now VDDEH1AB (was VDDEH1)<br>• N6 is now VRC33 (was VDD33)<br>• N9 is VDDEH4AB (was VDDEH4)<br>• N12 is now VRC33 (was VDD33)<br>• P6 is now NC<br>• T13 is VDDE5 (was NC) |

| Rev. 2   | 11/2009<br>(cont.) | Recommended operating characteristics for power transistor updated<br>Pad current specifications updated                                                                                                                                                                                                                                                                                                                                                                                                         |

|          |                    | LVDS pad specifications updated. SRC does not apply to common mode voltage.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                    | Temperature sensor electrical characteristics added                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|          |                    | eQADC electrical characteristics updated with VGA gain specs                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|          |                    | Pad AC specifications updated                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                    | Definition for RDY signal added to signal details                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|          |                    | $V_{STBY}$ maximum is 5.5 V (was listed incorrectly as 6.0 V)                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|          |                    | I <sub>MAXA</sub> maximum is 5 mA (was TBD)                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|          |                    | Analog differential input functions added to AN0–AN7 in signal summary                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### Table 53. Revision history (continued)

| Revision         | Date    | Substantive changes                                                                                                                                                                                   |

|------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 4<br>(cont) | 08/2010 | Change in signal name notation for DSPI, CAN and SCI signals:                                                                                                                                         |

| (0011)           |         | DSPI:                                                                                                                                                                                                 |

|                  |         | PCS_x[n] is now DSPI_x_PCS[n]                                                                                                                                                                         |

|                  |         | SOUT_x is now DSPI_x_SOUT                                                                                                                                                                             |

|                  |         | SIN_x is now DSPI_x_SIN                                                                                                                                                                               |

|                  |         | SCK_x is now DSPI_x_SCK                                                                                                                                                                               |

|                  |         | CAN:                                                                                                                                                                                                  |

|                  |         | CNTXx is now CAN_x_TX                                                                                                                                                                                 |

|                  |         | CNRXx is now CAN_x_RX                                                                                                                                                                                 |

|                  |         | SCI:                                                                                                                                                                                                  |

|                  |         | RXDx is now SCI x RX                                                                                                                                                                                  |

|                  |         | TXDx is now SCI_x_TX                                                                                                                                                                                  |

|                  |         | Updates to DC electrical specifications:                                                                                                                                                              |

|                  |         | Slew rate on power supply pins specification changed to 25 V/ms (was 50 V/ms)                                                                                                                         |

|                  |         | $V_{OH\_LS}\text{min}$ spec changed to 2.0 V at 0.5 mA (was 2.7 V at 0.5 mA)                                                                                                                          |

|                  |         | Updated I/O pad current specifications                                                                                                                                                                |

|                  |         | Updated I/O pad V <sub>RC33</sub> current specifications                                                                                                                                              |

|                  |         | Corrections to Nexus timing:                                                                                                                                                                          |

|                  |         | <ul> <li>Maximum Nexus debug port operating frequency is 40 MHz in all configurations</li> <li>To route Nexus to MDO, clear NPC_PCR[NEXCFG] (formerly this was documented as NDC_DCDFCALL)</li> </ul> |

|                  |         | <ul> <li>NPC_PCR[CAL]</li> <li>To route Nexus to CAL MDO, set NPC PCR[NEXCFG]=1 (formerly this was</li> </ul>                                                                                         |

|                  |         | documented as NPC_PCR[CAL]                                                                                                                                                                            |

#### Table 53. Revision history (continued)

\_\_\_\_\_

| Revision Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |