#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                 |

|----------------------------|------------------------------------------------------------------------|

| Core Processor             | e200z4                                                                 |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 120MHz                                                                 |

| Connectivity               | CANbus, EBI/EMI, LINbus, SCI, SPI                                      |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 151                                                                    |

| Program Memory Size        | 3MB (3M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                |                                                                        |

| RAM Size                   | 192K x 8                                                               |

| Voltage - Supply (Vcc/Vdd) | 1.14V ~ 5.25V                                                          |

| Data Converters            | A/D 40x12b                                                             |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

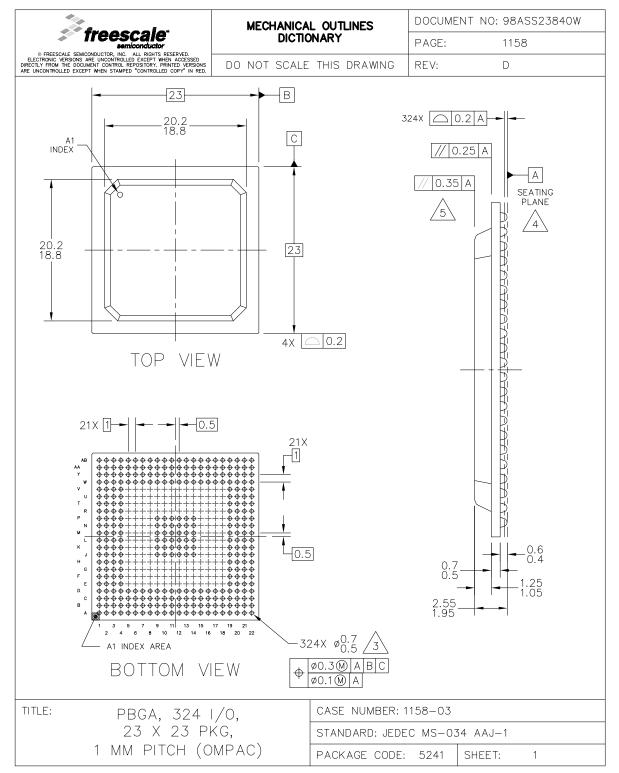

| Package / Case             | 324-BBGA                                                               |

| Supplier Device Package    | 324-PBGA (23x23)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5643af0mvz2 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.4.5 Memory protection unit (MPU)

The Memory Protection Unit (MPU) provides hardware access control for all memory references generated in a device. Using preprogrammed region descriptors, which define memory spaces and their associated access rights, the MPU concurrently monitors all system bus transactions and evaluates the appropriateness of each transfer. Memory references with sufficient access control rights are allowed to complete; references that are not mapped to any region descriptor or have insufficient rights are terminated with a protection error response.

The MPU has these major features:

- Support for 16 memory region descriptors, each 128 bits in size

- Specification of start and end addresses provide granularity for region sizes from 32 bytes to 4 GB

- MPU is invalid at reset, thus no access restrictions are enforced

- Two types of access control definitions: processor core bus master supports the traditional {read, write, execute} permissions with independent definitions for supervisor and user mode accesses; the remaining non-core bus masters (eDMA, FlexRay, and EBI<sup>1</sup>) support {read, write} attributes

- Automatic hardware maintenance of the region descriptor valid bit removes issues associated with maintaining a coherent image of the descriptor

- Alternate memory view of the access control word for each descriptor provides an efficient mechanism to dynamically alter the access rights of a descriptor only<sup>1</sup>

- For overlapping region descriptors, priority is given to permission granting over access denying as this approach

provides more flexibility to system software

- Support for two XBAR slave port connections (SRAM and PBRIDGE)

- For each connected XBAR slave port (SRAM and PBRIDGE), MPU hardware monitors every port access using the pre-programmed memory region descriptors

- An access protection error is detected if a memory reference does not hit in any memory region or the reference is flagged as illegal in all memory regions where it does hit. In the event of an access error, the XBAR reference is terminated with an error response and the MPU inhibits the bus cycle being sent to the targeted slave device

- 64-bit error registers, one for each XBAR slave port, capture the last faulting address, attributes, and detail information

## 1.4.6 FMPLL

The FMPLL allows the user to generate high speed system clocks from a 4 MHz to 40 MHz crystal oscillator or external clock generator. Further, the FMPLL supports programmable frequency modulation of the system clock. The PLL multiplication factor, output clock divider ratio are all software configurable. The PLL has the following major features:

- Input clock frequency from 4 MHz to 40 MHz

- Reduced frequency divider (RFD) for reduced frequency operation without forcing the PLL to relock

- Three modes of operation

- Bypass mode with PLL off

- Bypass mode with PLL running (default mode out of reset)

- PLL normal mode

- Each of the three modes may be run with a crystal oscillator or an external clock reference

- Programmable frequency modulation

- Modulation enabled/disabled through software

- Triangle wave modulation up to 100 kHz modulation frequency

- Programmable modulation depth (0% to 2% modulation depth)

- Programmable modulation frequency dependent on reference frequency

<sup>1.</sup> EBI not available on all packages and is not available, as a master, for customer.

- Supports serial bootloading via FlexCAN bus and eSCI with auto baud rate sensing

- Supports serial bootloading of either Power Architecture code (default) or Freescale VLE code

- Supports booting from calibration bus interface

- Supports censorship protection for internal flash memory

- Provides an option to enable the core watchdog timer

- Provides an option to disable the system watchdog timer

## 1.4.10 eMIOS

The eMIOS timer module provides the capability to generate or measure events in hardware.

The eMIOS module features include:

- Twenty-four 24-bit wide channels

- 3 channels' internal timebases can be shared between channels

- 1 Timebase from eTPU2 can be imported and used by the channels

- Global enable feature for all eMIOS and eTPU timebases

- Dedicated pin for each channel (not available on all package types)

Each channel (0–23) supports the following functions:

- General-purpose input/output (GPIO)

- Single-action input capture (SAIC)

- Single-action output compare (SAOC)

- Output pulse-width modulation buffered (OPWMB)

- Input period measurement (IPM)

- Input pulse-width measurement (IPWM)

- Double-action output compare (DAOC)

- Modulus counter buffered (MCB)

- Output pulse width and frequency modulation buffered (OPWFMB)

## 1.4.11 eTPU2

The eTPU2 is an enhanced co-processor designed for timing control. Operating in parallel with the host CPU, the eTPU2 processes instructions and real-time input events, performs output waveform generation, and accesses shared data without host intervention. Consequently, for each timer event, the host CPU setup and service times are minimized or eliminated. A powerful timer subsystem is formed by combining the eTPU2 with its own instruction and data RAM. High-level assembler/compiler and documentation allows customers to develop their own functions on the eTPU2.

MPC5644A devices feature the second generation of the eTPU, called eTPU2. Enhancements of the eTPU2 over the standard eTPU include:

- The Timer Counter (TCR1), channel logic and digital filters (both channel and the external timer clock input [TCRCLK]) now have an option to run at full system clock speed or system clock / 2.

- Channels support unordered transitions: transition 2 can now be detected before transition 1. Related to this enhancement, the transition detection latches (TDL1 and TDL2) can now be independently negated by microcode.

- A new User Programmable Channel Mode has been added: the blocking, enabling, service request and capture characteristics of this channel mode can be programmed via microcode.

- Microinstructions now provide an option to issue Interrupt and Data Transfer requests selected by channel. They can also be requested simultaneously at the same instruction.

- Channel Flags 0 and 1 can now be tested for branching, in addition to selecting the entry point.

- Channel digital filters can be bypassed.

- Optional programmable watchdog window mode

- Can optionally cause system reset or interrupt request on timeout

- · Reset by writing a software key to memory mapped register

- Enabled out of reset

- Configuration is protected by a software key or a write-once register

## 1.4.20 Cyclic redundancy check (CRC) module

The CRC computing unit is dedicated to the computation of CRC off-loading the CPU. The CRC features:

- Support for CRC-16-CCITT (x25 protocol):

- $X^{16} + X^{12} + X^5 + 1$

- Support for CRC-32 (Ethernet protocol):  $- X^{32} + X^{26} + X^{23} + X^{22} + X^{16} + X^{12} + X^{11} + X^{10} + X^8 + X^7 + X^5 + X^4 + X^2 + X + 1$

- Zero wait states for each write/read operations to the CRC\_CFG and CRC\_INP registers at the maximum frequency

## 1.4.21 Error correction status module (ECSM)

The ECSM provides a myriad of miscellaneous control functions regarding program-visible information about the platform configuration and revision levels, a reset status register, a software watchdog timer, wakeup control for exiting sleep modes, and information on platform memory errors reported by error-correcting codes and/or generic access error information for certain processor cores.

The Error Correction Status Module supports a number of miscellaneous control functions for the platform. The ECSM includes these features:

- Registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented

- For test purposes, optional registers to specify the generation of double-bit memory errors are enabled on the MPC5644A.

The sources of the ECC errors are:

- Flash

- SRAM

- Peripheral RAM (FlexRay, CAN, eTPU2 Parameter RAM)

## 1.4.22 External bus interface (EBI)

The MPC5644A device features an external bus interface that is available in 324 TEPBGA and calibration packages.

The EBI supports operation at frequencies of system clock /1, /2 and /4, with a maximum frequency support of 80 MHz. Customers running the device at 120 MHz or 132 MHz will use the /2 divider, giving an EBI frequency of 60 MHz or 66 MHz. Customers running the device at 80 MHz will be able to use the /1 divider to have the EBI run at the full 80 MHz frequency.

Features include:

- 1.8 V to 3.3 V  $\pm$  10% I/O (1.6 V to 3.6 V)

- Memory controller with support for various memory types

- 16-bit data bus, up to 22-bit address bus

- Pin muxing included to support 32-bit muxed bus

- Selectable drive strength

- Configurable bus speed modes

- Bus monitor

- Configurable wait states

## 1.5.2 Block summary

Table 2 summarizes the functions of the blocks present on the MPC5644A series microcontrollers.

Table 2. MPC5644A series block summary

| Block                                               | Function                                                                                                                                                                                                                             |

|-----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Boot assist module (BAM)                            | Block of read-only memory containing executable code that searches<br>for user-supplied boot code and, if none is found, executes the BAM<br>boot code resident in device ROM.                                                       |

| Calibration Bus interface                           | Transfers data across the crossbar switch to/from peripherals attached to the calibration system connector.                                                                                                                          |

| Controller area network (FlexCAN)                   | Supports the standard CAN communications protocol.                                                                                                                                                                                   |

| Crossbar switch (XBAR)                              | Internal busmaster.                                                                                                                                                                                                                  |

| Cyclic redundancy check (CRC)                       | CRC checksum generator.                                                                                                                                                                                                              |

| Deserial serial peripheral interface (DSPI)         | Provides a synchronous serial interface for communication with external devices.                                                                                                                                                     |

| e200z4 core                                         | Executes programs and interrupt handlers.                                                                                                                                                                                            |

| Enhanced direct memory access (eDMA)                | Performs complex data movements with minimal intervention from the core.                                                                                                                                                             |

| Enhanced modular input-output system (eMIOS)        | Provides the functionality to generate or measure events.                                                                                                                                                                            |

| Enhanced queued analog-to-digital converter (eQADC) | Provides accurate and fast conversions for a wide range of applications.                                                                                                                                                             |

| Enhanced serial communication interface (eSCI)      | Provides asynchronous serial communication capability with peripheral devices and other microcontroller units.                                                                                                                       |

| Enhanced time processor unit (eTPU2)                | Second-generation co-processor processes real-time input events, performs output waveform generation, and accesses shared data without host intervention.                                                                            |

| Error Correction Status Module (ECSM)               | The Error Correction Status Module supports a number of miscellaneous control functions for the platform, and includes registers for capturing information on platform memory errors if error-correcting codes (ECC) are implemented |

| External bus interface (EBI)                        | Enables expansion of internal bus to enable connection of external memory or peripherals.                                                                                                                                            |

| Flash memory                                        | Provides storage for program code, constants, and variables.                                                                                                                                                                         |

| FlexRay                                             | Provides high-speed distributed control for advanced automotive applications.                                                                                                                                                        |

| Interrupt controller (INTC)                         | Provides priority-based preemptive scheduling of interrupt requests.                                                                                                                                                                 |

| JTAG controller                                     | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode.                                                                                                    |

| Memory protection unit (MPU)                        | Provides hardware access control for all memory references generated.                                                                                                                                                                |

| Nexus port controller (NPC)                         | Provides real-time development support capabilities in compliance with the IEEE-ISTO 5001-2003 standard.                                                                                                                             |

| VSS     | VSS    | VSS      |         |         |         |         | VRC33    | NC       | NC               | VDDEH6AB | м  |

|---------|--------|----------|---------|---------|---------|---------|----------|----------|------------------|----------|----|

| VSS     | VSS    | VSS      |         |         |         |         | NC       | SCI_A_TX | VSS              | NC       | N  |

| VSS     | VSS    | VSS      |         |         |         |         | CAN_C_TX | SCI_A_RX | RSTOUT           | RSTCFG   | Р  |

|         |        |          |         |         |         |         | NC       | NC       | NC               | RESET    | R  |

|         |        |          |         |         |         |         | VSS      | BOOTCFG0 | VSS <sup>1</sup> | VSS      | т  |

|         |        |          |         |         |         |         | VDDEH6AB | PLLCFG1  | BOOTCFG1         | EXTAL    | υ  |

|         |        |          |         |         |         |         | SCI_C_RX | CAN_C_RX | PLLREF           | XTAL     | v  |

| ETPUA1  | EMIOS1 | VDDEH4AB | EMIOS8  | EMIOS15 | EMIOS16 | EMIOS23 | SCI_C_TX | VDD      | CAN_B_RX         | VDDPLL   | w  |

| ETPUA0  | EMIOS2 | EMIOS5   | EMIOS9  | EMIOS14 | EMIOS17 | EMIOS22 | CAN_A_RX | VSS      | VDD              | CAN_B_TX | Y  |

| EMIOS0  | EMIOS3 | EMIOS6   | EMIOS10 | EMIOS13 | EMIOS18 | EMIOS21 | VDDEH4AB | WKPCFG   | VSS              | VDD      | AA |

| TCRCLKA | EMIOS4 | EMIOS7   | EMIOS11 | EMIOS12 | EMIOS19 | EMIOS20 | CAN_A_TX | SCI_B_RX | SCI_B_TX         | VSS      | AB |

| 12      | 13     | 14       | 15      | 16      | 17      | 18      | 19       | 20       | 21               | 22       |    |

<sup>1</sup> This pin (T21) should be tied low.

Figure 7. 324-pin TEPBGA package ballmap (southeast, viewed from above)

## Table 3. MPC5644A signal properties (continued)

| Name                                                      |                                                                                                                                                                                    | Р                                                                   | PCR                      |                  | I/O           | Voltage <sup>5</sup> /            | Sta          | itus <sup>7</sup> | Package pin # |     |     |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------|------------------|---------------|-----------------------------------|--------------|-------------------|---------------|-----|-----|

|                                                           | Function <sup>1</sup>                                                                                                                                                              | A<br>G <sup>2</sup>                                                 | PA<br>Field <sup>3</sup> | PCR <sup>4</sup> | Туре          | Pad Type <sup>6</sup>             | During Reset | After<br>Reset    | 176           | 208 | 324 |

| MDO2 <sup>16</sup>                                        | Nexus message data out                                                                                                                                                             | Р                                                                   | 01                       | 222              | 0             | VRC33<br>Fast                     | —            | MDO[2] / —        | 19            | A13 | G3  |

| MDO3 <sup>16</sup>                                        | Nexus message data out                                                                                                                                                             | Р                                                                   | 01                       | 223              | 0             | VRC33<br>Fast                     | —            | MDO[3] / —        | 20            | B13 | G4  |

| MDO4 <sup>16</sup><br>ETPUA2_O <sup>8</sup><br>GPIO[75]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO[                                                                                                                    | P<br>A1<br>G                                                        | 01<br>10<br>00           | 75               | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>— I —</i>      | 126           | P10 | B19 |

| MDO5 <sup>16</sup><br>ETPUA4_O <sup>8</sup><br>GPIO[76]   | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | P<br>A1<br>G                                                        | 01<br>10<br>00           | 76               | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>_/_</i>        | 129           | T10 | B20 |

| MDO6 <sup>16</sup><br>ETPUA13_O <sup>8</sup><br>GPIO[77]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | eTPU A channel (output only) A1 10 O MultiV <sup>12,14</sup>        |                          | <i>_/_</i>       | 135           | T11                               | C18          |                   |               |     |     |

| MDO7 <sup>16</sup><br>ETPUA19_O <sup>8</sup><br>GPIO[78]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | IPU A channel (output only)   A1   10   O   MultiV <sup>12,14</sup> |                          | <i>_/_</i>       | 136           | N11                               | B18          |                   |               |     |     |

| MDO8 <sup>16</sup><br>ETPUA21_O <sup>8</sup><br>GPIO[79]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | P<br>A1<br>G                                                        | 01<br>10<br>00           | 79               | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>          | 137           | P11 | A18 |

| MDO9 <sup>16</sup><br>ETPUA25_O <sup>8</sup><br>GPIO[80]  | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | P<br>A1<br>G                                                        | 01<br>10<br>00           | 80               | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>_/_</i>        | 139           | Τ7  | D18 |

| MDO10 <sup>16</sup><br>ETPUA27_O <sup>8</sup><br>GPIO[81] | Nexus message data out<br>eTPU A channel (output only)<br>GPIO                                                                                                                     | P<br>A1<br>G                                                        | 01<br>10<br>00           | 81               | 0<br>0<br>I/0 | VDDEH7<br>MultiV <sup>12,14</sup> | —            | <i>/</i>          | 134           | R10 | A19 |

| MDO11 <sup>16</sup><br>ETPUA29_O <sup>8</sup><br>GPIO[82] | Nexus message data out     P     01     82     O     VDDEH7     —       eTPU A channel (output only)     A1     10     O     MultiV <sup>12,14</sup> GPIO[82]     G     00     I/O |                                                                     | <i>/</i>                 | 124              | P9            | C19                               |              |                   |               |     |     |

| MSEO[0] <sup>16</sup>                                     | Nexus message start/end out                                                                                                                                                        | Р                                                                   | 01                       | 224              | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | MSEO[0] /         | 118           | C15 | G21 |

| MSEO[1] <sup>16</sup>                                     | Nexus message start/end out                                                                                                                                                        | Р                                                                   | 01                       | 225              | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | MSEO[1] / —       | 117           | E16 | G22 |

| RDY                                                       | Nexus ready output                                                                                                                                                                 | Р                                                                   | 01                       | 226              | 0             | VDDEH7<br>MultiV <sup>12,14</sup> | —            | _                 | -             | -   | G19 |

Freescale Semiconductor

- <sup>5</sup> The VDDE and VDDEH supply inputs are broken into segments. Each segment of slow I/O pins (VDDEH) may have a separate supply in the 3.3 V to 5.0 V range (-10%/+5%). Each segment of fast I/O (VDDE) may have a separate supply in the 1.8 V to 3.3 V range (+/- 10%).

- <sup>6</sup> See Table 4 for details on pad types.

- <sup>7</sup> The Status During Reset pin is sampled after the internal POR is negated. Prior to exiting POR, the signal has a high impedance. Terminology is O - output, I - input, Up - weak pull up enabled, Down - weak pull down enabled, Low - output driven low, High - output driven high. A dash for the function in this column denotes that both the input and output buffer are turned off. The signal name to the left or right of the slash indicates the pin is enabled.

- <sup>8</sup> Output only.

- <sup>9</sup> When used as ETRIG, this pin must be configured as an input. For GPIO it can be configured either as an input or output.

- <sup>10</sup> Maximum frequency is 50 kHz.

- <sup>11</sup> The SIU\_PCR219 register is unusual in that it controls pads for two separate device pins: GPIO[219] and MCKO. See the MPC5644A Microcontroller Reference Manual (SIU chapter) for details.

- <sup>12</sup> Multivoltage pads are automatically configured in low swing mode when a JTAG or Nexus function is selected, otherwise they are high swing.

- <sup>13</sup> On 176 LQFP and 208 MAPBGA packages, this pin is tied low internally.

- <sup>14</sup> Nexus multivoltage pads default to 5 V operation until the Nexus module is enabled.

- <sup>15</sup> EVTO should be clamped to 3.3 V to prevent possible damage to external tools that only support 3.3 V.

- <sup>16</sup> Do not connect pin directly to a power supply or ground.

- <sup>17</sup> This signal name is used to support legacy naming.

- <sup>18</sup> During and just after POR negates, internal pull resistors can be enabled, resulting in as much as 4 mA of current draw. The pull resistors are disabled when the system clock propagates through the device.

- <sup>19</sup> For pins AN12-AN15, if the analog features are used the VDDEH7 input pins should be tied to VDDA because that segment must meet the VDDA specification to support analog input function.

- <sup>20</sup> Do not use VRC33 to drive external circuits.

- <sup>21</sup> VDDA0 and VDDA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VDDA.

- <sup>22</sup> VSSA0 and VSSA1 are shorted together internally in BGA packages. In the QFP package the two pads are double bonded on one pin called VSSA.

- <sup>23</sup> VDDE2 and VDDE3 are shorted together in all production packages.

- <sup>24</sup> VDDE2 and VDDE3 are shorted together in all production packages.

- <sup>25</sup> VDDEH1A, VDDEH1B, and VDDEH1AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>26</sup> VDDEH4, VDDEH4A, VDDEH4B, and VDDEH4AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

- <sup>27</sup> VDDEH6, VDDEH6A, VDDEH6B, and VDDEH6AB are shorted together in all production packages. The separation of the signal names is present to support legacy naming, however they should be considered as the same signal in this document.

| Power Segment      | Voltage                          | I/O Pins Powered by Segment                                                                                                                                                                                                                 |  |  |  |  |  |  |  |

|--------------------|----------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| VDDA               | 5 V                              | ANO, AN1, AN2, AN3, AN4, AN5, AN6, AN7, AN8, AN9, AN10,<br>AN11, AN16, AN17, AN18, AN19, AN20, AN21, AN22, AN23,<br>AN24, AN25, AN26, AN27, AN28, AN29, AN30, AN31, AN32,<br>AN33, AN34, AN35, AN36, AN37, AN38, AN39, VRH, VRL,<br>REFBYBC |  |  |  |  |  |  |  |

| VRC33 <sup>1</sup> | 3.3 V                            | MCKO, MDO0, MDO1, MDO2, MDO3                                                                                                                                                                                                                |  |  |  |  |  |  |  |

|                    | Other Power Segments             |                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |

| VDDREG             | 5 V                              | —                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| VRCCTL             | —                                | —                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| VDDPLL             | 1.2 V                            | —                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| VSTBY              | 0.95–1.2 V<br>(unregulated mode) | _                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

|                    | 2.0–5.5 V<br>(regulated mode)    | —                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

| VSS                | —                                | _                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |

### Table 6. Power/ground segmentation

<sup>1</sup> Do not use VRC33 to drive external circuits.

| ID | Nam      | е  |   | Parameter                                                                         | Min              | Тур     | Мах              | Unit | Notes |

|----|----------|----|---|-----------------------------------------------------------------------------------|------------------|---------|------------------|------|-------|

| 8a | _        | СС | С | Variation of LVI for rising<br>5 V V <sub>DDREG</sub> supply at<br>power-on reset | Lvi5p0 -<br>6%   | Lvi5p0  | Lvi5p0 +<br>6%   | V    |       |

| 8b | _        | СС | С | Variation of LVI for rising<br>5 V V <sub>DDRE</sub> G supply<br>power-on reset   | Lvi5p0 -<br>3%   | Lvi5p0  | Lvi5p0 +<br>3%   | V    |       |

| 8c | _        | CC | С | Trimming step LVI 5 V                                                             | _                | 20      | _                | mV   |       |

| 8d | Lvi5p0_h | CC | С | LVI 5 V hysteresis                                                                | _                | 60      | _                | mV   |       |

| 9  | Por5V_r  | СС | С | Nominal POR for rising 5 V<br>V <sub>DDREG</sub> supply                           | _                | 2.67    | -                | V    |       |

| 9a | _        | СС | С | Variation of POR for rising<br>5 V V <sub>DDREG</sub> supply                      | Por5V_r<br>- 35% | Por5V_r | Por5V_r<br>+ 50% | V    |       |

| 9b | Por5V_f  | СС | С | Nominal POR for falling 5 V<br>V <sub>DDREG</sub> supply                          | _                | 2.47    | —                | V    |       |

| 9c | —        | СС | С | Variation of POR for falling $5 \text{ V V}_{\text{DDREG}}$ supply                | Por5V_f<br>- 35% | Por5V_f | Por5V_f<br>+ 50% | V    |       |

| Table 15. PMC Electrical C | haracteristics (continued) |

|----------------------------|----------------------------|

|----------------------------|----------------------------|

<sup>1</sup> Using external ballast transistor.

<sup>2</sup> Min range is extended to 10% since Lvi1p2 is reprogrammed from 1.2 V to 1.16 V after power-on reset.

<sup>3</sup> LVI for falling supply is calculated as LVI rising – LVI hysteresis.

<sup>4</sup> Lvi1p2 tracks DC target variation of internal Vdd regulator. Minimum and maximum Lvi1p2 correspond to minimum and maximum Vdd DC target respectively.

<sup>5</sup> Minimum loading (<10 mA) for reading trim values from flash, powering internal RC oscillator, and IO consumption during POR.

<sup>6</sup> No external load is allowed, except for use as a reference for an external tool.

<sup>7</sup> This value is valid only when the internal regulator is bypassed. When the internal regulator is enabled, the maximum external load allowed on the Nexus pads is 30 pF at 40 MHz.

<sup>8</sup> Lvi3p3 tracks DC target variation of internal Vdd33 regulator. Minimum and maximum Lvi3p3 correspond to minimum and maximum Vdd33 DC target respectively.

## 3.6.1 Voltage regulator controller (V<sub>RC</sub>) electrical specifications

### Table 16. VRC electrical specifications

| Symbol            | Parameter                                                                    |         | Min. | Max. | Units |

|-------------------|------------------------------------------------------------------------------|---------|------|------|-------|

| L                 | Current can be sourced by V <sub>RCCTL</sub> at Tj:                          | 25 °C   | TBD  |      | mA    |

| VRCCTL            |                                                                              | 150 °C  | TBD  |      | mA    |

|                   | Required gain at Tj:<br>$I_{DD} \div I_{VRCCTL} (f_{sys} = f_{MAX})^{1,3,4}$ | – 40 °C | TBD  | _    | _     |

| BETA <sup>2</sup> | $I_{DD} \div I_{VRCCTL} (T_{sys} = T_{MAX})^{+, v_s, v_s}$                   | 25 °C   | TBD  | —    | —     |

|                   |                                                                              | 150 °C  | TBD  | TBD  | —     |

<sup>1</sup>  $I_{VRCCTL}$  is measured at the following conditions:  $V_{DD}$  = 1.35 V,  $V_{RC33}$  = 3.1 V,  $V_{VRCCTL}$  = 2.2 V.

Table 20. Power sequence pin states (medium, slow, and multi-voltage pads)

| V <sub>DDEH</sub> | V <sub>DD</sub> | Pad State      |

|-------------------|-----------------|----------------|

| LOW               | Х               | LOW            |

| V <sub>DDEH</sub> | LOW             | HIGH IMPEDANCE |

| V <sub>DDEH</sub> | V <sub>DD</sub> | FUNCTIONAL     |

# 3.8 DC electrical specifications

| Symbol                             |    | с | Demonster                             | O an diti an a   |                       | Value |                       | 11     |

|------------------------------------|----|---|---------------------------------------|------------------|-----------------------|-------|-----------------------|--------|

| Symbol                             |    | C | Parameter                             | Conditions       | min                   | typ   | max                   | - Unit |

| V <sub>DD</sub>                    | SR | _ | Core supply voltage                   | _                | 1.14                  |       | 1.32                  | V      |

| V <sub>DDE</sub>                   | SR | _ | I/O supply voltage                    | _                | 1.62                  |       | 3.6                   | V      |

| V <sub>DDEH</sub>                  | SR | _ | I/O supply voltage                    | _                | 3.0                   |       | 5.25                  | V      |

| V <sub>DDE-EH</sub>                | SR | — | I/O supply voltage                    | _                | 3.0                   |       | 5.25                  | V      |

| V <sub>RC33</sub>                  | SR | — | 3.3 V regulated voltage <sup>1</sup>  |                  |                       |       |                       | V      |

| V <sub>DDA</sub>                   | SR | — | Analog supply voltage                 | _                | 4.75 <sup>2</sup>     | _     | 5.25                  | V      |

| V <sub>INDC</sub>                  | SR | — | Analog input voltage                  | _                | V <sub>SSA</sub> -0.3 |       | V <sub>DDA</sub> +0.3 | V      |

| $V_{SS} - V_{SSA}$                 | SR | — | V <sub>SS</sub> differential voltage  | _                | -100                  | _     | 100                   | mV     |

| V <sub>RL</sub>                    | SR | — | Analog reference low voltage          | _                | V <sub>SSA</sub>      | _     | V <sub>SSA</sub> +0.1 | V      |

| V <sub>RL</sub> – V <sub>SSA</sub> | SR | _ | VRL differential voltage              | _                | -100                  |       | 100                   | mV     |

| V <sub>RH</sub>                    | SR | — | Analog reference high voltage         | _                | V <sub>DDA</sub> -0.1 | _     | V <sub>DDA</sub>      | V      |

| V <sub>RH</sub> – V <sub>RL</sub>  | SR | _ | V <sub>REF</sub> differential voltage | _                | 4.75                  | _     | 5.25                  | V      |

| V <sub>DDF</sub>                   | SR | _ | Flash operating voltage <sup>3</sup>  | _                | 1.14                  | _     | 1.32                  | V      |

| V <sub>FLASH</sub> <sup>4</sup>    | SR | _ | Flash read voltage                    | _                | 3.0                   |       | 3.6                   | V      |

| V <sub>STBY</sub>                  | SR | — | SRAM standby voltage                  | Unregulated mode | 0.95                  | _     | 1.2                   | V      |

|                                    |    |   | Keep-out Range:<br>1.2V–2V            | Regulated mode   | 2.0                   | —     | 5.5                   |        |

## 3.9 I/O pad current specifications

The power consumption of an I/O segment depends on the usage of the pins on a particular segment. The power consumption is the sum of all output pin currents for a particular segment. The output pin current can be calculated from Table 22 based on the voltage, frequency, and load on the pin. Use linear scaling to calculate pin currents for voltage, frequency, and load parameters that fall outside the values given in Table 22.

| Pad<br>Type                      | Symbol                        |    | с | Period<br>(ns) | Load <sup>2</sup><br>(pF) | V <sub>DDE</sub><br>(V) | Drive/Slew<br>Rate Select | I <sub>DDE</sub> Avg<br>(mA) <sup>3</sup> | I <sub>DDE</sub><br>RMS<br>(mA) |

|----------------------------------|-------------------------------|----|---|----------------|---------------------------|-------------------------|---------------------------|-------------------------------------------|---------------------------------|

| Slow                             | Slow I <sub>DRV_SSR_HV</sub>  |    | D | 37             | 50                        | 5.5                     | 11                        | 9                                         | _                               |

|                                  |                               | СС | D | 130            | 50                        | 5.5                     | 01                        | 2.5                                       | _                               |

|                                  |                               | СС | D | 650            | 50                        | 5.5                     | 00                        | 0.5                                       | _                               |

|                                  |                               | СС | D | 840            | 200                       | 5.5                     | 00                        | 1.5                                       |                                 |

| Medium                           | I <sub>DRV_MSR_HV</sub>       | СС | D | 24             | 50                        | 5.5                     | 11                        | 14                                        |                                 |

|                                  |                               | СС | D | 62             | 50                        | 5.5                     | 01                        | 5.3                                       |                                 |

|                                  |                               | СС | D | 317            | 50                        | 5.5                     | 00                        | 1.1                                       |                                 |

|                                  |                               | СС | D | 425            | 200                       | 5.5                     | 00                        | 3                                         | _                               |

| Fast                             | I <sub>DRV_FC</sub>           | СС | D | 10             | 50                        | 3.6                     | 11                        | 22.7                                      | 68.3                            |

|                                  |                               | СС | D | 10             | 30                        | 3.6                     | 10                        | 12.1                                      | 41.1                            |

|                                  |                               | СС | D | 10             | 20                        | 3.6                     | 01                        | 8.3                                       | 27.7                            |

|                                  |                               | СС | D | 10             | 10                        | 3.6                     | 00                        | 4.44                                      | 14.3                            |

|                                  |                               | СС | D | 10             | 50                        | 1.98                    | 11                        | 12.5                                      | 31                              |

|                                  |                               | СС | D | 10             | 30                        | 1.98                    | 10                        | 7.3                                       | 18.6                            |

|                                  |                               | СС | D | 10             | 20                        | 1.98                    | 01                        | 5.42                                      | 12.6                            |

|                                  |                               | СС | D | 10             | 10                        | 1.98                    | 00                        | 2.84                                      | 6.4                             |

| MultiV                           | I <sub>DRV_MULTV_</sub>       | СС | D | 20             | 50                        | 5.5                     | 11                        | 9                                         | _                               |

| (High<br>Swing                   | HV                            | СС | D | 30             | 50                        | 5.5                     | 01                        | 6.1                                       | _                               |

| Mode)                            |                               | СС | D | 117            | 50                        | 5.5                     | 00                        | 2.3                                       | _                               |

|                                  |                               | CC | D | 212            | 200                       | 5.5                     | 00                        | 5.8                                       | _                               |

| MultiV<br>(Low<br>Swing<br>Mode) | I <sub>DRV_MULTV_</sub><br>HV | CC | D | 30             | 30                        | 5.5                     | 11                        | 3.4                                       |                                 |

Table 22. I/O pad average I<sub>DDE</sub> specifications<sup>1</sup>

<sup>1</sup> Numbers from simulations at best case process, 150 °C.

<sup>2</sup> All loads are lumped.

<sup>3</sup> Average current is for pad configured as output only.

- <sup>8</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>9</sup> Values are with frequency modulation disabled. If frequency modulation is enabled, jitter is the sum of C<sub>JITTER</sub> and either f<sub>CS</sub> or f<sub>DS</sub> (depending on whether center spread or down spread modulation is enabled).

- <sup>10</sup> This value is determined by the crystal manufacturer and board design. For 4 MHz to 40 MHz crystals specified for this PLL, load capacitors should not exceed these limits.

- <sup>11</sup> Proper PC board layout procedures must be followed to achieve specifications.

- <sup>12</sup> This parameter is guaranteed by design rather than 100% tested.

- $^{13}\,V_{\text{IHEXT}}$  cannot exceed  $V_{\text{RC33}}$  in external reference mode.

- <sup>14</sup> This specification applies to the period required for the PLL to relock after changing the MFD frequency control bits in the synthesizer control register (SYNCR).

- <sup>15</sup> Modulation depth will be attenuated from depth setting when operating at modulation frequencies above 50 kHz.

## 3.11 Temperature sensor electrical characteristics

| Symbo | Symbol |   | Parameter                       | Conditions                     |     | Unit    |     |       |  |

|-------|--------|---|---------------------------------|--------------------------------|-----|---------|-----|-------|--|

| Cymbe | ,      | С | i uluneter                      | Conditions                     | min | typical | max |       |  |

| _     | CC     | С | Temperature<br>monitoring range |                                | -40 | _       | 150 | °C    |  |

| _     | CC     | С | Sensitivity                     |                                |     | 6.3     | _   | mV/°C |  |

|       | CC     | Ρ | Accuracy                        | T <sub>J</sub> = –40 to 150 °C | -10 | —       | 10  | °C    |  |

Table 27. Temperature sensor electrical characteristics

## 3.12 eQADC electrical characteristics

### Table 28. eQADC conversion specifications (operating)

| Symbol             |    | с | Parameter                            | Va   | Unit   |              |

|--------------------|----|---|--------------------------------------|------|--------|--------------|

|                    |    | Ŭ | i didifictor                         | min  | max    |              |

| f <sub>ADCLK</sub> | SR | _ | ADC clock (ADCLK) frequency          | 2    | 16     | MHz          |

| CC                 | CC | D | Conversion cycles                    | 2+13 | 128+14 | ADCLK cycles |

| T <sub>SR</sub>    | CC | С | Stop mode recovery time <sup>1</sup> | _    | 10     | μs           |

| f <sub>ADCLK</sub> | SR |   | ADC clock (ADCLK) frequency          | 2    | 16     | mV           |

Stop mode recovery time is the time from the setting of either of the enable bits in the ADC Control Register to the time that the ADC is ready to perform conversions.Delay from power up to full accuracy = 8 ms.

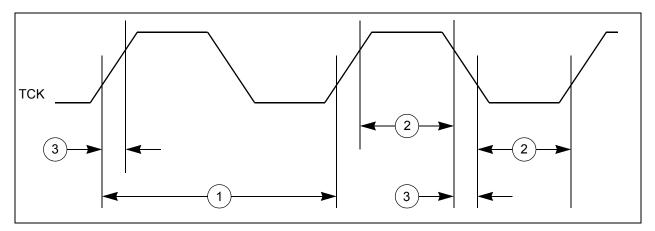

The tool/debugger must provide at least one TCK clock for the EVTI signal to be recognized by the MCU. When using the RDY signal to indicate the end of a Nexus read/write access, ensure that TCK continues to run for at least 1 TCK after leaving the Update-DR state. This can be just a TCK with TMS low while in the Run-Test/Idle state or by continuing with the next Nexus/JTAG command. Expect the affect of EVTI and RDY to be delayed by edges of TCK. Note: RDY is not available in all packages of all devices.

Figure 11. JTAG test clock input timing

| #  | Symbol             |    | С | Characteristic                                                                 | Min. Value | Max. Value | Unit |

|----|--------------------|----|---|--------------------------------------------------------------------------------|------------|------------|------|

| 11 | t <sub>NTDIS</sub> | CC | D | TDI Data Setup Time                                                            | 5          | —          | ns   |

| 12 | t <sub>NTDIH</sub> | CC | D | TDI Data Hold Time                                                             | 25         | —          | ns   |

| 13 | t <sub>NTMSS</sub> | CC | D | TMS Data Setup Time                                                            | 5          | —          | ns   |

| 14 | t <sub>NTMSH</sub> | CC | D | TMS Data Hold Time                                                             | 25         | _          | ns   |

| 15 | _                  | CC | D | TDO propagation delay from falling edge of TCK                                 | —          | 19.5       | ns   |

| 16 | —                  | CC | D | TDO hold time with respect to TCK falling edge (minimum TDO propagation delay) | 5.25       | _          | ns   |

Table 39. Nexus debug port timing<sup>1</sup> (continued)

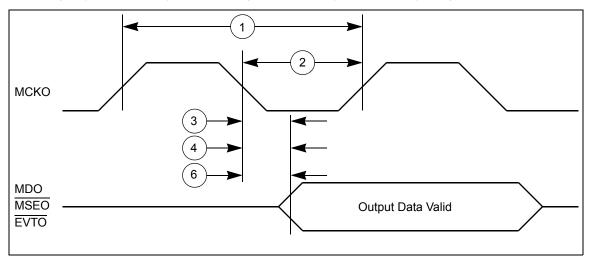

<sup>1</sup> All Nexus timing relative to MCKO is measured from 50% of MCKO and 50% of the respective signal. Nexus timing specified at  $V_{DD}$  = 1.14 V to 1.32 V,  $V_{DDEH}$  = 4.5 V to 5.5 V with multi-voltage pads programmed to Low-Swing mode,  $T_A$  =  $T_L$  to  $T_H$ , and  $C_L$  = 30 pF with DSC = 0b10.

<sup>2</sup> Achieving the absolute minimum MCKO cycle time may require setting the MCKO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV] depending on the actual system frequency being used.

<sup>3</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum MCKO period specification.

<sup>4</sup> This may require setting the MCO divider to more than its minimum setting (NPC\_PCR[MCKO\_DIV]) depending on the actual system frequency being used.

- <sup>5</sup> MDO, MSEO, and EVTO data is held valid until next MCKO low cycle.

- <sup>6</sup> Achieving the absolute minimum TCK cycle time may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

- <sup>7</sup> This is a functionally allowable feature. However, this may be limited by the maximum frequency specified by the Absolute minimum TCK period specification.

- <sup>8</sup> This may require a maximum clock speed (system frequency / 8) that is less than the maximum functional capability of the design (system frequency / 4) depending on the actual system frequency being used.

Figure 15. Nexus output timing

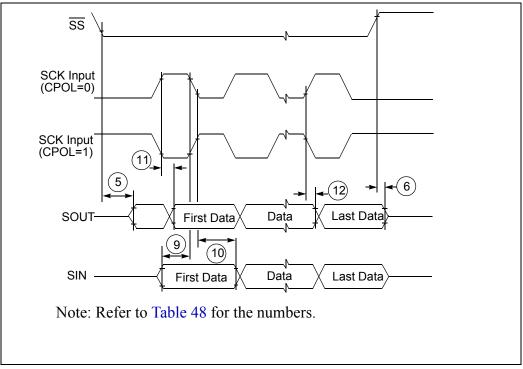

Figure 26. DSPI classic SPI timing — slave, CPHA = 1

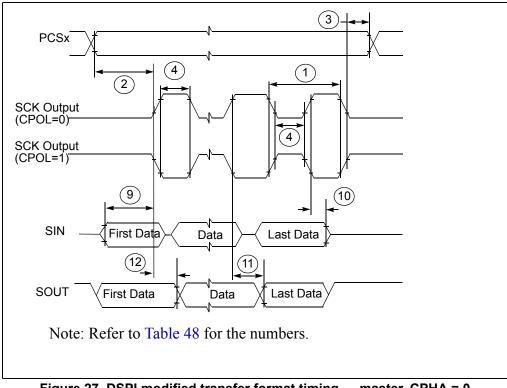

Figure 27. DSPI modified transfer format timing — master, CPHA = 0

MPC5644A Microcontroller Data Sheet, Rev. 7

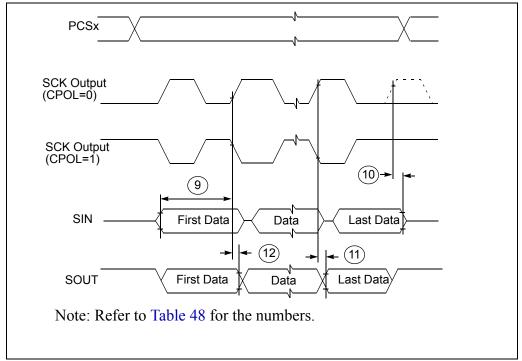

Figure 28. DSPI modified transfer format timing — master, CPHA = 1

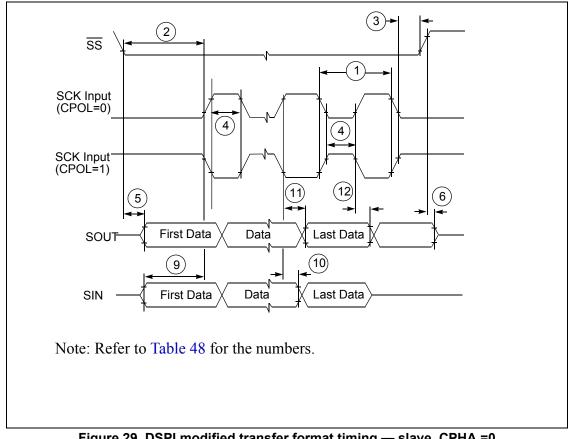

Figure 29. DSPI modified transfer format timing — slave, CPHA =0

MPC5644A Microcontroller Data Sheet, Rev. 7

| 1.                                                       | PROTRI                                           | JSION I                                                     | S 0.25MM                                                  | PER S                                         | T INCLUDE<br>SIDE. DIMEN<br>TERMINED                       | ISIONS                                 | D1 AND E                           | 1 DO IN                   | CLUDE    |             |                           |

|----------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------|----------------------------------------|------------------------------------|---------------------------|----------|-------------|---------------------------|

| 2                                                        | ALLOWA<br>EXCEED<br>DAMBA                        | ABLE DA<br>THE N<br>R CAN<br>EN PRO                         | AMBAR PR<br>AXIMUM I<br>NOT BE L<br>TRUSION A             | OTRUS<br>DIME<br>OCATE                        | DE DAMBA<br>ION SHALL<br>NSION BY<br>D ON THE<br>N ADJACEN | NOT O<br>MORE<br>LOWER                 | CAUSE THE<br>THEN 0.08<br>RADIUS ( | E LEAD '<br>MM.<br>DR THE | WIDTH TO | C<br>NUMINI | ММ                        |

|                                                          |                                                  |                                                             |                                                           |                                               |                                                            |                                        |                                    |                           |          |             |                           |

| ЛМ                                                       | MIN                                              | NOM                                                         | MAX                                                       | DIM                                           | MIN                                                        | NOM                                    | MAX                                | DIM                       | MIN      | NOM         | MAX                       |

| DIM<br>A                                                 | MIN                                              | NOM                                                         | MAX<br>1.6                                                | DIM<br>L1                                     | MIN                                                        | NOM<br>1 REF                           | MAX                                | DIM                       | MIN      | NOM         | МАХ                       |

| A                                                        |                                                  | NOM                                                         |                                                           |                                               | MIN<br>0.08                                                |                                        | MAX                                | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1                                                  |                                                  | NOM<br>1.4                                                  | 1.6                                                       | L1                                            |                                                            |                                        | MAX 0.2                            | DIM                       | MIN      | NOM         | МАХ                       |

| A<br>A1                                                  | 0.05                                             |                                                             | 1.6<br>0.15                                               | L1<br>R1                                      | 0.08<br>0.08                                               |                                        | 0.2                                | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b                                       | <br>0.05<br>1.35                                 | 1.4                                                         | 1.6<br>0.15<br>1.45                                       | L1<br>R1<br>R2                                | 0.08<br>0.08                                               | 1 REF                                  | 0.2                                | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b                                       | <br>0.05<br>1.35<br>0.17                         | 1.4<br>0.22                                                 | 1.6<br>0.15<br>1.45<br>0.27                               | L1<br>R1<br>R2<br>S                           | 0.08<br>0.08                                               | 1 REF<br>0.2 REF                       | 0.2                                | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b<br>b1<br>c                            | <br>0.05<br>1.35<br>0.17<br>0.17                 | 1.4<br>0.22                                                 | 1.6<br>0.15<br>1.45<br>0.27<br>0.23                       | L1<br>R1<br>R2<br>S<br><b>0</b>               | 0.08<br>0.08<br>0*                                         | 1 REF<br>0.2 REF                       | 0.2                                | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b<br>b1<br>c                            | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22                                                 | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.16        | L1<br>R1<br>R2<br>S<br><b>0</b><br><b>0</b> 1 | 0.08<br>0.08<br>0°<br>0°                                   | 1 REF<br>0.2 REF<br>3.5*               | 0.2<br>7°                          | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b<br>b1<br>c<br>c1<br>D                 | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22<br>0.2                                          | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.2<br>0.16 | L1<br>R1<br>R2<br>S<br><b>0</b><br>01<br>02   | 0.08<br>0.08<br>0°<br>0°<br>11°                            | 1 REF<br>0.2 REF<br>3.5*<br>12*        | 0.2<br>7°<br><br>13°               | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b<br>b1<br>c<br>c1<br>D                 | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22<br>0.2<br>26 BSC                                | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.16        | L1<br>R1<br>R2<br>S<br><b>0</b><br>01<br>02   | 0.08<br>0.08<br>0°<br>0°<br>11°                            | 1 REF<br>0.2 REF<br>3.5*<br>12*        | 0.2<br>7°<br><br>13°               | DIM                       | MIN      | NOM         | MAX                       |

| A1<br>A2<br>b<br>b1<br>c<br>c1<br>D<br>D1                | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22<br>0.2<br>26 BSC<br>24 BSC                      | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.16        | L1<br>R1<br>R2<br>S<br><b>0</b><br>01<br>02   | 0.08<br>0.08<br>0°<br>0°<br>11°                            | 1 REF<br>0.2 REF<br>3.5*<br>12*        | 0.2<br>7°<br><br>13°               | DIM                       | MIN      | NOM         | MAX                       |

| A<br>A1<br>A2<br>b<br>b1<br>c<br>c1<br>D<br>D1<br>e      | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22<br>0.2<br>26 BSC<br>24 BSC<br>0.5 BSC           | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.16        | L1<br>R1<br>R2<br>S<br><b>0</b><br>01<br>02   | 0.08<br>0.08<br>0°<br>11°<br>11°                           | 1 REF<br>0.2 REF<br>3.5°<br>12°<br>12° | 0.2<br>7°<br>13°<br>13°            |                           |          |             |                           |

| A<br>A1<br>A2<br>b<br>b1<br>c<br>c1<br>D<br>D1<br>e<br>E | <br>0.05<br>1.35<br>0.17<br>0.17<br>0.09<br>0.09 | 1.4<br>0.22<br>0.2<br>26 BSC<br>24 BSC<br>0.5 BSC<br>26 BSC | 1.6<br>0.15<br>1.45<br>0.27<br>0.23<br>0.2<br>0.16        | L1<br>R1<br>R2<br>S<br><b>0</b><br>01<br>02   | 0.08<br>0.08<br>0°<br>0°<br>11°                            | 1 REF<br>0.2 REF<br>3.5*<br>12*<br>12* | 0.2<br>7°<br><br>13°               | AND                       | REFER    | RANCE [     | MAX<br>DOCUMENT<br>0-1392 |

| Figure 35. 176 LQFP package mechanical dr | rawing (part 3) |

|-------------------------------------------|-----------------|

|-------------------------------------------|-----------------|

Figure 37. 208 MAPBGA package mechanical drawing (part 2)

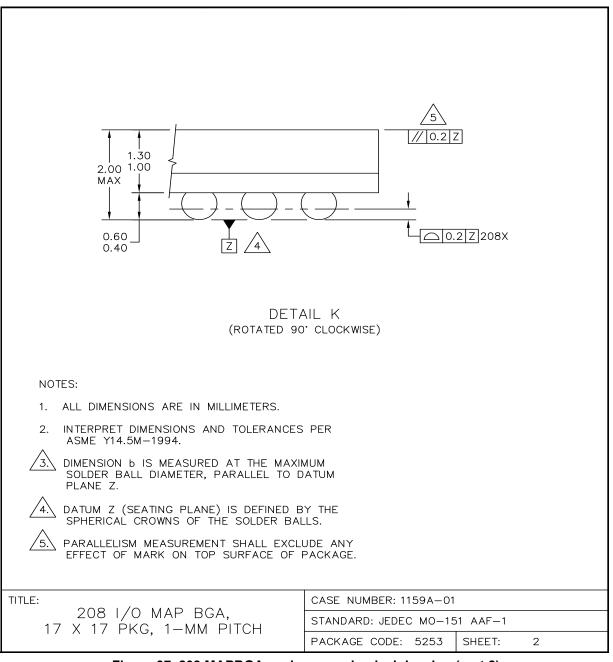

## 4.1.3 324 TEPBGA

Figure 38. 324 BGA package mechanical drawing (part 1)

MPC5644A Microcontroller Data Sheet, Rev. 7

\_\_\_\_\_

| Revision Date | Substantive changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 5 2/2011 | <ul> <li>Number of the second state of the "Deverview" section.</li> <li>Added ECSM to the block diagram.</li> <li>Added ECSM to the block diagram.</li> <li>Added DATA[0:15] to V<sub>DDE5</sub> in the "signal properties" table.</li> <li>Updated DATA[0:15] to V<sub>DDE5</sub> in the "signal properties" table.</li> <li>Updated VSTBY parameters in the "Absolute maximum ratings" table.</li> <li>Updated footnote instances in the "Absolute maximum ratings" table.</li> <li>Updated the parameter symbols and classifications throughout the document.</li> <li>Updated footnote instances in the "Absolute maximum ratings" table.</li> <li>Removed I<sub>MAXA</sub> footnote in the "Absolute maximum ratings" table.</li> <li>Removed the footnote on V<sub>DDE6</sub> in the "Power management control (PMC) and power on reset (POR) electrical specifications" table.</li> <li>Updated the format of the "EMI (electromagnetic interference) characteristics" table.</li> <li>Updated values for Vbg, Idd3p3, Por3.3V_r, Por3.3V_f, Por5V_r, and Por5V_f in the "PMC electrical characteristics" table.</li> <li>Updated "Bandgap reference supply voltage variation" in the "PMC Electrical Characteristics" table.</li> <li>Updated VIH_Ls in the "DC electrical specifications" table.</li> <li>Updated VIH_Ls in the "DC electrical specifications" table.</li> <li>Updated VIH_LS in the "DC electrical specifications" table.</li> <li>Updated Index Pand IDDSTBY160 in the "DC electrical specifications" table.</li> <li>Updated Index Pand IDDSTBY160 in the "DC electrical specifications" table.</li> <li>Updated VIH_LS in the 'DC IDDE1 LVDS pad specifications" table.</li> <li>Updated Values for V<sub>OD</sub> in the "DSPI LVDS pad specifications" table.</li> <li>Updated values for V<sub>OD</sub> in the "DSPI LVDS pad specifications" table.</li> <li>Updated values for OFFNC and GAINNC in the "eQADC conversion specifications (operating)" table.</li> <li>Updated values for OFFNC and GAINNC in the "Cutoff frequency for additional SRAM wait state" table.</li> <li>Updated maximum operating frequency values in the "Cutoff frequ</li></ul> |

| Rev. 6 —      | <ul> <li>specifications (V<sub>DDE</sub> = 3.3 V)" table.</li> <li>Rev. 6 not published.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 53. Revision history (continued)