Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | ARM® Cortex®-M0                                                        |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 48MHz                                                                  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |

| Number of I/O              | 37                                                                     |

| Program Memory Size        | 64KB (64K x 8)                                                         |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | -                                                                      |

| RAM Size                   | 16K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                  |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                          |

| Package / Case             | 48-UFQFN Exposed Pad                                                   |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                        |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f072c8u6  |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

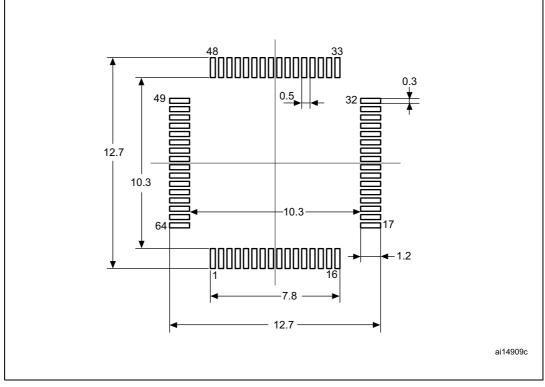

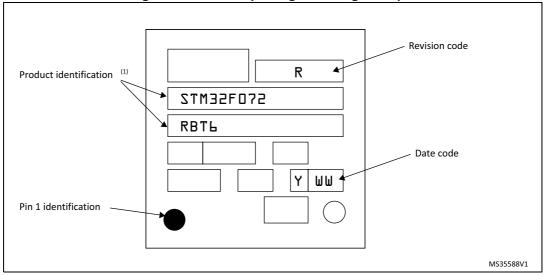

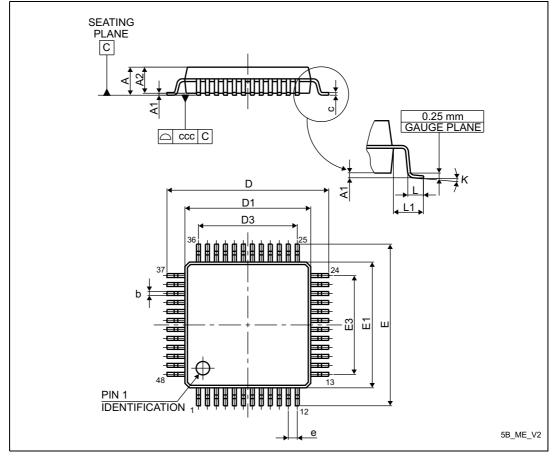

| Figure 49. | LQFP48 package outline                          | 115 |

|------------|-------------------------------------------------|-----|

| Figure 50. | Recommended footprint for LQFP48 package        | 116 |

| Figure 51. | LQFP48 package marking example                  | 117 |

| Figure 52. | UFQFPN48 package outline                        | 118 |

| Figure 53. | Recommended footprint for UFQFPN48 package      | 119 |

| Figure 54. | UFQFPN48 package marking example                | 120 |

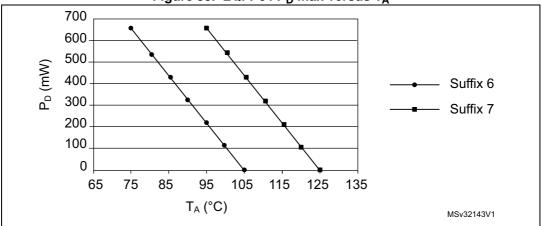

| Figure 55. | LQFP64 P <sub>D</sub> max versus T <sub>A</sub> | 123 |

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 87 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\scriptsize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

|          | Р       | 'in nu  | mber   | s               |         |                                      |             |               |       | Pin functions                                                                                                      |                                                    |  |

|----------|---------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                                                                | Additional<br>functions                            |  |

| M2       | 24      | H2      | 15     | 11              | G7      | PA1                                  | I/O         | TTa           | -     | USART2_RTS,<br>TIM2_CH2,<br>TIM15_CH1N,<br>TSC_G1_IO2,<br>USART4_RX,<br>EVENTOUT                                   | ADC_IN1,<br>COMP1_INP                              |  |

| КЗ       | 25      | F3      | 16     | 12              | E5      | PA2                                  | I/O         | ТТа           | -     | USART2_TX,<br>COMP2_OUT,<br>TIM2_CH3,<br>TIM15_CH1,<br>TSC_G1_IO3                                                  | ADC_IN2,<br>COMP2_INM6,<br>WKUP4                   |  |

| L3       | 26      | G3      | 17     | 13              | E4      | PA3                                  | I/O         | ТТа           | -     | USART2_RX,TIM2_CH4,<br>TIM15_CH2,<br>TSC_G1_IO4                                                                    | ADC_IN3,<br>COMP2_INP                              |  |

| D3       | 27      | C2      | 18     | -               | -       | VSS                                  | S           | -             | -     | Ground                                                                                                             |                                                    |  |

| H3       | 28      | D2      | 19     | -               | -       | VDD                                  | S           | -             | -     | Digital power supply                                                                                               |                                                    |  |

| М3       | 29      | H3      | 20     | 14              | G6      | PA4                                  | I/O         | ТТа           | -     | SPI1_NSS, I2S1_WS,<br>TIM14_CH1,<br>TSC_G2_IO1,<br>USART2_CK                                                       | COMP1_INM4,<br>COMP2_INM4,<br>ADC_IN4,<br>DAC_OUT1 |  |

| K4       | 30      | F4      | 21     | 15              | F5      | PA5                                  | I/O         | ТТа           | -     | SPI1_SCK, I2S1_CK,<br>CEC,<br>TIM2_CH1_ETR,<br>TSC_G2_IO2                                                          | COMP1_INM5,<br>COMP2_INM5,<br>ADC_IN5,<br>DAC_OUT2 |  |

| L4       | 31      | G4      | 22     | 16              | F4      | PA6                                  | I/O         | ТТа           | -     | SPI1_MISO, I2S1_MCK,<br>TIM3_CH1, TIM1_BKIN,<br>TIM16_CH1,<br>COMP1_OUT,<br>TSC_G2_IO3,<br>EVENTOUT,<br>USART3_CTS | ADC_IN6                                            |  |

| M4       | 32      | H4      | 23     | 17              | F3      | PA7                                  | I/O         | ТТа           | -     | SPI1_MOSI, I2S1_SD,<br>TIM3_CH2, TIM14_CH1,<br>TIM1_CH1N,<br>TIM17_CH1,<br>COMP2_OUT,<br>TSC_G2_IO4,<br>EVENTOUT   | ADC_IN7                                            |  |

Table 13. STM32F072x8/xB pin definitions (continued)

| Pin name | AF0                 | AF1       | AF2        | AF3        | AF4        | AF5               |

|----------|---------------------|-----------|------------|------------|------------|-------------------|

| PB0      | EVENTOUT            | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 | USART3_CK  | -                 |

| PB1      | TIM14_CH1           | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 | USART3_RTS | -                 |

| PB2      | -                   | -         | -          | TSC_G3_IO4 | -          | -                 |

| PB3      | SPI1_SCK, I2S1_CK   | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 | -          | -                 |

| PB4      | SPI1_MISO, I2S1_MCK | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 | -          | TIM17_BKIN        |

| PB5      | SPI1_MOSI, I2S1_SD  | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  | -          | -                 |

| PB6      | USART1_TX           | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 | -          | -                 |

| PB7      | USART1_RX           | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 | USART4_CTS | -                 |

| PB8      | CEC                 | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   | CAN_RX     | -                 |

| PB9      | IR_OUT              | I2C1_SDA  | TIM17_CH1  | EVENTOUT   | CAN_TX     | SPI2_NSS, I2S2_W  |

| PB10     | CEC                 | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   | USART3_TX  | SPI2_SCK, I2S2_CF |

| PB11     | EVENTOUT            | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 | USART3_RX  | -                 |

| PB12     | SPI2_NSS, I2S2_WS   | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 | USART3_CK  | TIM15_BKIN        |

| PB13     | SPI2_SCK, I2S2_CK   | -         | TIM1_CH1N  | TSC_G6_IO3 | USART3_CTS | I2C2_SCL          |

| PB14     | SPI2_MISO, I2S2_MCK | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 | USART3_RTS | I2C2_SDA          |

| PB15     | SPI2_MOSI, I2S2_SD  | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N | -          | -                 |

\_ - -- -- -- ----. \_

42/128

5

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_I02          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | -                   |

| PE8      | TIM1_CH1N | -                   |

| PE9      | TIM1_CH1  | -                   |

| PE10     | TIM1_CH2N | -                   |

| PE11     | TIM1_CH2  | -                   |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

Table 18. Alternate functions selected through GPIOE\_AFR registers for port E

#### Table 19. Alternate functions available on port F

| Pin name | AF        |

|----------|-----------|

|          |           |

| PF0      | CRS_SYNC  |

| PF1      | -         |

| PF2      | EVENTOUT  |

| PF3      | EVENTOUT  |

| PF6      | -         |

| PF9      | TIM15_CH1 |

| PF10     | TIM15_CH2 |

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

|                                      | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣI <sub>IO(PIN)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                                      | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

#### Table 22. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

A positive injection is induced by V<sub>IN</sub> > V<sub>DDIOx</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. On these I/Os, a positive injection is induced by  $V_{IN} > V_{DDA}$ . Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 59: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 23. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Т <sub>Ј</sub>   | Maximum junction temperature | 150         | °C   |

# 6.3.2 Operating conditions at power-up / power-down

The parameters given in *Table 25* are derived from tests performed under the ambient temperature condition summarized in *Table 24*.

| Symbol            | Parameter                       | Conditions | Min | Max | Unit  |

|-------------------|---------------------------------|------------|-----|-----|-------|

| t <sub>VDD</sub>  | V <sub>DD</sub> rise time rate  |            | 0   | 8   |       |

|                   | V <sub>DD</sub> fall time rate  |            | 20  | ∞   | μs/V  |

|                   | V <sub>DDA</sub> rise time rate |            | 0   | ∞   | μ5/ ν |

| t <sub>VDDA</sub> | V <sub>DDA</sub> fall time rate | -          | 20  | 8   |       |

Table 25. Operating conditions at power-up / power-down

# 6.3.3 Embedded reset and power control block characteristics

The parameters given in *Table 26* are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                               | Parameter           | Conditions                  | Min                 | Тур  | Max                 | Unit |

|--------------------------------------|---------------------|-----------------------------|---------------------|------|---------------------|------|

| V <sub>POR/PDR</sub> <sup>(1)</sup>  | react threahold     | Falling edge <sup>(2)</sup> | 1.80                | 1.88 | 1.96 <sup>(3)</sup> | V    |

|                                      |                     | Rising edge                 | 1.84 <sup>(3)</sup> | 1.92 | 2.00                | V    |

| V <sub>PDRhyst</sub>                 | PDR hysteresis      | -                           | -                   | 40   | -                   | mV   |

| t <sub>RSTTEMPO</sub> <sup>(4)</sup> | Reset temporization | -                           | 1.50                | 2.50 | 4.50                | ms   |

Table 26. Embedded reset and power control block characteristics

1. The PDR detector monitors  $V_{\text{DD}}$  and also  $V_{\text{DDA}}$  (if kept enabled in the option bytes). The POR detector monitors only  $V_{\text{DD}}.$

2. The product behavior is guaranteed by design down to the minimum  $V_{\text{POR/PDR}}$  value.

3. Data based on characterization results, not tested in production.

4. Guaranteed by design, not tested in production.

| Symbol            | Parameter        | Conditions   | Min  | Тур  | Max  | Unit |

|-------------------|------------------|--------------|------|------|------|------|

| V                 | PVD threshold 0  | Rising edge  | 2.1  | 2.18 | 2.26 | V    |

| V <sub>PVD0</sub> |                  | Falling edge | 2    | 2.08 | 2.16 | V    |

| V                 | PVD threshold 1  | Rising edge  | 2.19 | 2.28 | 2.37 | V    |

| V <sub>PVD1</sub> |                  | Falling edge | 2.09 | 2.18 | 2.27 | V    |

| V                 | PVD threshold 2  | Rising edge  | 2.28 | 2.38 | 2.48 | V    |

| V <sub>PVD2</sub> |                  | Falling edge | 2.18 | 2.28 | 2.38 | V    |

| V                 | PVD threshold 3  | Rising edge  | 2.38 | 2.48 | 2.58 | V    |

| V <sub>PVD3</sub> | PVD Infestiona 3 | Falling edge | 2.28 | 2.38 | 2.48 | V    |

| Symbol           |                                                                     |                                                                      | V <sub>DDA</sub> = 2.4 V |        |                    |                     | V <sub>DDA</sub> = 3.6 V |      |                    |        |                    |      |     |  |

|------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------|--------|--------------------|---------------------|--------------------------|------|--------------------|--------|--------------------|------|-----|--|

|                  | Para-<br>meter                                                      | Conditions<br>(1)                                                    | f <sub>HCLK</sub>        | Tun    | М                  | ax @ T <sub>A</sub> | (2)                      | Tun  | м                  | ax @ T | A <sup>(2)</sup>   | Unit |     |  |

|                  |                                                                     |                                                                      |                          | Тур    | 25 °C              | 85 °C               | 105 °C                   | Тур  | 25 °C              | 85 °C  | 105 °C             |      |     |  |

|                  |                                                                     | HSI48                                                                | 48 MHz                   | 311    | 326                | 334                 | 343                      | 322  | 337                | 345    | 354                |      |     |  |

|                  |                                                                     | HSE                                                                  | 48 MHz                   | 152    | 170 <sup>(3)</sup> | 178                 | 182 <sup>(3)</sup>       | 165  | 184 <sup>(3)</sup> | 196    | 200 <sup>(3)</sup> |      |     |  |

|                  | current in<br>Run or<br>Sleep<br>mode,<br>code<br>executing<br>from | A Code executing from Figure 1 (1) (1) (1) (1) (1) (1) (1) (1) (1) ( | bypass,                  | 32 MHz | 105                | 121                 | 126                      | 128  | 113                | 129    | 136                | 138  |     |  |

|                  |                                                                     |                                                                      | Run or<br>Sleep<br>mode  | n or   | 24 MHz             | 81.9                | 95.9                     | 99.5 | 101                | 88.7   | 102                | 107  | 108 |  |

|                  |                                                                     |                                                                      |                          |        | 8 MHz              | 2.7                 | 3.8                      | 4.3  | 4.6                | 3.6    | 4.7                | 5.2  | 5.5 |  |

| I <sub>DDA</sub> |                                                                     |                                                                      | bypass,<br>PLL off       | 1 MHz  | 2.7                | 3.8                 | 4.3                      | 4.6  | 3.6                | 4.7    | 5.2                | 5.5  | μA  |  |

|                  |                                                                     |                                                                      | from                     | 48 MHz | 223                | 244                 | 255                      | 260  | 245                | 265    | 279                | 284  |     |  |

|                  | Flash<br>memory                                                     | HSI clock,<br>PLL on                                                 | 32 MHz                   | 176    | 195                | 203                 | 206                      | 193  | 212                | 221    | 224                |      |     |  |

|                  | or RAM                                                              | -                                                                    |                          |        | 24 MHz             | 154                 | 171                      | 178  | 181                | 168    | 185                | 192  | 195 |  |

|                  |                                                                     |                                                                      | HSI clock,<br>PLL off    | 8 MHz  | 74.2               | 83.4                | 86.4                     | 87.3 | 83.4               | 92.5   | 95.3               | 96.6 |     |  |

Table 30. Typical and maximum current consumption from the  $\rm V_{\rm DDA}$  supply

Current consumption from the V<sub>DDA</sub> supply is independent of whether the digital peripherals are enabled or disabled, being in Run or Sleep mode or executing from Flash memory or RAM. Furthermore, when the PLL is off, I<sub>DDA</sub> is independent from the frequency.

2. Data based on characterization results, not tested in production unless otherwise specified.

3. Data based on characterization results and tested in production (using one common test limit for sum of I<sub>DD</sub> and I<sub>DDA</sub>).

| Symbol           | Parameter                       | 6                 |                        | sumption in<br>node     |                        | sumption in mode        | Unit |

|------------------|---------------------------------|-------------------|------------------------|-------------------------|------------------------|-------------------------|------|

| Symbol           | Falailletei                     | <sup>f</sup> нсLк | Peripherals<br>enabled | Peripherals<br>disabled | Peripherals<br>enabled | Peripherals<br>disabled | Onit |

|                  |                                 | 48 MHz            | 24.1                   | 13.5                    | 14.6                   | 3.5                     |      |

|                  |                                 | 36 MHz            | 18.3                   | 10.5                    | 11.1                   | 2.9                     |      |

|                  |                                 | 32 MHz            | 16.5                   | 9.6                     | 10.0                   | 2.7                     |      |

|                  | Current                         | 24 MHz            | 12.9                   | 7.6                     | 7.8                    | 2.2                     |      |

|                  | consumption                     | 16 MHz            | 8.9                    | 5.3                     | 5.5                    | 1.7                     | mA   |

| I <sub>DD</sub>  | from V <sub>DD</sub><br>supply  | 8 MHz             | 4.8                    | 3.1                     | 3.1                    | 1.2                     | ША   |

|                  | suppiy                          | 4 MHz             | 3.1                    | 2.1                     | 2.2                    | 1.1                     |      |

|                  |                                 | 2 MHz             | 2.1                    | 1.6                     | 1.6                    | 1.0                     |      |

|                  |                                 | 1 MHz             | 1.6                    | 1.3                     | 1.4                    | 1.0                     |      |

|                  |                                 | 500 kHz           | 1.3                    | 1.2                     | 1.2                    | 1.0                     |      |

|                  |                                 | 48 MHz            |                        | 16                      | 3.3                    |                         |      |

|                  |                                 | 36 MHz            |                        | 12                      | 4.3                    |                         |      |

|                  |                                 | 32 MHz            |                        | 11                      | 1.9                    |                         |      |

|                  | Current                         | 24 MHz            |                        | 87                      | 7.1                    |                         |      |

| I                | consumption                     | 16 MHz            |                        | 62                      | 2.5                    |                         | uА   |

| I <sub>DDA</sub> | from V <sub>DDA</sub><br>supply | 8 MHz             |                        | 2                       | .5                     |                         | μA   |

|                  | Suppry                          | 4 MHz             |                        | 2                       | .5                     |                         |      |

|                  | 2 N                             | 2 MHz             |                        | 2                       | .5                     |                         |      |

|                  |                                 | 1 MHz             |                        | 2                       | .5                     |                         |      |

|                  |                                 | 500 kHz           |                        | 2                       | .5                     |                         |      |

#### Table 33. Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal

### I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 53: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

### **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 35*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 21: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 35.* The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

| Peripheral |                          | Typical consumption at 25 °C | Unit   |

|------------|--------------------------|------------------------------|--------|

|            | BusMatrix <sup>(1)</sup> | 2.2                          |        |

|            | CRC                      | 1.6                          |        |

|            | DMA                      | 5.7                          |        |

|            | Flash memory interface   | 13.0                         |        |

|            | GPIOA                    | 8.2                          |        |

|            | GPIOB                    | 8.5                          |        |

| AHB        | GPIOC                    | 2.3                          | µA/MHz |

|            | GPIOD                    | 1.9                          |        |

|            | GPIOE                    | 2.2                          |        |

|            | GPIOF                    | 1.2                          |        |

|            | SRAM                     | 0.9                          |        |

|            | TSC                      | 5.0                          |        |

|            | All AHB peripherals      | 52.6                         |        |

#### Table 35. Peripheral current consumption

1. Guaranteed by design, not tested in production.

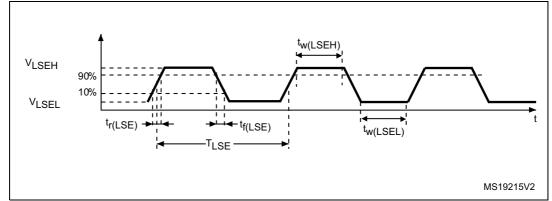

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                       | Parameter <sup>(1)</sup>              | Min                    | Тур    | Max                    | Unit |

|----------------------------------------------|---------------------------------------|------------------------|--------|------------------------|------|

| f <sub>LSE_ext</sub>                         | User external clock source frequency  | -                      | 32.768 | 1000                   | kHz  |

| V <sub>LSEH</sub>                            | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | -      | V <sub>DDIOx</sub>     | V    |

| $V_{LSEL}$                                   | OSC32_IN input pin low level voltage  | V <sub>SS</sub>        | -      | 0.3 V <sub>DDIOx</sub> | v    |

| t <sub>w(LSEH)</sub><br>t <sub>w(LSEL)</sub> | OSC32_IN high or low time             | 450                    | -      | -                      | ns   |

| t <sub>r(LSE)</sub><br>t <sub>f(LSE)</sub>   | OSC32_IN rise or fall time            | -                      | -      | 50                     | 115  |

Table 38. Low-speed external user clock characteristics

1. Guaranteed by design, not tested in production.

| Symbol           | Description                                                                                          | Func<br>suscer     | Unit               |      |

|------------------|------------------------------------------------------------------------------------------------------|--------------------|--------------------|------|

| Symbol           | Description                                                                                          | Negative injection | Positive injection | Unit |

|                  | Injected current on BOOT0 and PF1 pins                                                               | -0                 | NA                 |      |

|                  | Injected current on PC0 pin                                                                          | -0                 | +5                 |      |

| I <sub>INJ</sub> | Injected current on PA11 and PA12 pins with induced leakage current on adjacent pins less than -1 mA | -5                 | NA                 | mA   |

|                  | Injected current on all other FT and FTf pins                                                        | -5                 | NA                 |      |

|                  | Injected current on all other TTa, TC and RST pins                                                   | -5                 | +5                 |      |

### Table 52. I/O current injection susceptibility

# 6.3.14 I/O port characteristics

### General input/output characteristics

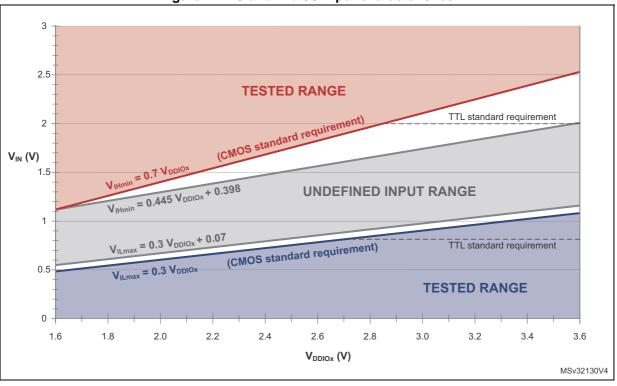

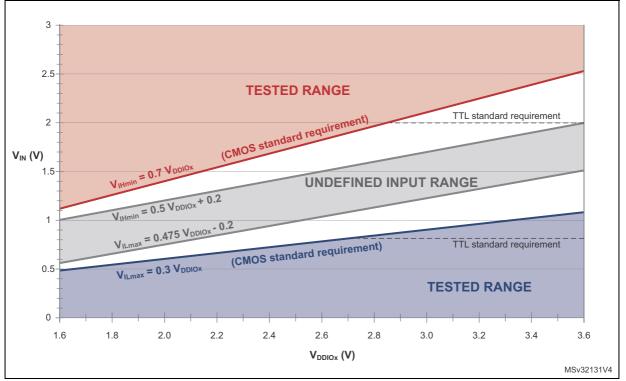

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                                         | Мах                                          | Unit                   |  |

|------------------|-------------------------------|------------------------------|------------------------------------------------|---------------------------------------------|----------------------------------------------|------------------------|--|

|                  | TC and TTa I/O -              |                              | -                                              | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup> |                                              |                        |  |

|                  | Low level input               | FT and FTf I/O               | -                                              | -                                           | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |                        |  |

| V <sub>IL</sub>  | voltage                       | BOOT0                        | -                                              | -                                           | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V                      |  |

|                  |                               | All I/Os except<br>BOOT0 pin |                                                | -                                           | -                                            | 0.3 V <sub>DDIOx</sub> |  |

|                  |                               | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                                           | -                                            |                        |  |

|                  |                               | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                                           | -                                            |                        |  |

| V <sub>IH</sub>  | High level input<br>voltage   | BOOT0                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                                           | -                                            | V                      |  |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                                           | -                                            |                        |  |

|                  |                               | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup>                          | -                                            |                        |  |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup>                          | -                                            | mV                     |  |

|                  |                               | BOOT0                        | -                                              | 300 <sup>(1)</sup>                          | -                                            |                        |  |

#### Table 53. I/O static characteristics

Figure 22. TC and TTa I/O input characteristics

Figure 23. Five volt tolerant (FT and FTf) I/O input characteristics

DocID025004 Rev 5

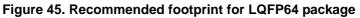

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol |       | millimeters |       |        | inches <sup>(1)</sup> |        |  |  |  |

|--------|-------|-------------|-------|--------|-----------------------|--------|--|--|--|

|        | Min   | Тур         | Max   | Min    | Тур                   | Max    |  |  |  |

| E3     | -     | 7.500       | -     | -      | 0.2953                | -      |  |  |  |

| е      | -     | 0.500       | -     | -      | 0.0197                | -      |  |  |  |

| К      | 0°    | 3.5°        | 7°    | 0°     | 3.5°                  | 7°     |  |  |  |

| L      | 0.450 | 0.600       | 0.750 | 0.0177 | 0.0236                | 0.0295 |  |  |  |

| L1     | -     | 1.000       | -     | -      | 0.0394                | -      |  |  |  |

| CCC    | -     | -           | 0.080 | -      | -                     | 0.0031 |  |  |  |

Table 76. LQFP64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

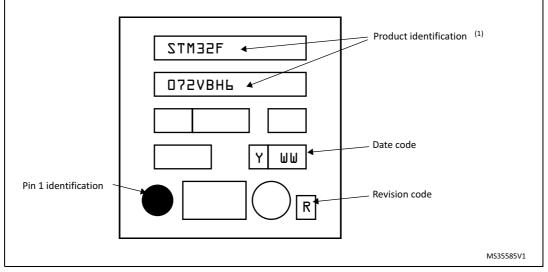

#### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

# 7.6 LQFP48 package information

LQFP48 is a 48-pin, 7 x 7 mm low-profile quad flat package.

1. Drawing is not to scale.

# 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 24: General operating conditions*.

The maximum chip-junction temperature,  $T_{\rm J}$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J max = T_A max + (P_D max x \Theta_{JA})$$

Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- P<sub>D</sub> max is the sum of P<sub>INT</sub> max and P<sub>I/O</sub> max (P<sub>D</sub> max = P<sub>INT</sub> max + P<sub>I/O</sub>max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

$\mathsf{P}_{I\!/\!O}$  max represents the maximum power dissipation on output pins where:

$\mathsf{P}_{\mathsf{I/O}} \max = \Sigma \; (\mathsf{V}_{\mathsf{OL}} \times \mathsf{I}_{\mathsf{OL}}) + \Sigma \; ((\mathsf{V}_{\mathsf{DDIOx}} - \mathsf{V}_{\mathsf{OH}}) \times \mathsf{I}_{\mathsf{OH}}),$

taking into account the actual V\_{OL} / I\_{OL} and V\_{OH} / I\_{OH} of the I/Os at low and high level in the application.

| Symbol        | Parameter                                                                 | Value | Unit |

|---------------|---------------------------------------------------------------------------|-------|------|

|               | <b>Thermal resistance junction-ambient</b><br>UFBGA100 - 7 × 7 mm         | 55    |      |

|               | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm               | 42    |      |

|               | Thermal resistance junction-ambient<br>UFBGA64 - 5 × 5 mm / 0.5 mm pitch  | 65    |      |

| $\Theta_{JA}$ | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 44    | °C/W |

|               | Thermal resistance junction-ambient<br>LQFP48 - 7 × 7 mm                  | 54    |      |

|               | Thermal resistance junction-ambient<br>UFQFPN48 - 7 × 7 mm                | 32    |      |

|               | Thermal resistance junction-ambient<br>WLCSP49 - 0.4 mm pitch             | 49    |      |

# 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

# 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

DocID025004 Rev 5

Using the values obtained in *Table 80*  $T_{Jmax}$  is calculated as follows:

- For LQFP64, 45 °C/W

- $T_{Jmax} = 100 \text{ °C} + (45 \text{ °C/W} \times 134 \text{ mW}) = 100 \text{ °C} + 6.03 \text{ °C} = 106.03 \text{ °C}$

This is above the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).

In this case, parts must be ordered at least with the temperature range suffix 7 (see *Section 8: Ordering information*) unless we reduce the power dissipation in order to be able to use suffix 6 parts.

Refer to *Figure 55* to select the required temperature range (suffix 6 or 7) according to your temperature or power requirements.

Figure 55. LQFP64 P<sub>D</sub> max versus T<sub>A</sub>

# 8 Ordering information

For a list of available options (memory, package, and so on) or for further information on any aspect of this device, please contact your nearest ST sales office.

| Table 81 | . Ordering | information | scheme |

|----------|------------|-------------|--------|

|----------|------------|-------------|--------|

| Example:                                 | STM32 | F | 072 | R | 8 | Т | 6 > |

|------------------------------------------|-------|---|-----|---|---|---|-----|

| Device family                            |       |   |     |   |   |   |     |

| STM32 = ARM-based 32-bit microcontroller |       |   |     |   |   |   |     |

|                                          |       |   |     |   |   |   |     |

| Product type                             |       |   |     |   |   |   |     |

| F = General-purpose                      |       |   |     |   |   |   |     |

| Sub-family                               |       |   |     |   |   |   |     |

| 072 = STM32F072xx                        |       |   |     |   |   |   |     |

|                                          |       |   |     |   |   |   |     |

| Pin count                                |       |   |     |   |   |   |     |

| C = 48/49 pins                           |       |   |     |   |   |   |     |

| R = 64 pins                              |       |   |     |   |   |   |     |

| V = 100 pins                             |       |   |     |   |   |   |     |

| lleer oode memory size                   |       |   |     |   |   |   |     |

| User code memory size                    |       |   |     |   |   |   |     |

| 8 = 64 Kbyte                             |       |   |     |   |   |   |     |

| B = 128 Kbyte                            |       |   |     |   |   |   |     |

| Package                                  |       |   |     |   |   |   |     |

| H = UFBGA                                |       |   |     |   |   |   |     |

| T = LQFP                                 |       |   |     |   |   |   |     |

| U = UFQFPN                               |       |   |     |   |   |   |     |

| Y = WLCSP                                |       |   |     |   |   |   |     |

|                                          |       |   |     |   |   |   |     |

| Temperature range                        |       |   |     |   |   |   |     |

| 6 = –40 to 85 °C                         |       |   |     |   |   |   |     |

| 7 = –40 to 105 °C                        |       |   |     |   |   |   |     |

|                                          |       |   |     |   |   |   |     |

| Options                                  |       |   |     |   |   |   |     |

xxx = code ID of programmed parts (includes packing type)TR = tape and reel packingblank = tray packing