Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB  |

| Peripherals                | DMA, I²S, POR, PWM, WDT                                                 |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 48-LQFP                                                                 |

| Supplier Device Package    | 48-LQFP (7x7)                                                           |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f072cbt6tr |

# **Contents**

| 1 | Intro | duction   |                                                   | 9  |

|---|-------|-----------|---------------------------------------------------|----|

| 2 | Desc  | cription  |                                                   | 10 |

| 3 | Fund  | ctional o | verview                                           | 13 |

|   | 3.1   | ARM®-     | Cortex®-M0 core                                   | 13 |

|   | 3.2   | Memor     | ies                                               | 13 |

|   | 3.3   | Boot m    | odes                                              | 13 |

|   | 3.4   | Cyclic r  | redundancy check calculation unit (CRC)           | 14 |

|   | 3.5   | Power     | management                                        | 14 |

|   |       | 3.5.1     | Power supply schemes                              | 14 |

|   |       | 3.5.2     | Power supply supervisors                          | 14 |

|   |       | 3.5.3     | Voltage regulator                                 | 15 |

|   |       | 3.5.4     | Low-power modes                                   | 15 |

|   | 3.6   | Clocks    | and startup                                       | 15 |

|   | 3.7   | Genera    | al-purpose inputs/outputs (GPIOs)                 | 17 |

|   | 3.8   | Direct r  | 17                                                |    |

|   | 3.9   | Interrup  | ots and events                                    | 17 |

|   |       | 3.9.1     | Nested vectored interrupt controller (NVIC)       | 17 |

|   |       | 3.9.2     | Extended interrupt/event controller (EXTI)        | 18 |

|   | 3.10  | Analog    | -to-digital converter (ADC)                       | 18 |

|   |       | 3.10.1    | Temperature sensor                                | 18 |

|   |       | 3.10.2    | Internal voltage reference (V <sub>REFINT</sub> ) | 18 |

|   |       | 3.10.3    | V <sub>BAT</sub> battery voltage monitoring       | 19 |

|   | 3.11  | Digital-  | to-analog converter (DAC)                         | 19 |

|   | 3.12  | Compa     | rators (COMP)                                     | 19 |

|   | 3.13  | Touch s   | sensing controller (TSC)                          | 20 |

|   | 3.14  | Timers    | and watchdogs                                     | 21 |

|   |       | 3.14.1    | Advanced-control timer (TIM1)                     | 22 |

|   |       | 3.14.2    | General-purpose timers (TIM2, 3, 14, 15, 16, 17)  | 22 |

|   |       | 3.14.3    | Basic timers TIM6 and TIM7                        | 23 |

|   |       | 3.14.4    | Independent watchdog (IWDG)                       | 23 |

|   |       | 3.14.5    | System window watchdog (WWDG)                     | 23 |

|   |      | 6.3.10    | Memory characteristics                      |

|---|------|-----------|---------------------------------------------|

|   |      | 6.3.11    | EMC characteristics                         |

|   |      | 6.3.12    | Electrical sensitivity characteristics      |

|   |      | 6.3.13    | I/O current injection characteristics       |

|   |      | 6.3.14    | I/O port characteristics                    |

|   |      | 6.3.15    | NRST pin characteristics                    |

|   |      | 6.3.16    | 12-bit ADC characteristics                  |

|   |      | 6.3.17    | DAC electrical specifications               |

|   |      | 6.3.18    | Comparator characteristics                  |

|   |      | 6.3.19    | Temperature sensor characteristics          |

|   |      | 6.3.20    | V <sub>BAT</sub> monitoring characteristics |

|   |      | 6.3.21    | Timer characteristics                       |

|   |      | 6.3.22    | Communication interfaces                    |

| 7 | Pack | kage info | ormation                                    |

|   | 7.1  | UFBGA     | A100 package information                    |

|   | 7.2  | LQFP1     | 00 package information                      |

|   | 7.3  | UFBGA     | A64 package information                     |

|   | 7.4  | LQFP6     | 4 package information                       |

|   | 7.5  | WLCSF     | P49 package information                     |

|   | 7.6  | LQFP4     | 8 package information                       |

|   | 7.7  | UFQFF     | PN48 package information                    |

|   | 7.8  | Therma    | al characteristics                          |

|   |      | 7.8.1     | Reference document                          |

|   |      | 7.8.2     | Selecting the product temperature range     |

| 8 | Orde | ering inf | ormation                                    |

| 9 | Revi | sion his  | tory                                        |

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

### 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

## 3.8 Direct memory access controller (DMA)

The 7-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

### 3.9 Interrupts and events

### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of Cortex -M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

Table 6. Number of capacitive sensing channels available on STM32F072x8/xB devices

| Analog I/O grassin                    | Number of capacitive sensing channels |             |             |  |  |  |  |

|---------------------------------------|---------------------------------------|-------------|-------------|--|--|--|--|

| Analog I/O group                      | STM32F072Vx                           | STM32F072Rx | STM32F072Cx |  |  |  |  |

| G1                                    | 3                                     | 3           | 3           |  |  |  |  |

| G2                                    | 3                                     | 3           | 3           |  |  |  |  |

| G3                                    | 3                                     | 3           | 2           |  |  |  |  |

| G4                                    | 3                                     | 3           | 3           |  |  |  |  |

| G5                                    | 3                                     | 3           | 3           |  |  |  |  |

| G6                                    | 3                                     | 3           | 3           |  |  |  |  |

| G7                                    | 3                                     | 0           | 0           |  |  |  |  |

| G8                                    | 3                                     | 0           | 0           |  |  |  |  |

| Number of capacitive sensing channels | 24                                    | 18          | 17          |  |  |  |  |

# 3.14 Timers and watchdogs

The STM32F072x8/xB devices include up to six general-purpose timers, two basic timers and an advanced control timer.

Table 7 compares the features of the different timers.

Table 7. Timer feature comparison

| Timer<br>type    | Timer          | Counter resolution | Counter<br>type      | Prescaler<br>factor        | DMA<br>request<br>generation | Capture/compare channels | Complementary outputs |

|------------------|----------------|--------------------|----------------------|----------------------------|------------------------------|--------------------------|-----------------------|

| Advanced control | TIM1           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | 3                     |

|                  | TIM2           | 32-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | -                     |

|                  | TIM3           | 16-bit             | Up, down,<br>up/down | integer from<br>1 to 65536 | Yes                          | 4                        | -                     |

| General purpose  | TIM14          | 16-bit             | Up                   | integer from<br>1 to 65536 | No                           | 1                        | -                     |

|                  | TIM15          | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 2                        | 1                     |

|                  | TIM16<br>TIM17 | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | 1                        | 1                     |

| Basic            | TIM6<br>TIM7   | 16-bit             | Up                   | integer from<br>1 to 65536 | Yes                          | -                        | -                     |

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

### 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

Table 13. STM32F072x8/xB pin definitions (continued)

|          | Р       | in nu   | mber   | s               |         |                                      |             |               |            | Pin function                                                                 | ns                      |

|----------|---------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|------------|------------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes      | Alternate functions                                                          | Additional<br>functions |

| D11      | 67      | D7      | 41     | 29              | D1      | PA8                                  | I/O         | FT            | (3)        | USART1_CK,<br>TIM1_CH1,<br>EVENTOUT, MCO,<br>CRS_SYNC                        | -                       |

| D10      | 68      | C7      | 42     | 30              | D2      | PA9                                  | I/O         | FT            | (3)        | USART1_TX,<br>TIM1_CH2,<br>TIM15_BKIN,<br>TSC_G4_IO1                         | -                       |

| C12      | 69      | C6      | 43     | 31              | C2      | PA10                                 | I/O         | FT            | (3)        | USART1_RX,<br>TIM1_CH3,<br>TIM17_BKIN,<br>TSC_G4_IO2                         | -                       |

| B12      | 70      | C8      | 44     | 32              | C1      | PA11                                 | I/O         | FT            | (3)        | CAN_RX, USART1_CTS, TIM1_CH4, COMP1_OUT, TSC_G4_IO3, EVENTOUT                | USB_DM                  |

| A12      | 71      | B8      | 45     | 33              | C3      | PA12                                 | I/O         | FT            | (3)        | CAN_TX, USART1_RTS,<br>TIM1_ETR,<br>COMP2_OUT,<br>TSC_G4_IO4,<br>EVENTOUT    | USB_DP                  |

| A11      | 72      | A8      | 46     | 34              | В3      | PA13                                 | I/O         | FT            | (3)<br>(4) | IR_OUT, SWDIO,<br>USB_NOE                                                    | -                       |

| C11      | 73      | -       | -      | -               | -       | PF6                                  | I/O         | FT            | (3)        | -                                                                            | -                       |

| F11      | 74      | D6      | 47     | 35              | B1      | VSS                                  | S           | -             | -          | Ground                                                                       |                         |

| G11      | 75      | E6      | 48     | 36              | B2      | VDDIO2                               | S           | ı             | -          | Digital power s                                                              | upply                   |

| A10      | 76      | A7      | 49     | 37              | A1      | PA14                                 | I/O         | FT            | (3)<br>(4) | USART2_TX, SWCLK                                                             | -                       |

| A9       | 77      | A6      | 50     | 38              | A2      | PA15                                 | I/O         | FT            | (3)        | SPI1_NSS, I2S1_WS,<br>USART2_RX,<br>USART4_RTS,<br>TIM2_CH1_ETR,<br>EVENTOUT | -                       |

| B11      | 78      | B7      | 51     | -               | -       | PC10                                 | I/O         | FT            | (3)        | USART3_TX,<br>USART4_TX                                                      | -                       |

38/128 DocID025004 Rev 5

| Table 15. Alternate functions selected through GPIOB_AFR registers for port B |                     |           |            |            |            |                   |  |  |  |  |  |

|-------------------------------------------------------------------------------|---------------------|-----------|------------|------------|------------|-------------------|--|--|--|--|--|

| Pin name                                                                      | AF0                 | AF1       | AF2        | AF3        | AF4        | AF5               |  |  |  |  |  |

| PB0                                                                           | EVENTOUT            | TIM3_CH3  | TIM1_CH2N  | TSC_G3_IO2 | USART3_CK  | -                 |  |  |  |  |  |

| PB1                                                                           | TIM14_CH1           | TIM3_CH4  | TIM1_CH3N  | TSC_G3_IO3 | USART3_RTS | -                 |  |  |  |  |  |

| PB2                                                                           | -                   | -         | -          | TSC_G3_IO4 | -          | -                 |  |  |  |  |  |

| PB3                                                                           | SPI1_SCK, I2S1_CK   | EVENTOUT  | TIM2_CH2   | TSC_G5_IO1 | -          | -                 |  |  |  |  |  |

| PB4                                                                           | SPI1_MISO, I2S1_MCK | TIM3_CH1  | EVENTOUT   | TSC_G5_IO2 | -          | TIM17_BKIN        |  |  |  |  |  |

| PB5                                                                           | SPI1_MOSI, I2S1_SD  | TIM3_CH2  | TIM16_BKIN | I2C1_SMBA  | -          | -                 |  |  |  |  |  |

| PB6                                                                           | USART1_TX           | I2C1_SCL  | TIM16_CH1N | TSC_G5_IO3 | -          | -                 |  |  |  |  |  |

| PB7                                                                           | USART1_RX           | I2C1_SDA  | TIM17_CH1N | TSC_G5_IO4 | USART4_CTS | -                 |  |  |  |  |  |

| PB8                                                                           | CEC                 | I2C1_SCL  | TIM16_CH1  | TSC_SYNC   | CAN_RX     | -                 |  |  |  |  |  |

| PB9                                                                           | IR_OUT              | I2C1_SDA  | TIM17_CH1  | EVENTOUT   | CAN_TX     | SPI2_NSS, I2S2_WS |  |  |  |  |  |

| PB10                                                                          | CEC                 | I2C2_SCL  | TIM2_CH3   | TSC_SYNC   | USART3_TX  | SPI2_SCK, I2S2_CK |  |  |  |  |  |

| PB11                                                                          | EVENTOUT            | I2C2_SDA  | TIM2_CH4   | TSC_G6_IO1 | USART3_RX  | -                 |  |  |  |  |  |

| PB12                                                                          | SPI2_NSS, I2S2_WS   | EVENTOUT  | TIM1_BKIN  | TSC_G6_IO2 | USART3_CK  | TIM15_BKIN        |  |  |  |  |  |

| PB13                                                                          | SPI2_SCK, I2S2_CK   | -         | TIM1_CH1N  | TSC_G6_IO3 | USART3_CTS | I2C2_SCL          |  |  |  |  |  |

| PB14                                                                          | SPI2_MISO, I2S2_MCK | TIM15_CH1 | TIM1_CH2N  | TSC_G6_IO4 | USART3_RTS | I2C2_SDA          |  |  |  |  |  |

| PB15                                                                          | SPI2_MOSI, I2S2_SD  | TIM15_CH2 | TIM1_CH3N  | TIM15_CH1N | -          | -                 |  |  |  |  |  |

Table 18. Alternate functions selected through GPIOE\_AFR registers for port E

| Pin name | AF0       | AF1                 |

|----------|-----------|---------------------|

| PE0      | TIM16_CH1 | EVENTOUT            |

| PE1      | TIM17_CH1 | EVENTOUT            |

| PE2      | TIM3_ETR  | TSC_G7_IO1          |

| PE3      | TIM3_CH1  | TSC_G7_IO2          |

| PE4      | TIM3_CH2  | TSC_G7_IO3          |

| PE5      | TIM3_CH3  | TSC_G7_IO4          |

| PE6      | TIM3_CH4  | -                   |

| PE7      | TIM1_ETR  | -                   |

| PE8      | TIM1_CH1N | -                   |

| PE9      | TIM1_CH1  | -                   |

| PE10     | TIM1_CH2N | -                   |

| PE11     | TIM1_CH2  | -                   |

| PE12     | TIM1_CH3N | SPI1_NSS, I2S1_WS   |

| PE13     | TIM1_CH3  | SPI1_SCK, I2S1_CK   |

| PE14     | TIM1_CH4  | SPI1_MISO, I2S1_MCK |

| PE15     | TIM1_BKIN | SPI1_MOSI, I2S1_SD  |

Table 19. Alternate functions available on port F

|          | · · · · · · · · · · · · · · · · · · · |

|----------|---------------------------------------|

| Pin name | AF                                    |

| PF0      | CRS_SYNC                              |

| PF1      | -                                     |

| PF2      | EVENTOUT                              |

| PF3      | EVENTOUT                              |

| PF6      | -                                     |

| PF9      | TIM15_CH1                             |

| PF10     | TIM15_CH2                             |

44/128 DocID025004 Rev 5

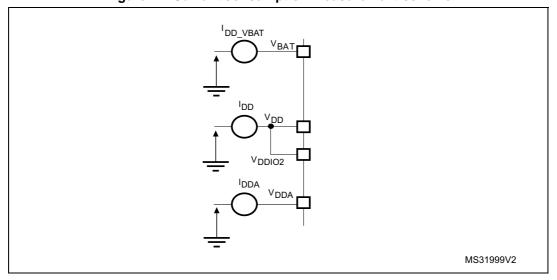

### 6.1.7 Current consumption measurement

Figure 14. Current consumption measurement scheme

## 6.3 Operating conditions

## 6.3.1 General operating conditions

Table 24. General operating conditions

| Symbol             | Parameter                                       | Conditions                                      | Min      | Max                                  | Unit     |  |  |

|--------------------|-------------------------------------------------|-------------------------------------------------|----------|--------------------------------------|----------|--|--|

| f <sub>HCLK</sub>  | Internal AHB clock frequency                    | -                                               | 0        | 48                                   | MHz      |  |  |

| f <sub>PCLK</sub>  | Internal APB clock frequency                    | -                                               | 0        | 48                                   | IVII IZ  |  |  |

| $V_{DD}$           | Standard operating voltage                      | -                                               | 2.0      | 3.6                                  | V        |  |  |

| V <sub>DDIO2</sub> | I/O supply voltage                              | Must not be supplied if $V_{DD}$ is not present | 1.65     | 3.6                                  | ٧        |  |  |

| V                  | Analog operating voltage (ADC and DAC not used) | Must have a potential equal                     | $V_{DD}$ | 3.6                                  | <        |  |  |

| $V_{DDA}$          | Analog operating voltage (ADC and DAC used)     | to or higher than V <sub>DD</sub>               | 2.4      | 3.6                                  | V        |  |  |

| V <sub>BAT</sub>   | Backup operating voltage                        | -                                               | 1.65     | 3.6                                  | V        |  |  |

|                    |                                                 | TC and RST I/O                                  | -0.3     | V <sub>DDIOx</sub> +0.3              |          |  |  |

| V <sub>IN</sub>    | I/O input voltage                               | TTa I/O                                         | -0.3     | V <sub>DDA</sub> +0.3 <sup>(1)</sup> | V        |  |  |

| VIN                |                                                 | FT and FTf I/O                                  | -0.3     | 5.5 <sup>(1)</sup>                   | <b>V</b> |  |  |

|                    |                                                 | воото                                           | 0        | 5.5                                  |          |  |  |

|                    |                                                 | UFBGA100                                        | -        | 364                                  |          |  |  |

|                    |                                                 | LQFP100                                         | -        | 476                                  |          |  |  |

|                    | Power dissipation at T <sub>A</sub> = 85 °C     | UFBGA64                                         | ı        | 308                                  | mW       |  |  |

| $P_{D}$            | for suffix 6 or $T_A = 105$ °C for              | LQFP64                                          | -        | 455                                  |          |  |  |

|                    | suffix 7 <sup>(2)</sup>                         | LQFP48                                          | -        | 370                                  |          |  |  |

|                    |                                                 | UFQFPN48                                        | -        | 625                                  |          |  |  |

|                    |                                                 | WLCSP49                                         | -        | 408                                  |          |  |  |

|                    | Ambient temperature for the                     | Maximum power dissipation                       | -40      | 85                                   | Ĵ        |  |  |

| TA                 | suffix 6 version                                | Low power dissipation <sup>(3)</sup>            | -40      | 105                                  | C        |  |  |

| IA IA              | Ambient temperature for the                     | Maximum power dissipation                       | -40      | 105                                  | - °C     |  |  |

|                    | suffix 7 version                                | Low power dissipation <sup>(3)</sup>            | -40      | 125                                  |          |  |  |

| TJ                 | Junction temperature range                      | Suffix 6 version                                | -40      | 105                                  | Ĵ        |  |  |

| 10                 | Tourious temperature range                      | Suffix 7 version                                | -40      | 125                                  |          |  |  |

<sup>1.</sup> For operation with a voltage higher than  $V_{DDIOx}$  + 0.3 V, the internal pull-up resistor must be disabled.

<sup>2.</sup> If  $T_A$  is lower, higher  $P_D$  values are allowed as long as  $T_J$  does not exceed  $T_{Jmax}$ . See Section 7.8: Thermal characteristics.

<sup>3.</sup> In low power dissipation state, T<sub>A</sub> can be extended to this range as long as T<sub>J</sub> does not exceed T<sub>Jmax</sub> (see Section 7.8: Thermal characteristics).

Table 29. Typical and maximum current consumption from  $V_{DD}$  supply at  $V_{DD}$  = 3.6 V (continued)

|                 | <u>.</u>                                            |                       |                   | All  | peripher                            | als enab | oled <sup>(1)</sup> | All peripherals disabled |                     |                     |                     |      |

|-----------------|-----------------------------------------------------|-----------------------|-------------------|------|-------------------------------------|----------|---------------------|--------------------------|---------------------|---------------------|---------------------|------|

| Symbol          | Parameter                                           | Conditions            | f <sub>HCLK</sub> |      | Max @ T <sub>A</sub> <sup>(2)</sup> |          |                     |                          | М                   | ax @ T <sub>A</sub> | Unit                |      |

| Sy              | Para                                                |                       |                   | Тур  | 25 °C                               | 85 °C    | 105 °C              | Тур                      | 25 °C               | 85 °C               | 105 °C              |      |

|                 |                                                     | HSI48                 | 48 MHz            | 23.1 | 25.4                                | 25.8     | 26.6                | 12.8                     | 13.5                | 13.7                | 13.9                |      |

|                 |                                                     |                       | 48 MHz            | 23.0 | 25.3 <sup>(3)</sup>                 | 25.7     | 26.5 <sup>(3)</sup> | 12.6                     | 13.3 <sup>(3)</sup> | 13.5                | 13.8 <sup>(3)</sup> |      |

|                 | Supply current in Run mode, code executing from RAM | HSE bypass,<br>PLL on | 32 MHz            | 15.4 | 17.3                                | 17.8     | 18.3                | 7.96                     | 8.92                | 9.17                | 9.73                |      |

|                 | E 22                                                |                       | 24 MHz            | 11.4 | 12.9                                | 13.5     | 13.7                | 6.48                     | 8.04                | 8.23                | 8.41                |      |

|                 | upply current in Run<br>code executing from         | HSE bypass,           | 8 MHz             | 4.21 | 4.6                                 | 4.89     | 5.25                | 2.07                     | 2.3                 | 2.35                | 2.94                |      |

|                 | ent i                                               | PLL off               | 1 MHz             | 0.78 | 0.9                                 | 0.92     | 1.15                | 0.36                     | 0.48                | 0.59                | 0.82                |      |

|                 | curr                                                |                       | 48 MHz            | 23.1 | 24.5                                | 25.0     | 25.2                | 12.6                     | 13.7                | 13.9                | 14.0                |      |

|                 | oply                                                | HSI clock,<br>PLL on  | 32 MHz            | 15.4 | 17.4                                | 17.7     | 18.2                | 8.05                     | 8.85                | 9.16                | 9.94                |      |

|                 | lns                                                 |                       | 24 MHz            | 11.5 | 13.0                                | 13.6     | 13.9                | 6.49                     | 8.06                | 8.21                | 8.47                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 4.34 | 4.75                                | 5.03     | 5.41                | 2.11                     | 2.36                | 2.38                | 2.98                | mA   |

| I <sub>DD</sub> |                                                     | HSI48                 | 48 MHz            | 15.1 | 16.6                                | 16.8     | 17.5                | 3.08                     | 3.43                | 3.56                | 3.61                | IIIA |

|                 |                                                     |                       | 48 MHz            | 15.0 | 16.5 <sup>(3)</sup>                 | 16.7     | 17.3 <sup>(3)</sup> | 2.93                     | 3.28 <sup>(3)</sup> | 3.41                | 3.46 <sup>(3)</sup> |      |

|                 | )ode                                                | HSE bypass,<br>PLL on | 32 MHz            | 9.9  | 11.4                                | 11.6     | 11.9                | 2.0                      | 2.24                | 2.32                | 2.49                |      |

|                 | eb n                                                |                       | 24 MHz            | 7.43 | 8.17                                | 8.71     | 8.82                | 1.63                     | 1.82                | 1.88                | 1.9                 |      |

|                 | Sle                                                 | HSE bypass,           | 8 MHz             | 2.83 | 3.09                                | 3.26     | 3.66                | 0.76                     | 0.88                | 0.91                | 0.93                |      |

|                 | int ir                                              | PLL off               | 1 MHz             | 0.42 | 0.54                                | 0.55     | 0.67                | 0.28                     | 0.39                | 0.41                | 0.43                |      |

|                 | curre                                               |                       | 48 MHz            | 15.0 | 17.2                                | 17.3     | 17.9                | 3.04                     | 3.37                | 3.41                | 3.46                |      |

|                 | Supply current in Sleep mode                        | HSI clock,<br>PLL on  | 32 MHz            | 9.93 | 11.3                                | 11.6     | 11.7                | 2.11                     | 2.35                | 2.44                | 2.65                |      |

|                 | Sup                                                 |                       | 24 MHz            | 7.53 | 8.45                                | 8.87     | 8.95                | 1.64                     | 1.83                | 1.9                 | 1.93                |      |

|                 |                                                     | HSI clock,<br>PLL off | 8 MHz             | 2.95 | 3.24                                | 3.41     | 3.8                 | 0.8                      | 0.92                | 0.94                | 0.97                |      |

<sup>1.</sup> USB is kept disabled as this IP functions only with a 48 MHz clock.

<sup>2.</sup> Data based on characterization results, not tested in production unless otherwise specified.

<sup>3.</sup> Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

Table 34. Switching output I/O current consumption

| Symbol          | Parameter                  | Conditions <sup>(1)</sup>                                             | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|----------------------------|-----------------------------------------------------------------------|----------------------------------------------|-------|------|

|                 |                            |                                                                       | 4 MHz                                        | 0.07  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                            | 8 MHz                                        | 0.15  |      |

|                 |                            | C =C <sub>INT</sub>                                                   | 16 MHz                                       | 0.31  |      |

|                 |                            |                                                                       | 24 MHz                                       | 0.53  |      |

|                 |                            |                                                                       | 48 MHz                                       | 0.92  |      |

|                 |                            |                                                                       | 4 MHz                                        | 0.18  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                            | 8 MHz                                        | 0.37  |      |

|                 |                            | C <sub>EXT</sub> = 0 pF                                               | 16 MHz                                       | 0.76  |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                       | 24 MHz                                       | 1.39  |      |

|                 |                            |                                                                       | 48 MHz                                       | 2.188 |      |

|                 |                            |                                                                       | 4 MHz                                        | 0.32  |      |

|                 | I/O current<br>consumption | V <sub>DDIOx</sub> = 3.3 V                                            | 8 MHz                                        | 0.64  | . mA |

|                 |                            | $C_{EXT} = 10 \text{ pF}$ $C = C_{INT} + C_{EXT} + C_{S}$             | 16 MHz                                       | 1.25  |      |

|                 |                            |                                                                       | 24 MHz                                       | 2.23  |      |

| I <sub>SW</sub> |                            |                                                                       | 48 MHz                                       | 4.442 |      |

| SVV             |                            |                                                                       | 4 MHz                                        | 0.49  |      |

|                 |                            | $V_{DDIOx} = 3.3 V$ $C_{EXT} = 22 pF$ $C = C_{INT} + C_{EXT} + C_{S}$ | 8 MHz                                        | 0.94  |      |

|                 |                            |                                                                       | 16 MHz                                       | 2.38  |      |

|                 |                            | INT EXT 0                                                             | 24 MHz                                       | 3.99  |      |

|                 |                            |                                                                       | 4 MHz                                        | 0.64  |      |

|                 |                            | $V_{DDIOx} = 3.3 \text{ V}$ $C_{EXT} = 33 \text{ pF}$                 | 8 MHz                                        | 1.25  |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                       | 16 MHz                                       | 3.24  |      |

|                 |                            | INT EXT O                                                             | 24 MHz                                       | 5.02  |      |

|                 |                            | V <sub>DDIOx</sub> = 3.3 V                                            | 4 MHz                                        | 0.81  |      |

|                 |                            | $C_{EXT} = 47 \text{ pF}$                                             | 8 MHz                                        | 1.7   |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$ $C = C_{int}$                         | 16 MHz                                       | 3.67  | -    |

|                 |                            | V <sub>DDIOx</sub> = 2.4 V                                            | 4 MHz                                        | 0.66  |      |

|                 |                            | $C_{\text{EXT}} = 47 \text{ pF}$                                      | 8 MHz                                        | 1.43  |      |

|                 |                            | $C = C_{INT} + C_{EXT} + C_{S}$                                       | 16 MHz                                       | 2.45  |      |

|                 |                            | C = C <sub>int</sub>                                                  | 24 MHz                                       | 4.97  |      |

<sup>1.</sup> C<sub>S</sub> = 7 pF (estimated value).

1. Guaranteed by design, not tested in production.

VHSEL

90%

10%

tr(HSE)

THSE

W(HSEH)

tw(HSEH)

tw(HSEL)

tw(HSEL)

MS19214V2

Figure 15. High-speed external clock source AC timing diagram

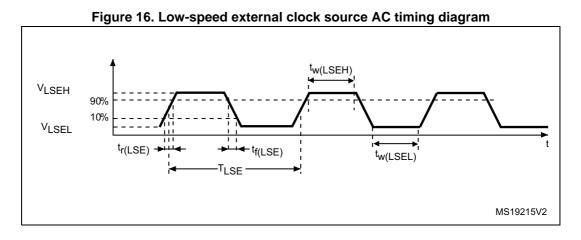

#### Low-speed external user clock generated from an external source

In bypass mode the LSE oscillator is switched off and the input pin is a standard GPIO.

The external clock signal has to respect the I/O characteristics in *Section 6.3.14*. However, the recommended clock input waveform is shown in *Figure 16*.

| Symbol                                                   | Parameter <sup>(1)</sup>              | Min                    | Тур                         | Max                    | Unit |  |

|----------------------------------------------------------|---------------------------------------|------------------------|-----------------------------|------------------------|------|--|

| f <sub>LSE_ext</sub>                                     | User external clock source frequency  | -                      | 32.768                      | 1000                   | kHz  |  |

| $V_{LSEH}$                                               | OSC32_IN input pin high level voltage | 0.7 V <sub>DDIOx</sub> | DIOX - V <sub>DDIOX</sub> V |                        |      |  |

| $V_{LSEL}$                                               | OSC32_IN input pin low level voltage  | $V_{SS}$               | -                           | 0.3 V <sub>DDIOx</sub> | 7 °  |  |

| $\begin{matrix} t_{w(LSEH)} \\ t_{w(LSEL)} \end{matrix}$ | OSC32_IN high or low time             | 450                    | -                           | -                      | ns   |  |

| $t_{r(LSE)}$ $t_{f(LSE)}$                                | OSC32_IN rise or fall time            | -                      | -                           | 50                     | 115  |  |

Table 38. Low-speed external user clock characteristics

<sup>1.</sup> Guaranteed by design, not tested in production.

- ADC Accuracy vs. Negative Injection Current: Injecting negative current on any of the standard (non-robust) analog input pins should be avoided as this significantly reduces the accuracy of the conversion being performed on another analog input. It is recommended to add a Schottky diode (pin to ground) to standard analog pins which may potentially inject negative current

- Any positive injection current within the limits specified for I<sub>INJ(PIN)</sub> and ΣI<sub>INJ(PIN)</sub> in Section 6.3.14 does not affect the ADC accuracy.

- Better performance may be achieved in restricted V<sub>DDA</sub>, frequency and temperature ranges.

- Data based on characterization results, not tested in production.

Eg (1) Example of an actual transfer curve 4095 (2) The ideal transfer curve (3) End point correlation line 4094 4093 ET = Total Unajusted Error: maximum deviation between the actual and ideal transfer curves. Eo = Offset Error: maximum deviation between the first actual transition and the first ideal one. 6 Eg = Gain Error: deviation between the last 5 ideal transition and the last actual one. Fi 4 ED = Differential Linearity Error: maximum deviation between actual steps and the ideal ones. 3 EL = Integral Linearity Error: maximum deviation 2 between any actual transition and the end point 1 LSB IDEAL correlation line. VDDA 0 4093 4094 4095 4096 5 6 7

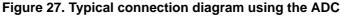

Figure 26. ADC accuracy characteristics

- Refer to Table 57: ADC characteristics for the values of  $R_{AIN}$ ,  $R_{ADC}$  and  $C_{ADC}$ .

- $C_{parasitic}$  represents the capacitance of the PCB (dependent on soldering and PCB layout quality) plus the pad capacitance (roughly 7 pF). A high  $C_{parasitic}$  value will downgrade conversion accuracy. To remedy this,  $f_{ADC}$  should be reduced.

#### General PCB design guidelines

Power supply decoupling should be performed as shown in Figure 13: Power supply scheme. The 10 nF capacitor should be ceramic (good quality) and it should be placed as close as possible to the chip.

MS19880V2

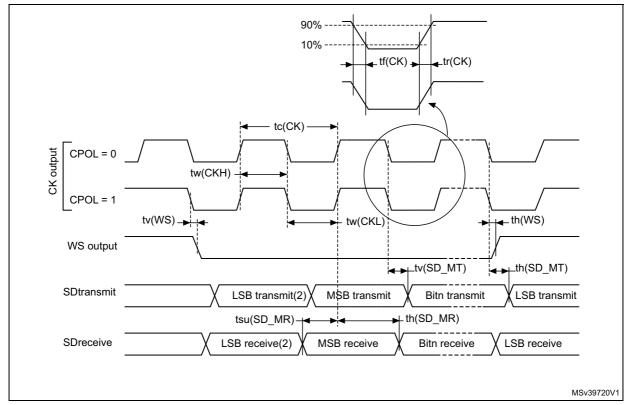

Figure 34. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

577

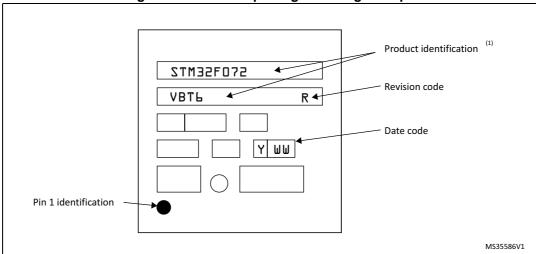

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 40. LQFP100 package marking example

1. Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

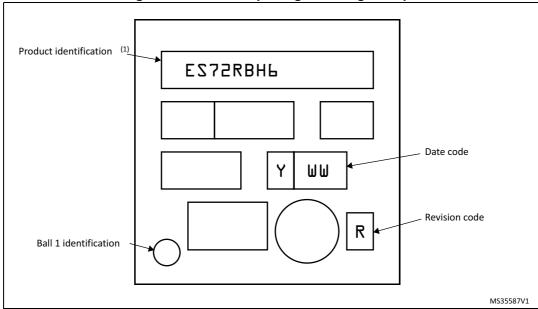

### **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Figure 43. UFBGA64 package marking example

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

### 7.8 Thermal characteristics

The maximum chip junction temperature (T<sub>J</sub>max) must never exceed the values given in *Table 24: General operating conditions*.

The maximum chip-junction temperature,  $T_J$  max, in degrees Celsius, may be calculated using the following equation:

$$T_J \max = T_A \max + (P_D \max x \Theta_{JA})$$

#### Where:

- T<sub>A</sub> max is the maximum ambient temperature in °C,

- Θ<sub>JA</sub> is the package junction-to-ambient thermal resistance, in °C/W,

- $P_D$  max is the sum of  $P_{INT}$  max and  $P_{I/O}$  max ( $P_D$  max =  $P_{INT}$  max +  $P_{I/O}$ max),

- P<sub>INT</sub> max is the product of I<sub>DD</sub> and V<sub>DD</sub>, expressed in Watts. This is the maximum chip internal power.

P<sub>I/O</sub> max represents the maximum power dissipation on output pins where:

$$P_{I/O}$$

max =  $\Sigma (V_{OL} \times I_{OL}) + \Sigma ((V_{DDIOx} - V_{OH}) \times I_{OH})$ ,

taking into account the actual  $V_{OL}$  /  $I_{OL}$  and  $V_{OH}$  /  $I_{OH}$  of the I/Os at low and high level in the application.

| Symbol                | Parameter                                                                 | Value | Unit |

|-----------------------|---------------------------------------------------------------------------|-------|------|

| $\Theta_{	extsf{JA}}$ | Thermal resistance junction-ambient UFBGA100 - 7 × 7 mm                   | 55    |      |

|                       | Thermal resistance junction-ambient<br>LQFP100 - 14 × 14 mm               | 42    |      |

|                       | Thermal resistance junction-ambient UFBGA64 - 5 × 5 mm / 0.5 mm pitch     | 65    |      |

|                       | Thermal resistance junction-ambient<br>LQFP64 - 10 × 10 mm / 0.5 mm pitch | 44    | °C/W |

|                       | Thermal resistance junction-ambient LQFP48 - 7 × 7 mm                     | 54    |      |

|                       | Thermal resistance junction-ambient UFQFPN48 - 7 × 7 mm                   | 32    |      |

|                       | Thermal resistance junction-ambient WLCSP49 - 0.4 mm pitch                | 49    |      |

Table 80. Package thermal characteristics

### 7.8.1 Reference document

JESD51-2 Integrated Circuits Thermal Test Method Environment Conditions - Natural Convection (Still Air). Available from www.jedec.org

### 7.8.2 Selecting the product temperature range

When ordering the microcontroller, the temperature range is specified in the ordering information scheme shown in *Section 8: Ordering information*.

Table 82. Document revision history (continued)

| Date        | Revision      | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 18-Sep-2015 | 3 (continued) | <ul> <li>Table 42: HSI14 oscillator characteristics: changed the min value for ACC<sub>HSI14</sub></li> <li>Table 46: Flash memory characteristics: removed V<sub>prog</sub></li> <li>Table 49: EMI characteristics updated</li> <li>Table 50: ESD absolute maximum ratings updated</li> <li>Table 57: ADC characteristics - updated some parameter values, test conditions and added footnotes <sup>(3)</sup> and <sup>(4)</sup></li> <li>Table 60: DAC characteristics - I<sub>DDA</sub> max value (DAC DC current consumption) updated</li> <li>Table 61: Comparator characteristics: changed the description and values for t<sub>S_SC</sub> parameter</li> <li>Table 62: TS characteristics: changed the min value for t<sub>S-temp</sub></li> <li>Table 63: VBAT monitoring characteristics: changed the typical value for R parameter</li> <li>Table 69: I<sup>2</sup>S characteristics: updated the min value for data input hold time (master and slave receiver)</li> <li>Section 7: Package information:         <ul> <li>information generally updated, UFBGA64 added</li> </ul> </li> <li>Section 8: Part numbering: UFBGA64 added</li> </ul> |

| 17-Dec-2015 | 4             | Section 2: Description:  - Figure 1: Block diagram updated Section 3: Functional overview:  - Figure 2: Clock tree updated Section 4: Pinouts and pin descriptions  - Package pinout figures updated (look and feel)  - Figure 9: WLCSP49 package pinout - now presented in top view Section 5: Memory mapping:  - added information on STM32F072x8 difference versus STM32F072xB map in Figure 10  - Table 28: Embedded internal reference voltage: removed -40°-to-85° condition for V <sub>REFINT</sub> and associated note Section 6: Electrical characteristics:  - Table 61: Comparator characteristics - min value for V <sub>DDA</sub> replaced with V <sub>DD</sub> - Figure 29: Maximum V <sub>REFINT</sub> scaler startup time from power down added  - Table 53: I/O static characteristics - note removed  - Table 69: I <sup>2</sup> S characteristics: table reorganized Section 8: Ordering information:  - added tray packing to options                                                                                                                                                                                                  |

Table 82. Document revision history (continued)

| Date        | Revision | Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Jan-2017 | 5        | Section 6: Electrical characteristics:  - Table 40: LSE oscillator characteristics (f <sub>LSE</sub> = 32.768 kHz) - information on configuring different drive capabilities removed. See the corresponding reference manual.  - Table 28: Embedded internal reference voltage - V <sub>REFINT</sub> values  - Table 60: DAC characteristics - min. R <sub>LOAD</sub> to V <sub>DDA</sub> defined - Figure 30: SPI timing diagram - slave mode and CPHA = 0 and Figure 31: SPI timing diagram - slave mode and CPHA = 1 enhanced and corrected  Section 8: Ordering information:  - The name of the section changed from the previous "Part numbering" |