Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                        |  |

|----------------------------|------------------------------------------------------------------------|--|

| Product Status             | Active                                                                 |  |

| Core Processor             | ARM® Cortex®-M0                                                        |  |

| Core Size                  | 32-Bit Single-Core                                                     |  |

| Speed                      | 48MHz                                                                  |  |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB |  |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                   |  |

| Number of I/O              | 37                                                                     |  |

| Program Memory Size        | 128KB (128K x 8)                                                       |  |

| Program Memory Type        | FLASH                                                                  |  |

| EEPROM Size                | -                                                                      |  |

| RAM Size                   | 16K x 8                                                                |  |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                           |  |

| Data Converters            | A/D 10x12b; D/A 2x12b                                                  |  |

| Oscillator Type            | Internal                                                               |  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                      |  |

| Mounting Type              | Surface Mount                                                          |  |

| Package / Case             | 48-UFQFN Exposed Pad                                                   |  |

| Supplier Device Package    | 48-UFQFPN (7x7)                                                        |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f072cbu6  |  |

|                            |                                                                        |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 3.14.6    | SysTick timer                                                                       | 23 |  |

|------|-----------|-------------------------------------------------------------------------------------|----|--|

| 3.15 | Real-ti   | me clock (RTC) and backup registers                                                 | 23 |  |

| 3.16 | Inter-ir  | Inter-integrated circuit interface (I <sup>2</sup> C) 2                             |    |  |

| 3.17 | Univer    | Universal synchronous/asynchronous receiver/transmitter (USART) 2                   |    |  |

| 3.18 | Serial    | Serial peripheral interface (SPI) / Inter-integrated sound interface ( $I^2S$ ) . 2 |    |  |

| 3.19 | •         | efinition multimedia interface (HDMI) - consumer                                    | 26 |  |

| 3.20 |           | ller area network (CAN)                                                             |    |  |

|      |           |                                                                                     |    |  |

| 3.21 |           | sal serial bus (USB)                                                                |    |  |

| 3.22 |           | recovery system (CRS)                                                               |    |  |

| 3.23 | Serial    | wire debug port (SW-DP)                                                             | 27 |  |

| Pino | uts and   | pin descriptions                                                                    | 28 |  |

| Mem  | ory ma    | pping                                                                               | 45 |  |

| Elec | trical cł | naracteristics                                                                      | 48 |  |

| 6.1  | Param     | eter conditions                                                                     | 48 |  |

|      | 6.1.1     | Minimum and maximum values                                                          | 48 |  |

|      | 6.1.2     | Typical values                                                                      | 48 |  |

|      | 6.1.3     | Typical curves                                                                      | 48 |  |

|      | 6.1.4     | Loading capacitor                                                                   | 48 |  |

|      | 6.1.5     | Pin input voltage                                                                   | 48 |  |

|      | 6.1.6     | Power supply scheme                                                                 | 49 |  |

|      | 6.1.7     | Current consumption measurement                                                     | 50 |  |

| 6.2  | Absolu    | Ite maximum ratings                                                                 | 51 |  |

| 6.3  | Opera     | ting conditions                                                                     | 53 |  |

|      | 6.3.1     | General operating conditions                                                        | 53 |  |

|      | 6.3.2     | Operating conditions at power-up / power-down                                       | 54 |  |

|      | 6.3.3     | Embedded reset and power control block characteristics                              | 54 |  |

|      | 6.3.4     | Embedded reference voltage                                                          | 55 |  |

|      | 6.3.5     | Supply current characteristics                                                      | 55 |  |

|      | 6.3.6     | Wakeup time from low-power mode                                                     | 66 |  |

|      | 6.3.7     | External clock source characteristics                                               | 66 |  |

|      | 6.3.8     | Internal clock source characteristics                                               | 70 |  |

|      | 6.3.9     | PLL characteristics                                                                 | 74 |  |

4

5

6

|   |      | 6.3.10     | Memory characteristics74                    |

|---|------|------------|---------------------------------------------|

|   |      | 6.3.11     | EMC characteristics                         |

|   |      | 6.3.12     | Electrical sensitivity characteristics      |

|   |      | 6.3.13     | I/O current injection characteristics77     |

|   |      | 6.3.14     | I/O port characteristics                    |

|   |      | 6.3.15     | NRST pin characteristics                    |

|   |      | 6.3.16     | 12-bit ADC characteristics                  |

|   |      | 6.3.17     | DAC electrical specifications               |

|   |      | 6.3.18     | Comparator characteristics90                |

|   |      | 6.3.19     | Temperature sensor characteristics 92       |

|   |      | 6.3.20     | V <sub>BAT</sub> monitoring characteristics |

|   |      | 6.3.21     | Timer characteristics                       |

|   |      | 6.3.22     | Communication interfaces                    |

| 7 | Pack | kage info  | ormation                                    |

|   | 7.1  | UFBGA      | 100 package information 100                 |

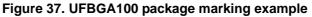

|   | 7.2  | LQFP1      | 00 package information                      |

|   | 7.3  | UFBGA      | 64 package information 106                  |

|   | 7.4  | LQFP6      | 4 package information                       |

|   | 7.5  | WLCSF      | P49 package information112                  |

|   | 7.6  | LQFP4      | 8 package information                       |

|   | 7.7  | UFQFF      | N48 package information118                  |

|   | 7.8  | Therma     | al characteristics                          |

|   |      | 7.8.1      | Reference document                          |

|   |      | 7.8.2      | Selecting the product temperature range     |

| 8 | Orde | ering info | ormation                                    |

| 9 | Revi | sion his   | tory                                        |

TIM15 has two independent channels, whereas TIM16 and TIM17 feature one single channel for input capture/output compare, PWM or one-pulse mode output.

The TIM15, TIM16 and TIM17 timers can work together, and TIM15 can also operate with TIM1 via the Timer Link feature for synchronization or event chaining.

TIM15 can be synchronized with TIM16 and TIM17.

TIM15, TIM16 and TIM17 have a complementary output with dead-time generation and independent DMA request generation.

Their counters can be frozen in debug mode.

#### 3.14.3 Basic timers TIM6 and TIM7

These timers are mainly used for DAC trigger generation. They can also be used as generic 16-bit time bases.

#### 3.14.4 Independent watchdog (IWDG)

The independent watchdog is based on an 8-bit prescaler and 12-bit downcounter with user-defined refresh window. It is clocked from an independent 40 kHz internal RC and as it operates independently from the main clock, it can operate in Stop and Standby modes. It can be used either as a watchdog to reset the device when a problem occurs, or as a free running timer for application timeout management. It is hardware or software configurable through the option bytes. The counter can be frozen in debug mode.

#### 3.14.5 System window watchdog (WWDG)

The system window watchdog is based on a 7-bit downcounter that can be set as free running. It can be used as a watchdog to reset the device when a problem occurs. It is clocked from the APB clock (PCLK). It has an early warning interrupt capability and the counter can be frozen in debug mode.

#### 3.14.6 SysTick timer

This timer is dedicated to real-time operating systems, but could also be used as a standard down counter. It features:

- a 24-bit down counter

- autoreload capability

- maskable system interrupt generation when the counter reaches 0

- programmable clock source (HCLK or HCLK/8)

# 3.15 Real-time clock (RTC) and backup registers

The RTC and the five backup registers are supplied through a switch that takes power either on  $V_{DD}$  supply when present or through the  $V_{BAT}$  pin. The backup registers are five 32-bit registers used to store 20 bytes of user application data when  $V_{DD}$  power is not present. They are not reset by a system or power reset, or at wake up from Standby mode.

verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to *Table 9* for the differences between I2C1 and I2C2.

| Table 9. STM32F072x8/xB | I <sup>2</sup> C implementation |

|-------------------------|---------------------------------|

|-------------------------|---------------------------------|

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive I/Os | Х    | Х    |

| Independent clock                                            | Х    | -    |

| SMBus                                                        | Х    | -    |

| Wakeup from STOP                                             | Х    | -    |

1. X = supported.

# 3.17 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds four universal synchronous/asynchronous receivers/transmitters (USART1, USART2, USART3, USART4) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 support also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and have a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 and<br>USART2 | USART3 and<br>USART4 |

|---------------------------------------|----------------------|----------------------|

| Hardware flow control for modem       | Х                    | Х                    |

| Continuous communication using DMA    | Х                    | Х                    |

| Multiprocessor communication          | Х                    | х                    |

| Synchronous mode                      | Х                    | Х                    |

| Smartcard mode                        | Х                    | -                    |

| Single-wire half-duplex communication | Х                    | Х                    |

| USART modes/features <sup>(1)</sup>         | USART1 and<br>USART2 | USART3 and<br>USART4 |

|---------------------------------------------|----------------------|----------------------|

| IrDA SIR ENDEC block                        | Х                    | -                    |

| LIN mode                                    | Х                    | -                    |

| Dual clock domain and wakeup from Stop mode | Х                    | -                    |

| Receiver timeout interrupt                  | Х                    | -                    |

| Modbus communication                        | Х                    | -                    |

| Auto baud rate detection                    | Х                    | -                    |

| Driver Enable                               | Х                    | Х                    |

| Table 10. STM3 | 2F072x8/xB USAR | T implementation | (continued) |  |

|----------------|-----------------|------------------|-------------|--|

|                |                 |                  | (           |  |

1. X = supported.

# 3.18 Serial peripheral interface (SPI) / Inter-integrated sound interface (I<sup>2</sup>S)

Two SPIs are able to communicate up to 18 Mbit/s in slave and master modes in full-duplex and half-duplex communication modes. The 3-bit prescaler gives 8 master mode frequencies and the frame size is configurable from 4 bits to 16 bits.

Two standard I<sup>2</sup>S interfaces (multiplexed with SPI1 and SPI2 respectively) supporting four different audio standards can operate as master or slave at half-duplex communication mode. They can be configured to transfer 16 and 24 or 32 bits with 16-bit or 32-bit data resolution and synchronized by a specific signal. Audio sampling frequency from 8 kHz up to 192 kHz can be set by an 8-bit programmable linear prescaler. When operating in master mode, they can output a clock for an external audio component at 256 times the sampling frequency.

| Table 11. STM32F072x8/xB SPI/I <sup>2</sup> S im | plementation |

|--------------------------------------------------|--------------|

|--------------------------------------------------|--------------|

| SPI features <sup>(1)</sup> | SPI1 and SPI2 |

|-----------------------------|---------------|

| Hardware CRC calculation    | Х             |

| Rx/Tx FIFO                  | Х             |

| NSS pulse mode              | Х             |

| I <sup>2</sup> S mode       | Х             |

| TI mode                     | Х             |

1. X = supported.

# 3.19 High-definition multimedia interface (HDMI) - consumer electronics control (CEC)

The device embeds a HDMI-CEC controller that provides hardware support for the Consumer Electronics Control (CEC) protocol (Supplement 1 to the HDMI standard).

This protocol provides high-level control functions between all audiovisual products in an environment. It is specified to operate at low speeds with minimum processing and memory

| Na                                                                                                                                      | me                     | Abbreviation                                                                                      | Definition                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

| Pin name Unless otherwise specified in brackets below the pin name, the pin function dur after reset is the same as the actual pin name |                        |                                                                                                   |                                                             |

|                                                                                                                                         |                        | S                                                                                                 | Supply pin                                                  |

| Pin                                                                                                                                     | type                   | I                                                                                                 | Input-only pin                                              |

|                                                                                                                                         |                        | I/O                                                                                               | Input / output pin                                          |

|                                                                                                                                         |                        | FT                                                                                                | 5 V-tolerant I/O                                            |

|                                                                                                                                         |                        | FTf                                                                                               | 5 V-tolerant I/O, FM+ capable                               |

| I/O otr                                                                                                                                 | ucture                 | TTa                                                                                               | 3.3 V-tolerant I/O directly connected to ADC                |

| 1/0 50                                                                                                                                  | ucture                 | TC                                                                                                | Standard 3.3 V I/O                                          |

|                                                                                                                                         |                        | В                                                                                                 | Dedicated BOOT0 pin                                         |

|                                                                                                                                         |                        | RST                                                                                               | Bidirectional reset pin with embedded weak pull-up resistor |

| Notes                                                                                                                                   |                        | Unless otherwise specified by a note, all I/Os are set as floating inputs during and after reset. |                                                             |

| Pin<br>functions                                                                                                                        | Alternate<br>functions | Functions selected through GPIOx_AFR registers                                                    |                                                             |

|                                                                                                                                         | Additional functions   | Functions directly selected/enabled through peripheral registers                                  |                                                             |

| Table 12. Legend/abbreviations used in the | oinout table |

|--------------------------------------------|--------------|

|                                            | on our cabie |

# Table 13. STM32F072x8/xB pin definitions

|          | Р       | 'in nu  | mber   | s               |         |                                      |             |                                |   | Pin functions           |                         |  |

|----------|---------|---------|--------|-----------------|---------|--------------------------------------|-------------|--------------------------------|---|-------------------------|-------------------------|--|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | تب ر                           |   | Alternate functions     | Additional<br>functions |  |

| B2       | 1       | -       | -      | -               | -       | PE2                                  | I/O         | FT                             | - | TSC_G7_IO1,<br>TIM3_ETR | -                       |  |

| A1       | 2       | -       | -      | -               | -       | PE3                                  | I/O         | FT                             | - | TSC_G7_IO2,<br>TIM3_CH1 | -                       |  |

| B1       | 3       | -       | -      | -               | -       | PE4                                  | I/O         | FT                             | - | TSC_G7_IO3,<br>TIM3_CH2 | -                       |  |

| C2       | 4       | -       | -      | -               | -       | PE5                                  | I/O         | ) FT - TSC_G7_IO4,<br>TIM3_CH3 |   | -                       |                         |  |

| D2       | 5       | -       | -      | -               | -       | PE6                                  | I/O         | FT                             | - | TIM3_CH4                | WKUP3,<br>RTC_TAMP3     |  |

| E2       | 6       | B2      | 1      | 1               | B7      | VBAT                                 | S           | -                              | - | Backup power supply     |                         |  |

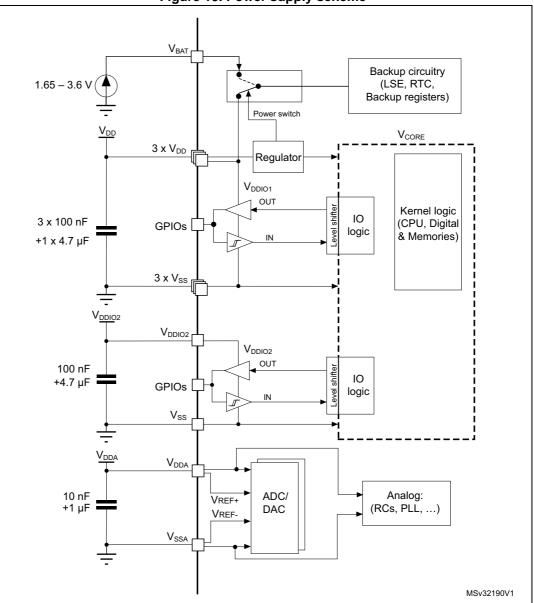

# 6.1.6 Power supply scheme

Figure 13. Power supply scheme

**Caution:** Each power supply pair (V<sub>DD</sub>/V<sub>SS</sub>, V<sub>DDA</sub>/V<sub>SSA</sub> etc.) must be decoupled with filtering ceramic capacitors as shown above. These capacitors must be placed as close as possible to, or below, the appropriate pins on the underside of the PCB to ensure the good functionality of the device.

| er              |                                                      |                       |            | All        | peripher            | als enab   |                     |            | periphe             | rals disa  | abled               |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|-----------------|------------------------------------------------------|-----------------------|------------|------------|---------------------|------------|---------------------|------------|---------------------|------------|---------------------|------------|------------|------------|------------|-------------------|--|---|----------------------|-----|--|-------------------------------------|--|--|------|

| Symbol          | Parameter                                            | Conditions            | Conditions | Conditions | Conditions          | Conditions | Conditions          | Conditions | Conditions          | Conditions | Conditions          | Conditions | Conditions | Conditions | Conditions | f <sub>HCLK</sub> |  | M | lax @ T <sub>A</sub> | (2) |  | Max @ T <sub>A</sub> <sup>(2)</sup> |  |  | Unit |

| Sy              | Para                                                 |                       |            | Тур        | 25 °C               | 85 °C      | 105 °C              | Тур        | 25 °C               | 85 °C      | 105 °C              |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 |                                                      | HSI48                 | 48 MHz     | 23.1       | 25.4                | 25.8       | 26.6                | 12.8       | 13.5                | 13.7       | 13.9                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 |                                                      |                       | 48 MHz     | 23.0       | 25.3 <sup>(3)</sup> | 25.7       | 26.5 <sup>(3)</sup> | 12.6       | 13.3 <sup>(3)</sup> | 13.5       | 13.8 <sup>(3)</sup> |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | Supply current in Run mode, code executing from RAM  | HSE bypass,<br>PLL on | 32 MHz     | 15.4       | 17.3                | 17.8       | 18.3                | 7.96       | 8.92                | 9.17       | 9.73                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | upply current in Run mode<br>code executing from RAM |                       | 24 MHz     | 11.4       | 12.9                | 13.5       | 13.7                | 6.48       | 8.04                | 8.23       | 8.41                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | n Ru<br>g froi                                       | HSE bypass,           | 8 MHz      | 4.21       | 4.6                 | 4.89       | 5.25                | 2.07       | 2.3                 | 2.35       | 2.94                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | ent i<br>utinç                                       | PLL off               | 1 MHz      | 0.78       | 0.9                 | 0.92       | 1.15                | 0.36       | 0.48                | 0.59       | 0.82                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | curr<br>exec                                         |                       | 48 MHz     | 23.1       | 24.5                | 25.0       | 25.2                | 12.6       | 13.7                | 13.9       | 14.0                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | pply<br>ode (                                        | HSI clock,<br>PLL on  | 32 MHz     | 15.4       | 17.4                | 17.7       | 18.2                | 8.05       | 8.85                | 9.16       | 9.94                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | Sul                                                  |                       | 24 MHz     | 11.5       | 13.0                | 13.6       | 13.9                | 6.49       | 8.06                | 8.21       | 8.47                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 |                                                      | HSI clock,<br>PLL off | 8 MHz      | 4.34       | 4.75                | 5.03       | 5.41                | 2.11       | 2.36                | 2.38       | 2.98                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

| I <sub>DD</sub> |                                                      | HSI48                 | 48 MHz     | 15.1       | 16.6                | 16.8       | 17.5                | 3.08       | 3.43                | 3.56       | 3.61                | mA         |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 |                                                      |                       | 48 MHz     | 15.0       | 16.5 <sup>(3)</sup> | 16.7       | 17.3 <sup>(3)</sup> | 2.93       | 3.28 <sup>(3)</sup> | 3.41       | 3.46 <sup>(3)</sup> |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | node                                                 | HSE bypass,<br>PLL on | 32 MHz     | 9.9        | 11.4                | 11.6       | 11.9                | 2.0        | 2.24                | 2.32       | 2.49                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | ep n                                                 |                       | 24 MHz     | 7.43       | 8.17                | 8.71       | 8.82                | 1.63       | 1.82                | 1.88       | 1.9                 |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | l Sle                                                | HSE bypass,           | 8 MHz      | 2.83       | 3.09                | 3.26       | 3.66                | 0.76       | 0.88                | 0.91       | 0.93                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | ent ir                                               | PLL off               | 1 MHz      | 0.42       | 0.54                | 0.55       | 0.67                | 0.28       | 0.39                | 0.41       | 0.43                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | Supply current in Sleep mode                         |                       | 48 MHz     | 15.0       | 17.2                | 17.3       | 17.9                | 3.04       | 3.37                | 3.41       | 3.46                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | ply .                                                | HSI clock,<br>PLL on  | 32 MHz     | 9.93       | 11.3                | 11.6       | 11.7                | 2.11       | 2.35                | 2.44       | 2.65                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 | ldnS                                                 |                       | 24 MHz     | 7.53       | 8.45                | 8.87       | 8.95                | 1.64       | 1.83                | 1.9        | 1.93                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

|                 |                                                      | HSI clock,<br>PLL off | 8 MHz      | 2.95       | 3.24                | 3.41       | 3.8                 | 0.8        | 0.92                | 0.94       | 0.97                |            |            |            |            |                   |  |   |                      |     |  |                                     |  |  |      |

| Table 29. Typical and maximum | current consumption from V <sub>Dr</sub> | <sub>D</sub> supply at V <sub>DD</sub> = 3.6 V (continued) |

|-------------------------------|------------------------------------------|------------------------------------------------------------|

|                               |                                          |                                                            |

1. USB is kept disabled as this IP functions only with a 48 MHz clock.

2. Data based on characterization results, not tested in production unless otherwise specified.

3. Data based on characterization results and tested in production (using one common test limit for sum of  $I_{DD}$  and  $I_{DDA}$ ).

#### STM32F072x8 STM32F072xB

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                                                                | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit  |

|-----------------|-------------|--------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-------|-------|

|                 |             |                                                                                                                          | 4 MHz                                        | 0.07  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                                                               | 8 MHz                                        | 0.15  |       |

|                 |             | C =C <sub>INT</sub>                                                                                                      | 16 MHz                                       | 0.31  |       |

|                 |             |                                                                                                                          | 24 MHz                                       | 0.53  |       |

|                 |             |                                                                                                                          | 48 MHz                                       | 0.92  |       |

|                 |             |                                                                                                                          | 4 MHz                                        | 0.18  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                                                               | 8 MHz                                        | 0.37  |       |

|                 |             | C <sub>EXT</sub> = 0 pF                                                                                                  | 16 MHz                                       | 0.76  |       |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                                                            | 24 MHz                                       | 1.39  |       |

|                 |             |                                                                                                                          | 48 MHz                                       | 2.188 |       |

|                 |             |                                                                                                                          | 4 MHz                                        | 0.32  |       |

|                 |             | $V_{\text{DDIOx}} = 3.3 \text{ V}$ $C_{\text{EXT}} = 10 \text{ pF}$ $C = C_{\text{INT}} + C_{\text{EXT}} + C_{\text{S}}$ | 8 MHz                                        | 0.64  | mA    |

|                 |             |                                                                                                                          | 16 MHz                                       | 1.25  |       |

|                 |             |                                                                                                                          | 24 MHz                                       | 2.23  |       |

| I <sub>SW</sub> | I/O current |                                                                                                                          | 48 MHz                                       | 4.442 |       |

| ISW             | consumption |                                                                                                                          | 4 MHz                                        | 0.49  | 110 ( |

|                 |             | $V_{DDIOX} = 3.3 V$<br>$C_{EXT} = 22 pF$<br>$C = C_{INT} + C_{EXT} + C_S$                                                | 8 MHz                                        | 0.94  |       |

|                 |             |                                                                                                                          | 16 MHz                                       | 2.38  |       |

|                 |             |                                                                                                                          | 24 MHz                                       | 3.99  |       |

|                 |             |                                                                                                                          | 4 MHz                                        | 0.64  |       |

|                 |             | $V_{\text{DDIOx}} = 3.3 \text{ V}$                                                                                       | 8 MHz                                        | 1.25  |       |

|                 |             | $C_{EXT}$ = 33 pF<br>C = C <sub>INT</sub> + C <sub>EXT</sub> + C <sub>S</sub>                                            | 16 MHz                                       | 3.24  |       |

|                 |             |                                                                                                                          | 24 MHz                                       | 5.02  |       |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                                                               | 4 MHz                                        | 0.81  |       |

|                 |             | C <sub>EXT</sub> = 47 pF                                                                                                 | 8 MHz                                        | 1.7   |       |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$ $C = C_{int}$                                                                              | 16 MHz                                       | 3.67  |       |

|                 |             | V <sub>DDIOx</sub> = 2.4 V                                                                                               | 4 MHz                                        | 0.66  |       |

|                 |             | 0 <sub>DDIOx</sub> = 2.4 0<br>C <sub>EXT</sub> = 47 pF                                                                   | 8 MHz                                        | 1.43  | -     |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                                                                                          | 16 MHz                                       | 2.45  |       |

|                 |             | C = C <sub>int</sub>                                                                                                     | 24 MHz                                       | 4.97  |       |

Table 34. Switching output I/O current consumption

1. C<sub>S</sub> = 7 pF (estimated value).

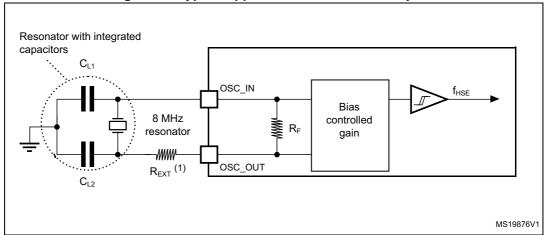

Figure 17. Typical application with an 8 MHz crystal

1.  $R_{EXT}$  value depends on the crystal characteristics.

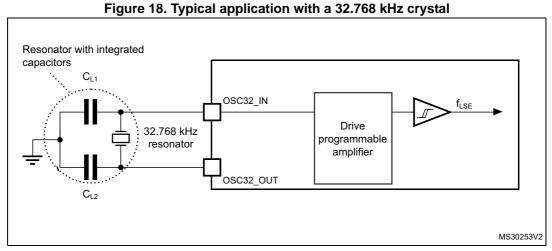

#### Low-speed external clock generated from a crystal resonator

The low-speed external (LSE) clock can be supplied with a 32.768 kHz crystal resonator oscillator. All the information given in this paragraph are based on design simulation results obtained with typical external components specified in *Table 40*. In the application, the resonator and the load capacitors have to be placed as close as possible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).

| Symbol                              | Parameter               | Conditions <sup>(1)</sup>        | Min <sup>(2)</sup> | Тур | Max <sup>(2)</sup> | Unit |

|-------------------------------------|-------------------------|----------------------------------|--------------------|-----|--------------------|------|

|                                     |                         | low drive capability             | -                  | 0.5 | 0.9                |      |

|                                     | LSE current consumption | medium-low drive capability      | -                  | -   | 1                  |      |

| IDD                                 |                         | medium-high drive capability     | -                  | -   | 1.3                | μA   |

|                                     |                         | high drive capability            | -                  | -   | 1.6                |      |

|                                     |                         | low drive capability             | 5                  | -   | -                  |      |

|                                     | Oscillator              | medium-low drive capability      | 8                  | -   | -                  |      |

| 9 <sub>m</sub>                      | transconductance        | medium-high drive capability     | 15                 | -   | -                  | µA/V |

|                                     |                         | high drive capability            | 25                 | -   | -                  |      |

| t <sub>SU(LSE)</sub> <sup>(3)</sup> | Startup time            | V <sub>DDIOx</sub> is stabilized | -                  | 2   | -                  | S    |

1. Refer to the note and caution paragraphs below the table, and to the application note AN2867 "Oscillator design guide for ST microcontrollers".

2. Guaranteed by design, not tested in production.

t<sub>SU(LSE)</sub> is the startup time measured from the moment it is enabled (by software) to a stabilized 32.768 kHz oscillation is reached. This value is measured for a standard crystal and it can vary significantly with the crystal manufacturer

*Note:* For information on selecting the crystal, refer to the application note AN2867 "Oscillator design guide for ST microcontrollers" available from the ST website <u>www.st.com</u>.

Note: An external resistor is not required between OSC32\_IN and OSC32\_OUT and it is forbidden to add one.

## 6.3.8 Internal clock source characteristics

The parameters given in *Table 41* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*. The provided curves are characterization results, not tested in production.

### Input/output AC characteristics

The definition and values of input/output AC characteristics are given in *Figure 24* and *Table 55*, respectively. Unless otherwise specified, the parameters given are derived from tests performed under the ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | Symbol                  | Parameter                        | Conditions                                         | Min                                                                                                                                                                                                 | Max  | Unit |  |

|----------------------------------------|-------------------------|----------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|--|

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                    | -                                                                                                                                                                                                   | 2    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2 \text{ V}$   | -                                                                                                                                                                                                   | 125  | ns   |  |

| vO                                     | t <sub>r(IO)out</sub>   | Output rise time                 |                                                    | -                                                                                                                                                                                                   | 125  | 115  |  |

| ×0                                     | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                    | -                                                                                                                                                                                                   | 1    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -                                                                                                                                                                                                   | 125  | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                    | -                                                                                                                                                                                                   | 125  | 115  |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                    | -                                                                                                                                                                                                   | 10   | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2 V$                 | -                                                                                                                                                                                                   | 25   | ns   |  |

| OSPEEDRy<br>[1:0] value <sup>(1)</sup> | t <sub>r(IO)out</sub>   | Output rise time                 |                                                    | -                                                                                                                                                                                                   | 25   | 115  |  |

|                                        | f <sub>max(IO)out</sub> | Maximum frequency <sup>(3)</sup> |                                                    | -                                                                                                                                                                                                   | 4    | MHz  |  |

|                                        | t <sub>f(IO)out</sub>   | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -                                                                                                                                                                                                   | 62.5 | ns   |  |

|                                        | t <sub>r(IO)out</sub>   | Output rise time                 |                                                    | -    2      -    125      -    125      -    1      -    125      -    125      -    125      -    125      -    125      -    125      -    125      -    10      -    25      -    25      -    4 | 115  |      |  |

|                                        | f (o) (                 |                                  |                                                    | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$                                                                                                                                                                | -    | 50   |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$               | -                                                                                                                                                                                                   | 30   | MHz  |  |

|                                        | 'max(IO)out             |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -                                                                                                                                                                                                   | 20   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -                                                                                                                                                                                                   | 10   |      |  |

|                                        |                         |                                  | $C_L$ = 30 pF, $V_{DDIOx} \ge 2.7 V$               | -                                                                                                                                                                                                   | 5    |      |  |

| 11                                     | town                    | Output fall time                 | $C_L$ = 50 pF, $V_{DDIOx} \ge 2.7 V$               | -                                                                                                                                                                                                   | 8    |      |  |

|                                        | ۲f(IO)out               |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -                                                                                                                                                                                                   | 12   |      |  |

|                                        |                         |                                  | $C_L$ = 50 pF, $V_{DDIOx}$ < 2 V                   | -                                                                                                                                                                                                   | 25   | 1    |  |

|                                        |                         |                                  | $C_L = 30 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -                                                                                                                                                                                                   | 5    | ns   |  |

|                                        | ture                    | Output rise time                 | $C_L = 50 \text{ pF}, V_{DDIOx} \ge 2.7 \text{ V}$ | -                                                                                                                                                                                                   | 8    |      |  |

|                                        | t <sub>r(IO)out</sub>   |                                  | $C_L$ = 50 pF, 2 V ≤ $V_{DDIOx}$ < 2.7 V           | -                                                                                                                                                                                                   | 12   |      |  |

|                                        |                         |                                  | $C_L = 50 \text{ pF}, V_{DDIOx} < 2 \text{ V}$     | -                                                                                                                                                                                                   | 25   |      |  |

Table 55. I/O AC characteristics<sup>(1)(2)</sup>

# 6.3.17 DAC electrical specifications

| Iable 60. DAC characteristics    |                                                                                                              |     |     |                         |      |                                                                                                                                |  |  |  |

|----------------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|-------------------------|------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                           | Parameter                                                                                                    | Min | Тур | Мах                     | Unit | Comments                                                                                                                       |  |  |  |

| V <sub>DDA</sub>                 | Analog supply voltage for<br>DAC ON                                                                          | 2.4 | -   | 3.6                     | V    | -                                                                                                                              |  |  |  |

| R <sub>LOAD</sub> <sup>(1)</sup> | Resistive load with buffer                                                                                   | 5   | -   | -                       | kΩ   | Load connected to V <sub>SSA</sub>                                                                                             |  |  |  |

| LOAD '                           | ON                                                                                                           | 25  | -   | -                       | kΩ   | Load connected to V <sub>DDA</sub>                                                                                             |  |  |  |

| R <sub>O</sub> <sup>(1)</sup>    | Impedance output with<br>buffer OFF                                                                          | -   | -   | 15                      | kΩ   | When the buffer is OFF, the Minimum resistive load between DAC_OUT and V <sub>SS</sub> to have a 1% accuracy is 1.5 M $\Omega$ |  |  |  |

| C <sub>LOAD</sub> <sup>(1)</sup> | Capacitive load                                                                                              | -   | -   | 50                      | pF   | Maximum capacitive load at DAC_OUT pin (when the buffer is ON).                                                                |  |  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer ON                                                                         | 0.2 | -   | -                       | V    | It gives the maximum output<br>excursion of the DAC.<br>It corresponds to 12-bit input<br>code (0x0E0) to (0xF1C) at           |  |  |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer ON                                                                        | -   | -   | V <sub>DDA</sub> – 0.2  | V    | $V_{DDA} = 3.6 V \text{ and } (0x155) \text{ and}$<br>(0xEAB) at $V_{DDA} = 2.4 V$                                             |  |  |  |

| DAC_OUT<br>min <sup>(1)</sup>    | Lower DAC_OUT voltage with buffer OFF                                                                        | -   | 0.5 | -                       | mV   | It gives the maximum output                                                                                                    |  |  |  |

| DAC_OUT<br>max <sup>(1)</sup>    | Higher DAC_OUT voltage with buffer OFF                                                                       | -   | -   | V <sub>DDA</sub> – 1LSB | V    | excursion of the DAC.                                                                                                          |  |  |  |

| I <sub>DDA</sub> <sup>(1)</sup>  | DAC DC current<br>consumption in quiescent                                                                   | -   | -   | 600                     | μA   | With no load, middle code<br>(0x800) on the input                                                                              |  |  |  |

| 'DDA                             | mode <sup>(2)</sup>                                                                                          | -   | -   | 700                     | μA   | With no load, worst code<br>(0xF1C) on the input                                                                               |  |  |  |

| DNL <sup>(3)</sup>               | Differential non linearity<br>Difference between two                                                         | -   | -   | ±0.5                    | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |  |  |

|                                  | consecutive code-1LSB)                                                                                       | -   | -   | ±2                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |  |  |

|                                  | Integral non linearity<br>(difference between                                                                | -   | -   | ±1                      | LSB  | Given for the DAC in 10-bit configuration                                                                                      |  |  |  |

| INL <sup>(3)</sup>               | measured value at Code i<br>and the value at Code i on a<br>line drawn between Code 0<br>and last Code 1023) | -   | -   | ±4                      | LSB  | Given for the DAC in 12-bit configuration                                                                                      |  |  |  |

|                                  | Offset error                                                                                                 | -   | -   | ±10                     | mV   | -                                                                                                                              |  |  |  |

| Offset <sup>(3)</sup>            | (difference between<br>measured value at Code                                                                | -   | -   | ±3                      | LSB  | Given for the DAC in 10-bit at $V_{DDA}$ = 3.6 V                                                                               |  |  |  |

|                                  | (0x800) and the ideal value<br>= V <sub>DDA</sub> /2)                                                        | -   | -   | ±12                     | LSB  | Given for the DAC in 12-bit at<br>V <sub>DDA</sub> = 3.6 V                                                                     |  |  |  |

| Table   | 60. | DAC  | characteristics  |

|---------|-----|------|------------------|

| i albio |     | 0/10 | 0110100101101100 |

# 6.3.18 Comparator characteristics

| Symbol                   | Parameter                                                     | Conditi                                           | ons                      | Min <sup>(1)</sup> | Тур              | Max <sup>(1)</sup> | Unit  |

|--------------------------|---------------------------------------------------------------|---------------------------------------------------|--------------------------|--------------------|------------------|--------------------|-------|

| $V_{DDA}$                | Analog supply voltage                                         | -                                                 |                          |                    | -                | 3.6                | V     |

| V <sub>IN</sub>          | Comparator input voltage range                                | -                                                 | 0                        | -                  | V <sub>DDA</sub> | -                  |       |

| V <sub>SC</sub>          | V <sub>REFINT</sub> scaler offset voltage                     | -                                                 |                          | -                  | ±5               | ±10                | mV    |

| t <sub>s_sc</sub>        | V <sub>REFINT</sub> scaler startup<br>time from power down    | First V <sub>REFINT</sub> scaler acti<br>power on | vation after device      | -                  | -                | 1000<br>(2)        | ms    |

|                          |                                                               | Next activations                                  |                          | -                  | -                | 0.2                |       |

| t <sub>START</sub>       | Comparator startup time                                       | Startup time to reach pro specification           | opagation delay          | -                  | -                | 60                 | μs    |

|                          |                                                               | Ultra-low power mode                              |                          | -                  | 2                | 4.5                |       |

|                          | Propagation delay for<br>200 mV step with<br>100 mV overdrive | Low power mode                                    | -                        | 0.7                | 1.5              | μs                 |       |

|                          |                                                               | Medium power mode                                 | -                        | 0.3                | 0.6              |                    |       |

|                          |                                                               | High speed mode                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 50               | 100                | 20    |

| +                        |                                                               | nigh speed mode                                   | -                        | 100                | 240              | ns                 |       |

| t <sub>D</sub>           |                                                               | Ultra-low power mode                              | -                        | 2                  | 7                |                    |       |

|                          | Propagation delay for                                         | Low power mode                                    | -                        | 0.7                | 2.1              | μs                 |       |

|                          | full range step with                                          | Medium power mode                                 |                          | -                  | 0.3              | 1.2                |       |

|                          | 100 mV overdrive                                              | High speed mode                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 90               | 180                | ns    |

|                          |                                                               | nigh speed mode                                   | V <sub>DDA</sub> < 2.7 V | -                  | 110              | 300                | 115   |

| V <sub>offset</sub>      | Comparator offset error                                       | -                                                 |                          | -                  | ±4               | ±10                | mV    |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                          | -                                                 |                          | -                  | 18               | -                  | µV/°C |

|                          |                                                               | Ultra-low power mode                              |                          | -                  | 1.2              | 1.5                |       |

|                          | COMP current                                                  | Low power mode                                    |                          | -                  | 3                | 5                  |       |

| I <sub>DD(COMP)</sub>    | consumption                                                   | Medium power mode                                 |                          | -                  | 10               | 15                 | μA    |

|                          |                                                               | High speed mode                                   |                          | -                  | 75               | 100                |       |

#### Table 61. Comparator characteristics

| Tab               |              | min/max timeout periou         |                                |      |

|-------------------|--------------|--------------------------------|--------------------------------|------|

| Prescaler divider | PR[2:0] bits | Min timeout RL[11:0]=<br>0x000 | Max timeout RL[11:0]=<br>0xFFF | Unit |

| /4                | 0            | 0.1                            | 409.6                          |      |

| /8                | 1            | 0.2                            | 819.2                          |      |

| /16               | 2            | 0.4                            | 1638.4                         |      |

| /32               | 3            | 0.8                            | 3276.8                         | ms   |

| /64               | 4            | 1.6                            | 6553.6                         |      |

| /128              | 5            | 3.2                            | 13107.2                        |      |

| /256              | 6 or 7       | 6.4                            | 26214.4                        |      |

Table 65. IWDG min/max timeout period at 40 kHz (LSI)<sup>(1)</sup>

1. These timings are given for a 40 kHz clock but the microcontroller internal RC frequency can vary from 30 to 60 kHz. Moreover, given an exact RC oscillator frequency, the exact timings still depend on the phasing of the APB interface clock versus the LSI clock so that there is always a full RC period of uncertainty.

| Prescaler | WDGTB | Min timeout value | Max timeout value | Unit |

|-----------|-------|-------------------|-------------------|------|

| 1         | 0     | 0.0853            | 5.4613            |      |

| 2         | 1     | 0.1706            | 10.9226           | me   |

| 4         | 2     | 0.3413            | 21.8453           | ms   |

| 8         | 3     | 0.6826            | 43.6906           |      |

Table 66. WWDG min/max timeout value at 48 MHz (PCLK)

## 6.3.22 Communication interfaces

### I<sup>2</sup>C interface characteristics

The  $I^2C$  interface meets the timings requirements of the  $I^2C$ -bus specification and user manual rev. 03 for:

- Standard-mode (Sm): with a bit rate up to 100 kbit/s

- Fast-mode (Fm): with a bit rate up to 400 kbit/s

- Fast-mode Plus (Fm+): with a bit rate up to 1 Mbit/s.

The I<sup>2</sup>C timings requirements are guaranteed by design when the I2Cx peripheral is properly configured (refer to Reference manual).

The SDA and SCL I/O requirements are met with the following restrictions: the SDA and SCL I/O pins are not "true" open-drain. When configured as open-drain, the PMOS connected between the I/O pin and  $V_{DDIOx}$  is disabled, but is still present. Only FTf I/O pins support Fm+ low level output current maximum requirement. Refer to Section 6.3.14: I/O port characteristics for the I<sup>2</sup>C I/Os characteristics.

All I<sup>2</sup>C SDA and SCL I/Os embed an analog filter. Refer to the table below for the analog filter characteristics:

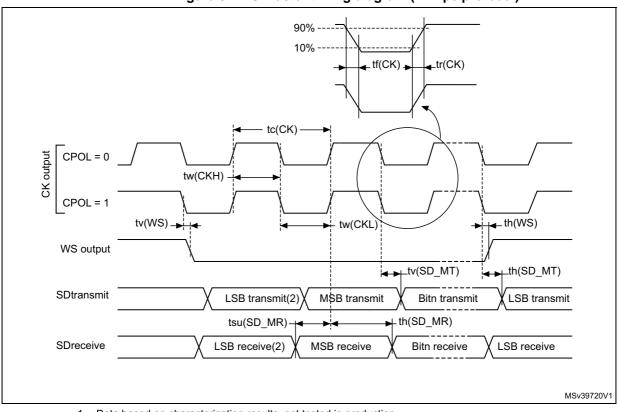

## Figure 34. I<sup>2</sup>S master timing diagram (Philips protocol)

- 1. Data based on characterization results, not tested in production.

- 2. LSB transmit/receive of the previously transmitted byte. No LSB transmit/receive is sent before the first byte.

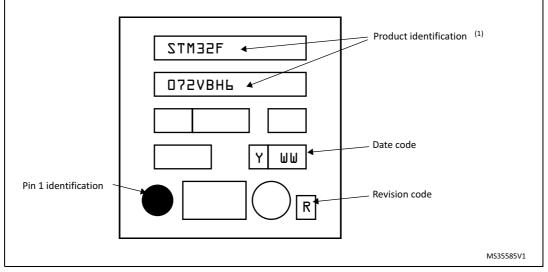

### **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Symbol | millimeters |        |        | inches <sup>(1)</sup> |        |        |

|--------|-------------|--------|--------|-----------------------|--------|--------|

|        | Min         | Тур    | Мах    | Min                   | Тур    | Max    |

| E1     | 13.800      | 14.000 | 14.200 | 0.5433                | 0.5512 | 0.5591 |

| E3     | -           | 12.000 | -      | -                     | 0.4724 | -      |

| е      | -           | 0.500  | -      | -                     | 0.0197 | -      |

| L      | 0.450       | 0.600  | 0.750  | 0.0177                | 0.0236 | 0.0295 |

| L1     | -           | 1.000  | -      | -                     | 0.0394 | -      |

| k      | 0.0°        | 3.5°   | 7.0°   | 0.0°                  | 3.5°   | 7.0°   |

| CCC    | -           | -      | 0.080  | -                     | -      | 0.0031 |

Table 73. LQPF100 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

1. Dimensions are expressed in millimeters.

| Symbol            | millimeters |        |       | inches <sup>(1)</sup> |        |        |

|-------------------|-------------|--------|-------|-----------------------|--------|--------|

|                   | Min         | Тур    | Мах   | Min                   | Тур    | Max    |

| А                 | 0.525       | 0.555  | 0.585 | 0.0207                | 0.0219 | 0.0230 |

| A1                | -           | 0.175  | -     | -                     | 0.0069 | -      |

| A2                | -           | 0.380  | -     | -                     | 0.0150 | -      |

| A3 <sup>(2)</sup> | -           | 0.025  | -     | -                     | 0.0010 | -      |

| b <sup>(3)</sup>  | 0.220       | 0.250  | 0.280 | 0.0087                | 0.0098 | 0.0110 |

| D                 | 3.242       | 3.277  | 3.312 | 0.1276                | 0.1290 | 0.1304 |

| Е                 | 3.074       | 3.109  | 3.144 | 0.1210                | 0.1224 | 0.1238 |

| е                 | -           | 0.400  | -     | -                     | 0.0157 | -      |

| e1                | -           | 2.400  | -     | -                     | 0.0945 | -      |

| e2                | -           | 2.400  | -     | -                     | 0.0945 | -      |

| F                 | -           | 0.4385 | -     | -                     | 0.0173 | -      |

| G                 | -           | 0.3545 | -     | -                     | 0.0140 | -      |

| aaa               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| bbb               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| CCC               | -           | -      | 0.100 | -                     | -      | 0.0039 |

| ddd               | -           | -      | 0.050 | -                     | -      | 0.0020 |

| eee               | -           | -      | 0.050 | -                     | -      | 0.0020 |

#### Table 77. WLCSP49 package mechanical data

1. Values in inches are converted from mm and rounded to 4 decimal digits.

2. Back side coating

3. Dimension is measured at the maximum bump diameter parallel to primary datum Z.

Each temperature range suffix corresponds to a specific guaranteed ambient temperature at maximum dissipation and, to a specific maximum junction temperature.

As applications do not commonly use the STM32F072x8/xB at maximum dissipation, it is useful to calculate the exact power consumption and junction temperature to determine which temperature range will be best suited to the application.

The following examples show how to calculate the temperature range needed for a given application.

#### **Example 1: High-performance application**

Assuming the following application conditions:

Maximum temperature  $T_{Amax}$  = 82 °C (measured according to JESD51-2),  $I_{DDmax}$  = 50 mA,  $V_{DD}$  = 3.5 V, maximum 20 I/Os used at the same time in output at low level with  $I_{OL}$  = 8 mA,  $V_{OL}$ = 0.4 V and maximum 8 I/Os used at the same time in output at low level with  $I_{OL}$  = 20 mA,  $V_{OL}$ = 1.3 V

P<sub>INTmax</sub> = 50 mA × 3.5 V= 175 mW

P<sub>IOmax</sub> = 20 × 8 mA × 0.4 V + 8 × 20 mA × 1.3 V = 272 mW

This gives:  $P_{INTmax}$  = 175 mW and  $P_{IOmax}$  = 272 mW:

P<sub>Dmax</sub>= 175 + 272 = 447 mW

Using the values obtained in *Table 80* T<sub>Jmax</sub> is calculated as follows:

- For LQFP64, 45 °C/W

T<sub>Jmax</sub> = 82 °C + (45 °C/W × 447 mW) = 82 °C + 20.115 °C = 102.115 °C

This is within the range of the suffix 6 version parts ( $-40 < T_J < 105 \text{ °C}$ ).