Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | ARM® Cortex®-M0                                                         |

| Core Size                  | 32-Bit Single-Core                                                      |

| Speed                      | 48MHz                                                                   |

| Connectivity               | CANbus, HDMI-CEC, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART, USB  |

| Peripherals                | DMA, I <sup>2</sup> S, POR, PWM, WDT                                    |

| Number of I/O              | 51                                                                      |

| Program Memory Size        | 128KB (128K x 8)                                                        |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                |                                                                         |

| RAM Size                   | 16K x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                            |

| Data Converters            | A/D 19x12b; D/A 1x12b                                                   |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                      |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 64-LQFP                                                                 |

| Supplier Device Package    | 64-LQFP (10x10)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/stm32f072rbt7tr |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Additionally, also the internal RC 48 MHz oscillator can be selected for system clock or PLL input source. This oscillator can be automatically fine-trimmed by the means of the CRS peripheral using the external synchronization.

# 3.7 General-purpose inputs/outputs (GPIOs)

Each of the GPIO pins can be configured by software as output (push-pull or open-drain), as input (with or without pull-up or pull-down) or as peripheral alternate function. Most of the GPIO pins are shared with digital or analog alternate functions.

The I/O configuration can be locked if needed following a specific sequence in order to avoid spurious writing to the I/Os registers.

# **3.8** Direct memory access controller (DMA)

The 7-channel general-purpose DMAs manage memory-to-memory, peripheral-to-memory and memory-to-peripheral transfers.

The DMA supports circular buffer management, removing the need for user code intervention when the controller reaches the end of the buffer.

Each channel is connected to dedicated hardware DMA requests, with support for software trigger on each channel. Configuration is made by software and transfer sizes between source and destination are independent.

DMA can be used with the main peripherals: SPIx, I2Sx, I2Cx, USARTx, all TIMx timers (except TIM14), DAC and ADC.

# 3.9 Interrupts and events

#### 3.9.1 Nested vectored interrupt controller (NVIC)

The STM32F0xx family embeds a nested vectored interrupt controller able to handle up to 32 maskable interrupt channels (not including the 16 interrupt lines of  $Cortex^{\mathbb{R}}$ -M0) and 4 priority levels.

- Closely coupled NVIC gives low latency interrupt processing

- Interrupt entry vector table address passed directly to the core

- Closely coupled NVIC core interface

- Allows early processing of interrupts

- Processing of late arriving higher priority interrupts

- Support for tail-chaining

- Processor state automatically saved

- Interrupt entry restored on interrupt exit with no instruction overhead

This hardware block provides flexible interrupt management features with minimal interrupt latency.

# 3.9.2 Extended interrupt/event controller (EXTI)

The extended interrupt/event controller consists of 32 edge detector lines used to generate interrupt/event requests and wake-up the system. Each line can be independently configured to select the trigger event (rising edge, falling edge, both) and can be masked independently. A pending register maintains the status of the interrupt requests. The EXTI can detect an external line with a pulse width shorter than the internal clock period. Up to 87 GPIOs can be connected to the 16 external interrupt lines.

# 3.10 Analog-to-digital converter (ADC)

The 12-bit analog-to-digital converter has up to 16 external and 3 internal (temperature sensor, voltage reference, VBAT voltage measurement) channels and performs conversions in single-shot or scan modes. In scan mode, automatic conversion is performed on a selected group of analog inputs.

The ADC can be served by the DMA controller.

An analog watchdog feature allows very precise monitoring of the converted voltage of one, some or all selected channels. An interrupt is generated when the converted voltage is outside the programmed thresholds.

# 3.10.1 Temperature sensor

The temperature sensor (TS) generates a voltage  $V_{\mbox{\scriptsize SENSE}}$  that varies linearly with temperature.

The temperature sensor is internally connected to the ADC\_IN16 input channel which is used to convert the sensor output voltage into a digital value.

The sensor provides good linearity but it has to be calibrated to obtain good overall accuracy of the temperature measurement. As the offset of the temperature sensor varies from chip to chip due to process variation, the uncalibrated internal temperature sensor is suitable for applications that detect temperature changes only.

To improve the accuracy of the temperature sensor measurement, each device is individually factory-calibrated by ST. The temperature sensor factory calibration data are stored by ST in the system memory area, accessible in read-only mode.

| Calibration value name | Description                                                                                                          | Memory address            |

|------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------|

| TS_CAL1                | TS ADC raw data acquired at a temperature of 30 °C ( $\pm$ 5 °C), V <sub>DDA</sub> = 3.3 V ( $\pm$ 10 mV)            | 0x1FFF F7B8 - 0x1FFF F7B9 |

| TS_CAL2                | TS ADC raw data acquired at a temperature of 110 $^{\circ}$ C (± 5 $^{\circ}$ C), V <sub>DDA</sub> = 3.3 V (± 10 mV) | 0x1FFF F7C2 - 0x1FFF F7C3 |

Table 3. Temperature sensor calibration values

# 3.10.2 Internal voltage reference (V<sub>REFINT</sub>)

The internal voltage reference ( $V_{REFINT}$ ) provides a stable (bandgap) voltage output for the ADC and comparators.  $V_{REFINT}$  is internally connected to the ADC\_IN17 input channel. The

verifications and ALERT protocol management. I2C1 also has a clock domain independent from the CPU clock, allowing the I2C1 to wake up the MCU from Stop mode on address match.

The I2C peripherals can be served by the DMA controller.

Refer to *Table 9* for the differences between I2C1 and I2C2.

| Table 9. STM32F072x8/xB | I <sup>2</sup> C implementation |

|-------------------------|---------------------------------|

|-------------------------|---------------------------------|

| I <sup>2</sup> C features <sup>(1)</sup>                     | I2C1 | I2C2 |

|--------------------------------------------------------------|------|------|

| 7-bit addressing mode                                        | Х    | Х    |

| 10-bit addressing mode                                       | Х    | Х    |

| Standard mode (up to 100 kbit/s)                             | Х    | Х    |

| Fast mode (up to 400 kbit/s)                                 | Х    | Х    |

| Fast Mode Plus (up to 1 Mbit/s) with 20 mA output drive I/Os | Х    | Х    |

| Independent clock                                            | Х    | -    |

| SMBus                                                        | Х    | -    |

| Wakeup from STOP                                             | Х    | -    |

1. X = supported.

# 3.17 Universal synchronous/asynchronous receiver/transmitter (USART)

The device embeds four universal synchronous/asynchronous receivers/transmitters (USART1, USART2, USART3, USART4) which communicate at speeds of up to 6 Mbit/s.

They provide hardware management of the CTS, RTS and RS485 DE signals, multiprocessor communication mode, master synchronous communication and single-wire half-duplex communication mode. USART1 and USART2 support also SmartCard communication (ISO 7816), IrDA SIR ENDEC, LIN Master/Slave capability and auto baud rate feature, and have a clock domain independent of the CPU clock, allowing to wake up the MCU from Stop mode.

The USART interfaces can be served by the DMA controller.

| USART modes/features <sup>(1)</sup>   | USART1 and<br>USART2 | USART3 and<br>USART4 |

|---------------------------------------|----------------------|----------------------|

| Hardware flow control for modem       | Х                    | Х                    |

| Continuous communication using DMA    | Х                    | Х                    |

| Multiprocessor communication          | Х                    | х                    |

| Synchronous mode                      | Х                    | Х                    |

| Smartcard mode                        | Х                    | -                    |

| Single-wire half-duplex communication | Х                    | Х                    |

# 4 Pinouts and pin descriptions

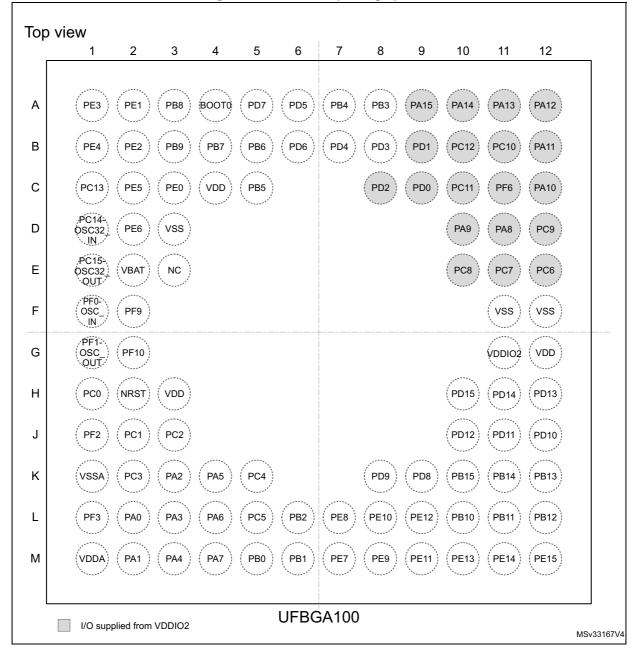

## Figure 3. UFBGA100 package pinout

DocID025004 Rev 5

|          | Р       | 'in nu  | mber   |                 |         | 5. 01111521 072.0                    | -           |               |       | Pin functions                                                      |                         |

|----------|---------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|--------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                | Additional<br>functions |

| K5       | 33      | H5      | 24     | -               | -       | PC4                                  | I/O         | TTa           | -     | EVENTOUT,<br>USART3_TX                                             | ADC_IN14                |

| L5       | 34      | H6      | 25     | -               | -       | PC5                                  | I/O         | ТТа           | -     | TSC_G3_IO1,<br>USART3_RX                                           | ADC_IN15,<br>WKUP5      |

| M5       | 35      | F5      | 26     | 18              | G5      | PB0                                  | I/O         | ТТа           | -     | TIM3_CH3, TIM1_CH2N,<br>TSC_G3_IO2,<br>EVENTOUT,<br>USART3_CK      | ADC_IN8                 |

| M6       | 36      | G5      | 27     | 19              | G4      | PB1                                  | I/O         | ТТа           | -     | TIM3_CH4,<br>USART3_RTS,<br>TIM14_CH1,<br>TIM1_CH3N,<br>TSC_G3_IO3 | ADC_IN9                 |

| L6       | 37      | G6      | 28     | 20              | G3      | PB2                                  | I/O         | FT            | -     | TSC_G3_IO4                                                         | -                       |

| M7       | 38      | -       | -      | -               | -       | PE7                                  | I/O         | FT            | -     | TIM1_ETR                                                           | -                       |

| L7       | 39      | -       | -      | -               | -       | PE8                                  | I/O         | FT            | -     | TIM1_CH1N                                                          | -                       |

| M8       | 40      | -       | -      | -               | -       | PE9                                  | I/O         | FT            | -     | TIM1_CH1                                                           | -                       |

| L8       | 41      | -       | -      | -               | -       | PE10                                 | I/O         | FT            | -     | TIM1_CH2N                                                          | -                       |

| M9       | 42      | -       | -      | -               | -       | PE11                                 | I/O         | FT            | -     | TIM1_CH2                                                           | -                       |

| L9       | 43      | -       | -      | -               | -       | PE12                                 | I/O         | FT            | -     | SPI1_NSS, I2S1_WS,<br>TIM1_CH3N                                    | -                       |

| M10      | 44      | -       | -      | -               | -       | PE13                                 | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM1_CH3                                     | -                       |

| M11      | 45      | -       | -      | -               | -       | PE14                                 | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM1_CH4                                   | -                       |

| M12      | 46      | -       | -      | -               | -       | PE15                                 | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>TIM1_BKIN                                   | -                       |

| L10      | 47      | G7      | 29     | 21              | E3      | PB10                                 | I/O         | FT            | -     | SPI2_SCK, I2C2_SCL,<br>USART3_TX, CEC,<br>TSC_SYNC, TIM2_CH3       | -                       |

| L11      | 48      | H7      | 30     | 22              | G2      | PB11                                 | I/O         | FT            | -     | USART3_RX,<br>TIM2_CH4,<br>EVENTOUT,<br>TSC_G6_IO1,<br>I2C2_SDA    | -                       |

| F12      | 49      | D5      | 31     | 23              | D3      | VSS                                  | S           | -             | -     | Ground                                                             |                         |

Table 13. STM32F072x8/xB pin definitions (continued)

|          | Ρ       | 'in nu  | mber   | s               |         |                                      |             |               |       | Pin functions                                                               |                         |

|----------|---------|---------|--------|-----------------|---------|--------------------------------------|-------------|---------------|-------|-----------------------------------------------------------------------------|-------------------------|

| UFBGA100 | LQFP100 | UFBGA64 | LQFP64 | LQFP48/UFQFPN48 | WLCSP49 | Pin name<br>(function upon<br>reset) | Pin<br>type | I/O structure | Notes | Alternate functions                                                         | Additional<br>functions |

| C10      | 79      | B6      | 52     | -               | -       | PC11                                 | I/O         | FT            | (3)   | USART3_RX,<br>USART4_RX                                                     | -                       |

| B10      | 80      | C5      | 53     | -               | -       | PC12                                 | I/O         | FT            | (3)   | USART3_CK,<br>USART4_CK                                                     | -                       |

| C9       | 81      | -       | -      | -               | -       | PD0                                  | I/O         | FT            | (3)   | SPI2_NSS, I2S2_WS,<br>CAN_RX                                                | -                       |

| В9       | 82      | -       | -      | -               | -       | PD1                                  | I/O         | FT            | (3)   | SPI2_SCK, I2S2_CK,<br>CAN_TX                                                | -                       |

| C8       | 83      | B5      | 54     | -               | -       | PD2                                  | I/O         | FT            | (3)   | USART3_RTS,<br>TIM3_ETR                                                     | -                       |

| B8       | 84      | -       | -      | -               | -       | PD3                                  | I/O         | FT            | -     | SPI2_MISO, I2S2_MCK,<br>USART2_CTS                                          | -                       |

| B7       | 85      | -       | -      | -               | -       | PD4                                  | I/O         | FT            | -     | SPI2_MOSI, I2S2_SD,<br>USART2_RTS                                           | -                       |

| A6       | 86      | -       | -      | -               | -       | PD5                                  | I/O         | FT            | -     | USART2_TX                                                                   | -                       |

| B6       | 87      | -       | -      | -               | -       | PD6                                  | I/O         | FT            | -     | USART2_RX                                                                   | -                       |

| A5       | 88      | -       | -      | -               | -       | PD7                                  | I/O         | FT            | -     | USART2_CK                                                                   | -                       |

| A8       | 89      | A5      | 55     | 39              | A3      | PB3                                  | I/O         | FT            | -     | SPI1_SCK, I2S1_CK,<br>TIM2_CH2,<br>TSC_G5_IO1,<br>EVENTOUT                  | -                       |

| A7       | 90      | A4      | 56     | 40              | A4      | PB4                                  | I/O         | FT            | -     | SPI1_MISO, I2S1_MCK,<br>TIM17_BKIN,<br>TIM3_CH1,<br>TSC_G5_IO2,<br>EVENTOUT | -                       |

| C5       | 91      | C4      | 57     | 41              | B4      | PB5                                  | I/O         | FT            | -     | SPI1_MOSI, I2S1_SD,<br>I2C1_SMBA,<br>TIM16_BKIN,<br>TIM3_CH2                | WKUP6                   |

| B5       | 92      | D3      | 58     | 42              | C4      | PB6                                  | I/O         | FTf           | -     | I2C1_SCL, USART1_TX,<br>TIM16_CH1N,<br>TSC_G5_I03                           | -                       |

Table 13. STM32F072x8/xB pin definitions (continued)

| Bus  | Boundary address          | Size    | Peripheral             |

|------|---------------------------|---------|------------------------|

|      | 0x4800 1800 - 0x5FFF FFFF | ~384 MB | Reserved               |

|      | 0x4800 1400 - 0x4800 17FF | 1 KB    | GPIOF                  |

|      | 0x4800 1000 - 0x4800 13FF | 1 KB    | GPIOE                  |

| AHB2 | 0x4800 0C00 - 0x4800 0FFF | 1 KB    | GPIOD                  |

| ANDZ | 0x4800 0800 - 0x4800 0BFF | 1 KB    | GPIOC                  |

|      | 0x4800 0400 - 0x4800 07FF | 1 KB    | GPIOB                  |

|      | 0x4800 0000 - 0x4800 03FF | 1 KB    | GPIOA                  |

|      | 0x4002 4400 - 0x47FF FFFF | ~128 MB | Reserved               |

|      | 0x4002 4000 - 0x4002 43FF | 1 KB    | TSC                    |

|      | 0x4002 3400 - 0x4002 3FFF | 3 KB    | Reserved               |

|      | 0x4002 3000 - 0x4002 33FF | 1 KB    | CRC                    |

|      | 0x4002 2400 - 0x4002 2FFF | 3 KB    | Reserved               |

| AHB1 | 0x4002 2000 - 0x4002 23FF | 1 KB    | Flash memory interface |

|      | 0x4002 1400 - 0x4002 1FFF | 3 KB    | Reserved               |

|      | 0x4002 1000 - 0x4002 13FF | 1 KB    | RCC                    |

|      | 0x4002 0400 - 0x4002 0FFF | 3 KB    | Reserved               |

|      | 0x4002 0000 - 0x4002 03FF | 1 KB    | DMA                    |

|      | 0x4001 8000 - 0x4001 FFFF | 32 KB   | Reserved               |

|      | 0x4001 5C00 - 0x4001 7FFF | 9 KB    | Reserved               |

|      | 0x4001 5800 - 0x4001 5BFF | 1 KB    | DBGMCU                 |

|      | 0x4001 4C00 - 0x4001 57FF | 3 KB    | Reserved               |

|      | 0x4001 4800 - 0x4001 4BFF | 1 KB    | TIM17                  |

|      | 0x4001 4400 - 0x4001 47FF | 1 KB    | TIM16                  |

|      | 0x4001 4000 - 0x4001 43FF | 1 KB    | TIM15                  |

|      | 0x4001 3C00 - 0x4001 3FFF | 1 KB    | Reserved               |

|      | 0x4001 3800 - 0x4001 3BFF | 1 KB    | USART1                 |

|      | 0x4001 3400 - 0x4001 37FF | 1 KB    | Reserved               |

|      | 0x4001 3000 - 0x4001 33FF | 1 KB    | SPI1/I2S1              |

| APB  | 0x4001 2C00 - 0x4001 2FFF | 1 KB    | TIM1                   |

|      | 0x4001 2800 - 0x4001 2BFF | 1 KB    | Reserved               |

|      | 0x4001 2400 - 0x4001 27FF | 1 KB    | ADC                    |

|      | 0x4001 0800 - 0x4001 23FF | 7 KB    | Reserved               |

|      | 0x4001 0400 - 0x4001 07FF | 1 KB    | EXTI                   |

|      | 0x4001 0000 - 0x4001 03FF | 1 KB    | SYSCFG + COMP          |

|      | 0x4000 8000 - 0x4000 FFFF | 32 KB   | Reserved               |

# Table 20. STM32F072x8/xB peripheral register boundary addresses

DocID025004 Rev 5

| Bus | Boundary address          | Size | Peripheral  |

|-----|---------------------------|------|-------------|

|     | 0x4000 7C00 - 0x4000 7FFF | 1 KB | Reserved    |

|     | 0x4000 7800 - 0x4000 7BFF | 1 KB | CEC         |

|     | 0x4000 7400 - 0x4000 77FF | 1 KB | DAC         |

|     | 0x4000 7000 - 0x4000 73FF | 1 KB | PWR         |

|     | 0x4000 6C00 - 0x4000 6FFF | 1 KB | CRS         |

|     | 0x4000 6800 - 0x4000 6BFF | 1 KB | Reserved    |

|     | 0x4000 6400 - 0x4000 67FF | 1 KB | BxCAN       |

|     | 0x4000 6000 - 0x4000 63FF | 1 KB | USB/CAN RAM |

|     | 0x4000 5C00 - 0x4000 5FFF | 1 KB | USB         |

|     | 0x4000 5800 - 0x4000 5BFF | 1 KB | I2C2        |

|     | 0x4000 5400 - 0x4000 57FF | 1 KB | I2C1        |

|     | 0x4000 5000 - 0x4000 53FF | 1 KB | Reserved    |

|     | 0x4000 4C00 - 0x4000 4FFF | 1 KB | USART4      |

|     | 0x4000 4800 - 0x4000 4BFF | 1 KB | USART3      |

|     | 0x4000 4400 - 0x4000 47FF | 1 KB | USART2      |

|     | 0x4000 3C00 - 0x4000 43FF | 2 KB | Reserved    |

|     | 0x4000 3800 - 0x4000 3BFF | 1 KB | SPI2        |

| APB | 0x4000 3400 - 0x4000 37FF | 1 KB | Reserved    |

|     | 0x4000 3000 - 0x4000 33FF | 1 KB | IWDG        |

|     | 0x4000 2C00 - 0x4000 2FFF | 1 KB | WWDG        |

|     | 0x4000 2800 - 0x4000 2BFF | 1 KB | RTC         |

|     | 0x4000 2400 - 0x4000 27FF | 1 KB | Reserved    |

|     | 0x4000 2000 - 0x4000 23FF | 1 KB | TIM14       |

|     | 0x4000 1800 - 0x4000 1FFF | 2 KB | Reserved    |

|     | 0x4000 1400 - 0x4000 17FF | 1 KB | TIM7        |

|     | 0x4000 1000 - 0x4000 13FF | 1 KB | TIM6        |

|     | 0x4000 0800 - 0x4000 0FFF | 2 KB | Reserved    |

|     | 0x4000 0400 - 0x4000 07FF | 1 KB | TIM3        |

|     | 0x4000 0000 - 0x4000 03FF | 1 KB | TIM2        |

Table 20. STM32F072x8/xB peripheral register boundary addresses (continued)

| Symbol                               | Ratings                                                                         | Max.                 | Unit |

|--------------------------------------|---------------------------------------------------------------------------------|----------------------|------|

| $\Sigma I_{VDD}$                     | Total current into sum of all VDD power lines (source) <sup>(1)</sup>           | 120                  |      |

| ΣI <sub>VSS</sub>                    | Total current out of sum of all VSS ground lines (sink) <sup>(1)</sup>          | -120                 |      |

| I <sub>VDD(PIN)</sub>                | Maximum current into each VDD power pin (source) <sup>(1)</sup>                 | 100                  |      |

| I <sub>VSS(PIN)</sub>                | Maximum current out of each VSS ground pin (sink) <sup>(1)</sup>                | -100                 |      |

|                                      | Output current sunk by any I/O and control pin                                  | 25                   |      |

| I <sub>IO(PIN)</sub>                 | Output current source by any I/O and control pin                                | -25                  |      |

|                                      | Total output current sunk by sum of all I/Os and control pins <sup>(2)</sup>    | 80                   |      |

| ΣΙ <sub>ΙΟ(ΡΙΝ)</sub>                | Total output current sourced by sum of all I/Os and control pins <sup>(2)</sup> | -80                  | mA   |

|                                      | Total output current sourced by sum of all I/Os supplied by VDDIO2              | -40                  |      |

|                                      | Injected current on B, FT and FTf pins                                          | -5/+0 <sup>(4)</sup> |      |

| I <sub>INJ(PIN)</sub> <sup>(3)</sup> | Injected current on TC and RST pin                                              | ± 5                  |      |

|                                      | Injected current on TTa pins <sup>(5)</sup>                                     | ± 5                  |      |

| ΣΙ <sub>INJ(PIN)</sub>               | Total injected current (sum of all I/O and control pins) <sup>(6)</sup>         | ± 25                 |      |

#### Table 22. Current characteristics

1. All main power (VDD, VDDA) and ground (VSS, VSSA) pins must always be connected to the external power supply, in the permitted range.

2. This current consumption must be correctly distributed over all I/Os and control pins. The total output current must not be sunk/sourced between two consecutive power supply pins referring to high pin count QFP packages.

A positive injection is induced by V<sub>IN</sub> > V<sub>DDIOx</sub> while a negative injection is induced by V<sub>IN</sub> < V<sub>SS</sub>. I<sub>INJ(PIN)</sub> must never be exceeded. Refer to *Table 21: Voltage characteristics* for the maximum allowed input voltage values.

4. Positive injection is not possible on these I/Os and does not occur for input voltages lower than the specified maximum value.

5. On these I/Os, a positive injection is induced by  $V_{IN} > V_{DDA}$ . Negative injection disturbs the analog performance of the device. See note <sup>(2)</sup> below *Table 59: ADC accuracy*.

6. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values).

#### Table 23. Thermal characteristics

| Symbol           | Ratings                      | Value       | Unit |

|------------------|------------------------------|-------------|------|

| T <sub>STG</sub> | Storage temperature range    | –65 to +150 | °C   |

| Т <sub>Ј</sub>   | Maximum junction temperature | 150         | °C   |

| Symbol           | Parameter                       | 6                 |                        | sumption in<br>node     |                        | sumption in mode        | Unit |

|------------------|---------------------------------|-------------------|------------------------|-------------------------|------------------------|-------------------------|------|

| Symbol           | Falanetei                       | <sup>f</sup> нсLк | Peripherals<br>enabled | Peripherals<br>disabled | Peripherals<br>enabled | Peripherals<br>disabled | Onit |

|                  |                                 | 48 MHz            | 24.1                   | 13.5                    | 14.6                   | 3.5                     |      |

|                  |                                 | 36 MHz            | 18.3                   | 10.5                    | 11.1                   | 2.9                     |      |

|                  |                                 | 32 MHz            | 16.5                   | 9.6                     | 10.0                   | 2.7                     |      |

|                  | Current                         | 24 MHz            | 12.9                   | 7.6                     | 7.8                    | 2.2                     |      |

|                  | consumption                     | 16 MHz            | 8.9                    | 5.3                     | 5.5                    | 1.7                     | mA   |

| I <sub>DD</sub>  | from V <sub>DD</sub><br>supply  | 8 MHz             | 4.8                    | 3.1                     | 3.1                    | 1.2                     | mA   |

|                  | Supply                          | 4 MHz             | 3.1                    | 2.1                     | 2.2                    | 1.1                     |      |

|                  |                                 | 2 MHz             | 2.1                    | 1.6                     | 1.6                    | 1.0                     |      |

|                  |                                 | 1 MHz             | 1.6                    | 1.3                     | 1.4                    | 1.0                     |      |

|                  |                                 | 500 kHz           | 1.3                    | 1.2                     | 1.2                    | 1.0                     |      |

|                  |                                 | 48 MHz            |                        | 16                      | 3.3                    |                         |      |

|                  |                                 | 36 MHz            |                        | 12                      | 4.3                    |                         |      |

|                  |                                 | 32 MHz            |                        | 11                      | 1.9                    |                         |      |

|                  | Current                         | 24 MHz            | 87.1                   |                         |                        |                         |      |

| I                | consumption                     | 16 MHz            |                        | 62                      | 2.5                    |                         | uА   |

| I <sub>DDA</sub> | from V <sub>DDA</sub><br>supply | 8 MHz             |                        | 2                       | .5                     |                         | μA   |

|                  | Suppry                          | 4 MHz             |                        | 2                       | .5                     |                         |      |

|                  |                                 | 2 MHz             |                        | 2                       | .5                     |                         |      |

|                  |                                 | 1 MHz             |                        | 2                       | .5                     |                         |      |

|                  |                                 | 500 kHz           |                        | 2                       | .5                     |                         |      |

#### Table 33. Typical current consumption, code executing from Flash memory, running from HSE 8 MHz crystal

# I/O system current consumption

The current consumption of the I/O system has two components: static and dynamic.

#### I/O static current consumption

All the I/Os used as inputs with pull-up generate current consumption when the pin is externally held low. The value of this current consumption can be simply computed by using the pull-up/pull-down resistors values given in *Table 53: I/O static characteristics*.

For the output pins, any external pull-down or external load must also be considered to estimate the current consumption.

Additional I/O current consumption is due to I/Os configured as inputs if an intermediate voltage level is externally applied. This current consumption is caused by the input Schmitt

## STM32F072x8 STM32F072xB

| Symbol          | Parameter   | Conditions <sup>(1)</sup>                                                     | I/O toggling<br>frequency (f <sub>SW</sub> ) | Тур   | Unit |

|-----------------|-------------|-------------------------------------------------------------------------------|----------------------------------------------|-------|------|

|                 |             |                                                                               | 4 MHz                                        | 0.07  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                    | 8 MHz                                        | 0.15  |      |

|                 |             | C =C <sub>INT</sub>                                                           | 16 MHz                                       | 0.31  |      |

|                 |             |                                                                               | 24 MHz                                       | 0.53  |      |

|                 |             |                                                                               | 48 MHz                                       | 0.92  | 1    |

|                 |             |                                                                               | 4 MHz                                        | 0.18  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                    | 8 MHz                                        | 0.37  |      |

|                 |             | C <sub>EXT</sub> = 0 pF                                                       | 16 MHz                                       | 0.76  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$                                                 | 24 MHz                                       | 1.39  |      |

|                 |             |                                                                               | 48 MHz                                       | 2.188 |      |

|                 |             |                                                                               | 4 MHz                                        | 0.32  | - mA |

|                 |             | $V_{DDIOx} = 3.3 V$<br>$C_{EXT} = 10 pF$<br>$C = C_{INT} + C_{EXT} + C_S$     | 8 MHz                                        | 0.64  |      |

|                 | I/O current |                                                                               | 16 MHz                                       | 1.25  |      |

|                 |             |                                                                               | 24 MHz                                       | 2.23  |      |

| I <sub>SW</sub> |             |                                                                               | 48 MHz                                       | 4.442 |      |

| ISW             | consumption | $V_{DDIOx} = 3.3 V$ $C_{EXT} = 22 pF$ $C = C_{INT} + C_{EXT} + C_{S}$         | 4 MHz                                        | 0.49  |      |

|                 |             |                                                                               | 8 MHz                                        | 0.94  |      |

|                 |             |                                                                               | 16 MHz                                       | 2.38  |      |

|                 |             |                                                                               | 24 MHz                                       | 3.99  |      |

|                 |             |                                                                               | 4 MHz                                        | 0.64  |      |

|                 |             | $V_{DDIOx} = 3.3 V$                                                           | 8 MHz                                        | 1.25  |      |

|                 |             | $C_{EXT}$ = 33 pF<br>C = C <sub>INT</sub> + C <sub>EXT</sub> + C <sub>S</sub> | 16 MHz                                       | 3.24  |      |

|                 |             |                                                                               | 24 MHz                                       | 5.02  |      |

|                 |             | V <sub>DDIOx</sub> = 3.3 V                                                    | 4 MHz                                        | 0.81  |      |

|                 |             | C <sub>EXT</sub> = 47 pF                                                      | 8 MHz                                        | 1.7   |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_S$ $C = C_{int}$                                   | 16 MHz                                       | 3.67  |      |

|                 |             | V <sub>DDIOx</sub> = 2.4 V                                                    | 4 MHz                                        | 0.66  |      |

|                 |             | 0 <sub>DDIOx</sub> = 2.4 0<br>C <sub>EXT</sub> = 47 pF                        | 8 MHz                                        | 1.43  |      |

|                 |             | $C = C_{INT} + C_{EXT} + C_{S}$                                               | 16 MHz                                       | 2.45  |      |

|                 |             | C = C <sub>int</sub>                                                          | 24 MHz                                       | 4.97  |      |

Table 34. Switching output I/O current consumption

1. C<sub>S</sub> = 7 pF (estimated value).

# **On-chip peripheral current consumption**

The current consumption of the on-chip peripherals is given in *Table 35*. The MCU is placed under the following conditions:

- All I/O pins are in analog mode

- All peripherals are disabled unless otherwise mentioned

- The given value is calculated by measuring the current consumption

- with all peripherals clocked off

- with only one peripheral clocked on

- Ambient operating temperature and supply voltage conditions summarized in *Table 21: Voltage characteristics*

- The power consumption of the digital part of the on-chip peripherals is given in *Table 35.* The power consumption of the analog part of the peripherals (where applicable) is indicated in each related section of the datasheet.

|     | Peripheral               | Typical consumption at 25 °C | Unit   |

|-----|--------------------------|------------------------------|--------|

|     | BusMatrix <sup>(1)</sup> | 2.2                          |        |

|     | CRC                      | 1.6                          |        |

|     | DMA                      | 5.7                          |        |

|     | Flash memory interface   | 13.0                         |        |

|     | GPIOA                    | 8.2                          |        |

|     | GPIOB                    | 8.5                          |        |

| AHB | GPIOC                    | 2.3                          | µA/MHz |

|     | GPIOD                    | 1.9                          |        |

|     | GPIOE                    | 2.2                          |        |

|     | GPIOF                    | 1.2                          |        |

|     | SRAM                     | 0.9                          |        |

|     | TSC                      | 5.0                          |        |

|     | All AHB peripherals      | 52.6                         |        |

#### Table 35. Peripheral current consumption

# Low-speed internal (LSI) RC oscillator

| Symbol                               | Parameter                        | Min | Тур  | Max | Unit |

|--------------------------------------|----------------------------------|-----|------|-----|------|

| f <sub>LSI</sub>                     | Frequency                        | 30  | 40   | 50  | kHz  |

| t <sub>su(LSI)</sub> <sup>(2)</sup>  | LSI oscillator startup time      | -   | -    | 85  | μs   |

| I <sub>DDA(LSI)</sub> <sup>(2)</sup> | LSI oscillator power consumption | -   | 0.75 | 1.2 | μA   |

1. V<sub>DDA</sub> = 3.3 V, T<sub>A</sub> = –40 to 105  $^\circ\text{C}$  unless otherwise specified.

2. Guaranteed by design, not tested in production.

# 6.3.9 PLL characteristics

The parameters given in *Table 45* are derived from tests performed under ambient temperature and supply voltage conditions summarized in *Table 24: General operating conditions*.

| Symbol                | Parameter                      |                   | Value |                    |      |  |

|-----------------------|--------------------------------|-------------------|-------|--------------------|------|--|

| Symbol                | Falameter                      | Min               | Тур   | Max                | Unit |  |

| f                     | PLL input clock <sup>(1)</sup> | 1 <sup>(2)</sup>  | 8.0   | 24 <sup>(2)</sup>  | MHz  |  |

| f <sub>PLL_IN</sub>   | PLL input clock duty cycle     | 40 <sup>(2)</sup> | -     | 60 <sup>(2)</sup>  | %    |  |

| f <sub>PLL_OUT</sub>  | PLL multiplier output clock    | 16 <sup>(2)</sup> | -     | 48                 | MHz  |  |

| t <sub>LOCK</sub>     | PLL lock time                  | -                 | -     | 200 <sup>(2)</sup> | μs   |  |

| Jitter <sub>PLL</sub> | Cycle-to-cycle jitter          | -                 | _     | 300 <sup>(2)</sup> | ps   |  |

Table 45. PLL characteristics

1. Take care to use the appropriate multiplier factors to obtain PLL input clock values compatible with the range defined by f<sub>PLL\_OUT</sub>.

2. Guaranteed by design, not tested in production.

# 6.3.10 Memory characteristics

# Flash memory

The characteristics are given at  $T_A$  = -40 to 105 °C unless otherwise specified.

| Symbol                         | Parameter               | Conditions                       | Min | Тур  | Max <sup>(1)</sup> | Unit |

|--------------------------------|-------------------------|----------------------------------|-----|------|--------------------|------|

| t <sub>prog</sub>              | 16-bit programming time | T <sub>A</sub> = - 40 to +105 °C | 40  | 53.5 | 60                 | μs   |

| t <sub>ERASE</sub>             | Page (2 KB) erase time  | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| t <sub>ME</sub>                | Mass erase time         | T <sub>A</sub> = - 40 to +105 °C | 20  | -    | 40                 | ms   |

| 1                              | Supply ourrant          | Write mode                       | -   | -    | 10                 | mA   |

| I <sub>DD</sub> Supply current |                         | Erase mode                       | -   | -    | 12                 | mA   |

1. Guaranteed by design, not tested in production.

| Symbol           | Description                                                                                          | Func<br>suscer | Unit               |      |

|------------------|------------------------------------------------------------------------------------------------------|----------------|--------------------|------|

|                  | Description                                                                                          |                | Positive injection | onit |

|                  | Injected current on BOOT0 and PF1 pins                                                               | -0             | NA                 |      |

|                  | Injected current on PC0 pin                                                                          | -0             | +5                 |      |

| I <sub>INJ</sub> | Injected current on PA11 and PA12 pins with induced leakage current on adjacent pins less than -1 mA | -5             | NA                 | mA   |

|                  | Injected current on all other FT and FTf pins                                                        | -5             | NA                 |      |

|                  | Injected current on all other TTa, TC and RST pins                                                   | -5             | +5                 |      |

# Table 52. I/O current injection susceptibility

# 6.3.14 I/O port characteristics

# General input/output characteristics

Unless otherwise specified, the parameters given in *Table 53* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*. All I/Os are designed as CMOS- and TTL-compliant (except BOOT0).

| Symbol           | Parameter                     | Conditions                   | Min                                            | Тур                | Мах                                          | Unit |

|------------------|-------------------------------|------------------------------|------------------------------------------------|--------------------|----------------------------------------------|------|

|                  |                               | TC and TTa I/O               | -                                              | -                  | 0.3 V <sub>DDIOx</sub> +0.07 <sup>(1)</sup>  |      |

|                  | Low level input               | FT and FTf I/O               | -                                              | -                  | 0.475 V <sub>DDIOx</sub> -0.2 <sup>(1)</sup> |      |

| V <sub>IL</sub>  | voltage                       | BOOT0                        | -                                              | -                  | 0.3 V <sub>DDIOx</sub> -0.3 <sup>(1)</sup>   | V    |

|                  |                               | All I/Os except<br>BOOT0 pin | -                                              | -                  | 0.3 V <sub>DDIOx</sub>                       |      |

|                  |                               | TC and TTa I/O               | 0.445 V <sub>DDIOx</sub> +0.398 <sup>(1)</sup> | -                  | -                                            |      |

|                  | High level input              | FT and FTf I/O               | 0.5 V <sub>DDIOx</sub> +0.2 <sup>(1)</sup>     | -                  | -                                            |      |

| V <sub>IH</sub>  | voltage                       | BOOT0                        | 0.2 V <sub>DDIOx</sub> +0.95 <sup>(1)</sup>    | -                  | -                                            | V    |

|                  |                               | All I/Os except<br>BOOT0 pin | 0.7 V <sub>DDIOx</sub>                         | -                  | -                                            |      |

|                  |                               | TC and TTa I/O               | -                                              | 200 <sup>(1)</sup> | -                                            |      |

| V <sub>hys</sub> | Schmitt trigger<br>hysteresis | FT and FTf I/O               | -                                              | 100 <sup>(1)</sup> | -                                            | mV   |

|                  | 11931010313                   | BOOT0                        | -                                              | 300 <sup>(1)</sup> | -                                            |      |

#### Table 53. I/O static characteristics

| Symbol                 | Parameter                                          | Conditions                        | Min                | Тур | Мах                | Unit |

|------------------------|----------------------------------------------------|-----------------------------------|--------------------|-----|--------------------|------|

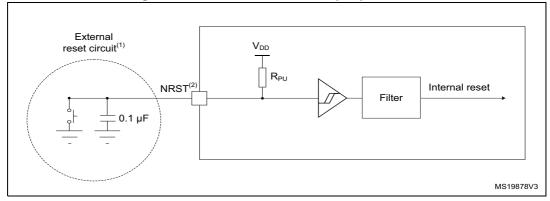

| V <sub>hys(NRST)</sub> | NRST Schmitt trigger voltage<br>hysteresis         | -                                 | -                  | 200 | -                  | mV   |

| R <sub>PU</sub>        | Weak pull-up equivalent<br>resistor <sup>(2)</sup> | V <sub>IN</sub> = V <sub>SS</sub> | 25                 | 40  | 55                 | kΩ   |

| V <sub>F(NRST)</sub>   | NRST input filtered pulse                          | -                                 | -                  | -   | 100 <sup>(1)</sup> | ns   |

| V                      | NRST input not filtered pulse                      | $2.7 < V_{DD} < 3.6$              | 300 <sup>(3)</sup> | -   | -                  | ns   |

| V <sub>NF(NRST)</sub>  |                                                    | $2.0 < V_{DD} < 3.6$              | 500 <sup>(3)</sup> | -   | -                  | 115  |

Table 56. NRST pin characteristics (continued)

1. Data based on design simulation only. Not tested in production.

The pull-up is designed with a true resistance in series with a switchable PMOS. This PMOS contribution to the series resistance is minimal (~10% order).

3. Data based on design simulation only. Not tested in production.

- 1. The external capacitor protects the device against parasitic resets.

- The user must ensure that the level on the NRST pin can go below the V<sub>IL(NRST)</sub> max level specified in Table 56: NRST pin characteristics. Otherwise the reset will not be taken into account by the device.

# 6.3.16 12-bit ADC characteristics

Unless otherwise specified, the parameters given in *Table 57* are derived from tests performed under the conditions summarized in *Table 24: General operating conditions*.

Note: It is recommended to perform a calibration after each power-up.

| Table 57. | ADC char | acteristics |

|-----------|----------|-------------|

|-----------|----------|-------------|

| Symbol                        | Parameter                                     | Conditions               | Min   | Тур | Max | Unit |

|-------------------------------|-----------------------------------------------|--------------------------|-------|-----|-----|------|

| V <sub>DDA</sub>              | Analog supply voltage for<br>ADC ON           | -                        | 2.4   | -   | 3.6 | V    |

| I <sub>DDA (ADC)</sub>        | Current consumption of the ADC <sup>(1)</sup> | V <sub>DDA</sub> = 3.3 V | -     | 0.9 | -   | mA   |

| f <sub>ADC</sub>              | ADC clock frequency                           | -                        | 0.6   | -   | 14  | MHz  |

| f <sub>S</sub> <sup>(2)</sup> | Sampling rate                                 | 12-bit resolution        | 0.043 | -   | 1   | MHz  |

# 6.3.18 Comparator characteristics

| Symbol                   | Parameter                                                         | Conditions                                                        |                          | Min <sup>(1)</sup> | Тур              | Max <sup>(1)</sup> | Unit |

|--------------------------|-------------------------------------------------------------------|-------------------------------------------------------------------|--------------------------|--------------------|------------------|--------------------|------|

| $V_{DDA}$                | Analog supply voltage                                             | -                                                                 | $V_{DD}$                 | -                  | 3.6              | V                  |      |

| V <sub>IN</sub>          | Comparator input voltage range                                    | -                                                                 | 0                        | -                  | V <sub>DDA</sub> | -                  |      |

| V <sub>SC</sub>          | V <sub>REFINT</sub> scaler offset voltage                         | -                                                                 |                          |                    | ±5               | ±10                | mV   |

| t <sub>s_sc</sub>        | V <sub>REFINT</sub> scaler startup<br>time from power down        | First V <sub>REFINT</sub> scaler activation after device power on |                          | -                  | -                | 1000<br>(2)        | ms   |

|                          |                                                                   | Next activations                                                  |                          | -                  | -                | 0.2                |      |

| t <sub>start</sub>       | Comparator startup time                                           | Startup time to reach propagation delay specification             |                          |                    | -                | 60                 | μs   |

| t <sub>D</sub>           |                                                                   | Ultra-low power mode                                              | -                        | 2                  | 4.5              | μs                 |      |

|                          | Propagation delay for<br>200 mV step with<br>100 mV overdrive     | Low power mode                                                    | -                        | 0.7                | 1.5              |                    |      |

|                          |                                                                   | Medium power mode                                                 | -                        | 0.3                | 0.6              |                    |      |

|                          |                                                                   | High speed mode                                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 50               | 100                |      |

|                          |                                                                   |                                                                   | V <sub>DDA</sub> < 2.7 V | -                  | 100              | 240                | ns   |

|                          | Propagation delay for<br>full range step with<br>100 mV overdrive | Ultra-low power mode                                              | -                        | 2                  | 7                |                    |      |

|                          |                                                                   | Low power mode                                                    | -                        | 0.7                | 2.1              | μs                 |      |

|                          |                                                                   | Medium power mode                                                 | -                        | 0.3                | 1.2              |                    |      |

|                          |                                                                   | High speed mode                                                   | V <sub>DDA</sub> ≥ 2.7 V | -                  | 90               | 180                | ns   |

|                          |                                                                   | nigh speed mode                                                   | V <sub>DDA</sub> < 2.7 V | -                  | 110              | 300                | 115  |

| V <sub>offset</sub>      | Comparator offset error                                           | -                                                                 |                          | -                  | ±4               | ±10                | mV   |

| dV <sub>offset</sub> /dT | Offset error temperature coefficient                              | -                                                                 | -                        | 18                 | -                | µV/°C              |      |

|                          |                                                                   | Ultra-low power mode                                              |                          | -                  | 1.2              | 1.5                | μΑ   |

| 1                        | COMP current consumption                                          | Low power mode                                                    |                          | -                  | 3                | 5                  |      |

| I <sub>DD</sub> (COMP)   |                                                                   | Medium power mode                                                 | -                        | 10                 | 15               |                    |      |

|                          |                                                                   | High speed mode                                                   | -                        | 75                 | 100              |                    |      |

#### Table 61. Comparator characteristics

## **USB** characteristics

The STM32F072x8/xB USB interface is fully compliant with the USB specification version 2.0 and is USB-IF certified (for Full-speed device operation).

| Symbol                              | Parameter                                      | Conditions              | Min.               | Тур  | Max. | Unit |  |

|-------------------------------------|------------------------------------------------|-------------------------|--------------------|------|------|------|--|

| V <sub>DDIO2</sub>                  | USB transceiver operating voltage              | -                       | 3.0 <sup>(1)</sup> | -    | 3.6  | V    |  |

| t <sub>STARTUP</sub> <sup>(2)</sup> | USB transceiver startup time                   | -                       | -                  | -    | 1.0  | μs   |  |

| R <sub>PUI</sub>                    | Embedded USB_DP pull-up value during idle      | -                       | 1.1                | 1.26 | 1.5  | kΩ   |  |

| R <sub>PUR</sub>                    | Embedded USB_DP pull-up value during reception | -                       | 2.0                | 2.26 | 2.6  |      |  |

| Z <sub>DRV</sub> <sup>(2)</sup>     | Output driver impedance <sup>(3)</sup>         | Driving high<br>and low | 28                 | 40   | 44   | Ω    |  |

| Table 70. USB electrical characteristic |

|-----------------------------------------|

|-----------------------------------------|

1. The STM32F072x8/xB USB functionality is ensured down to 2.7 V but not the full USB electrical characteristics which are degraded in the 2.7-to-3.0 V voltage range.

2. Guaranteed by design, not tested in production.

3. No external termination series resistors are required on USB\_DP (D+) and USB\_DM (D-); the matching impedance is already included in the embedded driver.

# CAN (controller area network) interface

Refer to Section 6.3.14: I/O port characteristics for more details on the input/output alternate function characteristics (CAN\_TX and CAN\_RX).

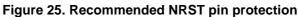

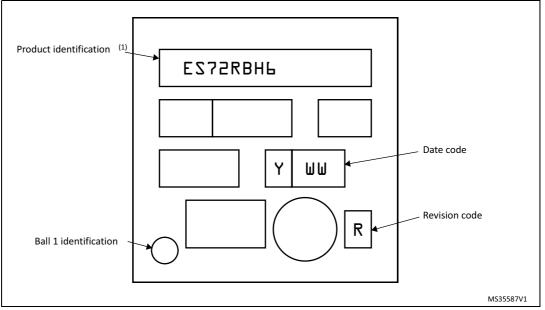

# **Device marking**

The following figure gives an example of topside marking orientation versus pin 1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.

| Table 141 et Berter publicage moonament auta (continued) |             |       |       |                       |        |        |  |

|----------------------------------------------------------|-------------|-------|-------|-----------------------|--------|--------|--|

| Symbol                                                   | millimeters |       |       | inches <sup>(1)</sup> |        |        |  |

| Symbol                                                   | Min         | Тур   | Max   | Min                   | Тур    | Max    |  |

| А                                                        | 0.460       | 0.530 | 0.600 | 0.0181                | 0.0209 | 0.0236 |  |

| ddd                                                      | -           | -     | 0.080 | -                     | -      | 0.0031 |  |

| eee                                                      | -           | -     | 0.150 | -                     | -      | 0.0059 |  |

| fff                                                      | -           | -     | 0.050 | -                     | -      | 0.0020 |  |

#### Table 74. UFBGA64 package mechanical data (continued)

1. Values in inches are converted from mm and rounded to 4 decimal digits.

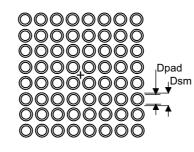

#### Figure 42. Recommended footprint for UFBGA64 package

A019\_FP\_V2

#### Table 75. UFBGA64 recommended PCB design rules

| Dimension         | Recommended values                                               |  |

|-------------------|------------------------------------------------------------------|--|

| Pitch             | 0.5                                                              |  |

| Dpad              | 0.280 mm                                                         |  |

| Dsm               | 0.370 mm typ. (depends on the soldermask registration tolerance) |  |

| Stencil opening   | 0.280 mm                                                         |  |

| Stencil thickness | Between 0.100 mm and 0.125 mm                                    |  |

| Pad trace width   | 0.100 mm                                                         |  |

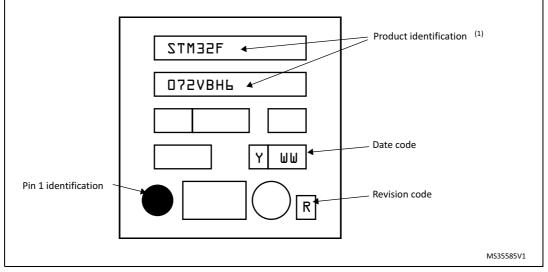

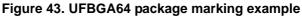

# **Device marking**

The following figure gives an example of topside marking orientation versus ball A1 identifier location.

Other optional marking or inset/upset marks, which identify the parts throughout supply chain operations, are not indicated below.

Parts marked as "ES", "E" or accompanied by an Engineering Sample notification letter, are not yet qualified and therefore not yet ready to be used in production and any consequences deriving from such usage will not be at ST charge. In no event, ST will be liable for any customer usage of these engineering samples in production. ST Quality has to be contacted prior to any decision to use these Engineering Samples to run qualification activity.