Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1057                                                        |

| Number of Logic Elements/Cells | 10570                                                       |

| Total RAM Bits                 | 920448                                                      |

| Number of I/O                  | 362                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 672-BBGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx10cf672c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

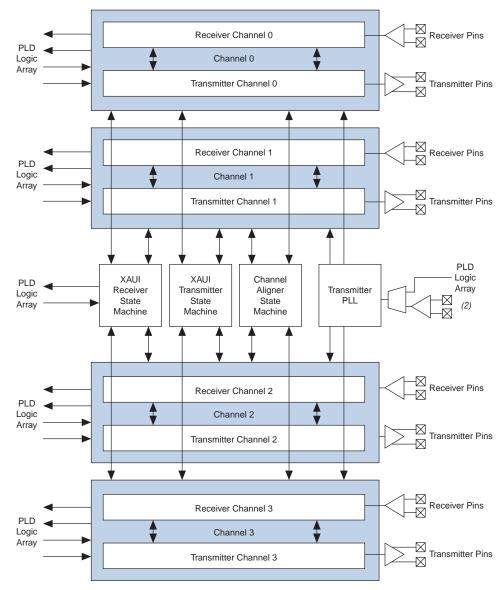

Figure 2–1. Stratix GX Transceiver Block Note (1)

#### *Notes to Figure 2–1:*

- (1) Each receiver channel has its own PLL and CRU, which are not shown in this diagram. For more information, refer to the section "Receiver Path" on page 2–13.

- (2) For possible transmitter PLL clock inputs, refer to the section "Transmitter Path" on page 2–5.

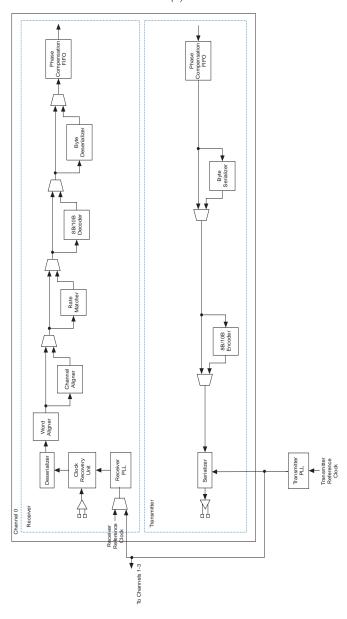

Figure 2–2. Stratix GX Transceiver Channel Note (1)

Note to Figure 2–2:

(1) There are four transceiver channels in a transceiver block.

## **Transmitter Path**

This section describes the data path through the Stratix GX transmitter (see Figure 2–2). Data travels through the Stratix GX transmitter via the following modules:

- Transmitter PLL

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel to serial converter)

- Transmitter output buffer

### Transmitter PLL

Each transceiver block has one transmitter PLL, which receives the reference clock and generates the following signals:

- High-speed serial clock used by the serializer

- Slow-speed reference clock used by the receiver

- Slow-speed clock used by the logic array (divisible by two for double-width mode)

The INCLK clock is the input into the transmitter PLL. There is one INCLK clock per transceiver block. This clock can be fed by either the REFCLKB pin, PLD routing, or the inter-transceiver routing line. See the section "Stratix GX Clocking" on page 2–30 for more information about the inter-transceiver lines.

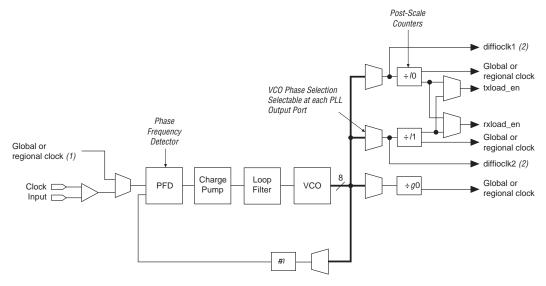

The transmitter PLL in each transceiver block clocks the circuits in the transmit path. The transmitter PLL is also used to train the receiver PLL. If no transmit channels are used in the transceiver block, the transmitter PLL can be turned off. Figure 2–3 is a block diagram of the transmitter PLL.

Figure 2-16. Word Aligner in 16-Bit Mode

In the 16-bit mode, the word aligner and pattern detector automatically aligns and detects a user-defined 16-bit alignment pattern. This pattern can be in the format of A1A2 or A1A1A2A2 (for the SONET protocol). The re-alignment of the byte boundary can be done via a user-controlled port. The 16-bit mode supports only the 8-bit data path in a single-width or double-width mode.

The 16-bit mode is available only for the Custom mode and SONET mode. The A1A1A2A2 word alignment pattern option is available only for the SONET mode and cannot be used in the Custom mode.

Figure 2–17 shows the word aligner in 10-bit mode.

have four dedicated fast PLLs for clock multiplication. Table 3–3 shows the maximum number of channels in each Stratix GX device that support DPA.

| Table 3–3. Strat | Table 3–3. Stratix GX Source-Synchronous Differential I/O Resources |           |                      |                                |                                                          |        |  |  |  |

|------------------|---------------------------------------------------------------------|-----------|----------------------|--------------------------------|----------------------------------------------------------|--------|--|--|--|

| Device           | Fast PLLs                                                           | Pin Count | Receiver<br>Channels | Transmitter<br>Channels<br>(1) | Receiver &<br>Transmitter<br>Channel Speed<br>(Gbps) (2) | LEs    |  |  |  |

| EP1SGX10C        | 2 (3)                                                               | 672       | 22                   | 22                             | 1                                                        | 10,570 |  |  |  |

| EP1SGX10D        | 2 (3)                                                               | 672       | 22                   | 22                             | 1                                                        | 10,570 |  |  |  |

| EP1SGX25C        | 2                                                                   | 672       | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |

| EP1SGX25D        | 2                                                                   | 672       | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |

|                  |                                                                     | 1,020     | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |

| EP1SGX25F        | 2                                                                   | 1,020     | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |

| EP1SGX40D        | 4 (4)                                                               | 1,020     | 45                   | 45                             | 1                                                        | 41,250 |  |  |  |

| EP1SGX40G        | 4 (4)                                                               | 1,020     | 45                   | 45                             | 1                                                        | 41,250 |  |  |  |

#### Notes to Table 3-3:

- (1) This is the number of receiver or transmitter channels in the source-synchronous (I/O bank 1 and 2) interface of the device.

- (2) Receiver channels operate at 1,000 Mbps with DPA. Without DPA, the receiver channels operate at 840 Mbps.

- (3) One of the two fast PLLs in EP1SGX10C and EP1SGX10D devices supports DPA.

- (4) Two of the four fast PLLs in EP1SGX40D and EP1SGX40G devices support DPA

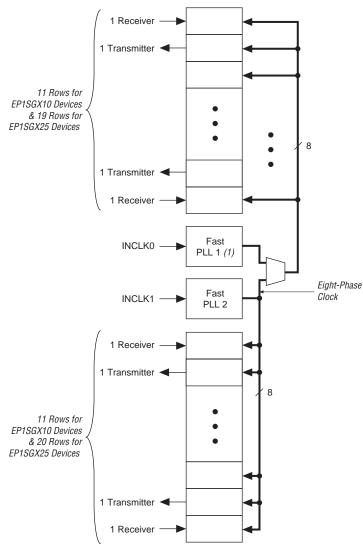

The receiver and transmitter channels are interleaved so that each I/O row in I/O banks 1 and 2 of the device has one receiver channel and one transmitter channel per row. Figures 3–6 and 3–7 show the fast PLL and channels with DPA layout in EP1SGX10, EP1SGX25, and EP1SGX40 devices. In EP1SGX10 devices, only fast PLL 2 supports DPA operations.

Figure 3–6. PLL & Channel Layout in EP1SGX10 & EP1SGX25

Devices Notes (1), (2)

#### Notes to Figure 3-6:

- (1) Fast PLL 1 in EP1SGX10 devices does not support DPA.

- (2) Not all eight phases are used by the receiver channel or transmitter channel in non-DPA mode.

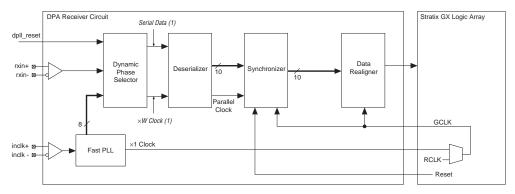

# **DPA Operation**

The DPA receiver circuitry contains the dynamic phase selector, the deserializer, the synchronizer, and the data realigner (see Figure 3–8). This section describes the DPA operation, synchronization and data realignment. In the SERDES with DPA mode, the source clock is fed to the fast PLL through the dedicated clock input pins. This clock is multiplied by the multiplication value *W* to match the serial data rate.

For information on the deserializer, see "Principles of SERDES Operation" on page 3–1.

Figure 3-8. DPA Receiver Circuit

Note to Figure 3-8:

(1) These are phase-matched and retimed high-speed clocks and data.

The dynamic phase selector matches the phase of the high-speed clock and data before sending them to the deserializer.

The fast PLL supplies eight phases of the same clock (each a separate tap from a four-stage differential VCO) to all the differential channels associated with the selected fast PLL. The DPA circuitry inside each channel locks to a phase closest to the serial data's phase and sends the retimed data and the selected clock to the deserializer. The DPA circuitry automatically performs this operation and is not something you select. Each channel's DPA circuit can independently choose a different clock phase. The data phase detection and the clock phase selection process is automatic and continuous. The eight phases of the clock give the DPA circuit a granularity of one eighth of the unit interval (UI) or 125 ps at 1 Gbps. Figure 3–9 illustrates the clocks generated by the fast PLL circuitry and their relationship to a data stream.

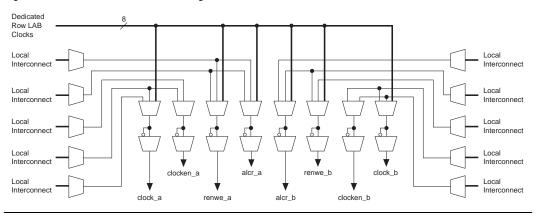

Figure 4-16. M4K RAM Block Control Signals

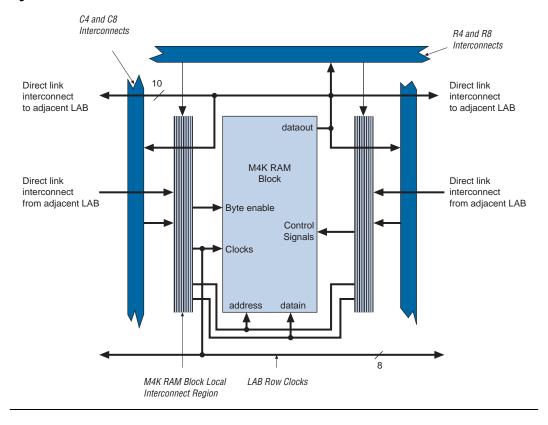

Figure 4-17. M4K RAM Block LAB Row Interface

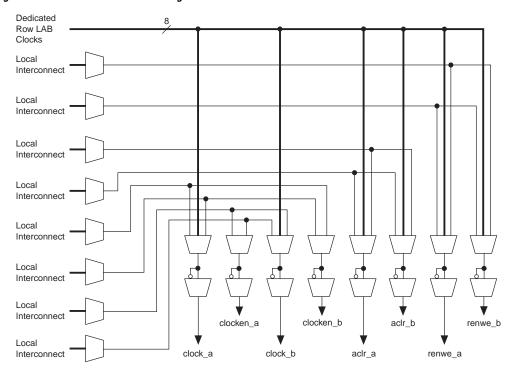

Figure 4-18. M-RAM Block Control Signals

One of the M-RAM block's horizontal sides drive the address and control signal (clock, renwe, byteena, etc.) inputs. Typically, the horizontal side closest to the device perimeter contains the interfaces. The one exception is when two M-RAM blocks are paired next to each other. In this case, the side of the M-RAM block opposite the common side of the two blocks contains the input interface. The top and bottom sides of any M-RAM block contain data input and output interfaces to the logic array. The top side has 72 data inputs and 72 data outputs for port B, and the bottom side has another 72 data inputs and 72 data outputs for port A. Figure 4–19 shows an example floorplan for the EP1SGX40 device and the location of the M-RAM interfaces.

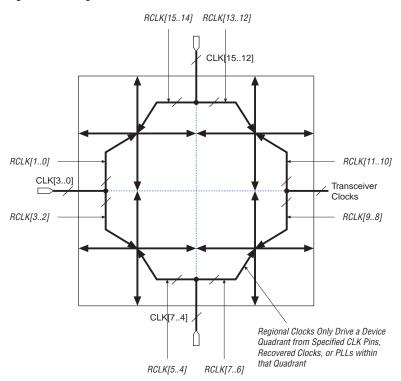

These clocks are organized into a hierarchical clock structure that allows for up to 22 clocks per device region with low skew and delay. This hierarchical clocking scheme provides up to 40 unique clock domains within EP1SGX10 and EP1SGX25 devices, and 48 unique clock domains within EP1SGX40 devices.

There are 12 dedicated clock pins (CLK[15..12], and CLK[7..0]) to drive either the global or regional clock networks. Three clock pins drive the top, bottom, and left side of the device. Enhanced and fast PLL outputs as well as an I/O interface can also drive these global and regional clock networks.

There are up to 20 recovered clocks (rxclkout [20..0]) and up to 5 transmitter clock outputs (coreclk\_out) which can drive any of the global clock networks (CLK[15..0]), as shown in Figure 4–41.

#### Global Clock Network

These clocks drive throughout the entire device, feeding all device quadrants. The global clock networks can be used as clock sources for all resources within the device IOEs, LEs, DSP blocks, and all memory blocks. These resources can also be used for control signals, such as clock enables and synchronous or asynchronous clears fed from the external pin. The global clock networks can also be driven by internal logic for internally generated global clocks and asynchronous clears, clock enables, or other control signals with large fanout. Figure 4–41 shows the 12 dedicated CLK pins and the transceiver clocks driving global clock networks.

Figure 4-42. Regional Clocks

# Fast Regional Clock Network

In EP1SGX25 and EP1SGX10 devices, there are two fast regional clock networks, FCLK [1..0], within each quadrant, fed by input pins (see Figure 4–43). In EP1SGX40 devices, there are two fast regional clock networks within each half-quadrant (see Figure 4–44). The FCLK [1..0] clocks can also be used for high fanout control signals, such as asynchronous clears, presets, clock enables, or protocol control signals such as TRDY and IRDY for PCI. Dual-purpose FCLK pins drive the fast clock networks. All devices have eight FCLK pins to drive fast regional clock networks. Any I/O pin can drive a clock or control signal onto any fast regional clock network with the addition of a delay. The I/O interconnect drives this signal.

Figure 4-57. Stratix GX Device Fast PLL

#### *Notes to Figure 4–57:*

- In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (2) This signal is a high-speed differential I/O support SERDES control signal.

## Clock Multiplication & Division

The Stratix GX device's fast PLLs provide clock synthesis for PLL output ports using m/(post scaler) scaling factors. The input clock is multiplied by the m feedback factor. Each output port has a unique post scale counter to divide down the high-frequency VCO. There is one multiply divider, m, per fast PLL with a range of 1 to 32. There are two post scale L dividers for regional and/or LVDS interface clocks, and g0 counter for global clock output port; all range from 1 to 32.

In the case of a high-speed differential interface, you can set the output counter to 1 to allow the high-speed VCO frequency to drive the SERDES.

## External Clock Outputs

Each fast PLL supports differential or single-ended outputs for source-synchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output

| JTAG Instruction       | Description                                                                                                                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP (1)              | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions       | Used when configuring a Stratix GX device through the JTAG port with a MasterBlaster™ or ByteBlasterMV™ download cable, or when using a .jam file or .jbc file with an embedded processor.                                                                                      |

| PULSE_NCONFIG          | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

| CONFIG_IO              | Allows the IOE standards to be configured through the JTAG chain. Stops configuration if executed during configuration. Can be executed before or after configuration.                                                                                                          |

| SignalTap instructions | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                                                                  |

#### Note to Table 4-33:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

The Stratix GX device instruction register length is 10 bits, and the USERCODE register length is 32 bits. Tables 4–34 and 4–35 show the boundary-scan register length and IDCODE information for Stratix GX devices.

| Table 4–34. Stratix GX Boundary-Scan Register Length |                               |  |  |  |

|------------------------------------------------------|-------------------------------|--|--|--|

| Device                                               | Boundary-Scan Register Length |  |  |  |

| EP1SGX10                                             | 1,029                         |  |  |  |

| EP1SGX25                                             | 1,665                         |  |  |  |

| EP1SGX40                                             | 1,941                         |  |  |  |

| Table 4–35. 32-Bit Stratix GX Device IDCODE (Part 1 of 2) |                                        |                     |                                    |                 |  |  |  |

|-----------------------------------------------------------|----------------------------------------|---------------------|------------------------------------|-----------------|--|--|--|

| IDCODE (32 Bits) (1)                                      |                                        |                     |                                    |                 |  |  |  |

| Device                                                    | Version (4 Bits) Part Number (16 Bits) |                     | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |  |

| EP1SGX10                                                  | 0000                                   | 0010 0000 0100 0001 | 000 0110 1110                      | 1               |  |  |  |

| EP1SGX25                                                  | 0000                                   | 0010 0000 0100 0011 | 000 0110 1110                      | 1               |  |  |  |

and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

A built-in weak pull-up resistor pulls all user I/O pins to  $V_{\text{CCIO}}$  before and during device configuration.

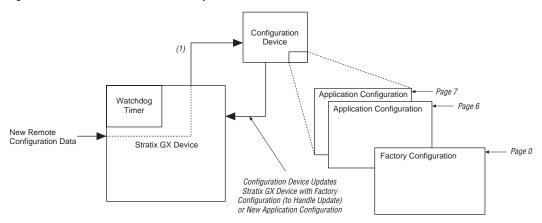

SRAM configuration elements allow Stratix GX devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

# **Configuration Schemes**

You can load the configuration data for a Stratix GX device with one of five configuration schemes (see Table 5–1), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix GX device. A configuration device can automatically configure a Stratix GX device at system power-up.

You can configure multiple Stratix GX devices in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 5–1. Data Sources for Configuration |                                                                                                         |  |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                      | Data Source                                                                                             |  |  |  |  |

| Configuration device                      | Enhanced or EPC2 configuration device                                                                   |  |  |  |  |

| Passive serial (PS)                       | ByteBlasterMV <sup>™</sup> or MasterBlaster <sup>™</sup> download cable or serial data source           |  |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                    |  |  |  |  |

| Fast passive parallel                     | Parallel data source                                                                                    |  |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam or JBC file (.jam or .jbc) |  |  |  |  |

Figure 5-1. Stratix GX Device Remote Update

#### Note to Figure 5-1:

(1) When the Stratix GX device is configured with the factory configuration, it can handle update data from EPC16, EPC8, or EPC4 configuration device pages and point to the next page in the configuration device.

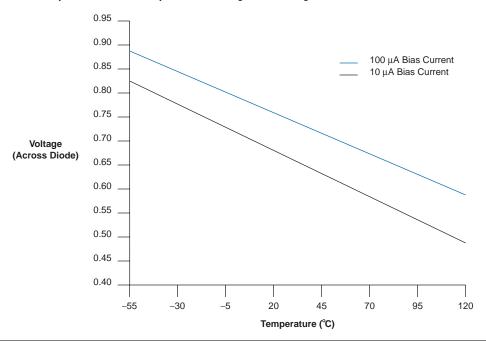

Figure 5–5. Temperature Versus Temperature-Sensing Diode Voltage

| Table 6–29. 1.5-V HSTL Class I Specifications (Part 2 of 2) |                           |                               |                         |  |     |   |  |

|-------------------------------------------------------------|---------------------------|-------------------------------|-------------------------|--|-----|---|--|

| Symbol Parameter Conditions Minimum Typical Maximum Unit    |                           |                               |                         |  |     |   |  |

| V <sub>OH</sub>                                             | High-level output voltage | I <sub>OH</sub> = 8 mA (1)    | V <sub>CCIO</sub> - 0.4 |  |     | V |  |

| V <sub>OL</sub>                                             | Low-level output voltage  | $I_{OH} = -8 \text{ mA } (1)$ |                         |  | 0.4 | V |  |

| Table 6-30           | Table 6–30. 1.5-V HSTL Class II Specifications |                                    |                         |         |                        |       |  |  |  |  |

|----------------------|------------------------------------------------|------------------------------------|-------------------------|---------|------------------------|-------|--|--|--|--|

| Symbol               | Parameter                                      | Conditions                         | Minimum                 | Typical | Maximum                | Units |  |  |  |  |

| V <sub>CCIO</sub>    | Output supply voltage                          |                                    | 1.4                     | 1.5     | 1.6                    | V     |  |  |  |  |

| V <sub>REF</sub>     | Input reference voltage                        |                                    | 0.68                    | 0.75    | 0.9                    | V     |  |  |  |  |

| V <sub>TT</sub>      | Termination voltage                            |                                    | 0.7                     | 0.75    | 0.8                    | V     |  |  |  |  |

| V <sub>IH</sub> (DC) | DC high-level input voltage                    |                                    | V <sub>REF</sub> + 0.1  |         |                        | V     |  |  |  |  |

| V <sub>IL</sub> (DC) | DC low-level input voltage                     |                                    | -0.3                    |         | V <sub>REF</sub> - 0.1 | V     |  |  |  |  |

| V <sub>IH</sub> (AC) | AC high-level input voltage                    |                                    | V <sub>REF</sub> + 0.2  |         |                        | V     |  |  |  |  |

| V <sub>IL</sub> (AC) | AC low-level input voltage                     |                                    |                         |         | V <sub>REF</sub> - 0.2 | V     |  |  |  |  |

| V <sub>OH</sub>      | High-level output voltage                      | I <sub>OH</sub> = 16 mA <i>(1)</i> | V <sub>CCIO</sub> - 0.4 |         |                        | V     |  |  |  |  |

| V <sub>OL</sub>      | Low-level output voltage                       | $I_{OH} = -16 \text{ mA } (1)$     |                         |         | 0.4                    | V     |  |  |  |  |

| Table 6–31. 1.5-V Differential HSTL Specifications |                               |            |         |         |         |       |  |  |

|----------------------------------------------------|-------------------------------|------------|---------|---------|---------|-------|--|--|

| Symbol                                             | Parameter                     | Conditions | Minimum | Typical | Maximum | Units |  |  |

| V <sub>CCIO</sub>                                  | I/O supply voltage            |            | 1.4     | 1.5     | 1.6     | V     |  |  |

| V <sub>DIF</sub> (DC)                              | DC input differential voltage |            | 0.2     |         |         | V     |  |  |

| V <sub>CM</sub> (DC)                               | DC common mode input voltage  |            | 0.68    |         | 0.9     | V     |  |  |

| V <sub>DIF</sub> (AC)                              | AC differential input voltage |            | 0.4     |         |         | V     |  |  |

| Table 6-32                        | Table 6–32. CTT I/O Specifications (Part 1 of 2) |            |                        |         |                        |       |  |  |

|-----------------------------------|--------------------------------------------------|------------|------------------------|---------|------------------------|-------|--|--|

| Symbol                            | Parameter                                        | Conditions | Minimum                | Typical | Maximum                | Units |  |  |

| V <sub>CCIO</sub>                 | Output supply voltage                            |            | 3.0                    | 3.3     | 3.6                    | V     |  |  |

| V <sub>TT</sub> /V <sub>REF</sub> | Termination and input reference voltage          |            | 1.35                   | 1.5     | 1.65                   | V     |  |  |

| V <sub>IH</sub>                   | High-level input voltage                         |            | V <sub>REF</sub> + 0.2 |         |                        | V     |  |  |

| V <sub>IL</sub>                   | Low-level input voltage                          |            |                        |         | V <sub>REF</sub> - 0.2 | V     |  |  |

| Table 6–56. EP1SGX10 Column Pin Global Clock External I/O Timing Parameters |         |                |       |                |       |                |      |  |

|-----------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|------|--|

| Symbol                                                                      | -5 Spee | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |      |  |

|                                                                             | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |

| t <sub>INSU</sub>                                                           | 1.785   |                | 1.814 |                | 2.087 |                | ns   |  |

| t <sub>INH</sub>                                                            | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |

| t <sub>outco</sub>                                                          | 2.000   | 5.057          | 2.000 | 5.438          | 2.000 | 6.214          | ns   |  |

| t <sub>INSUPLL</sub>                                                        | 0.988   |                | 0.936 |                | 1.066 |                | ns   |  |

| t <sub>INHPLL</sub>                                                         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |

| t <sub>OUTCOPLL</sub>                                                       | 0.500   | 2.634          | 0.500 | 2.774          | 0.500 | 3.162          | ns   |  |

| Table 6–57. EP1SGX10 Row Pin Fast Regional Clock External I/O Timing Parameters |         |         |         |         |                |       |      |  |

|---------------------------------------------------------------------------------|---------|---------|---------|---------|----------------|-------|------|--|

| Symbol                                                                          | -5 Spee | d Grade | -6 Spee | d Grade | -7 Speed Grade |       | II:A |  |

|                                                                                 | Min     | Max     | Min     | Max     | Min            | Max   | Unit |  |

| t <sub>INSU</sub>                                                               | 2.194   |         | 2.384   |         | 2.727          |       | ns   |  |

| t <sub>INH</sub>                                                                | 0.000   |         | 0.000   |         | 0.000          |       | ns   |  |

| t <sub>OUTCO</sub>                                                              | 2.000   | 4.956   | 2.000   | 4.971   | 2.000          | 5.463 | ns   |  |

| Table 6–58. EP1SGX10 Row Pin Regional Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |  |

|----------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|

| Symbol                                                                     | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | Hait  |      |  |  |

|                                                                            | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>                                                          | 2.244   |         | 2.413   |         | 2.574   |       | ns   |  |  |

| t <sub>INH</sub>                                                           | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCO</sub>                                                         | 2.000   | 4.906   | 2.000   | 4.942   | 2.000   | 5.616 | ns   |  |  |

| t <sub>INSUPLL</sub>                                                       | 1.126   |         | 1.186   |         | 1.352   |       | ns   |  |  |

| t <sub>INHPLL</sub>                                                        | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCOPLL</sub>                                                      | 0.500   | 2.804   | 0.500   | 2.627   | 0.500   | 2.765 | ns   |  |  |

| Table 6–59. EP1SGX10 Row Pin Global Clock External I/O Timing Parameters (Part 1 of 2) |                |     |         |         |         |      |        |  |  |

|----------------------------------------------------------------------------------------|----------------|-----|---------|---------|---------|------|--------|--|--|

| Symbol                                                                                 | -5 Speed Grade |     | -6 Spee | d Grade | -7 Spee | Umit |        |  |  |

|                                                                                        | Min            | Max | Min     | Max     | Min     | Max  | - Unit |  |  |

| t <sub>INSU</sub>                                                                      | 1.919          |     | 2.062   |         | 2.368   |      | ns     |  |  |

| t <sub>INH</sub>                                                                       | 0.000          |     | 0.000   |         | 0.000   |      | ns     |  |  |

| Symbol                                      | Conditions                                        |                                                                  | -5 Speed Grade                 |     |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     |      |     |

|---------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|--------------------------------|-----|-----|----------------|-----|-----|----------------|-----|-----|------|-----|

|                                             |                                                   |                                                                  | Min                            | Тур | Max | Min            | Тур | Max | Min            | Тур | Max | Unit |     |

| DPA Lock Time                               | Standard                                          | Train ing Patt ern                                               | Trans<br>ition<br>Den-<br>sity |     |     |                |     |     |                |     |     |      |     |

|                                             | SPI-4,<br>CSIX                                    | 0000<br>0000<br>0011<br>1111<br>1111                             | 10%                            | 256 |     |                | 256 |     |                | 256 |     |      | (4) |

|                                             | Rapid IO                                          | 0000<br>1111                                                     | 25%                            | 256 |     |                | 256 |     |                | 256 |     |      | (4) |

|                                             |                                                   | 1001<br>0000                                                     | 50%                            | 256 |     |                | 256 |     |                | 256 |     |      | (4) |

|                                             | Misc                                              | 1010<br>1010                                                     | 100<br>%                       | 256 |     |                | 256 |     |                | 256 |     |      | (4) |

|                                             |                                                   | 0101<br>0101                                                     |                                | 256 |     |                | 256 |     |                | 256 |     |      | (4) |

| TCCS                                        | All                                               |                                                                  | •                              |     |     | 200            |     |     | 200            |     |     | 300  | ps  |

| SW                                          | PCML ( <i>J</i> = 4, 7, 8, 10)                    |                                                                  |                                | 750 |     |                | 750 |     |                | 800 |     |      | ps  |

|                                             | PCML ( <i>J</i> = 2)                              |                                                                  | 900                            |     |     | 900            |     |     | 1,200          |     |     | ps   |     |

|                                             | PCML ( <i>J</i> = 1)                              |                                                                  | 1,500                          |     |     | 1,500          |     |     | 1,700          |     |     | ps   |     |

|                                             | LVDS and LVPECL (J = 1)                           |                                                                  | 500                            |     |     | 500            |     |     | 550            |     |     | ps   |     |

|                                             | LVDS, LVI<br>HyperTrar<br>technolog<br>through 10 | $\begin{array}{c} \text{nsport} \\ \text{y} \ (J=2) \end{array}$ | 2                              | 440 |     |                | 440 |     |                | 500 |     |      | ps  |

| Input jitter<br>tolerance<br>(peak-to-peak) | All                                               |                                                                  |                                |     |     | 250            |     |     | 250            |     |     | 250  | ps  |

| Output jitter<br>(peak-to-peak)             | All                                               |                                                                  |                                |     |     | 160            |     |     | 160            |     |     | 200  | ps  |

| Output t <sub>RISE</sub>                    | LVDS                                              |                                                                  | 80                             | 110 | 120 | 80             | 110 | 120 | 80             | 110 | 120 | ps   |     |

|                                             | HyperTransport technology                         |                                                                  | 110                            | 170 | 200 | 110            | 170 | 200 | 120            | 170 | 200 | ps   |     |

|                                             | LVPECL                                            |                                                                  |                                | 90  | 130 | 150            | 90  | 130 | 150            | 100 | 135 | 150  | ps  |

|                                             | PCML                                              |                                                                  |                                | 80  | 110 | 135            | 80  | 110 | 135            | 80  | 110 | 135  | ps  |

Table 6–91 describes the Stratix GX device fast PLL specifications.

| Table 6–91. Fast PLL Specifications for -5 & -6 Speed Grade Devices |                                                            |           |                                                            |              |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------|-----------|------------------------------------------------------------|--------------|--|--|--|

| Symbol                                                              | Parameter                                                  | Min       | Max                                                        | Unit         |  |  |  |

| f <sub>IN</sub>                                                     | CLKIN frequency (for $m = 1$ ) (1)                         | 300       | 717                                                        | MHz          |  |  |  |

|                                                                     | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 1,000/ <i>m</i>                                            | MHz          |  |  |  |

|                                                                     | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 1,000/ <i>m</i>                                            | MHz          |  |  |  |

| f <sub>OUT</sub>                                                    | Output frequency for internal global or regional clock (2) | 9.4       | 420                                                        | MHz          |  |  |  |

| f <sub>OUT_EXT</sub>                                                | Output frequency for external clock                        | 9.375     | 717                                                        | MHz          |  |  |  |

| $f_{VCO}$                                                           | VCO operating frequency                                    | 300       | 1,000                                                      | MHz          |  |  |  |

| t <sub>INDUTY</sub>                                                 | CLKIN duty cycle                                           | 40        | 60                                                         | %            |  |  |  |

| t <sub>INJITTER</sub>                                               | Period jitter for CLKIN pin                                |           | ±200                                                       | ps           |  |  |  |

| t <sub>DUTY</sub>                                                   | Duty cycle for DFFIO 1× CLKOUT pin (3)                     | 45        | 55                                                         | %            |  |  |  |

| t <sub>JITTER</sub>                                                 | Period jitter for DIFFIO clock out (3)                     |           | ±80                                                        | ps           |  |  |  |

|                                                                     | Period jitter for internal global or regional clock        |           | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |

| t <sub>LOCK</sub>                                                   | Time required for PLL to acquire lock                      | 10        | 100                                                        | μs           |  |  |  |

| m                                                                   | Multiplication factors for <i>m</i> counter (3)            | 1         | 32                                                         | Integer      |  |  |  |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0                                  | Multiplication factors for I0, I1, and g0 counter (4), (5) | 1         | 32                                                         | Integer      |  |  |  |

| t <sub>ARESET</sub>                                                 | Minimum pulse width on areset signal                       | 10        |                                                            | ns           |  |  |  |

| Symbol                | Parameter                                                  | Min       | Max           | Unit |  |

|-----------------------|------------------------------------------------------------|-----------|---------------|------|--|

| f <sub>IN</sub>       | CLKIN frequency (for $m = 1$ ) (1),                        | 300       | 640           | MHz  |  |

|                       | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 700/ <i>m</i> | MHz  |  |

|                       | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 700/ <i>m</i> | MHz  |  |

| f <sub>OUT</sub>      | Output frequency for internal global or regional clock (2) | 9.375     | 420           | MHz  |  |

| f <sub>OUT_EXT</sub>  | Output frequency for external clock                        | 9.4       | 500           | MHz  |  |

| f <sub>VCO</sub>      | VCO operating frequency                                    | 300       | 700           | MHz  |  |

| t <sub>INDUTY</sub>   | CLKIN duty cycle                                           | 40        | 60            | %    |  |

| t <sub>INJITTER</sub> | Period jitter for CLKIN pin                                |           | ±200          | ps   |  |