Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1057                                                       |

| Number of Logic Elements/Cells | 10570                                                      |

| Total RAM Bits                 | 920448                                                     |

| Number of I/O                  | 362                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BBGA                                                   |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx10df672c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

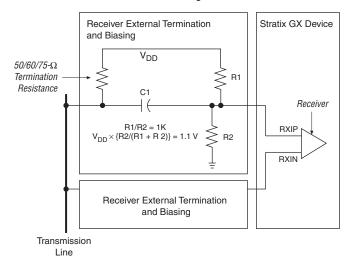

Figure 2-12. External Termination & Biasing Circuit

## Programmable Equalizer

The programmable equalizer module boosts the high frequency components of the incoming signal to compensate for losses in the transmission medium. There are five possible equalization settings (0, 1, 2, 3, 4) to compensate for 0'', 10'', 20'', 30'', and 40'' of FR4 trace. These settings should be interpreted loosely. The programmable equalizer can be set dynamically or statically.

#### Receiver PLL & CRU

Each transceiver block has four receiver PLLs and CRUs, each of which is dedicated to a receive channel. If the receive channel associated with a particular receiver PLL or CRU is not used, then the receiver PLL or CRU is powered down for the channel. Figure 2–13 is a diagram of the receiver PLL and CRU circuits.

#### Parallel Loopback

The parallel loopback mode exercises the digital logic portion of the transceiver data path. The analog portions are not use in the loopback path. The received data is not retimed. Figure 2–22 shows the data path in parallel loopback mode. This option is not dynamically switchable. Reception of an external signal is not possible in this mode.

Figure 2-22. Data Path in Parallel Loopback Mode

# Reverse Serial Loopback

The reverse serial loopback exercises the analog portion of the transceiver. This loopback mode is dynamically switchable through the tx\_srlpbk port on a channel by channel basis. Asserting rxanalogreset in reverse serial loopback mode powers down the receiver buffer and CRU, preventing data loopback. Figure 2–23 shows the data path in reverse serial loopback mode.

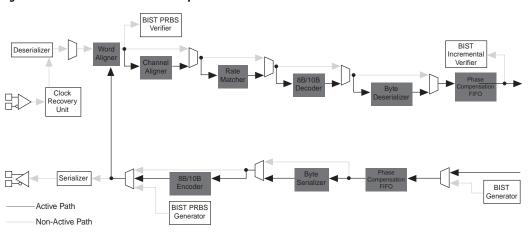

Figure 2-24. BIST PRBS Data Path

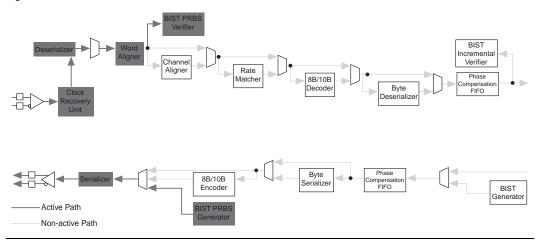

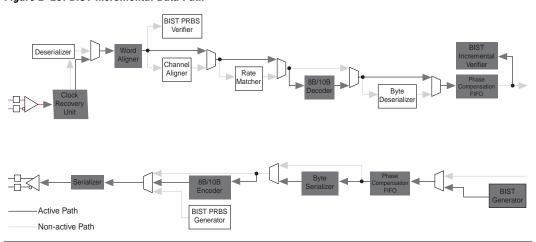

Figure 2-25. BIST Incremental Data Path

Table 2–9 shows the BIST data output and verifier alignment pattern.

| Table 2–9. BIST Data Output & Verifier Alignment Pattern (Part 1 of 2) |                    |                             |                                 |  |  |  |

|------------------------------------------------------------------------|--------------------|-----------------------------|---------------------------------|--|--|--|

| BIST Mode                                                              | Output             | Polynomials                 | Verifier Word Alignment Pattern |  |  |  |

| PRBS 8-bit                                                             | 2 <sup>8</sup> – 1 | $x^8 + x^7 + x^5 + x^3 + 1$ | 1000000011111111                |  |  |  |

| PRBS 10-bit                                                            | 210 - 1            | $x^{10} + x^7 + 1$          | 1111111111                      |  |  |  |

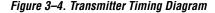

The logic array sends parallel data to the SERDES transmitter circuit when the TXLOADEN signal is asserted. This signal is generated by the high-speed counter circuitry of the logic array low-frequency clock's rising edge. The data is then transferred from the parallel register into the serial shift register by the TXLOADEN signal on the third rising edge of the high-frequency clock.

Figure 3–3 shows the block diagram of a single SERDES transmitter channel and Figure 3–4 shows the timing relationship between the data and clocks in Stratix GX devices in  $\times 10$  mode. W is the low-frequency multiplier and J is the data parallelization division factor.

Transmitter Circuit Parallel Serial Register Register -⊠ TXOUT+ PD9 PD9 PD8 -⊠ TXOUT-PD8 PD7 PD7 PD6 PD6 PD5 PD5 PD4 PD4 PD3 PD3 Stratix GX PD2 PD2 Logic Array PD1 PD1 PD0 PD0  $\times W$ Fast **TXLOADEN PLL**

Figure 3-3. Stratix GX High-Speed Interface Serialized in ×10 Mode

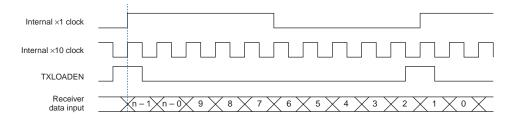

M4K RAM blocks, or DSP blocks from the left and right can also drive an LAB's local interconnect through the direct link connection. The direct link connection feature minimizes the use of row and column interconnects, providing higher performance and flexibility. Each LE can drive 30 other LEs through fast local and direct link interconnects. Figure 4–2 shows the direct link connection.

Figure 4-2. Direct Link Connection

# **LAB Control Signals**

Each LAB contains dedicated logic for driving control signals to its LEs. The control signals include two clocks, two clock enables, two asynchronous clears, synchronous clear, asynchronous preset/load, synchronous load, and add/subtract control signals. This gives a maximum of 10 control signals at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked. For example, any LE in a particular LAB using the labclk1 signal also uses labclkena1. If the LAB uses both the rising and falling edges of a clock, it also uses both LAB-wide clock signals. De-asserting the clock enable signal turns off the LAB-wide clock.

LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix GX devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 4–9 shows the LUT chain and register chain interconnects.

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 4–4 and 4–5 summarize the possible M4K RAM block configurations.

| Table 4–4. M4 | Table 4–4. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|

|               |                                                            | Write Port |          |          |          |          |          |             |          |

| Read Port     | 4K 1                                                       | 2K × 2     | 1K ° 4   | 512 ° 8  | 256 ° 16 | 128 ° 32 | 512 ° 9  | 256 ° 18    | 128 ° 36 |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |

| Table 4–5. M4K RAM | able 4–5. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |  |

|--------------------|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|--|

| Dowl A             |                                                         | Port B   |          |          |          |          |          |  |

| Port A             | 4K × 1                                                  | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |

| 4K × 1             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |

| 2K <b>x</b> 2      | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 1K × 4             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 512 <b>x</b> 8     | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 256 × 16           | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |

| 512 <b>x</b> 9     |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |

| 256 × 18           |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

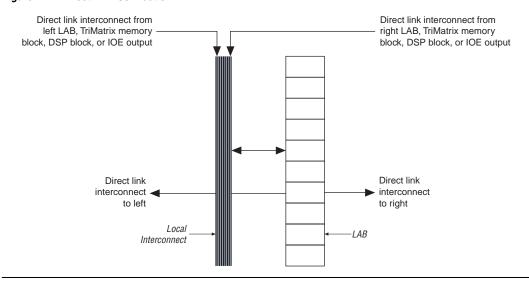

Figure 4–26. Read/Write Clock Mode in Simple Dual-Port Mode Note (1)

*Note to Figure 4–26:*

(1) All registers shown except the rden register have asynchronous clear ports.

# **Single-Port Mode**

The memory blocks also support single-port mode, used when simultaneous reads and writes are not required. See Figure 4–27. A single block in a memory block can support up to two single-port mode RAM blocks in the M4K RAM blocks if each RAM block is less than or equal to 2K bits in size.

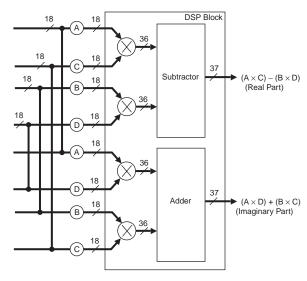

You can use the two-multipliers adder mode for complex multiplications, which are written as:

$$(a+jb)\times(c+jd) = [(a\times c) - (b\times d)] + j\times[(a\times d) + (b\times c)]$$

The two-multipliers adder mode allows a single DSP block to calculate the real part [(a × c) – (b × d)] using one subtractor and the imaginary part [(a × d) + (b × c)] using one adder, for data widths up to 18 bits. Two complex multiplications are possible for data widths up to 9 bits using four adder/subtractor/accumulator blocks. Figure 4–37 shows an 18-bit two-multipliers adder.

Figure 4-37. Two-Multipliers Adder Mode Implementing Complex Multiply

# Four-Multipliers Adder Mode

In the four-multipliers adder mode, the DSP block adds the results of two first -stage adder/subtractor blocks. One sum of four  $18 \times 18$ -bit multipliers or two different sums of two sets of four  $9 \times 9$ -bit multipliers can be implemented in a single DSP block. The product width for each multiplier must be the same size. The four-multipliers adder mode is useful for FIR filter applications. Figure 4–38 shows the four multipliers adder mode.

For FIR filters, the DSP block combines the four-multipliers adder mode with the shift register inputs. One set of shift inputs contains the filter data, while the other holds the coefficients loaded in serial or parallel. The input shift register eliminates the need for shift registers external to the DSP block (that is, implemented in LEs). This architecture simplifies filter design since the DSP block implements all of the filter circuitry.

One DSP block can implement an entire 18-bit FIR filter with up to four taps. For FIR filters larger than four taps, DSP blocks can be cascaded with additional adder stages implemented in LEs.

Table 4–15 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions.

| Table 4–15. Multiplier Size & Configurations per DSP block |                                              |                                            |                                        |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|--|

| DSP Block Mode                                             | 9 × 9                                        | 18 × 18                                    | <b>36</b> × <b>36</b> (1)              |  |  |  |  |

| Multiplier                                                 | Eight multipliers with eight product outputs | Four multipliers with four product outputs | One multiplier with one product output |  |  |  |  |

| Multiply-accumulator                                       | Two multiply and accumulate (52 bits)        | Two multiply and accumulate (52 bits)      | _                                      |  |  |  |  |

| Two-multipliers adder                                      | Four sums of two multiplier products each    | Two sums of two multiplier products each   | _                                      |  |  |  |  |

| Four-multipliers adder                                     | Two sums of four multiplier products each    | One sum of four multiplier products each   | -                                      |  |  |  |  |

Note to Table 4–15:

#### **DSP Block Interface**

Stratix GX device DSP block outputs can cascade down within the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in LEs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in LEs. Each DSP block can route the shift register chain out of the block to cascade two full columns of DSP blocks.

The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

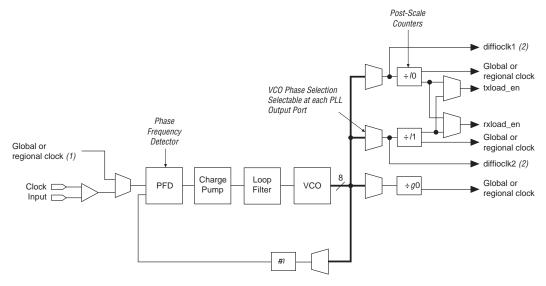

Figure 4-57. Stratix GX Device Fast PLL

#### *Notes to Figure 4–57:*

- In high-speed differential I/O support mode, this high-speed PLL clock feeds the SERDES. Stratix GX devices only support one rate of data transfer per fast PLL in high-speed differential I/O support mode.

- (2) This signal is a high-speed differential I/O support SERDES control signal.

#### Clock Multiplication & Division

The Stratix GX device's fast PLLs provide clock synthesis for PLL output ports using m/(post scaler) scaling factors. The input clock is multiplied by the m feedback factor. Each output port has a unique post scale counter to divide down the high-frequency VCO. There is one multiply divider, m, per fast PLL with a range of 1 to 32. There are two post scale L dividers for regional and/or LVDS interface clocks, and g0 counter for global clock output port; all range from 1 to 32.

In the case of a high-speed differential interface, you can set the output counter to 1 to allow the high-speed VCO frequency to drive the SERDES.

#### External Clock Outputs

Each fast PLL supports differential or single-ended outputs for source-synchronous transmitters or for general-purpose external clocks. There are no dedicated external clock output pins. Any I/O pin can be driven by the fast PLL global or regional outputs as an external output

Table 4–23 shows the number of DQ and DQS buses that are supported per device.

| Table 4–23. | DQS & DQ Bus Mode Support | Note (1)               |                         |                         |

|-------------|---------------------------|------------------------|-------------------------|-------------------------|

| Device      | Package                   | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |

| EP1SGX10    | 672-pin FineLine BGA      | 12 (2)                 | 0                       | 0                       |

| EP1SGX25    | 672-pin FineLine BGA      | 16 (3)                 | 8                       | 4                       |

|             | 1,020-pin FineLine BGA    | 20                     | 8                       | 4                       |

| EP1SGX40    | 1,020-pin FineLine BGA    | 20                     | 8                       | 4                       |

#### Notes to Table 4-23:

- See the Selectable I/O Standards in Stratix & Stratix GX Devices chapter of the Stratix GX Device Handbook, Volume 2 for V<sub>RFF</sub> guidelines.

- (2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

- (3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and clocks DQ input registers with the DQS signal.

Two separate single phase-shifting reference circuits are located on the top and bottom of the Stratix GX device. Each circuit is driven by a system reference clock through the CLK pins that is the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase-shift circuitry on the bottom of the device. The phase-shifting reference circuit on the top of the device controls the compensated delay elements for all 10 DQS pins located at the top of the device. The phase-shifting reference circuit on the bottom of the device controls the compensated delay elements for all 10 DQS pins located on the bottom of the device. All 10 delay elements (DQS signals) on either the top or bottom of the device shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 4–68 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

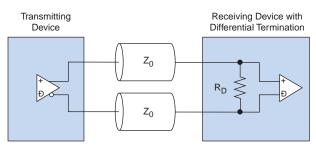

Figure 4-70. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 4–29 shows the Stratix GX device differential termination support.

| Table 4–29. Differential Termination Supported by I/O Banks |                      |                                     |                    |  |  |

|-------------------------------------------------------------|----------------------|-------------------------------------|--------------------|--|--|

| Differential Termination Support                            | I/O Standard Support | Top & Bottom<br>Banks (3, 4, 7 & 8) | Left Banks (1 & 2) |  |  |

| Differential termination (1), (2)                           | LVDS                 |                                     | <b>✓</b>           |  |  |

Notes to Table 4-29:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 4–30 shows the termination support for different pin types.

| Table 4–30. Differential Termination Support Across Pin Types |                |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |

| FCLK                                                          |                |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega\!\pm\!20$  %.

| Table 4–36. Stratix GX JTAG Timing Parameters & Values (Part 2 of 2) |                                                |          |          |  |  |  |

|----------------------------------------------------------------------|------------------------------------------------|----------|----------|--|--|--|

| Symbol                                                               | Parameter                                      | Min (ns) | Max (ns) |  |  |  |

| $t_{JPH}$                                                            | JTAG port hold time                            | 45       |          |  |  |  |

| $t_{\text{JPCO}}$                                                    | JTAG port clock to output                      |          | 25       |  |  |  |

| $t_{JPZX}$                                                           | JTAG port high impedance to valid output       |          | 25       |  |  |  |

| t <sub>JPXZ</sub>                                                    | JTAG port valid output to high impedance       |          | 25       |  |  |  |

| t <sub>JSSU</sub>                                                    | Capture register setup time                    | 20       |          |  |  |  |

| t <sub>JSH</sub>                                                     | Capture register hold time                     | 45       |          |  |  |  |

| tusco                                                                | Update register clock to output                |          | 35       |  |  |  |

| t <sub>JSZX</sub>                                                    | Update register high impedance to valid output |          | 35       |  |  |  |

| t <sub>JSXZ</sub>                                                    | Update register valid output to high impedance |          | 35       |  |  |  |

# **Partial Reconfiguration**

The enhanced PLLs within the Stratix GX device family support partial reconfiguration of their multiply, divide, and time delay settings without reconfiguring the entire device. You can use either serial data from the logic array or regular I/O pins to program the PLL's counter settings in a serial chain. This option provides considerable flexibility for frequency synthesis, allowing real-time variation of the PLL frequency and delay. The rest of the device is functional while reconfiguring the PLL. See the *Stratix GX Architecture* chapter of the *Stratix GX Device Handbook*, *Volume 1* for more information on Stratix GX PLLs.

# **Remote Update Configuration Modes**

Stratix GX devices also support remote configuration using an Altera enhanced configuration device (for example, EPC16, EPC8, and EPC4 devices) with page mode selection. Factory configuration data is stored in the default page of the configuration device. This is the default configuration which contains the design required to control remote updates and handle or recover from errors. You write the factory configuration once into the flash memory or configuration device. Remote update data can update any of the remaining pages of the configuration device. If there is an error or corruption in a remote update configuration, the configuration device reverts back to the factory configuration information.

There are two remote configuration modes: remote and local configuration. You can use the remote update configuration mode for all three configuration modes: serial, parallel synchronous, and parallel asynchronous. Configuration devices (for example, EPC16 devices) only support serial and parallel synchronous modes. Asynchronous parallel mode allows remote updates when an intelligent host is used to configure the Stratix GX device. This host must support page mode settings similar to an EPC16 device.

## Remote Update Mode

When the Stratix GX device is first powered-up in remote update programming mode, it loads the configuration located at page address 000. The factory configuration should always be located at page address 000, and should never be remotely updated. The factory configuration contains the required logic to perform the following operations:

- Determine the page address/load location for the next application's configuration data

- Recover from a previous configuration error

| Table 6–2. Stratix GX Device Recommended Operating Conditions (Part 2 of 2)       Note (7), (12), (13) |                                |                    |         |                   |      |  |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|---------|-------------------|------|--|--|

| Symbol                                                                                                 | Parameter                      | Conditions         | Minimum | Maximum           | Unit |  |  |

| Vo                                                                                                     | Output voltage                 |                    | 0       | V <sub>CCIO</sub> | V    |  |  |

| T <sub>J</sub>                                                                                         | Operating junction temperature | For commercial use | 0       | 85                | ° C  |  |  |

|                                                                                                        |                                | For industrial use | -40     | 100               | ° C  |  |  |

| Table 6–3.                    | Table 6-3. Stratix GX Device DC Operating Conditions   Note (12) |                                |         |         |         |      |  |  |  |

|-------------------------------|------------------------------------------------------------------|--------------------------------|---------|---------|---------|------|--|--|--|

| Symbol                        | Parameter                                                        | Conditions                     | Minimum | Typical | Maximum | Unit |  |  |  |

| l <sub>i</sub>                | Input pin leakage current                                        | $V_I = V_{CCIOmax}$ to 0 V (8) | -10     |         | 10      | μА   |  |  |  |

| l <sub>OZ</sub>               | Tri-stated I/O pin leakage current                               | $V_O = V_{CCIOmax}$ to 0 V (8) | -10     |         | 10      | μА   |  |  |  |

| R <sub>CONF</sub>             | Value of I/O pin pull-                                           | V <sub>CCIO</sub> = 3.0 V (9)  | 20      |         | 50      | kΩ   |  |  |  |

| up resistor before and during | V <sub>CCIO</sub> = 2.375 V (9)                                  | 30                             |         | 80      | kΩ      |      |  |  |  |

|                               | configuration                                                    | V <sub>CCIO</sub> = 1.71 V (9) | 60      |         | 150     | kΩ   |  |  |  |

| Table 6–4. Stratix GX Transceiver Block Absolute Maximum Ratings |                                              |                           |         |                     |       |  |  |

|------------------------------------------------------------------|----------------------------------------------|---------------------------|---------|---------------------|-------|--|--|

| Symbol                                                           | Parameter                                    | Conditions                | Minimum | Maximum             | Units |  |  |

| V <sub>CCA</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 4.6                 | ٧     |  |  |

| V <sub>CCP</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | ٧     |  |  |

| V <sub>CCR</sub>                                                 | Transceiver block supply Voltage             | Commercial and industrial | -0.5    | 2.4                 | ٧     |  |  |

| V <sub>CCT</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | V     |  |  |

| V <sub>CCG</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | V     |  |  |

| Receiver input voltage                                           | V <sub>ICM</sub> ±V <sub>ID</sub> single / 2 | Commercial and industrial |         | 1.675<br>(10), (13) | ٧     |  |  |

| refclkb input<br>voltage                                         | V <sub>ICM</sub> ±V <sub>ID</sub> single / 2 | Commercial and industrial |         | 1.675<br>(10), (13) | V     |  |  |

| Table 6-7. S            | tratix GX Transceiv            | er Blo                           | ck AC S | Specificat                                          | ion (Pa | art 3 of | 7)                                     |         |     |      |    |

|-------------------------|--------------------------------|----------------------------------|---------|-----------------------------------------------------|---------|----------|----------------------------------------|---------|-----|------|----|

| Symbol /<br>Description | Conditions                     | -5 Commercial<br>Speed Grade (1) |         | -6 Commercial &<br>Industrial Speed<br>Grade<br>(1) |         |          | -7 Commercial & Industrial Speed Grade |         |     | Unit |    |

|                         |                                | Min                              | Тур     | Max                                                 | Min     | Тур      | Max                                    | Min     | Тур | Max  |    |

| Sinusoidal<br>jitter    | f = 42.5 kHz at<br>1.0625 Gbps |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 637 kHz at<br>1.0625 Gbps  |                                  |         | 0.1                                                 |         |          | 0.1                                    |         |     | 0.1  | UI |

| Deterministic jitter    | 2.125 Gbps                     |                                  |         | 0.33                                                |         |          | 0.33                                   |         |     | 0.33 | UI |

| Total jitter            | 2.125 Gbps                     |                                  |         | 0.62                                                |         |          | 0.62                                   |         |     | 0.62 | UI |

| Sinusoidal jitter       | f = 85 kHz at<br>2.125 Gbps    |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 1,274 kHz at<br>2.125 Gbps |                                  |         | 0.1                                                 |         |          | 0.1                                    |         |     | 0.1  | UI |

| Serial Rapid            | I/O Receiver Jitter            | Tolera                           | nce usi | ng 8B/10                                            | B Enco  | ded CJF  | PAT No                                 | ote (2) | ,   |      | •  |

| Deterministic jitter    | 1.25 Gbps                      |                                  |         | 0.45                                                |         |          | 0.45                                   |         |     | 0.45 | UI |

| Total jitter            | 1.25 Gbps                      |                                  |         | 0.71                                                |         |          | 0.71                                   |         |     | 0.71 | UI |

| Deterministic jitter    | 2.5 Gbps                       |                                  |         | 0.41                                                |         |          | 0.41                                   |         |     | 0.41 | UI |

| Total jitter            | 2.5 Gbps                       |                                  |         | 0.65                                                |         |          | 0.65                                   |         |     | 0.65 | UI |

| Deterministic jitter    | 3.125 Gbps                     |                                  |         | 0.36                                                |         |          | 0.36                                   |         |     | N/A  | UI |

| Total jitter            | 3.125 Gbps                     |                                  |         | 0.60                                                |         |          | 0.60                                   |         |     | N/A  | UI |

| SONET Receiv            | ver Jitter Tolerance           | using                            | PRBS    | <b>23</b> No                                        | te (2)  |          |                                        |         |     |      |    |

| Sinusoidal<br>jitter    | f = 6 kHz at 2.48832<br>Gbps   |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 1 MHz at<br>2.48832 Gbps   |                                  |         | 0.15                                                |         |          | 0.15                                   |         |     | 0.15 | UI |

| XAUI Receive            | r Jitter Tolerance u           | sing 8                           | B/10B   | Encoded                                             | CJPAT   | Note     | e (2)                                  |         |     |      |    |

| Deterministic jitter    | 3.125 Gbps                     |                                  |         | 0.37                                                |         |          | 0.37                                   |         |     | N/A  | UI |

| Total jitter            | 3.125 Gbps                     |                                  |         | 0.65                                                |         |          | 0.65                                   |         |     | N/A  | UI |

| Table 6–23. SSTL-2 Class I Specifications (Part 2 of 2) |                           |                                |                        |         |                        |       |  |  |  |

|---------------------------------------------------------|---------------------------|--------------------------------|------------------------|---------|------------------------|-------|--|--|--|

| Symbol                                                  | Parameter                 | Conditions                     | Minimum                | Typical | Maximum                | Units |  |  |  |

| V <sub>OH</sub>                                         | High-level output voltage | $I_{OH} = -8.1 \text{ mA}$ (1) | V <sub>TT</sub> + 0.57 |         |                        | V     |  |  |  |

| V <sub>OL</sub>                                         | Low-level output voltage  | I <sub>OL</sub> = 8.1 mA (1)   |                        |         | V <sub>TT</sub> – 0.57 | V     |  |  |  |

| Table 6–24. SSTL-2 Class II Specifications |                           |                                 |                         |                  |                         |       |  |  |  |

|--------------------------------------------|---------------------------|---------------------------------|-------------------------|------------------|-------------------------|-------|--|--|--|

| Symbol                                     | Parameter                 | Conditions                      | Minimum                 | Typical          | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub>                          | Output supply voltage     |                                 | 2.3                     | 2.5              | 2.7                     | ٧     |  |  |  |

| V <sub>TT</sub>                            | Termination voltage       |                                 | V <sub>REF</sub> - 0.04 | V <sub>REF</sub> | V <sub>REF</sub> + 0.04 | V     |  |  |  |

| $V_{REF}$                                  | Reference voltage         |                                 | 1.15                    | 1.25             | 1.35                    | V     |  |  |  |

| V <sub>IH</sub>                            | High-level input voltage  |                                 | V <sub>REF</sub> + 0.18 |                  | V <sub>CCIO</sub> + 0.3 | V     |  |  |  |

| $V_{IL}$                                   | Low-level input voltage   |                                 | -0.3                    |                  | V <sub>REF</sub> - 0.18 | V     |  |  |  |

| V <sub>OH</sub>                            | High-level output voltage | $I_{OH} = -16.4 \text{ mA}$ (1) | V <sub>TT</sub> + 0.76  |                  |                         | V     |  |  |  |

| $V_{OL}$                                   | Low-level output voltage  | I <sub>OL</sub> = 16.4 mA (1)   |                         |                  | V <sub>TT</sub> – 0.76  | V     |  |  |  |

| Table 6–25. SSTL-3 Class I Specifications |                           |                               |                         |                  |                         |       |  |  |

|-------------------------------------------|---------------------------|-------------------------------|-------------------------|------------------|-------------------------|-------|--|--|

| Symbol                                    | Parameter                 | Conditions                    | Minimum                 | Typical          | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                         | Output supply voltage     |                               | 3.0                     | 3.3              | 3.6                     | V     |  |  |

| V <sub>TT</sub>                           | Termination voltage       |                               | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V     |  |  |

| $V_{REF}$                                 | Reference voltage         |                               | 1.3                     | 1.5              | 1.7                     | V     |  |  |

| V <sub>IH</sub>                           | High-level input voltage  |                               | V <sub>REF</sub> + 0.2  |                  | $V_{\rm CCIO} + 0.3$    | V     |  |  |

| V <sub>IL</sub>                           | Low-level input voltage   |                               | -0.3                    |                  | V <sub>REF</sub> - 0.2  | V     |  |  |

| V <sub>OH</sub>                           | High-level output voltage | $I_{OH} = -8 \text{ mA } (1)$ | V <sub>TT</sub> + 0.6   |                  |                         | ٧     |  |  |

| V <sub>OL</sub>                           | Low-level output voltage  | I <sub>OL</sub> = 8 mA (1)    |                         |                  | V <sub>TT</sub> - 0.6   | V     |  |  |

| Table 6–26. SSTL-3 Class II Specifications (Part 1 of 2) |                          |            |                         |           |                      |       |  |  |  |

|----------------------------------------------------------|--------------------------|------------|-------------------------|-----------|----------------------|-------|--|--|--|

| Symbol                                                   | Parameter                | Conditions | Minimum                 | Typical   | Maximum              | Units |  |  |  |

| $V_{CCIO}$                                               | Output supply voltage    |            | 3.0                     | 3.3       | 3.6                  | V     |  |  |  |

| V <sub>TT</sub>                                          | Termination voltage      |            | V <sub>REF</sub> - 0.05 | $V_{REF}$ | $V_{REF} + 0.05$     | ٧     |  |  |  |

| V <sub>REF</sub>                                         | Reference voltage        |            | 1.3                     | 1.5       | 1.7                  | V     |  |  |  |

| $V_{IH}$                                                 | High-level input voltage |            | V <sub>REF</sub> + 0.2  |           | $V_{\rm CCIO} + 0.3$ | V     |  |  |  |

| Table 6–35. Stratix GX Device Performance (Part 2 of 3) Notes (1), (2) |                                      |     |                               |               |                      |                      |                      |       |  |

|------------------------------------------------------------------------|--------------------------------------|-----|-------------------------------|---------------|----------------------|----------------------|----------------------|-------|--|

|                                                                        |                                      |     | Resources L                   | Jsed          |                      | Performance          |                      |       |  |

| Applications                                                           |                                      | LEs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | Units |  |

| TriMatrix memory                                                       | Simple dual-port RAM 32 × 18 bit     | 0   | 1                             | 0             | 317.76               | 277.62               | 241.48               | MHz   |  |

| M512 block                                                             | FIFO 32 × 18 bit                     | 30  | 1                             | 0             | 319.18               | 278.86               | 242.54               | MHz   |  |

| TriMatrix memory                                                       | Simple dual-port RAM 128 × 36 bit    | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |  |

| M4K block                                                              | True dual-port RAM 128 × 18 bit      | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |  |

|                                                                        | FIFO 128 × 36 bit                    | 34  | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |  |

| TriMatrix memory                                                       | Single port<br>RAM 4K × 144 bit      | 1   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |  |

| M-RAM<br>block                                                         | Simple dual-port<br>RAM 4K × 144 bit | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | MHz   |  |

|                                                                        | True dual-port<br>RAM 4K × 144 bit   | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | MHz   |  |

|                                                                        | Single port<br>RAM 8K × 72 bit       | 0   | 1                             | 0             | 278.94               | 243.19               | 211.59               | MHz   |  |

|                                                                        | Simple dual-port<br>RAM 8K × 72 bit  | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |  |

|                                                                        | True dual-port<br>RAM 8K × 72 bit    | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |  |

|                                                                        | Single port<br>RAM 16K × 36 bit      | 0   | 1                             | 0             | 280.66               | 254.32               | 221.28               | MHz   |  |

|                                                                        | Simple dual-port<br>RAM 16K × 36 bit | 0   | 1                             | 0             | 269.83               | 237.69               | 206.82               | MHz   |  |

| Table 6–40. M4K Block Internal Timing Microparameter Descriptions |                                                   |  |  |  |  |

|-------------------------------------------------------------------|---------------------------------------------------|--|--|--|--|

| Symbol                                                            | Parameter                                         |  |  |  |  |

| t <sub>M4KRC</sub>                                                | Synchronous read cycle time                       |  |  |  |  |

| t <sub>M4KWC</sub>                                                | Synchronous write cycle time                      |  |  |  |  |

| t <sub>M4KWERESU</sub>                                            | Write or read enable setup time before clock      |  |  |  |  |

| t <sub>M4KWEREH</sub>                                             | Write or read enable hold time after clock        |  |  |  |  |

| t <sub>M4KBESU</sub>                                              | Byte enable setup time before clock               |  |  |  |  |

| t <sub>M4KBEH</sub>                                               | Byte enable hold time after clock                 |  |  |  |  |

| t <sub>M4KDATAASU</sub>                                           | A port data setup time before clock               |  |  |  |  |

| t <sub>M4KDATAAH</sub>                                            | A port data hold time after clock                 |  |  |  |  |

| t <sub>M4KADDRASU</sub>                                           | A port address setup time before clock            |  |  |  |  |

| t <sub>M4KADDRAH</sub>                                            | A port address hold time after clock              |  |  |  |  |

| t <sub>M4KDATABSU</sub>                                           | B port data setup time before clock               |  |  |  |  |

| t <sub>M4KDATABH</sub>                                            | B port data hold time after clock                 |  |  |  |  |

| t <sub>M4KADDRBSU</sub>                                           | B port address setup time before clock            |  |  |  |  |

| t <sub>M4KADDRBH</sub>                                            | B port address hold time after clock              |  |  |  |  |

| t <sub>M4KDATACO1</sub>                                           | Clock-to-output delay when using output registers |  |  |  |  |

| t <sub>M4KDATACO2</sub>                                           | Clock-to-output delay without output registers    |  |  |  |  |

| t <sub>M4KCLKHL</sub>                                             | Minimum clock high or low time                    |  |  |  |  |

| t <sub>M4KCLR</sub>                                               | Minimum clear pulse width                         |  |  |  |  |

| Table 6–41. M-RAM Block Internal Timing Microparameter<br>Descriptions (Part 1 of 2) |                                              |  |  |  |  |  |

|--------------------------------------------------------------------------------------|----------------------------------------------|--|--|--|--|--|

| Symbol                                                                               | Parameter                                    |  |  |  |  |  |

| t <sub>MRAMRC</sub>                                                                  | Synchronous read cycle time                  |  |  |  |  |  |

| t <sub>MRAMWC</sub>                                                                  | Synchronous write cycle time                 |  |  |  |  |  |

| t <sub>MRAMWERESU</sub>                                                              | Write or read enable setup time before clock |  |  |  |  |  |

| t <sub>MRAMWEREH</sub>                                                               | Write or read enable hold time after clock   |  |  |  |  |  |

| t <sub>MRAMBESU</sub>                                                                | Byte enable setup time before clock          |  |  |  |  |  |

| t <sub>MRAMBEH</sub>                                                                 | Byte enable hold time after clock            |  |  |  |  |  |

| t <sub>MRAMDATAASU</sub>                                                             | A port data setup time before clock          |  |  |  |  |  |

| t <sub>MRAMDATAAH</sub>                                                              | A port data hold time after clock            |  |  |  |  |  |

| t <sub>MRAMADDRASU</sub>                                                             | A port address setup time before clock       |  |  |  |  |  |

| t <sub>MRAMADDRAH</sub>                                                              | A port address hold time after clock         |  |  |  |  |  |