Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 1057                                                       |

| Number of Logic Elements/Cells | 10570                                                      |

| Total RAM Bits                 | 920448                                                     |

| Number of I/O                  | 362                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BBGA                                                   |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx10df672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

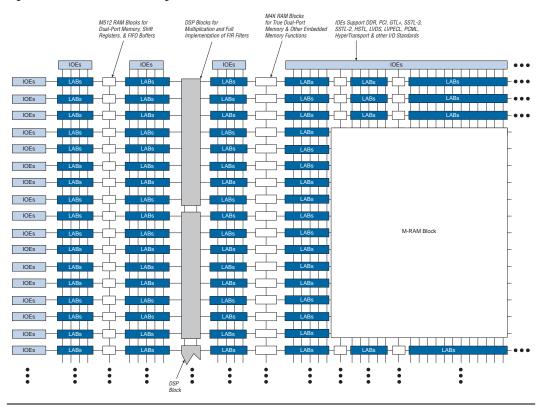

Figure 1–2. Stratix GX Block Diagram

The number of M512 RAM, M4K RAM, and DSP blocks varies by device along with row and column numbers and M-RAM blocks. Table 1–5 lists the resources available in Stratix GX devices.

| Table 1–5. Stratix GX Device Resources                               |         |         |   |      |    |    |  |  |  |

|----------------------------------------------------------------------|---------|---------|---|------|----|----|--|--|--|

| Device M512 RAM Columns/Blocks Columns/Blocks Columns/Blocks Columns |         |         |   |      |    |    |  |  |  |

| EP1SGX10                                                             | 4 / 94  | 2/60    | 1 | 2/6  | 40 | 30 |  |  |  |

| EP1SGX25                                                             | 6 / 224 | 3 / 138 | 2 | 2/10 | 62 | 46 |  |  |  |

| EP1SGX40                                                             | 8 / 384 | 3 / 183 | 4 | 2/14 | 77 | 61 |  |  |  |

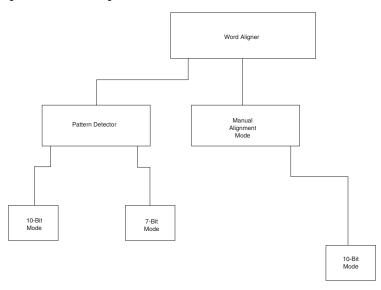

Figure 2-17. Word Aligner in 10-Bit Mode

In the 10-bit mode, the word aligner automatically aligns the user's predefined 10-bit alignment pattern. The pattern detector can detect the full 10-bit pattern or only the lower seven bits of the pattern. The word aligner and pattern detector detect both the positive and the negative disparity of the pattern. A user-controlled enable port is available for the word aligner.

The 10-bit mode is available only for the Custom mode.

Figure 2–18 shows the word aligner in XAUI mode.

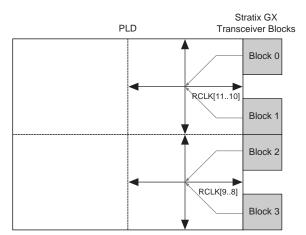

The receiver PLL can also drive the fast regional, regional clocks, and local routing adjacent to the associated transceiver block. Figures 2–28 through 2–31 show which fast regional and regional clock resource can be used by the recovered clock.

In the EP1SGX25 device, the receiver PLL recovered clocks from transceiver blocks 0 and 1 drive RCLK [1..0] while transceiver blocks 2 and 3 drive RCLK [7..6]. The regional clocks feed logic in their associated regions.

Figure 2–28. EP1SGX25 Receiver PLL Recovered Clock to Regional Clock Connection

In addition, the receiver PLL's recovered clocks can drive fast regional lines (FCLK) as shown Figure 2–29. The fast regional clocks can feed logic in their associated regions.

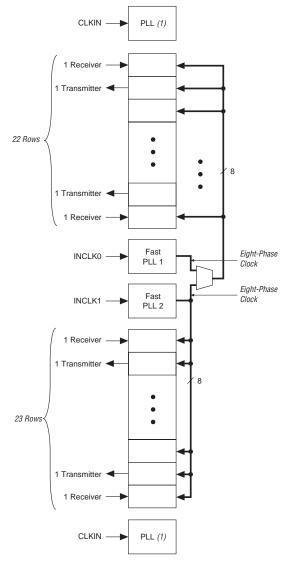

Figure 3–7. PLL & Channel Layout in EP1SGX40 Devices Notes (1), (2), (3)

*Notes to Figure 3–7:*

- (1) Corner PLLs do not support DPA.

- (2) Not all eight phases are used by the receiver channel or transmitter channel in non-DPA mode.

- (3) The center PLLs can only clock 20 transceivers in either direction. Using Fast PLL2, you can clock a total of 40 transceivers, 20 in each direction.

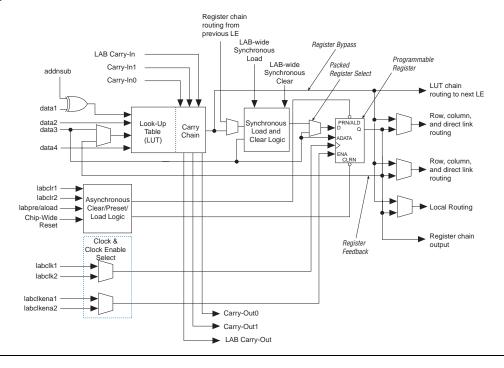

Figure 4-4. Stratix GX LE

Each LE's programmable register can be configured for D, T, JK, or SR operation. Each register has data, true asynchronous load data, clock, clock enable, clear, and asynchronous load/preset inputs. Global signals, general-purpose I/O pins, or any internal logic can drive the register's clock and clear control signals. Either general-purpose I/O pins or internal logic can drive the clock enable, preset, asynchronous load, and asynchronous data. The asynchronous load data input comes from the data3 input of the LE. For combinatorial functions, the register is bypassed and the output of the LUT drives directly to the outputs of the LE.

Each LE has three outputs that drive the local, row, and column routing resources. The LUT or register output can drive these three outputs independently. Two LE outputs drive column or row and direct link routing connections and one drives local interconnect resources. This allows the LUT to drive one output while the register drives another output. This feature, called register packing, improves device utilization because the device can use the register and the LUT for unrelated functions. Another special packing mode allows the register output to feed back into the LUT of the same LE so that the register is packed with

its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

## **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 4–11 for more information on LUT chain and register chain connections.

### addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

# **LE Operating Modes**

The Stratix GX LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset load, synchronous clear, synchronous load, and

LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix GX devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 4–9 shows the LUT chain and register chain interconnects.

Table 4–11 shows the input and output data signal connections for the column units (B1 to B6 and A1 to A6). It also shows the address and control signal input connections to the row units (R1 to R11).

| Table 4–11. M-RAM    | Row & Column Interface Unit                  | Signals         |

|----------------------|----------------------------------------------|-----------------|

| Unit Interface Block | Input Signals                                | Output Signals  |

| R1                   | addressa[70]                                 |                 |

| R2                   | addressa[158]                                |                 |

| R3                   | byte_enable_a[70]<br>renwe_a                 |                 |

| R4                   | -                                            |                 |

| R5                   | -                                            |                 |

| R6                   | clock_a<br>clocken_a<br>clock_b<br>clocken b |                 |

| R7                   | -                                            |                 |

| R8                   | -                                            |                 |

| R9                   | byte_enable_b[70]<br>renwe_b                 |                 |

| R10                  | addressb[158]                                |                 |

| R11                  | addressb[70]                                 |                 |

| B1                   | datain_b[7160]                               | dataout_b[7160] |

| B2                   | datain_b[5948]                               | dataout_b[5948] |

| B3                   | datain_b[4736]                               | dataout_b[4736] |

| B4                   | datain_b[3524]                               | dataout_b[3524] |

| B5                   | datain_b[2312]                               | dataout_b[2312] |

| B6                   | datain_b[110]                                | dataout_b[110]  |

| A1                   | datain_a[7160]                               | dataout_a[7160] |

| A2                   | datain_a[5948]                               | dataout_a[5948] |

| A3                   | datain_a[4736]                               | dataout_a[4736] |

| A4                   | datain_a[3524]                               | dataout_a[3524] |

| A5                   | datain_a[2312]                               | dataout_a[2312] |

| A6                   | datain_a[110]                                | dataout_a[110]  |

# **Independent Clock Mode**

The memory blocks implement independent clock mode for true dual-port memory. In this mode, a separate clock is available for each port (ports A and B). Clock A controls all registers on the port A side, while clock B controls all registers on the port B side. Each port, A and B, also supports independent clock enables and asynchronous clear signals for port A and B registers. Figure 4–23 shows a TriMatrix memory block in independent clock mode.

Fast Clock Fast Clock [1..0]

FCLK[1..0] FCLK[1..0]

FCLK[1..0] FCLK[1..0]

Figure 4–43. EP1SGX25 & EP1SGX10 Device Fast Clock Pin Connections to Fast Regional Clocks

| Table 4–18. Stratix GX Enhanced PLL & Fast PLL Features (Part 2 of 2)       Notes (1)–(8) |                                                                 |     |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|--|--|--|--|--|--|

| Feature                                                                                   | Fast PLL                                                        |     |  |  |  |  |  |  |

| Number of external clock outputs                                                          | Four differential/eight singled-ended or one single-ended $(6)$ | (7) |  |  |  |  |  |  |

| Number of feedback clock inputs                                                           | 4 (8)                                                           |     |  |  |  |  |  |  |

#### Notes to Table 4-18:

- (1) The maximum count value is 1024, with a 50% duty cycle setting on the counter. The maximum count value for any other duty cycle setting is 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the VCO period divided by 8.

- (4) For degree increments, Stratix GX devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7 and 8 have two output ports per PLL. PLLs 1 and 2 have three output ports per PLL.

- (6) Every Stratix GX device has two enhanced PLLs (PLLs 5 and 6) with eight single-ended or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EP1SGX40 devices each have one single-ended output.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix GX device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

Figure 4–48 shows a top-level diagram of the Stratix GX device and the PLL floorplan.

### External Clock Outputs

Enhanced PLLs 5 and 6 each support up to eight single-ended clock outputs (or four differential pairs). See Figure 4–54.

From IOE (1) > extclk0\_a e0 Counter From IOE (1) From IOE (1) e1 Counter From IOE (1) From IOE (1 extclk2\_a e2 Counter extclk2\_b From IOE (1) From IOE (1) e3 Counter extclk3\_b From IOE (1)

Figure 4-54. External Clock Outputs for PLLs 5 & 6

Notes to Figure 4-54:

- Each external clock output pin can be used as a general purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each

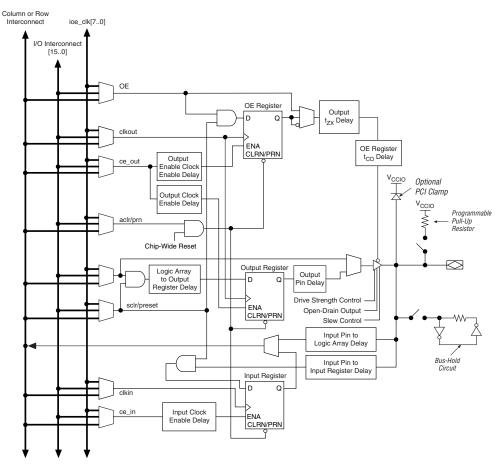

Figure 4–63. Stratix GX IOE in Bidirectional I/O Configuration Note (1)

*Note to Figure 4–63:*

(1) All input signals to the IOE can be inverted at the IOE.

The Stratix GX device IOE includes programmable delays that can be activated to ensure zero hold times, input IOE register-to-logic array register transfers, or logic array-to-output IOE register transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

| Table 4–28. I/O Support by Bank (Part 2 of 2) |                                     |                       |                                                                 |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------|-----------------------|-----------------------------------------------------------------|--|--|--|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left Banks<br>(1 & 2) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |  |  |  |

| SSTL-3 class II                               | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| AGP (1× and 2×)                               | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| СТТ                                           | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

### **Differential On-Chip Termination**

Stratix GX devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

Stratix GX devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 4–70 shows the device with differential termination.

| Table 6-7. S            | tratix GX Transceiv            | er Blo                           | ck AC S | Specificat                                          | ion (Pa | art 3 of | 7)                                     |         |     |      |    |

|-------------------------|--------------------------------|----------------------------------|---------|-----------------------------------------------------|---------|----------|----------------------------------------|---------|-----|------|----|

| Symbol /<br>Description | Conditions                     | -5 Commercial<br>Speed Grade (1) |         | -6 Commercial &<br>Industrial Speed<br>Grade<br>(1) |         |          | -7 Commercial & Industrial Speed Grade |         |     | Unit |    |

|                         |                                | Min                              | Тур     | Max                                                 | Min     | Тур      | Max                                    | Min     | Тур | Max  |    |

| Sinusoidal<br>jitter    | f = 42.5 kHz at<br>1.0625 Gbps |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 637 kHz at<br>1.0625 Gbps  |                                  |         | 0.1                                                 |         |          | 0.1                                    |         |     | 0.1  | UI |

| Deterministic jitter    | 2.125 Gbps                     |                                  |         | 0.33                                                |         |          | 0.33                                   |         |     | 0.33 | UI |

| Total jitter            | 2.125 Gbps                     |                                  |         | 0.62                                                |         |          | 0.62                                   |         |     | 0.62 | UI |

| Sinusoidal jitter       | f = 85 kHz at<br>2.125 Gbps    |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 1,274 kHz at<br>2.125 Gbps |                                  |         | 0.1                                                 |         |          | 0.1                                    |         |     | 0.1  | UI |

| Serial Rapid            | I/O Receiver Jitter            | Tolera                           | nce usi | ng 8B/10                                            | B Enco  | ded CJF  | PAT No                                 | ote (2) |     |      | •  |

| Deterministic jitter    | 1.25 Gbps                      |                                  |         | 0.45                                                |         |          | 0.45                                   |         |     | 0.45 | UI |

| Total jitter            | 1.25 Gbps                      |                                  |         | 0.71                                                |         |          | 0.71                                   |         |     | 0.71 | UI |

| Deterministic jitter    | 2.5 Gbps                       |                                  |         | 0.41                                                |         |          | 0.41                                   |         |     | 0.41 | UI |

| Total jitter            | 2.5 Gbps                       |                                  |         | 0.65                                                |         |          | 0.65                                   |         |     | 0.65 | UI |

| Deterministic jitter    | 3.125 Gbps                     |                                  |         | 0.36                                                |         |          | 0.36                                   |         |     | N/A  | UI |

| Total jitter            | 3.125 Gbps                     |                                  |         | 0.60                                                |         |          | 0.60                                   |         |     | N/A  | UI |

| SONET Receiv            | ver Jitter Tolerance           | using                            | PRBS    | <b>23</b> No                                        | te (2)  |          |                                        |         |     |      |    |

| Sinusoidal<br>jitter    | f = 6 kHz at 2.48832<br>Gbps   |                                  |         | 1.5                                                 |         |          | 1.5                                    |         |     | 1.5  | UI |

|                         | f = 1 MHz at<br>2.48832 Gbps   |                                  |         | 0.15                                                |         |          | 0.15                                   |         |     | 0.15 | UI |

| XAUI Receive            | r Jitter Tolerance u           | sing 8                           | B/10B   | Encoded                                             | CJPAT   | Note     | e (2)                                  |         | _   |      |    |

| Deterministic jitter    | 3.125 Gbps                     |                                  |         | 0.37                                                |         |          | 0.37                                   |         |     | N/A  | UI |

| Total jitter            | 3.125 Gbps                     |                                  |         | 0.65                                                |         |          | 0.65                                   |         |     | N/A  | UI |

| Table 6-7. S            | tratix GX Transceiv                                                                                                       | er Blo | ck AC S         | Specificat | ion (Pa                                             | art 5 of | 7)      |                                        |     |      |      |

|-------------------------|---------------------------------------------------------------------------------------------------------------------------|--------|-----------------|------------|-----------------------------------------------------|----------|---------|----------------------------------------|-----|------|------|

| Symbol /<br>Description | Conditions                                                                                                                | _      | Comm<br>eed Gra |            | -6 Commercial &<br>Industrial Speed<br>Grade<br>(1) |          |         | -7 Commercial & Industrial Speed Grade |     |      | Unit |

|                         |                                                                                                                           | Min    | Тур             | Max        | Min                                                 | Тур      | Max     | Min                                    | Тур | Max  |      |

| Fibre Channe            | l Transmitter Jitter                                                                                                      | using  | 8B/10B          | Encoded    | CRPAT                                               | No       | ote (9) |                                        |     |      |      |

| Deterministic jitter    | 1.0625 Gbps<br>Pre-emphasis = 0                                                                                           |        |                 | 0.09       |                                                     |          | 0.09    |                                        |     | 0.09 | UI   |

| Total jitter            | $V_{OD} = 1,200 \text{ mV}$                                                                                               |        |                 | 0.17       |                                                     |          | 0.17    |                                        |     | 0.17 | UI   |

| Deterministic jitter    | 2.125 Gbps<br>Pre-emphasis= 1                                                                                             |        |                 | 0.16       |                                                     |          | 0.16    |                                        |     | 0.16 | UI   |

| Total jitter            | $V_{OD} = 1,200 \text{ mV}$                                                                                               |        |                 | 0.33       |                                                     |          | 0.33    |                                        |     | 0.33 | UI   |

| Serial Rapid            | /O Short Run Trans                                                                                                        | mitter | Jitter          | using 8B/  | 10B En                                              | coded (  | CRPAT   | Note (                                 | 9)  |      |      |

| Deterministic jitter    | 1.25 Gbps<br>Pre-emphasis = 1                                                                                             |        |                 | 0.09       |                                                     |          | 0.09    |                                        |     | 0.09 | UI   |

| Total jitter            | $V_{OD} = 1,600 \text{ mV}$                                                                                               |        |                 | 0.17       |                                                     |          | 0.17    |                                        |     | 0.17 | UI   |

| Deterministic jitter    | 2.5 Gbps<br>Pre-emphasis = 1                                                                                              |        |                 | 0.15       |                                                     |          | 0.15    |                                        |     | 0.15 | UI   |

| Total jitter            | V <sub>OD</sub> = 800 mV                                                                                                  |        |                 | 0.32       |                                                     |          | 0.32    |                                        |     | 0.32 | UI   |

| Deterministic jitter    | 3.125 Gbps<br>Pre-emphasis = 1                                                                                            |        |                 | 0.15       |                                                     |          | 0.15    |                                        |     | N/A  | UI   |

| Total jitter            | $V_{OD} = 800 \text{ mV}$                                                                                                 |        |                 | 0.32       |                                                     |          | 0.32    |                                        |     | N/A  | UI   |

| Serial Rapid            | /O Long Run Trans                                                                                                         | mitter | Jitter ı        | ising 8B/1 | OB End                                              | oded C   | RPAT    | Note (9                                | 9)  |      |      |

| Deterministic jitter    | 1.25 Gbps<br>Pre-emphasis = 1                                                                                             |        |                 | 0.09       |                                                     |          | 0.09    |                                        |     | 0.09 | UI   |

| Total jitter            | $V_{OD} = 1,600 \text{ mV}$                                                                                               |        |                 | 0.17       |                                                     |          | 0.17    |                                        |     | 0.17 | UI   |

| Deterministic jitter    | 2.5 Gbps<br>Pre-emphasis = 2                                                                                              |        |                 | 0.18       |                                                     |          | 0.18    |                                        |     | 0.18 | UI   |

| Total jitter            | $V_{OD} = 1,400 \text{ mV}$                                                                                               |        |                 | 0.35       |                                                     |          | 0.35    |                                        |     | 0.35 | UI   |

| Deterministic jitter    | 3.125 Gbps<br>Pre-emphasis = 2                                                                                            |        |                 | 0.20       |                                                     |          | 0.20    |                                        |     | N/A  | UI   |

| Total jitter            | $V_{OD} = 1,400 \text{ mV}$                                                                                               |        |                 | 0.37       |                                                     |          | 0.37    |                                        |     | N/A  | UI   |

| SONET Transi            | nitter Jitter PRBS2                                                                                                       | 3 /    | Note (9)        | )          |                                                     |          |         |                                        |     |      |      |

| Total jitter            | $ \begin{array}{l} 2.48832 \text{ Gbps} \\ \text{Pre-emphasis} = 1 \\ \text{V}_{\text{OD}} = 800 \text{ mV} \end{array} $ |        |                 | 0.20       |                                                     |          | 0.20    |                                        |     | 0.20 | UI   |

| Table 6-35          | 5. Stratix GX Device Performance     | (Part | 3 of 3)                       | Notes (1      | '), (2)              |                      |                      |       |

|---------------------|--------------------------------------|-------|-------------------------------|---------------|----------------------|----------------------|----------------------|-------|

|                     |                                      | F     | Resources L                   | Jsed          | Performance          |                      |                      |       |

|                     | Applications                         | LEs   | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | Units |

| TriMatrix<br>memory | True dual-port<br>RAM 16K × 36 bit   | 0     | 1                             | 0             | 269.83               | 237.69               | 206.82               | MHz   |

| M-RAM<br>block      | Single port<br>RAM 32K × 18 bit      | 0     | 1                             | 0             | 275.86               | 244.55               | 212.76               | MHz   |

|                     | Simple dual-port<br>RAM 32K × 18 bit | 0     | 1                             | 0             | 275.86               | 244.55               | 212.76               | MHz   |

|                     | True dual-port<br>RAM 32K × 18 bit   | 0     | 1                             | 0             | 275.86               | 244.55               | 212.76               | MHz   |

|                     | Single port<br>RAM 64K × 9 bit       | 0     | 1                             | 0             | 287.85               | 253.29               | 220.36               | MHz   |

|                     | Simple dual-port<br>RAM 64K × 9 bit  | 0     | 1                             | 0             | 287.85               | 253.29               | 220.36               | MHz   |

|                     | True dual-port<br>RAM 64K × 9 bit    | 0     | 1                             | 0             | 287.85               | 253.29               | 220.36               | MHz   |

| DSP block           | 9 × 9-bit multiplier (3)             | 0     | 0                             | 1             | 335.0                | 293.94               | 255.68               | MHz   |

|                     | 18 × 18-bit multiplier (4)           | 0     | 0                             | 1             | 278.78               | 237.41               | 206.52               | MHz   |

|                     | 36 × 36-bit multiplier (4)           | 0     | 0                             | 1             | 148.25               | 134.71               | 117.16               | MHz   |

|                     | 36 × 36-bit multiplier (5)           | 0     | 0                             | 1             | 278.78               | 237.41               | 206.52               | MHz   |

|                     | 18-bit, 4-tap FIR filter             | 0     | 0                             | 1             | 278.78               | 237.41               | 206.52               | MHz   |

| Larger              | 8-bit, 16-tap parallel FIR filter    | 58    | 0                             | 4             | 141.26               | 133.49               | 114.88               | MHz   |

| Designs             | 8-bit, 1,024-point FFT function      | 870   | 5                             | 1             | 261.09               | 235.51               | 205.21               | MHz   |

### Notes to Table 6-35:

- (1) These design performance numbers were obtained using the Quartus II software.

- (2) Numbers not listed will be included in a future version of the data sheet.

- (3) This application uses registered inputs and outputs.

- (4) This application uses registered multiplier input and output stages within the DSP block.

- (5) This application uses registered multiplier input, pipeline, and output stages within the DSP block.

| Table 6–53. Stratix GX Global Clock External I/O Timing Parameters (Part 2 of 2)       Notes (1), (2) |                                                                                                                                              |                           |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|--|

| Symbol                                                                                                | Parameter                                                                                                                                    | Conditions                |  |  |  |  |  |

| t <sub>INHPLL</sub>                                                                                   | Hold time for input or bidirectional pin using column IOE input register with global clock fed by enhanced PLL with default phase setting    |                           |  |  |  |  |  |

| toutcople                                                                                             | Clock-to-output delay output or bidirectional pin using column IOE output register with global clock enhanced PLL with default phase setting | C <sub>LOAD</sub> = 10 pF |  |  |  |  |  |

#### Notes to Table 6-53:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column IOE pins. Row IOE pins are 100- to 250-ps slower depending on device, speed grade, and the specific parameter in question. You should use the Quartus II software to verify the external timing for any pin.

Tables 6-54 through 6-59 show the external timing parameters on column and row pins for EP1SGX10 devices.

| Table 6–54. EP1SGX10 Column Pin Fast Regional Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |  |

|------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|

| Cumbal                                                                             | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee |       |      |  |  |

| Symbol                                                                             | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>                                                                  | 2.245   |         | 2.332   |         | 2.666   |       | ns   |  |  |

| t <sub>INH</sub>                                                                   | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCO</sub>                                                                 | 2.000   | 4.597   | 2.000   | 4.920   | 2.000   | 5.635 | ns   |  |  |

| Table 6–55. EP1SGX10 Column Pin Regional Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |

|-------------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|

| O                                                                             | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee |       |      |  |

| Symbol                                                                        | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |

| t <sub>INSU</sub>                                                             | 2.114   |         | 2.218   |         | 2.348   |       | ns   |  |

| t <sub>INH</sub>                                                              | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |

| t <sub>outco</sub>                                                            | 2.000   | 4.728   | 2.000   | 5.078   | 2.000   | 6.004 | ns   |  |

| t <sub>INSUPLL</sub>                                                          | 1.035   |         | 0.941   |         | 1.070   |       | ns   |  |

| t <sub>INHPLL</sub>                                                           | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |

| t <sub>OUTCOPLL</sub>                                                         | 0.500   | 2.629   | 0.500   | 2.769   | 0.500   | 3.158 | ns   |  |

| Table 6–71. EP1SGX40 Row Pin Global Clock External I/O Timing Parameters (Part 2 of 2) |         |         |         |         |         |         |      |  |  |

|----------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|------|--|--|

| Cumbal                                                                                 | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade |      |  |  |

| Symbol                                                                                 | Min     | Max     | Min     | Max     | Min     | Max     | Unit |  |  |

| t <sub>OUTCO</sub>                                                                     | 2.000   | 5.365   | 2.000   | 5.775   | 2.000   | 6.621   | ns   |  |  |

| t <sub>INSUPLL</sub>                                                                   | 1.126   |         | 1.186   |         | 1.352   |         | ns   |  |  |

| t <sub>INHPLL</sub>                                                                    | 0.000   |         | 0.000   |         | 0.000   |         | ns   |  |  |

| t <sub>OUTCOPLL</sub>                                                                  | 0.500   | 2.304   | 0.500   | 2.427   | 0.500   | 2.765   | ns   |  |  |

# External I/O Delay Parameters

External I/O delay timing parameters, both for I/O standard input and output adders and programmable input and output delays, are specified by speed grade, independent of device density.

Tables 6–72 through 6–77 show the adder delays associated with column and row I/O pins. If an I/O standard is selected other than LVTTL 24 mA with a fast slew rate, add the selected delay to the external  $t_{CO}$  and  $t_{SU}$  I/O parameters.

| Table 6–72. Stratix GX I/O Standard Column Pin Input Delay Adders (Part 1 of 2) |        |                |     |                |     |                |      |  |  |  |  |

|---------------------------------------------------------------------------------|--------|----------------|-----|----------------|-----|----------------|------|--|--|--|--|

| I/O Standard                                                                    | -5 Spe | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |      |  |  |  |  |

|                                                                                 | Min    | Max            | Min | Max            | Min | Max            | Unit |  |  |  |  |

| LVCMOS                                                                          |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| 3.3-V LVTTL                                                                     |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| 2.5-V LVTTL                                                                     |        | 30             |     | 31             |     | 35             | ps   |  |  |  |  |

| 1.8-V LVTTL                                                                     |        | 150            |     | 157            |     | 180            | ps   |  |  |  |  |

| 1.5-V LVTTL                                                                     |        | 210            |     | 220            |     | 252            | ps   |  |  |  |  |

| GTL                                                                             |        | 220            |     | 231            |     | 265            | ps   |  |  |  |  |

| GTL+                                                                            |        | 220            |     | 231            |     | 265            | ps   |  |  |  |  |

| 3.3-V PCI                                                                       |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| 3.3-V PCI-X 1.0                                                                 |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| Compact PCI                                                                     |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| AGP 1×                                                                          |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| AGP 2×                                                                          |        | 0              |     | 0              |     | 0              | ps   |  |  |  |  |

| CTT                                                                             |        | 120            |     | 126            |     | 144            | ps   |  |  |  |  |

| SSTL-3 class I                                                                  |        | -30            |     | -32            |     | -37            | ps   |  |  |  |  |

| SSTL-3 class II                                                                 |        | -30            |     | -32            |     | -37            | ps   |  |  |  |  |

Tables 6–78 and 6–79 show the adder delays for the column and row IOE programmable delays, respectively. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Parameter                                 | Setting | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       |      |

|-------------------------------------------|---------|----------------|-------|----------------|-------|----------------|-------|------|

|                                           |         | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| Decrease input delay to internal cells    | Off     |                | 3,970 |                | 4,367 |                | 5,022 | ps   |

|                                           | On      |                | 3,390 |                | 3,729 |                | 4,288 | ps   |

|                                           | Small   |                | 2,810 |                | 3,091 |                | 3,554 | ps   |

|                                           | Medium  |                | 212   |                | 224   |                | 257   | ps   |

|                                           | Large   |                | 212   |                | 224   |                | 257   | ps   |

| Decrease input delay to input register    | Off     |                | 3900  |                | 4,290 |                | 4,933 | ps   |

|                                           | On      |                | 0     |                | 0     |                | 0     | ps   |

| Decrease input delay to output register   | Off     |                | 1,240 |                | 1,364 |                | 1,568 | ps   |

|                                           | On      |                | 0     |                | 0     |                | 0     | ps   |

| Increase delay to output pin              | Off     |                | 0     |                | 0     |                | 0     | ps   |

|                                           | On      |                | 377   |                | 397   |                | 456   | ps   |

| Increase delay to output enable pin       | Off     |                | 0     |                | 0     |                | 0     | ps   |

|                                           | On      |                | 338   |                | 372   |                | 427   | ps   |

| Increase output clock enable delay        | Off     |                | 0     |                | 0     |                | 0     | ps   |

|                                           | On      |                | 540   |                | 594   |                | 683   | ps   |

|                                           | Small   |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                                           | Large   |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

| Increase input clock enable delay         | Off     |                | 0     |                | 0     |                | 0     | ps   |

|                                           | On      |                | 540   |                | 594   |                | 683   | ps   |

|                                           | Small   |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                                           | Large   |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

| Increase output enable clock enable delay | Off     |                | 0     |                | 0     |                | 0     | ps   |

|                                           | On      |                | 540   |                | 594   |                | 683   | ps   |

|                                           | Small   |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                                           | Large   |                | 1,016 | _              | 1,118 |                | 1,285 | ps   |