Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1057                                                        |

| Number of Logic Elements/Cells | 10570                                                       |

| Total RAM Bits                 | 920448                                                      |

| Number of I/O                  | 362                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 672-BBGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx10df672c7n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Power-down functions are static, in other words., they are implemented upon device configuration and programmed, through the Quartus II software, to static values. Resets can be static as well as dynamic inputs coming from the logic array or pins.

| Table 2–11. Reset Si | Table 2–11. Reset Signal Map to Stratix GX Blocks           |                            |                        |                             |                 |                                |                             |                 |                       |                       |                             |                       |                         |                                                    |                    |                             |                |                          |

|----------------------|-------------------------------------------------------------|----------------------------|------------------------|-----------------------------|-----------------|--------------------------------|-----------------------------|-----------------|-----------------------|-----------------------|-----------------------------|-----------------------|-------------------------|----------------------------------------------------|--------------------|-----------------------------|----------------|--------------------------|

| Reset Signal         | Transmitter Phase Compensation FIFO Module/ Byte Serializer | Transmitter 8B/10B Encoder | Transmitter Serializer | Transmitter Analog Circuits | Transmitter PLL | Transmitter XAUI State Machine | Transmitter Analog Circuits | BIST Generators | Receiver Deserializer | Receiver Word Aligner | Receiver Deskew FIFO Module | Receiver Rate Matcher | Receiver 8B/10B Decoder | Receiver Phase Comp FIFO Module/ Byte Deserializer | Receiver PLL / CRU | Receiver XAUI State Machine | BIST Verifiers | Receiver Analog Circuits |

| rxdigitalreset       |                                                             |                            |                        |                             |                 |                                |                             |                 |                       | <b>\</b>              | <b>✓</b>                    | <b>\</b>              | <b>\</b>                | <b>\</b>                                           |                    | <                           | <              |                          |

| rxanalogreset        |                                                             |                            |                        |                             |                 |                                |                             |                 | <b>&gt;</b>           |                       |                             |                       |                         |                                                    | <b>&gt;</b>        |                             |                | <b>✓</b>                 |

| txdigitalreset       | <b>✓</b>                                                    | <b>✓</b>                   |                        |                             |                 | <b>&gt;</b>                    |                             | <b>&gt;</b>     |                       |                       |                             |                       |                         |                                                    |                    |                             |                |                          |

| pll_areset           | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>        | <b>✓</b>                       | <b>\</b>                    | <b>\</b>        | <b>\</b>              | <b>\</b>              | <b>✓</b>                    | <b>\</b>              | <b>\</b>                | <b>\</b>                                           | <b>\</b>           | <b>✓</b>                    | <b>\</b>       | <b>✓</b>                 |

| pllenable            | <b>✓</b>                                                    | <b>✓</b>                   | <b>✓</b>               | <b>✓</b>                    | <b>✓</b>        | <b>✓</b>                       | <b>✓</b>                    | <b>✓</b>        | <b>✓</b>              | <b>✓</b>              | <b>✓</b>                    | <b>✓</b>              | <b>✓</b>                | <b>✓</b>                                           | <b>✓</b>           | <b>✓</b>                    | <b>✓</b>       | <b>✓</b>                 |

# **Voltage Reference Capabilities**

Stratix GX transceivers provide voltage reference and bias circuitry. To set-up internal bias for controlling the transmitter output drivers' voltage swing—as well as to provide voltage/current biasing for other analog circuitry—use the internal bandgap voltage reference at 0.7 V. To provide bias for internal pull-up PMOS resistors for I/O termination at the serial interface of receiver and transmitter channels (independent of power supply drift, process changes, or temperature variation) an external resistor, which is connected to the external low voltage power supply, is

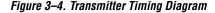

The logic array sends parallel data to the SERDES transmitter circuit when the TXLOADEN signal is asserted. This signal is generated by the high-speed counter circuitry of the logic array low-frequency clock's rising edge. The data is then transferred from the parallel register into the serial shift register by the TXLOADEN signal on the third rising edge of the high-frequency clock.

Figure 3–3 shows the block diagram of a single SERDES transmitter channel and Figure 3–4 shows the timing relationship between the data and clocks in Stratix GX devices in  $\times 10$  mode. W is the low-frequency multiplier and J is the data parallelization division factor.

Transmitter Circuit Parallel Serial Register Register -⊠ TXOUT+ PD9 PD9 PD8 -⊠ TXOUT-PD8 PD7 PD7 PD6 PD6 PD5 PD5 PD4 PD4 PD3 PD3 Stratix GX PD2 PD2 Logic Array PD1 PD1 PD0 PD0  $\times W$ Fast **TXLOADEN PLL**

Figure 3-3. Stratix GX High-Speed Interface Serialized in ×10 Mode

have four dedicated fast PLLs for clock multiplication. Table 3–3 shows the maximum number of channels in each Stratix GX device that support DPA.

| Table 3–3. Strat | Table 3–3. Stratix GX Source-Synchronous Differential I/O Resources |           |                      |                                |                                                          |        |  |  |  |  |  |  |  |

|------------------|---------------------------------------------------------------------|-----------|----------------------|--------------------------------|----------------------------------------------------------|--------|--|--|--|--|--|--|--|

| Device           | Fast PLLs                                                           | Pin Count | Receiver<br>Channels | Transmitter<br>Channels<br>(1) | Receiver &<br>Transmitter<br>Channel Speed<br>(Gbps) (2) | LEs    |  |  |  |  |  |  |  |

| EP1SGX10C        | 2 (3)                                                               | 672       | 22                   | 22                             | 1                                                        | 10,570 |  |  |  |  |  |  |  |

| EP1SGX10D        | 2 (3)                                                               | 672       | 22                   | 22                             | 1                                                        | 10,570 |  |  |  |  |  |  |  |

| EP1SGX25C        | 2                                                                   | 672       | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |  |  |  |  |

| EP1SGX25D        | 2                                                                   | 672       | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |  |  |  |  |

|                  |                                                                     | 1,020     | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |  |  |  |  |

| EP1SGX25F        | 2                                                                   | 1,020     | 39                   | 39                             | 1                                                        | 25,660 |  |  |  |  |  |  |  |

| EP1SGX40D        | 4 (4)                                                               | 1,020     | 45                   | 45                             | 1                                                        | 41,250 |  |  |  |  |  |  |  |

| EP1SGX40G        | 4 (4)                                                               | 1,020     | 45                   | 45                             | 1                                                        | 41,250 |  |  |  |  |  |  |  |

#### Notes to Table 3-3:

- (1) This is the number of receiver or transmitter channels in the source-synchronous (I/O bank 1 and 2) interface of the device.

- (2) Receiver channels operate at 1,000 Mbps with DPA. Without DPA, the receiver channels operate at 840 Mbps.

- (3) One of the two fast PLLs in EP1SGX10C and EP1SGX10D devices supports DPA.

- (4) Two of the four fast PLLs in EP1SGX40D and EP1SGX40G devices support DPA

The receiver and transmitter channels are interleaved so that each I/O row in I/O banks 1 and 2 of the device has one receiver channel and one transmitter channel per row. Figures 3–6 and 3–7 show the fast PLL and channels with DPA layout in EP1SGX10, EP1SGX25, and EP1SGX40 devices. In EP1SGX10 devices, only fast PLL 2 supports DPA operations.

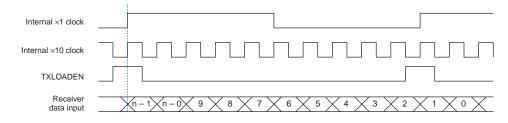

Figure 4-9. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 4–10 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

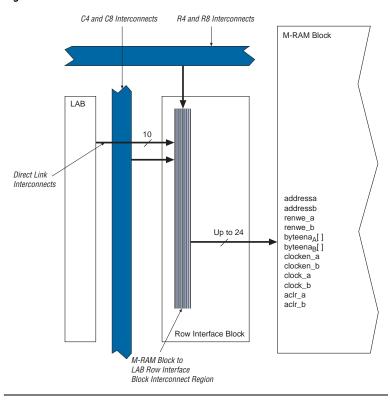

Figure 4–21. M-RAM Row Unit Interface to Interconnect

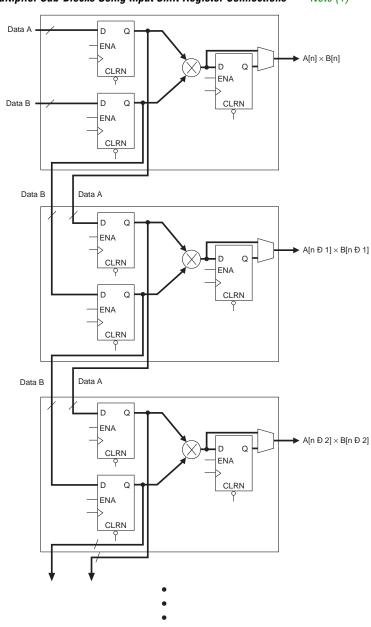

Figure 4–32. Multiplier Sub-Blocks Using Input Shift Register Connections Note (1)

*Note to Figure 4–32:*

(1) Either Data A or Data B input can be set to a parallel input for constant coefficient multiplication.

For FIR filters, the DSP block combines the four-multipliers adder mode with the shift register inputs. One set of shift inputs contains the filter data, while the other holds the coefficients loaded in serial or parallel. The input shift register eliminates the need for shift registers external to the DSP block (that is, implemented in LEs). This architecture simplifies filter design since the DSP block implements all of the filter circuitry.

One DSP block can implement an entire 18-bit FIR filter with up to four taps. For FIR filters larger than four taps, DSP blocks can be cascaded with additional adder stages implemented in LEs.

Table 4–15 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions.

| Table 4–15. Multiplier Size & Configurations per DSP block |                                              |                                            |                                        |  |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|--|--|--|--|--|

| DSP Block Mode                                             | 9 × 9                                        | 18 × 18                                    | <b>36</b> × <b>36</b> (1)              |  |  |  |  |  |  |  |  |

| Multiplier                                                 | Eight multipliers with eight product outputs | Four multipliers with four product outputs | One multiplier with one product output |  |  |  |  |  |  |  |  |

| Multiply-accumulator                                       | Two multiply and accumulate (52 bits)        | Two multiply and accumulate (52 bits)      | _                                      |  |  |  |  |  |  |  |  |

| Two-multipliers adder                                      | Four sums of two multiplier products each    | Two sums of two multiplier products each   | _                                      |  |  |  |  |  |  |  |  |

| Four-multipliers adder                                     | Two sums of four multiplier products each    | One sum of four multiplier products each   | -                                      |  |  |  |  |  |  |  |  |

Note to Table 4–15:

#### **DSP Block Interface**

Stratix GX device DSP block outputs can cascade down within the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in LEs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in LEs. Each DSP block can route the shift register chain out of the block to cascade two full columns of DSP blocks.

The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

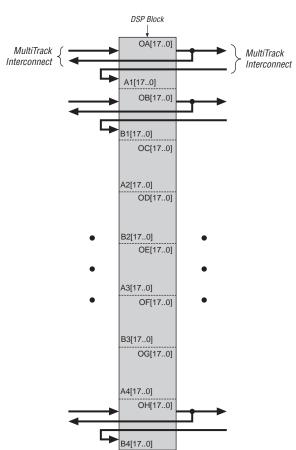

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 4–39 and 4–40 show the DSP block interfaces to LAB rows.

Figure 4-39. DSP Block Interconnect Interface

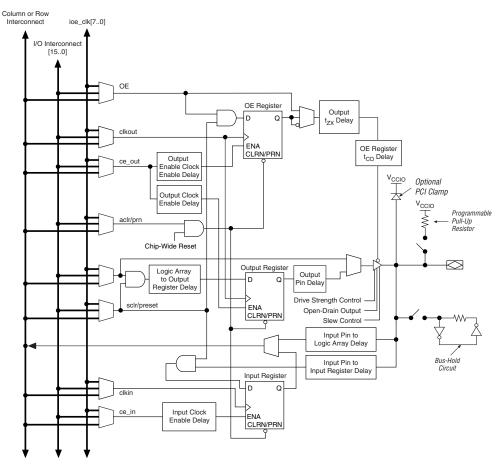

Figure 4–63. Stratix GX IOE in Bidirectional I/O Configuration Note (1)

*Note to Figure 4–63:*

(1) All input signals to the IOE can be inverted at the IOE.

The Stratix GX device IOE includes programmable delays that can be activated to ensure zero hold times, input IOE register-to-logic array register transfers, or logic array-to-output IOE register transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

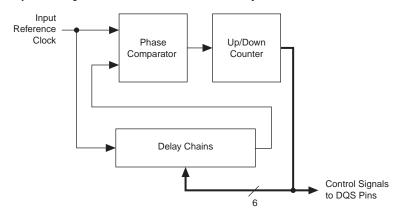

Figure 4-68. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter of the *Stratix GX Device Handbook, Volume 2* for more information on external memory interfaces.

## **Programmable Drive Strength**

The output buffer for each Stratix GX device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 class I and II, SSTL-2 class I and II, HSTL class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

Receive new configuration data and write it into the configuration device

The factory configuration is the default and takes control if an error occurs while loading the application configuration.

While in the factory configuration, the factory-configuration logic performs the following operations:

- Loads a remote update-control register to determine the page address of the new application configuration

- Determines whether to enable a user watchdog timer for the application configuration

- Determines what the watchdog timer setting should be if it is enabled

The user watchdog timer is a counter that must be continually reset within a specific amount of time in the user mode of an application configuration to ensure that valid configuration occurred during a remote update. Only valid application configurations designed for remote update can reset the user watchdog timer in user mode. If a valid application configuration does not reset the user watchdog timer in a specific amount of time, the timer updates a status register and loads the factory configuration. The user watchdog timer is automatically disabled for factory configurations.

If an error occurs in loading the application configuration, the configuration logic writes a status register to specify the cause of the reconfiguration. Once this occurs, the Stratix GX device automatically loads the factory configuration, which reads the status register and determines the reason for reconfiguration. Based on the reason, the factory configuration takes appropriate steps and writes the remote update control register to specify the next application configuration page to be loaded.

When the Stratix GX device successfully loads the application configuration, it enters into user mode. The Stratix GX device then executes the main application of the user. Intellectual property (IP), such as a Nios® embedded processor, can help the Stratix GX device determine when remote update is coming. The Nios embedded processor or user logic receives incoming data, writes it to the configuration device, and loads the factory configuration. The factory configuration reads the remote update status register and determine the valid application configuration to load. Figure 5–1 shows the Stratix GX remote update. Figure 5–2 shows the transition diagram for remote update mode.

## **Internal Timing Parameters**

Internal timing parameters are specified on a speed grade basis independent of device density. Tables 6–36 through 6–42 describe the Stratix GX device internal timing microparameters for LEs, IOEs, TriMatrix  $^{\text{TM}}$  memory structures, DSP blocks, and MultiTrack interconnects.

| Table 6–36. LE Internal Timing Microparameter Descriptions |                                                    |  |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|--|--|

| Symbol                                                     | Parameter                                          |  |  |  |  |  |  |  |

| t <sub>SU</sub>                                            | LE register setup time before clock                |  |  |  |  |  |  |  |

| t <sub>H</sub>                                             | LE register hold time after clock                  |  |  |  |  |  |  |  |

| t <sub>CO</sub>                                            | LE register clock-to-output delay                  |  |  |  |  |  |  |  |

| t <sub>LUT</sub>                                           | LE combinational LUT delay for data-in to data-out |  |  |  |  |  |  |  |

| t <sub>CLR</sub>                                           | Minimum clear pulse width                          |  |  |  |  |  |  |  |

| t <sub>PRE</sub>                                           | Minimum preset pulse width                         |  |  |  |  |  |  |  |

| t <sub>CLKHL</sub>                                         | Minimum clock high or low time                     |  |  |  |  |  |  |  |

| Table 6–37. IOE Internal Timing Microparameter Descriptions |                                                       |  |  |  |  |  |  |

|-------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|--|--|

| Symbol                                                      | Parameter                                             |  |  |  |  |  |  |

| t <sub>SU</sub>                                             | IOE input and output register setup time before clock |  |  |  |  |  |  |

| t <sub>H</sub>                                              | IOE input and output register hold time after clock   |  |  |  |  |  |  |

| t <sub>CO</sub>                                             | IOE input and output register clock-to-output delay   |  |  |  |  |  |  |

| t <sub>PIN2COMBOUT_R</sub>                                  | Row input pin to IOE combinational output             |  |  |  |  |  |  |

| t <sub>PIN2COMBOUT_C</sub>                                  | Column input pin to IOE combinational output          |  |  |  |  |  |  |

| t <sub>COMBIN2PIN_R</sub>                                   | Row IOE data input to combinational output pin        |  |  |  |  |  |  |

| t <sub>COMBIN2PIN_C</sub>                                   | Column IOE data input to combinational output pin     |  |  |  |  |  |  |

| t <sub>CLR</sub>                                            | Minimum clear pulse width                             |  |  |  |  |  |  |

| t <sub>PRE</sub>                                            | Minimum preset pulse width                            |  |  |  |  |  |  |

| t <sub>CLKHL</sub>                                          | Minimum clock high or low time                        |  |  |  |  |  |  |

Figure 6-5. Stratix GX Transceiver Reset & PLL Lock Time Waveform Note (1)

#### Note to Figure 6-5:

(1) Waveforms are for minimum pulse width timing and output timing only. Please refer to the *Stratix GX Transceiver User Guide* for the complete reset sequence.

Tables 6–44 through 6–50 show the internal timing microparameters for all Stratix GX devices.

| Table 6–44. LE Internal Timing Microparameters |         |         |         |         |         |     |      |  |  |  |  |

|------------------------------------------------|---------|---------|---------|---------|---------|-----|------|--|--|--|--|

| Symbol                                         | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | 11  |      |  |  |  |  |

|                                                | Min     | Max     | Min     | Max     | Min     | Max | Unit |  |  |  |  |

| t <sub>SU</sub>                                | 10      |         | 10      |         | 11      |     | ps   |  |  |  |  |

| t <sub>H</sub>                                 | 100     |         | 100     |         | 114     |     | ps   |  |  |  |  |

| t <sub>CO</sub>                                |         | 156     |         | 176     |         | 202 | ps   |  |  |  |  |

| t <sub>LUT</sub>                               |         | 366     |         | 459     |         | 527 | ps   |  |  |  |  |

| t <sub>CLR</sub>                               | 100     |         | 100     |         | 114     |     | ps   |  |  |  |  |

| t <sub>PRE</sub>                               | 100     |         | 100     |         | 114     |     | ps   |  |  |  |  |

| t <sub>CLKHL</sub>                             | 100     |         | 100     |         | 114     |     | ps   |  |  |  |  |

| Table 6–45. IOE Internal Timing Microparameters |         |         |         |         |         |       |      |  |  |  |

|-------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|--|

| Cumbal                                          | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | llmi4 |      |  |  |  |

| Symbol                                          | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |  |

| t <sub>SU</sub>                                 | 64      |         | 68      |         | 68      |       | ps   |  |  |  |

| t <sub>H</sub>                                  | 76      |         | 80      |         | 80      |       | ps   |  |  |  |

| t <sub>CO</sub>                                 |         | 162     |         | 171     |         | 171   | ps   |  |  |  |

| t <sub>PIN2COMBOUT_R</sub>                      |         | 1,038   |         | 1,093   |         | 1,256 | ps   |  |  |  |

| t <sub>PIN2COMBOUT_C</sub>                      |         | 927     |         | 976     |         | 1,122 | ps   |  |  |  |

| t <sub>COMBIN2PIN_R</sub>                       |         | 2,944   |         | 3,099   |         | 3,563 | ps   |  |  |  |

| t <sub>COMBIN2PIN_C</sub>                       |         | 3,189   |         | 3,357   |         | 3,860 | ps   |  |  |  |

| t <sub>CLR</sub>                                | 262     |         | 276     |         | 317     |       | ps   |  |  |  |

| t <sub>PRE</sub>                                | 262     |         | 276     |         | 317     |       | ps   |  |  |  |

| t <sub>CLKHL</sub>                              | 90      |         | 95      |         | 109     |       | ps   |  |  |  |

| Table 6–46. DSP Block Internal Timing Microparameters |       |             |       |             |             |       |    |  |  |  |  |

|-------------------------------------------------------|-------|-------------|-------|-------------|-------------|-------|----|--|--|--|--|

| Symbol                                                |       | peed<br>ade |       | peed<br>ade | -7 S<br>Gra | Unit  |    |  |  |  |  |

|                                                       | Min   | Max         | Min   | Max         | Min         | Max   |    |  |  |  |  |

| t <sub>SU</sub>                                       | 0     |             | 0     |             | 0           |       | ps |  |  |  |  |

| t <sub>H</sub>                                        | 67    |             | 75    |             | 86          |       | ps |  |  |  |  |

| t <sub>CO</sub>                                       |       | 142         |       | 158         |             | 181   | ps |  |  |  |  |

| t <sub>INREG2PIPE18</sub>                             |       | 2,613       |       | 2,982       |             | 3,429 | ps |  |  |  |  |

| t <sub>INREG2PIPE9</sub>                              |       | 3,390       |       | 3,993       |             | 4,591 | ps |  |  |  |  |

| t <sub>PIPE2OUTREG2ADD</sub>                          |       | 2,002       |       | 2,203       |             | 2,533 | ps |  |  |  |  |

| t <sub>PIPE2OUTREG4ADD</sub>                          |       | 2,899       |       | 3,189       |             | 3,667 | ps |  |  |  |  |

| t <sub>PD9</sub>                                      |       | 3,709       |       | 4,081       |             | 4,692 | ps |  |  |  |  |

| t <sub>PD18</sub>                                     |       | 4,795       |       | 5,275       |             | 6,065 | ps |  |  |  |  |

| t <sub>PD36</sub>                                     |       | 7,495       |       | 8,245       |             | 9,481 | ps |  |  |  |  |

| t <sub>CLR</sub>                                      | 450   |             | 500   |             | 575         |       | ps |  |  |  |  |

| t <sub>CLKHL</sub>                                    | 1,350 |             | 1,500 |             | 1,724       |       | ps |  |  |  |  |

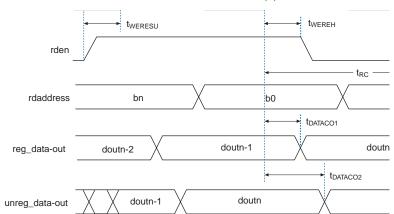

| Table 6–48. M4K Block Internal Timing Microparameters (Part 2 of 2) |         |         |         |         |         |       |      |  |  |  |  |

|---------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|--|--|

| Symbol                                                              | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | Heit  |      |  |  |  |  |

|                                                                     | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |  |  |

| t <sub>M4KDATACO1</sub>                                             |         | 571     |         | 635     |         | 729   | ps   |  |  |  |  |

| t <sub>M4KDATACO2</sub>                                             |         | 3,984   |         | 4,507   |         | 5,182 | ps   |  |  |  |  |

| t <sub>M4KCLKHL</sub>                                               | 150     |         | 167     |         | 192     |       | ps   |  |  |  |  |

| t <sub>M4KCLR</sub>                                                 | 170     |         | 189     |         | 255     |       | ps   |  |  |  |  |

| Table 6–49. M-RAM Block Internal Timing Microparameters |     |       |     |       |     |          |      |  |  |  |  |

|---------------------------------------------------------|-----|-------|-----|-------|-----|----------|------|--|--|--|--|

| O. mahal                                                | -   | ·5    | -   | 6     | -   | II.m.i.k |      |  |  |  |  |

| Symbol                                                  | Min | Max   | Min | Max   | Min | Max      | Unit |  |  |  |  |

| t <sub>MRAMRC</sub>                                     |     | 4,364 |     | 4,838 |     | 5,562    | ps   |  |  |  |  |

| t <sub>MRAMWC</sub>                                     |     | 3,654 |     | 4,127 |     | 4,746    | ps   |  |  |  |  |

| t <sub>MRAMWERESU</sub>                                 | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMWERH</sub>                                   | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMDATASU</sub>                                 | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMDATAH</sub>                                  | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMWADDRASU</sub>                               | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMWADDRH</sub>                                 | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMRADDRASU</sub>                               | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMRADDRH</sub>                                 | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMDATABSU</sub>                                | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMDATABH</sub>                                 | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMADDRBSU</sub>                                | 25  |       | 25  |       | 28  |          | ps   |  |  |  |  |

| t <sub>MRAMADDRBH</sub>                                 | 18  |       | 20  |       | 23  |          | ps   |  |  |  |  |

| t <sub>MRAMDATACO1</sub>                                |     | 1,038 |     | 1,053 |     | 1,210    | ps   |  |  |  |  |

| t <sub>MRAMDATACO2</sub>                                |     | 4,362 |     | 4,939 |     | 5,678    | ps   |  |  |  |  |

| t <sub>MRAMCLKHL</sub>                                  | 270 |       | 300 |       | 345 |          | ps   |  |  |  |  |

| t <sub>MRAMCLR</sub>                                    | 135 |       | 150 |       | 172 |          | ps   |  |  |  |  |

| Table 6–68. EP1SGX40 Column Pin Global Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |  |  |  |

|-----------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|--|--|

| Symbol                                                                      | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | 11-:4 |      |  |  |  |  |

|                                                                             | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |  |  |

| t <sub>INSU</sub>                                                           | 2.033   |         | 2.184   |         | 2.451   |       | ns   |  |  |  |  |

| t <sub>INH</sub>                                                            | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |  |  |

| t <sub>outco</sub>                                                          | 2.000   | 5.689   | 2.000   | 6.116   | 2.000   | 7.010 | ns   |  |  |  |  |

| t <sub>INSUPLL</sub>                                                        | 1.228   |         | 1.278   |         | 1.415   |       | ns   |  |  |  |  |

| t <sub>INHPLL</sub>                                                         | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |  |  |

| t <sub>OUTCOPLL</sub>                                                       | 0.500   | 2.594   | 0.500   | 2.732   | 0.500   | 3.113 | ns   |  |  |  |  |

| Table 6–69. EP1SGX40 Row Pin Fast Regional Clock External I/O Timing Parameters |         |         |                               |       |       |       |       |  |

|---------------------------------------------------------------------------------|---------|---------|-------------------------------|-------|-------|-------|-------|--|

| O                                                                               | -5 Spee | d Grade | -6 Speed Grade -7 Speed Grade |       |       |       | 11-24 |  |

| Symbol                                                                          | Min     | Max     | Min                           | Max   | Min   | Max   | Unit  |  |

| t <sub>INSU</sub>                                                               | 2.450   |         | 2.662                         |       | 3.046 |       | ns    |  |

| t <sub>INH</sub>                                                                | 0.000   |         | 0.000                         |       | 0.000 |       | ns    |  |

| t <sub>OUTCO</sub>                                                              | 2.000   | 4.880   | 2.000                         | 5.241 | 2.000 | 6.004 | ns    |  |

| Symbol                | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | 11!4  |      |

|-----------------------|---------|---------|---------|---------|---------|-------|------|

|                       | Min     | Max     | Min     | Max     | Min     | Max   | Unit |

| t <sub>INSU</sub>     | 2.398   |         | 2.567   |         | 2.938   |       | ns   |

| t <sub>INH</sub>      | 0.000   |         | 0.000   |         | 0.000   |       | ns   |

| t <sub>outco</sub>    | 2.000   | 4.932   | 2.000   | 5.336   | 2.000   | 6.112 | ns   |

| t <sub>INSUPLL</sub>  | 1.126   |         | 1.186   |         | 1.352   |       | ns   |

| t <sub>INHPLL</sub>   | 0.000   |         | 0.000   |         | 0.000   |       | ns   |

| t <sub>OUTCOPLL</sub> | 0.500   | 2.304   | 0.500   | 2.427   | 0.500   | 2.765 | ns   |

| Table 6-71. EP1SGX40 Row Pin Global Clock External I/O Timing Parameters (Part 1 of 2) |         |         |         |         |         |         |        |  |  |

|----------------------------------------------------------------------------------------|---------|---------|---------|---------|---------|---------|--------|--|--|

| Cumbal                                                                                 | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade | llm:4  |  |  |

| Symbol                                                                                 | Min     | Max     | Min     | Max     | Min     | Max     | - Unit |  |  |

| t <sub>INSU</sub>                                                                      | 1.965   |         | 2.128   |         | 2.429   |         | ns     |  |  |

| t <sub>INH</sub>                                                                       | 0.000   |         | 0.000   |         | 0.000   |         | ns     |  |  |

| Table 6–73. Stratix GX I/O Standard Row Pin Input Delay Adders (Part 2 of 2) |        |                |     |                |     |                |      |  |  |  |

|------------------------------------------------------------------------------|--------|----------------|-----|----------------|-----|----------------|------|--|--|--|

| I/O Standard                                                                 | -5 Spe | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |      |  |  |  |

|                                                                              | Min    | Max            | Min | Max            | Min | Max            | Unit |  |  |  |

| 1.5-V HSTL class II                                                          |        | 0              |     | 0              |     | 0              | ps   |  |  |  |

| 1.8-V HSTL class I                                                           |        | 70             |     | 73             |     | 83             | ps   |  |  |  |

| 1.8-V HSTL class II                                                          |        | 70             |     | 73             |     | 83             | ps   |  |  |  |

| LVDS (1)                                                                     |        | 40             |     | 42             |     | 48             | ps   |  |  |  |

| LVPECL (1)                                                                   |        | -50            |     | -53            |     | -61            | ps   |  |  |  |

| 3.3-V PCML (1)                                                               |        | 330            |     | 346            |     | 397            | ps   |  |  |  |

| HyperTransport (1)                                                           |        | 80             |     | 84             |     | 96             | ps   |  |  |  |

| Table 6–74. Stratix GX I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 1 of 2) |       |         |          |                |       |                |       |      |  |  |

|---------------------------------------------------------------------------------------------------------|-------|---------|----------|----------------|-------|----------------|-------|------|--|--|

| Otomala                                                                                                 |       | -5 Spec | ed Grade | -6 Speed Grade |       | -7 Speed Grade |       |      |  |  |

| Standard                                                                                                |       | Min     | Max      | Min            | Max   | Min            | Max   | Unit |  |  |

| LVCMOS                                                                                                  | 2 mA  |         | 570      |                | 599   |                | 689   | ps   |  |  |

|                                                                                                         | 4 mA  |         | 570      |                | 599   |                | 689   | ps   |  |  |

|                                                                                                         | 8 mA  |         | 350      |                | 368   |                | 423   | ps   |  |  |

|                                                                                                         | 12 mA |         | 130      |                | 137   |                | 157   | ps   |  |  |

|                                                                                                         | 24 mA |         | 0        |                | 0     |                | 0     | ps   |  |  |

| 3.3-V LVTTL                                                                                             | 4 mA  |         | 570      |                | 599   |                | 689   | ps   |  |  |

|                                                                                                         | 8 mA  |         | 350      |                | 368   |                | 423   | ps   |  |  |

|                                                                                                         | 12 mA |         | 130      |                | 137   |                | 157   | ps   |  |  |

|                                                                                                         | 16 mA |         | 70       |                | 74    |                | 85    | ps   |  |  |

|                                                                                                         | 24 mA |         | 0        |                | 0     |                | 0     | ps   |  |  |

| 2.5-V LVTTL                                                                                             | 2 mA  |         | 830      |                | 872   |                | 1,002 | ps   |  |  |

|                                                                                                         | 8 mA  |         | 250      |                | 263   |                | 302   | ps   |  |  |

|                                                                                                         | 12 mA |         | 140      |                | 147   |                | 169   | ps   |  |  |

|                                                                                                         | 16 mA |         | 100      |                | 105   |                | 120   | ps   |  |  |

| 1.8-V LVTTL                                                                                             | 2 mA  |         | 420      |                | 441   |                | 507   | ps   |  |  |

|                                                                                                         | 8 mA  |         | 350      |                | 368   |                | 423   | ps   |  |  |

|                                                                                                         | 12 mA |         | 350      |                | 368   |                | 423   | ps   |  |  |

| 1.5-V LVTTL                                                                                             | 2 mA  |         | 1,740    |                | 1,827 |                | 2,101 | ps   |  |  |

|                                                                                                         | 4 mA  |         | 1,160    |                | 1,218 |                | 1,400 | ps   |  |  |

|                                                                                                         | 8 mA  |         | 690      |                | 725   |                | 833   | ps   |  |  |

| GTL                                                                                                     |       |         | -150     |                | -157  |                | -181  | ps   |  |  |

Tables 6–78 and 6–79 show the adder delays for the column and row IOE programmable delays, respectively. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Dt                                      | 0 - 44: | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | 11:4  |      |

|-----------------------------------------|---------|----------------|-------|----------------|-------|---------|-------|------|

| Parameter                               | Setting | Min            | Max   | Min            | Max   | Min     | Max   | Unit |

| Decrease input delay to                 | Off     |                | 3,970 |                | 4,367 |         | 5,022 | ps   |

| internal cells                          | On      |                | 3,390 |                | 3,729 |         | 4,288 | ps   |

|                                         | Small   |                | 2,810 |                | 3,091 |         | 3,554 | ps   |

|                                         | Medium  |                | 212   |                | 224   |         | 257   | ps   |

|                                         | Large   |                | 212   |                | 224   |         | 257   | ps   |

| Decrease input delay to input register  | Off     |                | 3900  |                | 4,290 |         | 4,933 | ps   |

|                                         | On      |                | 0     |                | 0     |         | 0     | ps   |

| Decrease input delay to output register | Off     |                | 1,240 |                | 1,364 |         | 1,568 | ps   |

|                                         | On      |                | 0     |                | 0     |         | 0     | ps   |

| Increase delay to output                | Off     |                | 0     |                | 0     |         | 0     | ps   |

| pin                                     | On      |                | 377   |                | 397   |         | 456   | ps   |

| Increase delay to output                | Off     |                | 0     |                | 0     |         | 0     | ps   |

| enable pin                              | On      |                | 338   |                | 372   |         | 427   | ps   |

| Increase output clock                   | Off     |                | 0     |                | 0     |         | 0     | ps   |

| enable delay                            | On      |                | 540   |                | 594   |         | 683   | ps   |

|                                         | Small   |                | 1,016 |                | 1,118 |         | 1,285 | ps   |

|                                         | Large   |                | 1,016 |                | 1,118 |         | 1,285 | ps   |

| Increase input clock enable             | Off     |                | 0     |                | 0     |         | 0     | ps   |

| delay                                   | On      |                | 540   |                | 594   |         | 683   | ps   |

|                                         | Small   |                | 1,016 |                | 1,118 |         | 1,285 | ps   |

|                                         | Large   |                | 1,016 |                | 1,118 |         | 1,285 | ps   |

| Increase output enable                  | Off     |                | 0     |                | 0     |         | 0     | ps   |

| clock enable delay                      | On      |                | 540   |                | 594   |         | 683   | ps   |

|                                         | Small   |                | 1,016 |                | 1,118 |         | 1,285 | ps   |

|                                         | Large   |                | 1,016 | _              | 1,118 |         | 1,285 | ps   |

The scaling factors for output pin timing in Table 6–80 are shown in units of time per pF unit of capacitance (ps/pF). Add this delay to the combinational timing path for output or bidirectional pins in addition to the "I/O Adder" delays shown in Tables 6–72 through 6–77 and the "IOE Programmable Delays" in Tables 6–78 and 6–79.

| Table 6–80. Output Delay Adder for Loading on LVTTL/LVCMOS Output Buffers |                            |                                |               |                |             |            |  |  |  |  |

|---------------------------------------------------------------------------|----------------------------|--------------------------------|---------------|----------------|-------------|------------|--|--|--|--|

|                                                                           |                            | LVTTL/L                        | VCMOS Standa  | rds            |             |            |  |  |  |  |

| Conditi                                                                   | ons                        |                                | Output P      | in Adder Delay | (ps/pF)     |            |  |  |  |  |

| Parameter                                                                 | Value                      | 3.3-V LVTTL                    | 2.5-V LVTTL   | 1.8-V LVTTL    | 1.5-V LVTTL | LVCMOS     |  |  |  |  |

|                                                                           | 24 mA                      | 15                             | _             | _              | -           | 8          |  |  |  |  |

|                                                                           | 16 mA                      | 25                             | 18            | -              | -           | -          |  |  |  |  |

| Drive Strongth                                                            | 12 mA                      | 30                             | 25            | 25             | -           | 15         |  |  |  |  |

| Drive Strength                                                            | 8 mA                       | 50                             | 35            | 40             | 35          | 20         |  |  |  |  |

|                                                                           | 4 mA                       | 60                             | -             | -              | 80          | 30         |  |  |  |  |

|                                                                           | 2 mA                       | _                              | 75            | 120            | 160         | 60         |  |  |  |  |

|                                                                           |                            | SSTL/                          | HSTL Standard | S              |             |            |  |  |  |  |

| Conditi                                                                   | one                        |                                | Output P      | in Adder Delay | (ps/pF)     |            |  |  |  |  |

|                                                                           |                            |                                |               |                |             | 1.8-V HSTL |  |  |  |  |

| Class                                                                     |                            | 25                             | 25            | 25             | 25          | 25         |  |  |  |  |

| Class                                                                     | s II                       | 25                             | 20            | 25             | 20          | 20         |  |  |  |  |

|                                                                           | GTL+/GTL/CTT/PCI Standards |                                |               |                |             |            |  |  |  |  |

| Conditi                                                                   | ons                        | Output Pin Adder Delay (ps/pF) |               |                |             |            |  |  |  |  |

| Parameter                                                                 | Value                      | GTL+                           | GTL           | CTT            | PCI         | AGP        |  |  |  |  |

| V <sub>CCIO</sub> voltage                                                 | 3.3 V                      | 18                             | 18            | 25             | 20          | 20         |  |  |  |  |

| level                                                                     | 2.5 V                      | 15                             | 18            | -              | -           | -          |  |  |  |  |