Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 1057                                                        |

| Number of Logic Elements/Cells | 10570                                                       |

| Total RAM Bits                 | 920448                                                      |

| Number of I/O                  | 362                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 672-BBGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx10df672i6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Each Stratix GX transceiver channel consists of a transmitter and receiver. The transmitter contains the following:

- Transmitter PLL

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel to serial converter)

- Transmitter output buffer

The receiver contains the following:

- Input buffer

- Clock recovery unit (CRU)

- Deserializer

- Pattern detector and word aligner

- Rate matcher and channel aligner

- 8B/10B decoder

- Receiver logic array interface

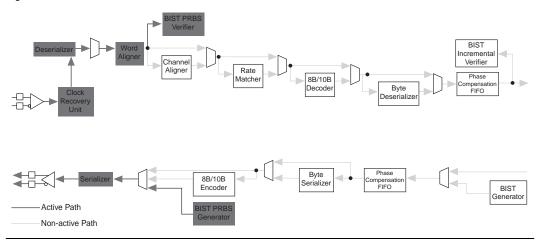

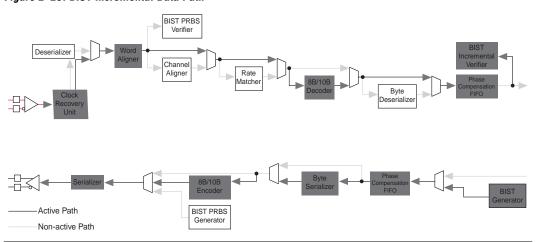

You can set all the Stratix GX transceiver functions through the Quartus II software. You can set programmable pre-emphasis, programmable equalizer, and programmable  $V_{OD}$  dynamically as well. Each Stratix GX transceiver channel is also capable of BIST generation and verification in addition to various loopback modes. Figure 2–2 shows the block diagram for the Stratix GX transceiver channel.

Stratix GX transceivers provide physical coding sublayer (PCS) and physical media attachment (PMA) implementation for protocols such as 10-gigabit XAUI and GIGE. The PCS portion of the transceiver consists of the logic array interface, 8B/10B encoder/decoder, pattern detector, word aligner, rate matcher, channel aligner, and the BIST and pseudo-random binary sequence pattern generator/verifier. The PMA portion of the transceiver consists of the serializer/deserializer, the CRU, and the I/O buffers.

### **Transmitter Path**

This section describes the data path through the Stratix GX transmitter (see Figure 2–2). Data travels through the Stratix GX transmitter via the following modules:

- Transmitter PLL

- Transmitter phase compensation FIFO buffer

- Byte serializer

- 8B/10B encoder

- Serializer (parallel to serial converter)

- Transmitter output buffer

### Transmitter PLL

Each transceiver block has one transmitter PLL, which receives the reference clock and generates the following signals:

- High-speed serial clock used by the serializer

- Slow-speed reference clock used by the receiver

- Slow-speed clock used by the logic array (divisible by two for double-width mode)

The INCLK clock is the input into the transmitter PLL. There is one INCLK clock per transceiver block. This clock can be fed by either the REFCLKB pin, PLD routing, or the inter-transceiver routing line. See the section "Stratix GX Clocking" on page 2–30 for more information about the inter-transceiver lines.

The transmitter PLL in each transceiver block clocks the circuits in the transmit path. The transmitter PLL is also used to train the receiver PLL. If no transmit channels are used in the transceiver block, the transmitter PLL can be turned off. Figure 2–3 is a block diagram of the transmitter PLL.

The transmitter PLL can support up to 3.1875 Mbps. The input clock frequency for -5 and -6 speed grade devices is limited to 650 MHz if you use the REFCLKB pin or to 325 MHz if you use the other clock routing resources. For -7 speed grade devices, the maximum input clock frequency is 312.5 MHz with the REFCLKB pin, and the maximum is 156.25 MHz for all other clock routing resources. An optional PLL\_LOCKED port is available to indicate whether the transmitter PLL is locked to the reference clock. The transmitter PLL has a programmable loop bandwidth that can be set to low or high. The loop bandwidth parameter can be statically set in the Quartus II software.

Table 2–2 lists the adjustable parameters in the transmitter PLL.

| Table 2–2. Transmitter PLL Specifications |                               |  |  |  |  |

|-------------------------------------------|-------------------------------|--|--|--|--|

| Parameter                                 | Specifications                |  |  |  |  |

| Input reference frequency range           | 25 MHz to 650 MHz             |  |  |  |  |

| Data rate support                         | 500 Mbps to 3.1875 Gbps       |  |  |  |  |

| Multiplication factor (W)                 | 2, 4, 5, 8, 10, 16, or 20 (1) |  |  |  |  |

| Bandwidth                                 | Low, high                     |  |  |  |  |

*Note to Table 2–2:*

Multiplication factors 2 and 5 can only be achieved with the use of the pre-divider on the REFCLKB pin.

### Transmitter Phase Compensation FIFO Buffer

The transmitter phase compensation FIFO buffer resides in the transceiver block at the PLD boundary. This FIFO buffer compensates for the phase differences between the transmitter reference clock (inclk) and the PLD interface clock (tx\_coreclk). The phase difference between the two clocks must be less than  $360^{\circ}$ . The PLD interface clock must also be frequency locked to the transmitter reference clock. The phase compensation FIFO buffer is four words deep and cannot be bypassed.

### Byte Serializer

The byte serializer takes double-width words (16 or 20 bits) from the PLD interface and converts them to a single width word (8 or 10 bits) for use in the transceiver. The transmit data path after the byte serializer is single width (8 or 10 bits). The byte serializer is bypassed when single width mode (8 or 10 bits) is used at the PLD interface.

Figure 2-24. BIST PRBS Data Path

Figure 2-25. BIST Incremental Data Path

Table 2–9 shows the BIST data output and verifier alignment pattern.

| Table 2–9. BIST Data Output & Verifier Alignment Pattern (Part 1 of 2) |                    |                             |                                 |  |  |  |  |  |

|------------------------------------------------------------------------|--------------------|-----------------------------|---------------------------------|--|--|--|--|--|

| BIST Mode                                                              | Output             | Polynomials                 | Verifier Word Alignment Pattern |  |  |  |  |  |

| PRBS 8-bit                                                             | 2 <sup>8</sup> – 1 | $x^8 + x^7 + x^5 + x^3 + 1$ | 1000000011111111                |  |  |  |  |  |

| PRBS 10-bit                                                            | 210 - 1            | $x^{10} + x^7 + 1$          | 1111111111                      |  |  |  |  |  |

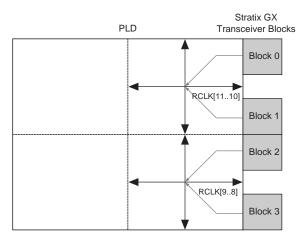

The receiver PLL can also drive the fast regional, regional clocks, and local routing adjacent to the associated transceiver block. Figures 2–28 through 2–31 show which fast regional and regional clock resource can be used by the recovered clock.

In the EP1SGX25 device, the receiver PLL recovered clocks from transceiver blocks 0 and 1 drive RCLK [1..0] while transceiver blocks 2 and 3 drive RCLK [7..6]. The regional clocks feed logic in their associated regions.

Figure 2–28. EP1SGX25 Receiver PLL Recovered Clock to Regional Clock Connection

In addition, the receiver PLL's recovered clocks can drive fast regional lines (FCLK) as shown Figure 2–29. The fast regional clocks can feed logic in their associated regions.

## **High-Speed Serial Bus Protocols**

With wide, serial data rate range, Stratix GX devices can support multiple, high-speed serial bus protocols. Table 2–12 shows some of the protocols that Stratix GX devices can support.

| Table 2–12. High-Speed Serial Bus Protocols |                                                   |  |  |  |  |  |

|---------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| Bus Transfer Protocol                       | Stratix GX (Gbps)<br>(Supports up to 3.1875 Gbps) |  |  |  |  |  |

| SONET backplane                             | 2.488                                             |  |  |  |  |  |

| 10 Gigabit Ethernet XAUI                    | 3.125                                             |  |  |  |  |  |

| 10 Gigabit fibre channel                    | 3.1875                                            |  |  |  |  |  |

| InfiniBand                                  | 2.5                                               |  |  |  |  |  |

| Fibre channel (1G, 2G)                      | 1.0625, 2.125                                     |  |  |  |  |  |

| Serial RapidIO™                             | 1.25, 2.5, 3.125                                  |  |  |  |  |  |

| PCI Express                                 | 2.5                                               |  |  |  |  |  |

| SMPTE 292M                                  | 1.485                                             |  |  |  |  |  |

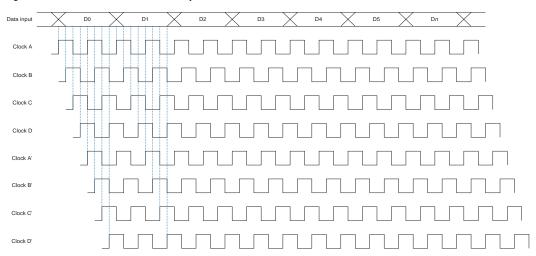

Figure 3-9. Fast PLL Clocks & Data Input

### Protocols, Training Pattern & DPA Lock Time

The dynamic phase aligner uses a fast PLL for clock multiplication, and the dynamic phase selector for the phase detection and alignment. The dynamic phase aligner uses the high-speed clock out of the dynamic phase selector to deserialize high-speed data and the receiver's source synchronous operations.

At each rising edge of the clock, the dynamic phase selector determines the phase difference between the clock and the data and automatically compensates for the phase difference between the data and clock.

## TriMatrix Memory

TriMatrix memory consists of three types of RAM blocks: M512, M4K, and M-RAM blocks. Although these memory blocks are different, they can all implement various types of memory with or without parity, including true dual-port, simple dual-port, and single-port RAM, ROM, and FIFO buffers. Table 4–2 shows the size and features of the different RAM blocks.

| Table 4–2. TriMatrix                              | Table 4–2. TriMatrix Memory Features (Part 1 of 2) |                                  |                                |  |  |  |  |  |

|---------------------------------------------------|----------------------------------------------------|----------------------------------|--------------------------------|--|--|--|--|--|

| Memory Feature                                    | M512 RAM Block<br>(32 × 18 Bits)                   | M4K RAM Block<br>(128 × 36 Bits) | M-RAM Block<br>(4K × 144 Bits) |  |  |  |  |  |

| Maximum performance                               | (1)                                                | (1)                              | (1)                            |  |  |  |  |  |

| True dual-port memory                             |                                                    | <b>✓</b>                         | <b>✓</b>                       |  |  |  |  |  |

| Simple dual-port memory                           | ✓                                                  | ~                                | <b>✓</b>                       |  |  |  |  |  |

| Single-port memory                                | ✓                                                  | ✓                                | ✓                              |  |  |  |  |  |

| Shift register                                    | ✓                                                  | ✓                                |                                |  |  |  |  |  |

| ROM                                               | ✓                                                  | ✓                                | (2)                            |  |  |  |  |  |

| FIFO buffer                                       | ✓                                                  | ✓                                | ✓                              |  |  |  |  |  |

| Byte enable                                       |                                                    | ✓                                | ✓                              |  |  |  |  |  |

| Parity bits                                       | ✓                                                  | ✓                                | ✓                              |  |  |  |  |  |

| Mixed clock mode                                  | ✓                                                  | ✓                                | ✓                              |  |  |  |  |  |

| Memory initialization                             | ✓                                                  | ✓                                |                                |  |  |  |  |  |

| Simple dual-port<br>memory mixed width<br>support | <b>✓</b>                                           | ~                                | ~                              |  |  |  |  |  |

| True dual-port memory mixed width support         |                                                    | ~                                | <b>✓</b>                       |  |  |  |  |  |

| Power-up conditions                               | Outputs cleared                                    | Outputs cleared                  | Outputs<br>unknown             |  |  |  |  |  |

| Register clears                                   | Input and output registers                         | Input and output registers       | Output registers               |  |  |  |  |  |

| Mixed-port read-<br>during-write                  | Unknown output/old data                            | Unknown<br>output/old data       | Unknown output                 |  |  |  |  |  |

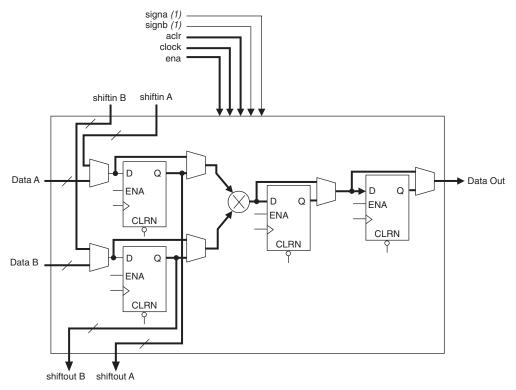

Figure 4–34. Simple Multiplier Mode

Note to Figure 4-34:

(1) These signals are not registered or registered once to match the data path pipeline.

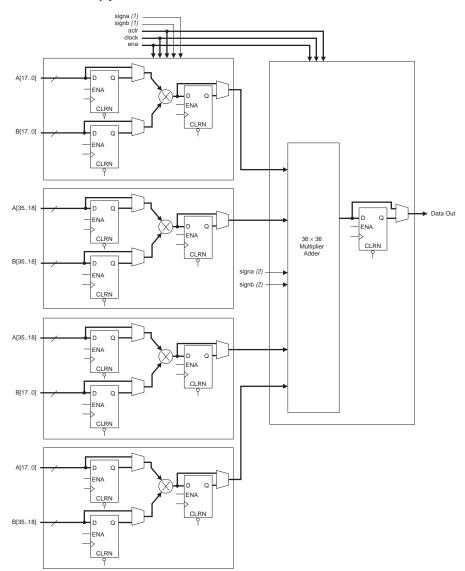

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 4–35 shows the  $36 \times 36$ -bit multiply mode.

Figure 4–35. 36 × 36 Multiply Mode

### *Notes to Figure 4–35:*

- (1) These signals are not registered or registered once to match the pipeline.

- (2) These signals are not registered, registered once, or registered twice for latency to match the pipeline.

| Table 4–18. Stratix GX Enhanced PLL & Fast PLL Features (Part 2 of 2) Notes (1)–(8) |                                                                 |          |  |  |  |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------|--|--|--|--|--|

| Feature                                                                             | Enhanced PLL                                                    | Fast PLL |  |  |  |  |  |

| Number of external clock outputs                                                    | Four differential/eight singled-ended or one single-ended $(6)$ | (7)      |  |  |  |  |  |

| Number of feedback clock inputs                                                     | 4 (8)                                                           |          |  |  |  |  |  |

### Notes to Table 4-18:

- (1) The maximum count value is 1024, with a 50% duty cycle setting on the counter. The maximum count value for any other duty cycle setting is 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the VCO period divided by 8.

- (4) For degree increments, Stratix GX devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7 and 8 have two output ports per PLL. PLLs 1 and 2 have three output ports per PLL.

- (6) Every Stratix GX device has two enhanced PLLs (PLLs 5 and 6) with eight single-ended or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EP1SGX40 devices each have one single-ended output.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix GX device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

Figure 4–48 shows a top-level diagram of the Stratix GX device and the PLL floorplan.

pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 4–19 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| I/O Otomdond              |          | Output   |           |        |

|---------------------------|----------|----------|-----------|--------|

| I/O Standard              | INCLK    | FBIN     | PLLENABLE | EXTCLK |

| LVTTL                     | <b>✓</b> | ✓        | <b>✓</b>  | ✓      |

| LVCMOS                    | ✓        | ✓        | ✓         | ✓      |

| 2.5 V                     | ✓        | ✓        |           | ✓      |

| 1.8 V                     | ✓        | ✓        |           | ✓      |

| 1.5 V                     | ✓        | <b>✓</b> |           | ✓      |

| 3.3-V PCI                 | ✓        | ✓        |           | ✓      |

| 3.3-V PCI-X               | ✓        | ✓        |           | ✓      |

| LVPECL                    | <b>✓</b> | <b>✓</b> |           | ✓      |

| 3.3-V PCML                | ✓        | ✓        |           | ✓      |

| LVDS                      | <b>✓</b> | ✓        |           | ✓      |

| HyperTransport technology | <b>✓</b> | ✓        |           | ✓      |

| Differential HSTL         | ✓        |          |           | ✓      |

| Differential SSTL         |          |          |           | ✓      |

| 3.3-V GTL                 | ✓        | ✓        |           | ✓      |

| 3.3-V GTL+                | ✓        | ✓        |           | ✓      |

| 1.5-V HSTL class I        | ✓        | ✓        |           | ✓      |

| 1.5-V HSTL class II       | ✓        | ✓        |           | ✓      |

| SSTL-18 class I           | ✓        | ✓        |           | ✓      |

| SSTL-18 class II          | ✓        | ✓        |           | ✓      |

| SSTL-2 class I            | ✓        | ✓        |           | ✓      |

| SSTL-2 class II           | ✓        | ✓        |           | ✓      |

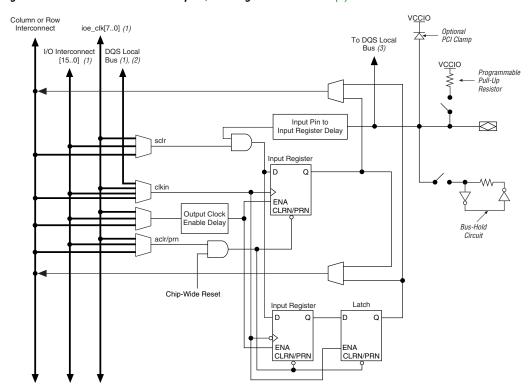

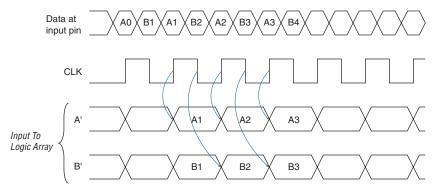

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 4–64 shows an IOE configured for DDR input. Figure 4–65 shows the DDR input timing diagram.

Figure 4–64. Stratix GX IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 4–64:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

Figure 4-65. Input Timing Diagram in DDR Mode

When using the IOE for DDR outputs, the two output registers are configured to clock two data paths from LEs on rising clock edges. These output registers are multiplexed by the clock to drive the output pin at a  $\times 2$  rate. One output register clocks the first bit out on the clock high time, while the other output register clocks the second bit out on the clock low time. Figure 4–66 shows the IOE configured for DDR output. Figure 4–67 shows the DDR output timing diagram.

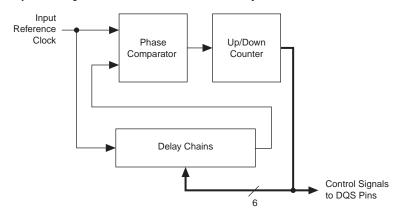

Figure 4-68. Simplified Diagram of the DQS Phase-Shift Circuitry

See the *External Memory Interfaces* chapter of the *Stratix GX Device Handbook, Volume 2* for more information on external memory interfaces.

## **Programmable Drive Strength**

The output buffer for each Stratix GX device I/O pin has a programmable drive strength control for certain I/O standards. The LVTTL and LVCMOS standard has several levels of drive strength that the user can control. SSTL-3 class I and II, SSTL-2 class I and II, HSTL class I and II, and 3.3-V GTL+ support a minimum setting, the lowest drive strength that guarantees the  $\rm I_{OH}/I_{OL}$  of the standard. Using minimum settings provides signal slew rate control to reduce system noise and signal overshoot.

| Table 6–6. Stratix GX Transceiver Block On-Chip Termination (Part 2 of 2) |                       |                                                  |     |     |       |   |  |  |  |

|---------------------------------------------------------------------------|-----------------------|--------------------------------------------------|-----|-----|-------|---|--|--|--|

| Symbol                                                                    | Parameter             | Min                                              | Тур | Max | Units |   |  |  |  |

| Refclkb                                                                   | Dedicated transceiver | Commercial and industrial, 100- $\Omega$ setting | 103 | 108 | 113   | Ω |  |  |  |

|                                                                           | clock termination     | Commercial and industrial, 120- $\Omega$ setting | 120 | 128 | 134   | Ω |  |  |  |

|                                                                           |                       | Commercial and industrial, 150-Ω setting         | 149 | 158 | 167   | Ω |  |  |  |

### Notes to Tables 6-1 through 6-6:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Conditions beyond those listed in Table 6–1 may cause permanent damage to a device. Additionally, device operation at the absolute maximum ratings for extended periods of time may have adverse affects on the device.

- (3) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 4.6 V for input currents less than 100 mA and periods shorter than 20 ns. (The information in this note does not include the transceiver pins.)

- (4) Maximum V<sub>CC</sub> rise time is 100 ms, and V<sub>CC</sub> must rise monotonically.

- (5) V<sub>CCIO</sub> maximum and minimum conditions for LVPECL, LVDS, and 3.3-V PCML are shown in parentheses.

- (6) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (7) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.5$  V, and  $V_{CCIO} = 1.5$  V, 1.8 V, 2.5 V, and 3.3 V.

- (8) This value is specified for normal device operation. The value may vary during power-up. This applies for all  $V_{CCIO}$  settings (3.3, 2.5, 1.8, and 1.5 V).

- Pin pull-up resistance values decrease if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) The device can tolerate prolonged operation at this absolute maximum, as long as the maximum specification is not violated.

- (11) Each usable quad requires its own  $R_{REF}$  resistor path to ground. For example, the "D" in the EP1SGX25DC1020 device code means it has two usable quad so two different  $R_{REF}$  pins must be connected to a  $R_{REF}$  resistor each to ground. The DC signal on the  $R_{REF}$  pin must be as clean as possible. Ensure that no noise is coupled to this pin.

- (12) The Stratix GX device's recommended operating conditions do not include the transceiver. Refer to Tables 6–4 to 6–7.

- (13) Minimum DC input to the transceiver pins is -0.5 V. During transitions, the transceiver pins may undershoot to -0.5 V or overshoot to 3.5 V for input currents less than 100 mA and periods shorter than 20 ns.

| Table 6–7. S                            | tratix GX Transceiv                                      | er Blo                           | ck AC S | Specificat                             | ion (Pa | art 1 of | 7)                                     |     |     |      |    |

|-----------------------------------------|----------------------------------------------------------|----------------------------------|---------|----------------------------------------|---------|----------|----------------------------------------|-----|-----|------|----|

| Symbol /<br>Description                 | Conditions                                               | -5 Commercial<br>Speed Grade (1) |         | -6 Commercial & Industrial Speed Grade |         |          | -7 Commercial & Industrial Speed Grade |     |     | Unit |    |

|                                         |                                                          | Min                              | Тур     | Max                                    | Min     | Тур      | Max                                    | Min | Тур | Max  |    |

| Power per<br>quadrant<br>(PCS +<br>PMA) | 3.125 Gbps, 400-<br>mV V <sub>od</sub><br>0 pre-emphasis |                                  | 450     |                                        |         | 450      |                                        |     |     |      | mW |

| Table 6–68. EP1SGX40 Column Pin Global Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |  |

|-----------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|

| Symbol                                                                      | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | 11-:4 |      |  |  |

|                                                                             | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>                                                           | 2.033   |         | 2.184   |         | 2.451   |       | ns   |  |  |

| t <sub>INH</sub>                                                            | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>outco</sub>                                                          | 2.000   | 5.689   | 2.000   | 6.116   | 2.000   | 7.010 | ns   |  |  |

| t <sub>INSUPLL</sub>                                                        | 1.228   |         | 1.278   |         | 1.415   |       | ns   |  |  |

| t <sub>INHPLL</sub>                                                         | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCOPLL</sub>                                                       | 0.500   | 2.594   | 0.500   | 2.732   | 0.500   | 3.113 | ns   |  |  |

| Table 6–69. EP1SGX40 Row Pin Fast Regional Clock External I/O Timing Parameters |         |         |                |       |                |       |      |  |  |

|---------------------------------------------------------------------------------|---------|---------|----------------|-------|----------------|-------|------|--|--|

| Symbol                                                                          | -5 Spee | d Grade | -6 Speed Grade |       | -7 Speed Grade |       | 11   |  |  |

|                                                                                 | Min     | Max     | Min            | Max   | Min            | Max   | Unit |  |  |

| t <sub>INSU</sub>                                                               | 2.450   |         | 2.662          |       | 3.046          |       | ns   |  |  |

| t <sub>INH</sub>                                                                | 0.000   |         | 0.000          |       | 0.000          |       | ns   |  |  |

| t <sub>OUTCO</sub>                                                              | 2.000   | 4.880   | 2.000          | 5.241 | 2.000          | 6.004 | ns   |  |  |

| Cumbal                | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | d Grade |      |

|-----------------------|---------|---------|---------|---------|---------|---------|------|

| Symbol                | Min     | Max     | Min     | Max     | Min     | Max     | Unit |

| t <sub>INSU</sub>     | 2.398   |         | 2.567   |         | 2.938   |         | ns   |

| t <sub>INH</sub>      | 0.000   |         | 0.000   |         | 0.000   |         | ns   |

| t <sub>outco</sub>    | 2.000   | 4.932   | 2.000   | 5.336   | 2.000   | 6.112   | ns   |

| t <sub>INSUPLL</sub>  | 1.126   |         | 1.186   |         | 1.352   |         | ns   |

| t <sub>INHPLL</sub>   | 0.000   |         | 0.000   |         | 0.000   |         | ns   |

| t <sub>OUTCOPLL</sub> | 0.500   | 2.304   | 0.500   | 2.427   | 0.500   | 2.765   | ns   |

| Table 6–71. EP1SGX40 Row Pin Global Clock External I/O Timing Parameters (Part 1 of 2) |         |                |       |                |       |                |      |

|----------------------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|------|

| Symbol                                                                                 | -5 Spee | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |      |

|                                                                                        | Min     | Max            | Min   | Max            | Min   | Max            | Unit |

| t <sub>INSU</sub>                                                                      | 1.965   |                | 2.128 |                | 2.429 |                | ns   |

| t <sub>INH</sub>                                                                       | 0.000   |                | 0.000 |                | 0.000 |                | ns   |

| Table 6-82. Stratix GX Maximum Input Clock Rate for CLK[0, 2, 9, 11] Pins & FPLL[87]CLK Pins |                |                |                |      |  |

|----------------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                                 | -5 Speed Grade | -6 Speed Grade | -7 Speed Grade | Unit |  |

| LVTTL                                                                                        | 422            | 422            | 390            | MHz  |  |

| 2.5 V                                                                                        | 422            | 422            | 390            | MHz  |  |

| 1.8 V                                                                                        | 422            | 422            | 390            | MHz  |  |

| 1.5 V                                                                                        | 422            | 422            | 390            | MHz  |  |

| LVCMOS                                                                                       | 422            | 422            | 390            | MHz  |  |

| GTL                                                                                          | 300            | 250            | 200            | MHz  |  |

| GTL+                                                                                         | 300            | 250            | 200            | MHz  |  |

| SSTL-3 class I                                                                               | 400            | 350            | 300            | MHz  |  |

| SSTL-3 class II                                                                              | 400            | 350            | 300            | MHz  |  |

| SSTL-2 class I                                                                               | 400            | 350            | 300            | MHz  |  |

| SSTL-2 class II                                                                              | 400            | 350            | 300            | MHz  |  |

| SSTL-18 class I                                                                              | 400            | 350            | 300            | MHz  |  |

| SSTL-18 class II                                                                             | 400            | 350            | 300            | MHz  |  |

| 1.5-V HSTL class I                                                                           | 400            | 350            | 300            | MHz  |  |

| 1.5-V HSTL class II                                                                          | 400            | 350            | 300            | MHz  |  |

| 1.8-V HSTL class I                                                                           | 400            | 350            | 300            | MHz  |  |

| 1.8-V HSTL class II                                                                          | 400            | 350            | 300            | MHz  |  |

| 3.3-V PCI                                                                                    | 422            | 422            | 390            | MHz  |  |

| 3.3-V PCI-X 1.0                                                                              | 422            | 422            | 390            | MHz  |  |

| Compact PCI                                                                                  | 422            | 422            | 390            | MHz  |  |

| AGP 1×                                                                                       | 422            | 422            | 390            | MHz  |  |

| AGP 2×                                                                                       | 422            | 422            | 390            | MHz  |  |

| СТТ                                                                                          | 300            | 250            | 200            | MHz  |  |

| Differential HSTL                                                                            | 400            | 350            | 300            | MHz  |  |

| LVDS                                                                                         | 717            | 717            | 640            | MHz  |  |

| LVPECL                                                                                       | 717            | 717            | 640            | MHz  |  |

| PCML                                                                                         | 400            | 375            | 350            | MHz  |  |

| HyperTransport technology                                                                    | 717            | 717            | 640            | MHz  |  |

| Table 6–83. Stratix GX Maximum Input Clock Rate for CLK[1, 3, 8, 10] Pins (Part 1 of 2) |                |                |                |      |  |

|-----------------------------------------------------------------------------------------|----------------|----------------|----------------|------|--|

| I/O Standard                                                                            | -5 Speed Grade | -6 Speed Grade | -7 Speed Grade | Unit |  |

| LVTTL                                                                                   | 422            | 422            | 390            | MHz  |  |

| 2.5 V                                                                                   | 422            | 422            | 390            | MHz  |  |

| Symbol                             | Parameter                                                  | Min | Max                                                        | Unit         |

|------------------------------------|------------------------------------------------------------|-----|------------------------------------------------------------|--------------|

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (3)                     | 45  | 55                                                         | %            |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (3)                     |     | ±80                                                        | ps           |

|                                    | Period jitter for internal global or regional clock        |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUl |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                      | 10  | 100                                                        | μs           |

| m                                  | Multiplication factors for <i>m</i> counter (4)            | 1   | 32                                                         | Integer      |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for 10, 11, and g0 counter (4), (5) | 1   | 32                                                         | Integer      |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                       | 10  |                                                            | ns           |

### *Notes to Tables 6-91 & 6-92:*

- (1) See "Maximum Input & Output Clock Rates" on page 6–54.

- (2) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (3) This parameter is for high-speed differential I/O mode only.

- (4) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (5) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

## **DLL Jitter**

Table 6–93 reports the jitter for the DLL in the DQS phase-shift reference circuit.

| Table 6–93. DLL Jitter for DQS Phase Shift Reference Circuit |                 |  |  |

|--------------------------------------------------------------|-----------------|--|--|

| Frequency (MHz)                                              | DLL Jitter (ps) |  |  |

| 197 to 200                                                   | ± 100           |  |  |

| 160 to 196                                                   | ± 300           |  |  |

| 100 to 159                                                   | ± 500           |  |  |