Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 2566                                                       |

| Number of Logic Elements/Cells | 25660                                                      |

| Total RAM Bits                 | 1944576                                                    |

| Number of I/O                  | 455                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                            |

| Package / Case                 | 672-BBGA                                                   |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25cf672c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 1–1. Stratix GX Device Features  |                        |                                     |                        |

|----------------------------------------|------------------------|-------------------------------------|------------------------|

| Feature                                | EP1SGX10C<br>EP1SGX10D | EP1SGX25C<br>EP1SGX25D<br>EP1SGX25F | EP1SGX40D<br>EP1SGX40G |

| LEs                                    | 10,570                 | 25,660                              | 41,250                 |

| Transceiver channels                   | 4, 8                   | 4, 8, 16                            | 8, 20                  |

| Source-synchronous channels            | 22                     | 39                                  | 45                     |

| M512 RAM blocks (32 × 18 bits)         | 94                     | 224                                 | 384                    |

| M4K RAM blocks (128 × 36 bits)         | 60                     | 138                                 | 183                    |

| M-RAM blocks (4K ×144 bits)            | 1                      | 2                                   | 4                      |

| Total RAM bits                         | 920,448                | 1,944,576                           | 3,423,744              |

| Digital signal processing (DSP) blocks | 6                      | 10                                  | 14                     |

| Embedded multipliers (1)               | 48                     | 80                                  | 112                    |

| PLLs                                   | 4                      | 4                                   | 8                      |

### Note to Table 1–1:

(1) This parameter lists the total number of 9- × 9-bit multipliers for each device. For the total number of 18- × 18-bit multipliers per device, divide the total number of 9- × 9-bit multipliers by 2. For the total number of 36- × 36-bit multipliers per device, decide the total number of 9- × 9-bit multipliers by 8.

Stratix GX devices are available in space-saving FineLine BGA® packages (refer to Tables 1–2 and 1–3), and in multiple speed grades (refer to Table 1–4). Stratix GX devices support vertical migration within the same package (that is, you can migrate between the EP1SGX10C and EP1SGX25C devices in the 672-pin FineLine BGA package). See the Stratix GX device pin tables for more information. Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type, to identify which I/O pins it is possible to migrate. The Quartus II software can automatically cross reference and place all pins for migration when given a device migration list.

| Table 1–2. Stratix GX Package Options & I/O Pin Counts (Part 1 of 2) Note (1) |     |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Device 672-Pin FineLine BGA 1,020-Pin FineLine BGA                            |     |  |  |  |  |  |  |

| EP1SGX10C                                                                     | 362 |  |  |  |  |  |  |

| EP1SGX10D                                                                     | 362 |  |  |  |  |  |  |

| EP1SGX25C                                                                     | 455 |  |  |  |  |  |  |

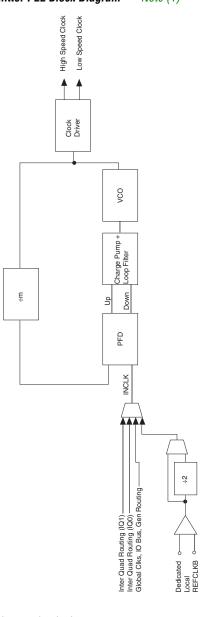

Figure 2–3. Transmitter PLL Block Diagram Note (1)

Note to Figure 2–3:

(1) The divider in the PLL divides by 4, 8, 10, 16, or 20.

The transmitter PLL can support up to 3.1875 Mbps. The input clock frequency for -5 and -6 speed grade devices is limited to 650 MHz if you use the REFCLKB pin or to 325 MHz if you use the other clock routing resources. For -7 speed grade devices, the maximum input clock frequency is 312.5 MHz with the REFCLKB pin, and the maximum is 156.25 MHz for all other clock routing resources. An optional PLL\_LOCKED port is available to indicate whether the transmitter PLL is locked to the reference clock. The transmitter PLL has a programmable loop bandwidth that can be set to low or high. The loop bandwidth parameter can be statically set in the Quartus II software.

Table 2–2 lists the adjustable parameters in the transmitter PLL.

| Table 2–2. Transmitter PLL Specifications |                               |  |  |  |  |

|-------------------------------------------|-------------------------------|--|--|--|--|

| Parameter                                 | Specifications                |  |  |  |  |

| Input reference frequency range           | 25 MHz to 650 MHz             |  |  |  |  |

| Data rate support                         | 500 Mbps to 3.1875 Gbps       |  |  |  |  |

| Multiplication factor (W)                 | 2, 4, 5, 8, 10, 16, or 20 (1) |  |  |  |  |

| Bandwidth                                 | Low, high                     |  |  |  |  |

*Note to Table 2–2:*

Multiplication factors 2 and 5 can only be achieved with the use of the pre-divider on the REFCLKB pin.

### Transmitter Phase Compensation FIFO Buffer

The transmitter phase compensation FIFO buffer resides in the transceiver block at the PLD boundary. This FIFO buffer compensates for the phase differences between the transmitter reference clock (inclk) and the PLD interface clock (tx\_coreclk). The phase difference between the two clocks must be less than  $360^{\circ}$ . The PLD interface clock must also be frequency locked to the transmitter reference clock. The phase compensation FIFO buffer is four words deep and cannot be bypassed.

# Byte Serializer

The byte serializer takes double-width words (16 or 20 bits) from the PLD interface and converts them to a single width word (8 or 10 bits) for use in the transceiver. The transmit data path after the byte serializer is single width (8 or 10 bits). The byte serializer is bypassed when single width mode (8 or 10 bits) is used at the PLD interface.

### 8B/10B Encoder

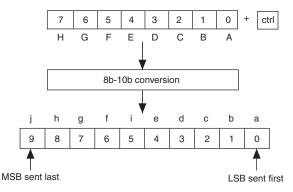

The 8B/10B encoder translates 8-bit wide data + 1 control enable bit into a 10-bit encoded data. The encoded data has a maximum run length of 5. The 8B/10B encoder can be bypassed. Figure 2–4 diagrams the encoding process.

Figure 2-4. Encoding Process

### Transmit State Machine

The transmit state machine operates in either XAUI mode or in GIGE mode, depending on the protocol used.

### **GIGE Mode**

In GIGE mode, the transmit state machines convert all idle ordered sets (/K28.5/,/Dx.y/) to either /I1/ or /I2/ ordered sets. /I1/ consists of a negative-ending disparity /K28.5/ (denoted by /K28.5/-) followed by a neutral /D5.6/./I2/ consists of a positive-ending disparity /K28.5/ (denoted by /K28.5/+) and a negative-ending disparity /D16.2/ (denoted by /D16.2/-). The transmit state machines do not convert any of the ordered sets to match /C1/ or /C2/, which are the configuration ordered sets. (/C1/ and /C2/ are defined by (/K28.5/, /D21.5/) and (/K28.5/, /D2.2/), respectively.) Both the /I1/ and /I2/ ordered sets guarantee a negative-ending disparity after each ordered set. The GIGE transmit state machine can be statically disabled in the Quartus II software, even if using the GIGE protocol mode.

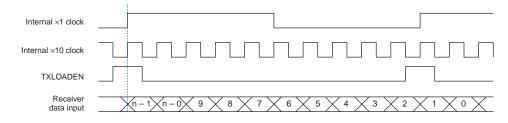

The logic array sends parallel data to the SERDES transmitter circuit when the TXLOADEN signal is asserted. This signal is generated by the high-speed counter circuitry of the logic array low-frequency clock's rising edge. The data is then transferred from the parallel register into the serial shift register by the TXLOADEN signal on the third rising edge of the high-frequency clock.

Figure 3–3 shows the block diagram of a single SERDES transmitter channel and Figure 3–4 shows the timing relationship between the data and clocks in Stratix GX devices in  $\times 10$  mode. W is the low-frequency multiplier and J is the data parallelization division factor.

Transmitter Circuit Parallel Serial Register Register -⊠ TXOUT+ PD9 PD9 PD8 -⊠ TXOUT-PD8 PD7 PD7 PD6 PD6 PD5 PD5 PD4 PD4 PD3 PD3 Stratix GX PD2 PD2 Logic Array PD1 PD1 PD0 PD0  $\times W$ Fast **TXLOADEN PLL**

Figure 3-3. Stratix GX High-Speed Interface Serialized in ×10 Mode

interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

or regional clock. In contrast, a circuit using asynchronous RAM must generate the RAM WREN signal while ensuring its data and address signals meet setup and hold time specifications relative to the WREN signal. The output registers can be bypassed. Flow-through reading is possible in the simple dual-port mode of M512 and M4K RAM blocks by clocking the read enable and read address registers on the negative clock edge and bypassing the output registers.

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The Quartus II software automatically implements larger memory by combining multiple TriMatrix memory blocks. For example, two  $256 \times 16$ -bit RAM blocks can be combined to form a  $256 \times 32$ -bit RAM block. Memory performance does not degrade for memory blocks using the maximum number of words available in one memory block. Logical memory blocks using less than the maximum number of words use physical blocks in parallel, eliminating any external control logic that would increase delays. To create a larger high-speed memory block, the Quartus II software automatically combines memory blocks with LE control logic.

# **Parity Bit Support**

The memory blocks support a parity bit for each byte. The parity bit, along with internal LE logic, can implement parity checking for error detection to ensure data integrity. You can also use parity-size data words to store user-specified control bits. In the M4K and M-RAM blocks, byte enables are also available for data input masking during write operations.

# **Shift Register Support**

You can configure embedded memory blocks to implement shift registers for DSP applications such as pseudo-random number generators, multichannel filtering, auto-correlation, and cross-correlation functions. These and other DSP applications require local data storage, traditionally implemented with standard flip-flops, which can quickly consume many logic cells and routing resources for large shift registers. A more efficient alternative is to use embedded memory as a shift register block, which saves logic cell and routing resources and provides a more efficient implementation with the dedicated circuitry.

The size of a  $w \times m \times n$  shift register is determined by the input data width (w), the length of the taps (m), and the number of taps (n). The size of a  $w \times m \times n$  shift register must be less than or equal to the maximum number of memory bits in the respective block: 576 bits for the M512

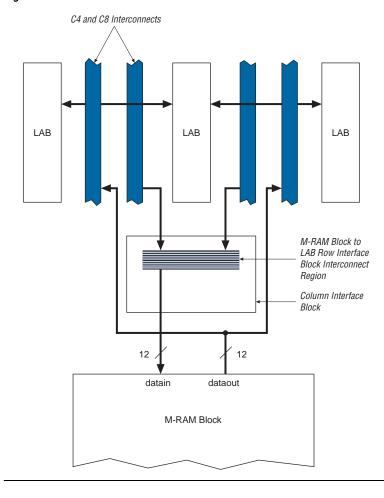

Figure 4–22. M-RAM Column Unit Interface to Interconnect

the capabilities for dynamic and mixed sign multiplications are handled differently. The following list provides the largest functions that can fit into a single DSP block.

- 36 × 36-bit unsigned by unsigned multiplication

- 36 × 36-bit signed by signed multiplication

- 35 × 36-bit unsigned by signed multiplication

- 36 × 35-bit signed by unsigned multiplication

- 36 x 35-bit signed by dynamic sign multiplication

- 35 × 36-bit dynamic sign by signed multiplication

- 35 × 36-bit unsigned by dynamic sign multiplication

- 36 × 35-bit dynamic sign by unsigned multiplication

- 35 x 35-bit dynamic sign multiplication when the sign controls for each operand are different

- 36 x 36-bit dynamic sign multiplication when the same sign control is used for both operands

This list only shows functions that can fit into a single DSP block. Multiple DSP blocks can support larger multiplication functions.

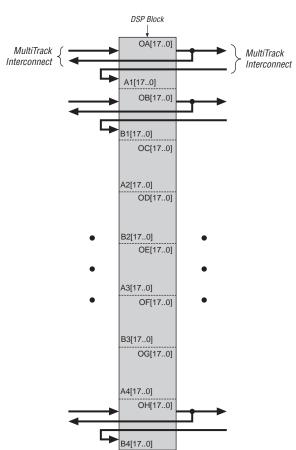

Figure 4–28 shows one of the columns with surrounding LAB rows.

The DSP block is divided into eight block units that interface with eight LAB rows on the left and right. Each block unit can be considered half of an 18 × 18-bit multiplier sub-block with 18 inputs and 18 outputs. A local interconnect region is associated with each DSP block. Like an LAB, this interconnect region can be fed with 10 direct link interconnects from the LAB to the left or right of the DSP block in the same row. All row and column routing resources can access the DSP block's local interconnect region. The outputs also work similarly to LAB outputs as well. Nine outputs from the DSP block can drive to the left LAB through direct link interconnects and nine can drive to the right LAB though direct link interconnects. All 18 outputs can drive to all types of row and column routing. Outputs can drive right- or left-column routing. Figures 4–39 and 4–40 show the DSP block interfaces to LAB rows.

Figure 4-39. DSP Block Interconnect Interface

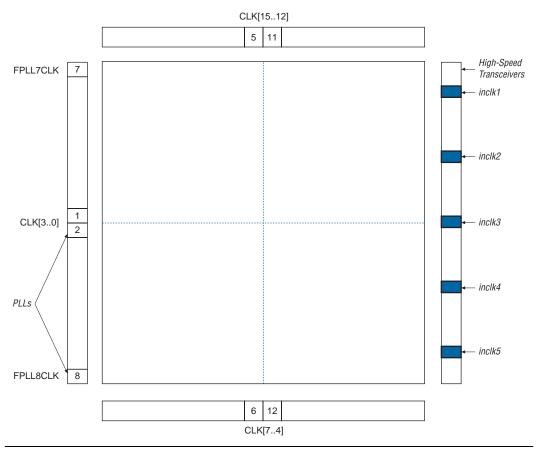

Figure 4–49 shows the global and regional clock connections from the PLL outputs and the CLK pins.

Programmable delays can increase the register-to-pin delays for output and/or output enable registers. A programmable delay exists to increase the  $t_{ZX}$  delay to the output pin, which is required for ZBT interfaces. Table 4–21 shows the programmable delays for Stratix GX devices.

| Table 4–21. Stratix GX Programma             | able Delay Chain                             |

|----------------------------------------------|----------------------------------------------|

| Programmable Delays                          | Quartus II Logic Option                      |

| Input pin to logic array delay               | Decrease input delay to internal cells       |

| Input pin to input register delay            | Decrease input delay to input register       |

| Output pin delay                             | Increase delay to output pin                 |

| Output enable register t <sub>CO</sub> delay | Increase delay to output enable pin          |

| Output t <sub>ZX</sub> delay                 | Increase t <sub>ZX</sub> delay to output pin |

| Output clock enable delay                    | Increase output clock enable delay           |

| Input clock enable delay                     | Increase input clock enable delay            |

| Logic array to output register delay         | Decrease input delay to output register      |

| Output enable clock enable delay             | Increase output enable clock enable delay    |

The IOE registers in Stratix GX devices share the same source for clear or preset. You can program preset or clear for each individual IOE. You can also program the registers to power up high or low after configuration is complete. If programmed to power up low, an asynchronous clear can control the registers. If programmed to power up high, an asynchronous preset can control the registers. This feature prevents the inadvertent activation of another device's active-low input upon power-up. If one register in an IOE uses a preset or clear signal then all registers in the IOE must use that same signal if they require preset or clear. Additionally, a synchronous reset signal is available for the IOE registers.

# Double-Data Rate I/O Pins

Stratix GX devices have six registers in the IOE, which support DDR interfacing by clocking data on both positive and negative clock edges. The IOEs in Stratix GX devices support DDR inputs, DDR outputs, and bidirectional DDR modes.

2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 4–32. Stratix GX MultiVolt I/O Support Note (1) |                  |          |              |              |              |                   |              |              |          |          |

|-------------------------------------------------------|------------------|----------|--------------|--------------|--------------|-------------------|--------------|--------------|----------|----------|

| V (V)                                                 | Input Signal (5) |          |              |              |              | Output Signal (6) |              |              |          |          |

| V <sub>CCIO</sub> (V)                                 | 1.5 V            | 1.8 V    | 2.5 V        | 3.3 V        | 5.0 V        | 1.5 V             | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V    |

| 1.5                                                   | <b>✓</b>         | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |              | <b>✓</b>          |              |              |          |          |

| 1.8                                                   | <b>√</b> (2)     | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |              | <b>√</b> (3)      | <b>✓</b>     |              |          |          |

| 2.5                                                   |                  |          | <b>✓</b>     | <b>✓</b>     |              | <b>√</b> (3)      | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                                                   |                  |          | <b>✓</b> (2) | <b>✓</b>     | <b>√</b> (4) | <b>√</b> (3)      | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |

#### Notes to Table 4-32:

- (1) To drive inputs higher than V<sub>CCIO</sub> but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent V<sub>1</sub> from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix GX device to drive out, a receiving device powered at a different level can still interface with the Stratix GX device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix GX devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix GX device.

- (6) This represents the system voltage that Stratix GX supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix GX is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

# Power Sequencing & Hot Socketing

Because Stratix GX devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Signals can be driven into Stratix GX devices before and during power up without damaging the device. In addition, Stratix GX devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix GX devices operate as specified by the user. For more information, see the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter of the *Stratix GX Device Handbook*, *Volume 2*.

| Table 6–7. Stratix GX Transceiver Block AC Specification (Part 7 of 7) |                       |                                  |     |                                                     |     |                                        |     |      |     |     |    |

|------------------------------------------------------------------------|-----------------------|----------------------------------|-----|-----------------------------------------------------|-----|----------------------------------------|-----|------|-----|-----|----|

| Symbol /<br>Description                                                | _                     | -5 Commercial<br>Speed Grade (1) |     | -6 Commercial &<br>Industrial Speed<br>Grade<br>(1) |     | -7 Commercial & Industrial Speed Grade |     | Unit |     |     |    |

|                                                                        |                       | Min                              | Тур | Max                                                 | Min | Тур                                    | Max | Min  | Тур | Max |    |

| Output return loss                                                     | 100 MHz to<br>2.5 GHz | -10                              |     |                                                     | -10 |                                        |     | -10  |     |     | dB |

#### Notes to Table 6-7:

- (1) All numbers for the -6 and -7 speed grades are for both commercial and industrial unless specified otherwise in the Conditions column. Speed grade -5 is available only for commercial specifications.

- (2) Not all  $V_{ID}$  and equalizer values will get the same results. The condition for the specification was that the  $V_{ID}$  before jitter was added is 1,000 mV and the equalizer was set to the maximum condition of 111 (equalizer control setting = 4 in the MegaWizard Plug-In Manager).

- (3) Number of parallel clocks.

- (4) Receive latency delay from serial receiver indata to parallel receiver data.

- (5) Per IEEE Standard 802.3ae @ 3.125 for -5 and -6.

- (6) The specification is for channel aligner tolerance.

- (7) UI = Unit Interval.

- (8) Run-length conditions are true for all data rates, but the average transition density must be enough to keep the receiver phase aligned and the overall data must be DC balanced.

- (9) Not all combinations of V<sub>OD</sub> and pre-emphasis will get the same results.

- (10) The numbers are for 3.125-Gbps data rate for -5 and -6 devices and 2.5 Gbps for -7 devices.

- (11) Transmitter latency delay from parallel transceiver data to serial transceiver out data.

- (12) The receiver operates with a BER of better than 10<sup>-12</sup> in the presence of an input signal as defined in the XAUI driver template for 3.125 Gbps and in the PCI Exp transmitter eye mask for 2.5 Gbps.

| Table 6–8.        | Table 6–8. LVTTL Specifications |                                               |         |         |       |  |  |  |  |  |

|-------------------|---------------------------------|-----------------------------------------------|---------|---------|-------|--|--|--|--|--|

| Symbol            | Parameter                       | Conditions                                    | Minimum | Maximum | Units |  |  |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage           |                                               | 3.0     | 3.6     | V     |  |  |  |  |  |

| V <sub>IH</sub>   | High-level input voltage        |                                               | 1.7     | 4.1     | V     |  |  |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage         |                                               | -0.5    | 0.7     | V     |  |  |  |  |  |

| V <sub>OH</sub>   | High-level output voltage       | $I_{OH} = -4 \text{ to } -24 \text{ mA } (1)$ | 2.4     |         | V     |  |  |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage        | I <sub>OL</sub> = 4 to 24 mA (1)              |         | 0.45    | V     |  |  |  |  |  |

| Table 6–9. LVCMOS Specifications |                          |            |         |         |       |  |  |  |  |

|----------------------------------|--------------------------|------------|---------|---------|-------|--|--|--|--|

| Symbol                           | Parameter                | Conditions | Minimum | Maximum | Units |  |  |  |  |

| V <sub>CCIO</sub>                | Output supply voltage    |            | 3.0     | 3.6     | V     |  |  |  |  |

| V <sub>IH</sub>                  | High-level input voltage |            | 1.7     | 4.1     | V     |  |  |  |  |

| V <sub>IL</sub>                  | Low-level input voltage  |            | -0.5    | 0.7     | V     |  |  |  |  |

| Table 6–12. 1.5-V I/O Specifications (Part 2 of 2) |                                                |                              |  |                               |   |  |  |  |

|----------------------------------------------------|------------------------------------------------|------------------------------|--|-------------------------------|---|--|--|--|

| Symbol                                             | ymbol Parameter Conditions Minimum Maximum Uni |                              |  |                               |   |  |  |  |

| $V_{OL}$                                           | Low-level output voltage                       | $I_{OL} = 2 \text{ mA } (1)$ |  | $0.25 \times V_{\text{CCIO}}$ | V |  |  |  |

*Note to Tables 6–8 through 6–12:*

(1) Drive strength is programmable according to values in found in the *Stratix GX Architecture* chapter of the *Stratix GX Device Handbook, Volume 1*.

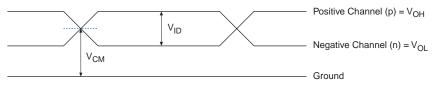

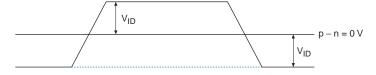

Figures 6–1 through 6–3 show receiver input and transmitter output waveforms, respectively, for all differential I/O standards (LVDS, 3.3-V PCML, LVPECL, and HyperTransport technology).

Figure 6-1. Receiver Input Waveforms for Differential I/O Standards

# Single-Ended Waveform

### **Differential Waveform**

### $(V_{ID} (Differential) = 2 \times V_{ID} (single-ended))$

| Table 6–14        | 1. 3.3-V PCML Specifications                    |            |         |                   |         |       |

|-------------------|-------------------------------------------------|------------|---------|-------------------|---------|-------|

| Symbol            | Parameter                                       | Conditions | Minimum | Typical           | Maximum | Units |

| $V_{\text{CCIO}}$ | I/O supply voltage                              |            | 3.135   | 3.3               | 3.465   | V     |

| V <sub>ID</sub>   | Input differential voltage swing (single-ended) |            | 300     |                   | 600     | mV    |

| V <sub>ICM</sub>  | Input common mode voltage                       |            | 1.5     |                   | 3.465   | V     |

| V <sub>OD</sub>   | Output differential voltage (single-ended)      |            | 300     | 370               | 500     | mV    |

| $\Delta V_{OD}$   | Change in V <sub>OD</sub> between high and low  |            |         |                   | 50      | mV    |

| V <sub>OCM</sub>  | Output common mode voltage                      |            | 2.5     | 2.85              | 3.3     | V     |

| $\Delta V_{OCM}$  | Change in V <sub>OCM</sub> between high and low |            |         |                   | 50      | mV    |

| V <sub>T</sub>    | Output termination voltage                      |            |         | V <sub>CCIO</sub> |         | V     |

| R <sub>1</sub>    | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω     |

| R <sub>2</sub>    | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω     |

| Table 6–15        | Table 6–15. LVPECL Specifications               |                        |         |         |         |       |  |  |  |  |  |

|-------------------|-------------------------------------------------|------------------------|---------|---------|---------|-------|--|--|--|--|--|

| Symbol            | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Units |  |  |  |  |  |

| V <sub>CCIO</sub> | I/O supply voltage                              |                        | 3.135   | 3.3     | 3.465   | V     |  |  |  |  |  |

| V <sub>ID</sub>   | Input differential voltage swing (single-ended) |                        | 300     |         | 1,000   | mV    |  |  |  |  |  |

| V <sub>ICM</sub>  | Input common mode voltage                       |                        | 1       |         | 2       | V     |  |  |  |  |  |

| V <sub>OD</sub>   | Differential output voltage (single ended)      | R <sub>L</sub> = 100 Ω | 525     | 700     | 970     | mV    |  |  |  |  |  |

| V <sub>OCM</sub>  | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1.5     | 1.7     | 1.9     | V     |  |  |  |  |  |

| R <sub>L</sub>    | Receiver differential input resistor, external  |                        | 90      | 100     | 110     | Ω     |  |  |  |  |  |

| Table 6–68. EP1SGX40 Column Pin Global Clock External I/O Timing Parameters |         |         |         |         |         |       |      |  |  |

|-----------------------------------------------------------------------------|---------|---------|---------|---------|---------|-------|------|--|--|

| Symbol                                                                      | -5 Spee | d Grade | -6 Spee | d Grade | -7 Spee | 11-:4 |      |  |  |

|                                                                             | Min     | Max     | Min     | Max     | Min     | Max   | Unit |  |  |

| t <sub>INSU</sub>                                                           | 2.033   |         | 2.184   |         | 2.451   |       | ns   |  |  |

| t <sub>INH</sub>                                                            | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>outco</sub>                                                          | 2.000   | 5.689   | 2.000   | 6.116   | 2.000   | 7.010 | ns   |  |  |

| t <sub>INSUPLL</sub>                                                        | 1.228   |         | 1.278   |         | 1.415   |       | ns   |  |  |

| t <sub>INHPLL</sub>                                                         | 0.000   |         | 0.000   |         | 0.000   |       | ns   |  |  |

| t <sub>OUTCOPLL</sub>                                                       | 0.500   | 2.594   | 0.500   | 2.732   | 0.500   | 3.113 | ns   |  |  |

| Table 6–69. EP1SGX40 Row Pin Fast Regional Clock External I/O Timing Parameters |         |         |         |          |         |         |      |  |

|---------------------------------------------------------------------------------|---------|---------|---------|----------|---------|---------|------|--|

| Symbol                                                                          | -5 Spee | d Grade | -6 Spee | ed Grade | -7 Spee | II.a.iA |      |  |

|                                                                                 | Min     | Max     | Min     | Max      | Min     | Max     | Unit |  |

| t <sub>INSU</sub>                                                               | 2.450   |         | 2.662   |          | 3.046   |         | ns   |  |

| t <sub>INH</sub>                                                                | 0.000   |         | 0.000   |          | 0.000   |         | ns   |  |

| t <sub>OUTCO</sub>                                                              | 2.000   | 4.880   | 2.000   | 5.241    | 2.000   | 6.004   | ns   |  |

| Symbol                | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee |       |      |

|-----------------------|----------------|-------|----------------|-------|---------|-------|------|

|                       | Min            | Max   | Min            | Max   | Min     | Max   | Unit |

| t <sub>INSU</sub>     | 2.398          |       | 2.567          |       | 2.938   |       | ns   |

| t <sub>INH</sub>      | 0.000          |       | 0.000          |       | 0.000   |       | ns   |

| t <sub>outco</sub>    | 2.000          | 4.932 | 2.000          | 5.336 | 2.000   | 6.112 | ns   |

| t <sub>INSUPLL</sub>  | 1.126          |       | 1.186          |       | 1.352   |       | ns   |

| t <sub>INHPLL</sub>   | 0.000          |       | 0.000          |       | 0.000   |       | ns   |

| t <sub>OUTCOPLL</sub> | 0.500          | 2.304 | 0.500          | 2.427 | 0.500   | 2.765 | ns   |

| Table 6–71. EP1SGX40 Row Pin Global Clock External I/O Timing Parameters (Part 1 of 2) |         |         |         |         |                |     |        |  |

|----------------------------------------------------------------------------------------|---------|---------|---------|---------|----------------|-----|--------|--|

| Symbol                                                                                 | -5 Spee | d Grade | -6 Spee | d Grade | -7 Speed Grade |     | llm:4  |  |

|                                                                                        | Min     | Max     | Min     | Max     | Min            | Max | - Unit |  |

| t <sub>INSU</sub>                                                                      | 1.965   |         | 2.128   |         | 2.429          |     | ns     |  |

| t <sub>INH</sub>                                                                       | 0.000   |         | 0.000   |         | 0.000          |     | ns     |  |

Tables 6–78 and 6–79 show the adder delays for the column and row IOE programmable delays, respectively. These delays are controlled with the Quartus II software logic options listed in the Parameter column.

| Dt                          | 0 - 44:   | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | 11-2 |

|-----------------------------|-----------|----------------|-------|----------------|-------|----------------|-------|------|

| Parameter                   | Setting — | Min            | Max   | Min            | Max   | Min            | Max   | Unit |

| Decrease input delay to     | Off       |                | 3,970 |                | 4,367 |                | 5,022 | ps   |

| internal cells              | On        |                | 3,390 |                | 3,729 |                | 4,288 | ps   |

|                             | Small     |                | 2,810 |                | 3,091 |                | 3,554 | ps   |

|                             | Medium    |                | 212   |                | 224   |                | 257   | ps   |

|                             | Large     |                | 212   |                | 224   |                | 257   | ps   |

| Decrease input delay to     | Off       |                | 3900  |                | 4,290 |                | 4,933 | ps   |

| input register              | On        |                | 0     |                | 0     |                | 0     | ps   |

| Decrease input delay to     | Off       |                | 1,240 |                | 1,364 |                | 1,568 | ps   |

| output register             | On        |                | 0     |                | 0     |                | 0     | ps   |

| Increase delay to output    | Off       |                | 0     |                | 0     |                | 0     | ps   |

| pin                         | On        |                | 377   |                | 397   |                | 456   | ps   |

| Increase delay to output    | Off       |                | 0     |                | 0     |                | 0     | ps   |

| enable pin                  | On        |                | 338   |                | 372   |                | 427   | ps   |

| Increase output clock       | Off       |                | 0     |                | 0     |                | 0     | ps   |

| enable delay                | On        |                | 540   |                | 594   |                | 683   | ps   |

|                             | Small     |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                             | Large     |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

| Increase input clock enable | Off       |                | 0     |                | 0     |                | 0     | ps   |

| delay                       | On        |                | 540   |                | 594   |                | 683   | ps   |

|                             | Small     |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                             | Large     |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

| Increase output enable      | Off       |                | 0     |                | 0     |                | 0     | ps   |

| clock enable delay          | On        |                | 540   |                | 594   |                | 683   | ps   |

|                             | Small     |                | 1,016 |                | 1,118 |                | 1,285 | ps   |

|                             | Large     |                | 1,016 | _              | 1,118 |                | 1,285 | ps   |

| Table 6–90. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 3) |                                                                                                                   |     |     |                                                            |              |  |  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|--|--|

| Symbol                                                                   | Parameter                                                                                                         | Min | Тур | Max                                                        | Unit         |  |  |  |  |  |

| t <sub>FCOMP</sub>                                                       | External feedback clock compensation time (3)                                                                     |     |     | 6                                                          | ns           |  |  |  |  |  |

| f <sub>OUT</sub>                                                         | Output frequency for internal global or regional clock                                                            | 0.3 |     | 420                                                        | MHz          |  |  |  |  |  |

| f <sub>OUT_EXT</sub>                                                     | Output frequency for external clock (2)                                                                           | 0.3 |     | 434                                                        | MHz          |  |  |  |  |  |

| t <sub>OUTDUTY</sub>                                                     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |  |  |  |

| t <sub>JITTER</sub>                                                      | Period jitter for external clock output (5)                                                                       |     |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |  |  |  |  |  |

| t <sub>CONFIG5,6</sub>                                                   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |  |

| t <sub>CONFIG11,12</sub>                                                 | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |  |

| t <sub>SCANCLK</sub>                                                     | scanclk frequency (4)                                                                                             |     |     | 22                                                         | MHz          |  |  |  |  |  |

| t <sub>DLOCK</sub>                                                       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) (10) | (8) |     | 100                                                        | μs           |  |  |  |  |  |

| t <sub>LOCK</sub>                                                        | Time required to lock from end of device configuration (10)                                                       | 10  |     | 400                                                        | μs           |  |  |  |  |  |

| f <sub>VCO</sub>                                                         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (7)                                                    | MHz          |  |  |  |  |  |