Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2566                                                        |

| Number of Logic Elements/Cells | 25660                                                       |

| Total RAM Bits                 | 1944576                                                     |

| Number of I/O                  | 455                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 672-BBGA                                                    |

| Supplier Device Package        | 672-FBGA (27x27)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25df672c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

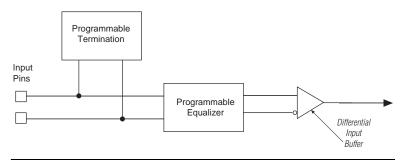

Figure 2–10 shows a diagram of the receiver input buffer, which contains:

- Programmable termination

- Programmable equalizer

Figure 2-10. Receiver Input Buffer

## **Programmable Termination**

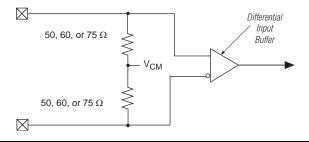

The programmable termination can be statically set in the Quartus II software. Figure 2–11 shows the setup for programmable receiver termination.

Figure 2-11. Programmable Receiver Termination

If you use external termination, then the receiver must be externally terminated and biased to 1.1 V. Figure 2–12 shows an example of an external termination/biasing circuit.

## Receiver State Machine

The receiver state machine operates in GIGE and XAUI modes. In GIGE mode, the receiver state machine replaces invalid code groups with 9'h1FE. In XAUI mode, the receiver state machine translates the XAUI PCS code group to the XAUI XGMII code group. Table 2–8 shows the code conversion. The conversion adheres to the IEEE 802.3ae specification.

| Table 2–8. Code Conversion |                                     |                                     |                         |  |  |  |  |  |

|----------------------------|-------------------------------------|-------------------------------------|-------------------------|--|--|--|--|--|

| XGMII RXC                  | XGMII RXD                           | PCS code-group                      | Description             |  |  |  |  |  |

| 0                          | 00 through FF                       | Dxx.y                               | Normal Data             |  |  |  |  |  |

| 1                          | 07                                  | K28.0 or K28.3 or K28.5             | Idle in    <b>I</b>     |  |  |  |  |  |

| 1                          | 07                                  | K28.5                               | Idle in   T             |  |  |  |  |  |

| 1                          | 9C                                  | K28.4                               | Sequence                |  |  |  |  |  |

| 1                          | FB                                  | K27.7                               | Start                   |  |  |  |  |  |

| 1                          | FD                                  | K29.7                               | Terminate               |  |  |  |  |  |

| 1                          | FE                                  | K30.7                               | Error                   |  |  |  |  |  |

| 1                          | FE                                  | Invalid code group                  | Invalid XGMII character |  |  |  |  |  |

| 1                          | See IEEE 802.3 reserved code groups | See IEEE 802.3 reserved code groups | Reserved code groups    |  |  |  |  |  |

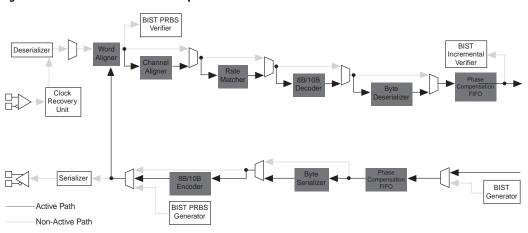

# Byte Deserializer

The byte deserializer takes a single width word (8 or 10 bits) from the transceiver logic and converts it into double-width words (16 or 20 bits) to the phase compensation FIFO buffer. The byte deserializer is bypassed when single width mode (8 or 10 bits) is used at the PLD interface.

# Phase Compensation FIFO Buffer

The receiver phase compensation FIFO buffer resides in the transceiver block at the programmable logic device (PLD) boundary. This buffer compensates for the phase difference between the recovered clock within the transceiver and the recovered clock after it has transferred to the PLD core. The phase compensation FIFO buffer is four words deep and cannot be bypassed.

## Parallel Loopback

The parallel loopback mode exercises the digital logic portion of the transceiver data path. The analog portions are not use in the loopback path. The received data is not retimed. Figure 2–22 shows the data path in parallel loopback mode. This option is not dynamically switchable. Reception of an external signal is not possible in this mode.

Figure 2-22. Data Path in Parallel Loopback Mode

# Reverse Serial Loopback

The reverse serial loopback exercises the analog portion of the transceiver. This loopback mode is dynamically switchable through the tx\_srlpbk port on a channel by channel basis. Asserting rxanalogreset in reverse serial loopback mode powers down the receiver buffer and CRU, preventing data loopback. Figure 2–23 shows the data path in reverse serial loopback mode.

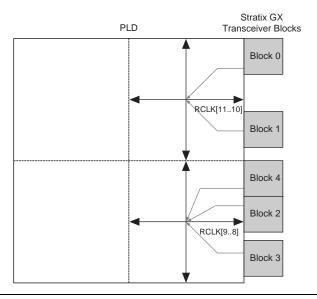

Figure 2–30. EP1SGX40 Receiver PLL Recovered Clock to Regional Clock Connection

Figure 2–31 shows the possible recovered clock connection to the fast regional clock resource. The fast regional clocks can drive logic in their associated regions.

The actual lock time for different data patterns varies depending on the data's transition density (how often the data switches between 1 and 0) and jitter characteristic. The DPA circuitry is designed to lock onto any data pattern with sufficient transition density, so the circuitry works with current and future protocols. Experiments and simulations show that the DPA circuitry locks when the data patterns listed in Table 3–4 are repeated for the specified number of times. There are other suitable patterns not shown in Table 3–4 and/or pattern lengths, but the lock time may vary. The circuit can adjust for any phase variation that may occur during operation.

| Table 3–4. Training Patterns for Different Protocols |                                                                             |     |  |  |  |  |

|------------------------------------------------------|-----------------------------------------------------------------------------|-----|--|--|--|--|

| Protocols                                            | Number of Repetitions                                                       |     |  |  |  |  |

| SPI-4, NPSI                                          | Ten 0's, ten 1's (000000000001111111111)                                    | 256 |  |  |  |  |

| RapidIO                                              | Four 0's, four 1's (00001111) or one 1, two 0's, one 1, four 0's (10010000) |     |  |  |  |  |

| Other designs                                        | Eight alternating 1's and 0's (10101010 or 01010101)                        |     |  |  |  |  |

| SFI-4, XSBI                                          | Not specified                                                               |     |  |  |  |  |

# Phase Synchronizer

Each receiver has its own phase synchronizer. The receiver phase synchronizer aligns the phase of the parallel data from all the receivers to one global clock. The synchronizers in each channel consist of a 4-bit deep and *J*-bit wide FIFO buffer. The parallel clock writes to the FIFO buffer and the global clock (GCLK) reads from the FIFO buffer. The global and parallel clock inputs into the synchronizers must have identical frequencies and differ only in phase. The FIFO buffer never becomes full or empty (because the source and receive signals are frequency locked) when operating within the DPA specifications, and the operation does not require an empty/full flag or read/write enable signals.

# Receiver Data Realignment In DPA Mode

While DPA operation aligns the incoming clock phase to the incoming data phase, it does not guarantee the parallelization boundary or byte boundary. When the dynamic phase aligner realigns the data bits, the bits may be shifted out of byte alignment, as shown in Figure 3–10.

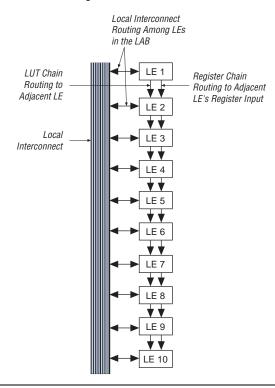

Figure 4-9. LUT Chain & Register Chain Interconnects

The C4 interconnects span four LABs, M512, or M4K blocks up or down from a source LAB. Every LAB has its own set of C4 interconnects to drive either up or down. Figure 4–10 shows the C4 interconnect connections from an LAB in a column. The C4 interconnects can drive and be driven by all types of architecture blocks, including DSP blocks, TriMatrix memory blocks, and vertical IOEs. For LAB interconnection, a primary LAB or its LAB neighbor can drive a given C4 interconnect. C4 interconnects can drive each other to extend their range as well as drive row interconnects for column-to-column connections.

RAM block and 4,608 bits for the M4K RAM block. The total number of shift register outputs (number of taps  $n \times$  width w) must be less than the maximum data width of the RAM block (18 for M512 blocks, 36 for M4K blocks). To create larger shift registers, the memory blocks are cascaded together.

Data is written into each address location at the falling edge of the clock and read from the address at the rising edge of the clock. The shift register mode logic automatically controls the positive and negative edge clocking to shift the data in one clock cycle. Figure 4–13 shows the TriMatrix memory block in the shift register mode.

m-Bit Shift Register

Figure 4-13. Shift Register Memory Configuration

# **Memory Block Size**

TriMatrix memory provides three different memory sizes for efficient application support. The large number of M512 blocks are ideal for designs with many shallow first-in first-out (FIFO) buffers. M4K blocks provide additional resources for channelized functions that do not require large amounts of storage. The M-RAM blocks provide a large

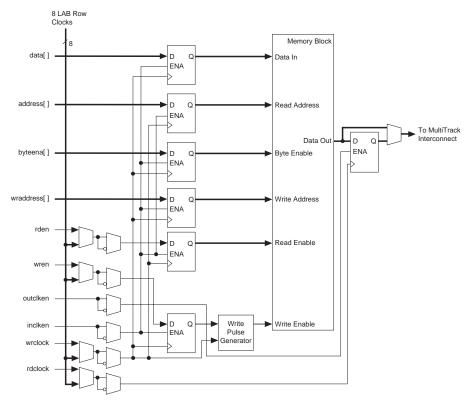

Figure 4–25. Input/Output Clock Mode in Simple Dual-Port Mode Note (1)

Note to Figure 4-25:

(1) All registers shown except the rden register have asynchronous clear ports.

# Read/Write Clock Mode

The memory blocks implement read/write clock mode for simple dual-port memory. You can use up to two clocks in this mode. The write clock controls the block's data inputs, wraddress, and wren. The read clock controls the data output, rdaddress, and rden. The memory blocks support independent clock enables for each clock and asynchronous clear signals for the read- and write-side registers. Figure 4–26 shows a memory block in read/write clock mode.

clocking, programmable bandwidth, phase and delay control, and dynamic PLL reconfiguration, the Stratix GX device's enhanced PLLs provide you with complete control of your clocks and system timing. The fast PLLs provide general purpose clocking with multiplication and phase shifting as well as high-speed outputs for high-speed differential I/O support. Enhanced and fast PLLs work together with the Stratix GX high-speed I/O and advanced clock architecture to provide significant improvements in system performance and bandwidth.

The Quartus II software enables the PLLs and their features without requiring any external devices. Table 4–17 shows which PLLs are available for each Stratix GX device and their type. Table 4–18 shows the enhanced PLL and fast PLL features in Stratix GX devices.

| Table 4–17. Stratix GX Device PLL Availability |          |             |       |              |          |          |       |        |              |          |               |                      |

|------------------------------------------------|----------|-------------|-------|--------------|----------|----------|-------|--------|--------------|----------|---------------|----------------------|

|                                                |          |             |       |              |          |          |       | Enhanc | ed PLLs      |          |               |                      |

| Device                                         | 1        | 2           | 3 (1) | <b>4</b> (1) | 7        | 8        | 9 (1) | 10 (1) | <b>5</b> (2) | 6 (2)    | <b>11</b> (3) | <b>12</b> <i>(3)</i> |

| EP1SGX10                                       | <b>✓</b> | <b>✓</b>    |       |              |          |          |       |        | <b>✓</b>     | <b>✓</b> |               |                      |

| EP1SGX25                                       | <b>✓</b> | <b>✓</b>    |       |              |          |          |       |        | <b>✓</b>     | <b>✓</b> |               |                      |

| EP1SGX40                                       | <b>\</b> | <b>&gt;</b> |       |              | <b>\</b> | <b>✓</b> |       |        | <b>&gt;</b>  | <b>✓</b> | <b>✓</b>      | <b>\</b>             |

#### Notes to Table 4–17:

- (1) PLLs 3, 4, 9, and 10 are not available in Stratix GX devices. However, these PLLs are listed in Table 4–17 because the Stratix GX PLL numbering scheme is consistent with Stratix devices.

- (2) PLLs 5 and 6 each have eight single-ended outputs or four differential outputs.

- (3) PLLs 11 and 12 each have one single-ended output.

| Feature                           | Enhanced PLL                          | Fast PLL                           |

|-----------------------------------|---------------------------------------|------------------------------------|

| Clock multiplication and division | m/ (n × post-scale counter) (1)       | m/(post-scale counter) (2)         |

| Phase shift                       | Down to 156.25-ps increments (3), (4) | Down to 125-ps increments (3), (4) |

| Delay shift                       | 250-ps increments for ±3 ns           |                                    |

| Clock switchover                  | ✓                                     |                                    |

| PLL reconfiguration               | ✓                                     |                                    |

| Programmable bandwidth            | ✓                                     |                                    |

| Spread spectrum clocking          | ✓                                     |                                    |

| Programmable duty cycle           | ✓                                     | ✓                                  |

| Number of internal clock outputs  | 6                                     | 3 (5)                              |

feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop.

- Normal mode: If an internal clock is used in this mode, it is phase-aligned to the input clock pin. The external clock output pin has a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL does not compensate for any clock networks or external clock outputs.

## Phase & Delay Shifting

Stratix GX device enhanced PLLs provide advanced programmable phase and clock delay shifting. For phase shifting, you can specify a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. Phase-shifting values in time units are allowed with a resolution range of 160 to 420 ps. This resolution is a function of frequency input and the multiplication and division factors. In other words, it is a function of the VCO period equal to one-eighth of the VCO period. Each clock output counter can choose a different phase of the VCO period from up to eight taps. You can use this clock output counter along with an initial setting on the post-scale counter to achieve a phase-shift range for the entire period of the output clock. The phase tap feedback to the *m* counter can shift all outputs to a single phase or delay. The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entered.

In addition to the phase-shift feature, the fine tune clock delay shift feature provides advanced time delay shift control on each of the four PLL outputs. Each PLL output shifts in 250-ps increments for a range of  $-3.0\,\mathrm{ns}$  to  $+3.0\,\mathrm{ns}$  between any two outputs using discrete delay elements. Total delay shift between any two PLL outputs must be less than 3 ns. For example, shifts on outputs of -1 and +2 ns is allowed, but not -1 and  $+2.5\,\mathrm{ns}$ . There is some delay variation due to process, voltage, and temperature. Only the clock delay shift blocks can be controlled during system operation for dynamic clock delay control.

## Spread-Spectrum Clocking

The Stratix GX device's enhanced PLLs use spread-spectrum technology to reduce electromagnetic interference generation from a system by distributing the energy over a broader frequency range. The enhanced

PLL typically provides 0.5% down spread modulation using a triangular profile. The modulation frequency is programmable. Enabling spread spectrum for a PLL affects all of its outputs.

## Lock Detect

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. You may need to gate the lock signal for use as a system control. The lock signal from the locked port can drive the logic array or an output pin.

Whenever the PLL loses lock for any reason (be it excessive inclk jitter, clock switchover, PLL reconfiguration, power supply noise etc.), the PLL must be reset with the areset signal for correct phase shift operation. If the phase relationship between the input clock versus output clock, and between different output clocks from the PLL is not important in the design, then the PLL need not be reset.

See the *Stratix GX FPGA Errata Sheet* for more information on implementing the gated lock signal in the design.

# Programmable Duty Cycle

The programmable duty cycle allows enhanced PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each enhanced PLL post-scale counter (g0..g3, l0..l3, e0..e3). The duty cycle setting is achieved by a low and high time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

## Advanced Clear & Enable Control

There are several control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and gate PLL output clocks for low-power applications.

The pllenable pin is a dedicated pin that enables/disables PLLs. When the pllenable pin is low, the clock output ports are driven by GND and all the PLLs go out of lock. When the pllenable pin goes high again, the PLLs relock and resynchronize to the input clocks. You can choose which PLLs are controlled by the pllenable signal by connecting the pllenable input port of the altpll megafunction to the common pllenable input pin.

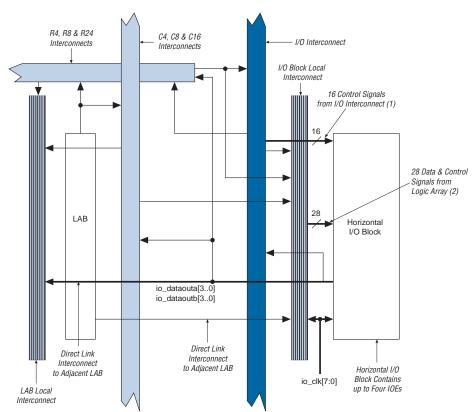

Figure 4-59. Row I/O Block Connection to the Interconnect

#### Notes to Figure 4-59:

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

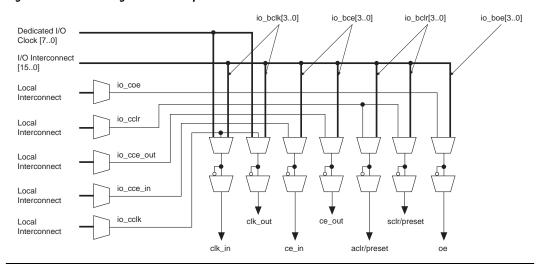

Figure 4-62. Control Signal Selection per IOE

In normal bidirectional operation, the input register can be used for input data requiring fast setup times. The input register can have its own clock input and clock enable separate from the OE and output registers. The output register can be used for data requiring fast clock-to-output performance. The OE register can be used for fast clock-to-output enable timing. The OE and output register share the same clock source and the same clock enable source from local interconnect in the associated LAB, dedicated I/O clocks, and the column and row interconnects. Figure 4–63 shows the IOE in bidirectional configuration.

Table 4–23 shows the number of DQ and DQS buses that are supported per device.

| Table 4–23. | DQS & DQ Bus Mode Support | Note (1)               |                         |                         |

|-------------|---------------------------|------------------------|-------------------------|-------------------------|

| Device      | Package                   | Number of ×8<br>Groups | Number of ×16<br>Groups | Number of ×32<br>Groups |

| EP1SGX10    | 672-pin FineLine BGA      | 12 (2)                 | 0                       | 0                       |

| EP1SGX25    | 672-pin FineLine BGA      | 16 (3)                 | 8                       | 4                       |

|             | 1,020-pin FineLine BGA    | 20                     | 8                       | 4                       |

| EP1SGX40    | 1,020-pin FineLine BGA    | 20                     | 8                       | 4                       |

#### Notes to Table 4-23:

- See the Selectable I/O Standards in Stratix & Stratix GX Devices chapter of the Stratix GX Device Handbook, Volume 2 for V<sub>RFF</sub> guidelines.

- (2) These packages have six groups in I/O banks 3 and 4 and six groups in I/O banks 7 and 8.

- (3) These packages have eight groups in I/O banks 3 and 4 and eight groups in I/O banks 7 and 8.

A compensated delay element on each DQS pin automatically aligns input DQS synchronization signals with the data window of their corresponding DQ data signals. The DQS signals drive a local DQS bus in the top and bottom I/O banks. This DQS bus is an additional resource to the I/O clocks and clocks DQ input registers with the DQS signal.

Two separate single phase-shifting reference circuits are located on the top and bottom of the Stratix GX device. Each circuit is driven by a system reference clock through the CLK pins that is the same frequency as the DQS signal. Clock pins CLK [15..12] p feed the phase-shift circuitry on the top of the device and clock pins CLK [7..4] p feed the phase-shift circuitry on the bottom of the device. The phase-shifting reference circuit on the top of the device controls the compensated delay elements for all 10 DQS pins located at the top of the device. The phase-shifting reference circuit on the bottom of the device controls the compensated delay elements for all 10 DQS pins located on the bottom of the device. All 10 delay elements (DQS signals) on either the top or bottom of the device shift by the same degree amount. For example, all 10 DQS pins on the top of the device can be shifted by 90° and all 10 DQS pins on the bottom of the device can be shifted by 72°. The reference circuits require a maximum of 256 system reference clock cycles to set the correct phase on the DQS delay elements. Figure 4–68 illustrates the phase-shift reference circuit control of each DQS delay shift on the top of the device. This same circuit is duplicated on the bottom of the device.

Table 4–24 shows the possible settings for the I/O standards with drive strength control.

| Table 4–24. Programmable Drive Strength                                                                                         |                                                                 |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|--|--|--|--|

| I/O Standard                                                                                                                    | I <sub>OH</sub> / I <sub>OL</sub> Current Strength Setting (mA) |  |  |  |  |

| 3.3-V LVTTL                                                                                                                     | 24 (1), 16, 12, 8, 4                                            |  |  |  |  |

| 3.3-V LVCMOS                                                                                                                    | 24 (2), 12 (1), 8, 4, 2                                         |  |  |  |  |

| 2.5-V LVTTL/LVCMOS                                                                                                              | 16 (1), 12, 8, 2                                                |  |  |  |  |

| 1.8-V LVTTL/LVCMOS                                                                                                              | 12 (1), 8, 2                                                    |  |  |  |  |

| 1.5-V LVCMOS                                                                                                                    | 8 (1), 4, 2                                                     |  |  |  |  |

| GTL/GTL+ 1.5-V HSTL class I and II 1.8-V HSTL class I and II SSTL-3 class I and II SSTL-2 class I and II SSTL-18 class I and II | Support maximum and minimum strength                            |  |  |  |  |

Notes to Table 4-24:

- (1) This is the Quartus II software default current setting.

- (2) I/O banks 1 and 2 do not support this setting.

The Quartus II software, beginning with version 4.2, reports current strength as "PCI Compliant" for 3.3-V PCI, 3.3-V PCI-X 1.0, and Compact PCI I/O standards.

Stratix GX devices support series on-chip termination (OCT) using programmable drive strength. For more information, contact your Altera Support Representative.

# **Open-Drain Output**

Stratix GX devices provide an optional open-drain (equivalent to an open-collector) output for each I/O pin. This open-drain output enables the device to provide system-level control signals (that is, interrupt and write-enable signals) that can be asserted by any of several devices.

## Slew-Rate Control

The output buffer for each Stratix GX device I/O pin has a programmable output slew-rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew-rate control, allowing you to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

## **Bus Hold**

Each Stratix GX device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not needed to hold a signal level when the bus is tri-stated.

Table 4–25 shows bus hold support for different pin types.

| Table 4–25. Bus Hold Support |          |  |  |  |  |

|------------------------------|----------|--|--|--|--|

| Pin Type                     | Bus Hold |  |  |  |  |

| I/O pins                     | ✓        |  |  |  |  |

| CLK[150]                     |          |  |  |  |  |

| CLK[0,1,2,3,8,9,10,11]       |          |  |  |  |  |

| FCLK                         | <b>✓</b> |  |  |  |  |

| FPLL[710]CLK                 |          |  |  |  |  |

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when using opendrain outputs with the GTL+ I/O standard or when the I/O pin has been configured for differential signals.

Table 4–28 shows I/O standard support for each I/O bank.

| Table 4–28. I/O Support by Bank (Part 1 of 2) |                                     |                       |                                                                 |  |  |  |  |  |

|-----------------------------------------------|-------------------------------------|-----------------------|-----------------------------------------------------------------|--|--|--|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left Banks<br>(1 & 2) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |  |  |  |

| LVTTL                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| LVCMOS                                        | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 2.5 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 1.8 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 1.5 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 3.3-V PCI                                     | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| 3.3-V PCI-X 1.0                               | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| LVPECL                                        |                                     | ✓                     | ✓                                                               |  |  |  |  |  |

| 3.3-V PCML                                    |                                     | ✓                     | ✓                                                               |  |  |  |  |  |

| LVDS                                          |                                     | ✓                     | ✓                                                               |  |  |  |  |  |

| HyperTransport technology                     |                                     | ✓                     | ✓                                                               |  |  |  |  |  |

| Differential HSTL (clock inputs)              | ~                                   | ✓                     |                                                                 |  |  |  |  |  |

| Differential HSTL (clock outputs)             |                                     |                       | ✓                                                               |  |  |  |  |  |

| Differential SSTL (clock outputs)             |                                     |                       | <b>✓</b>                                                        |  |  |  |  |  |

| 3.3-V GTL                                     | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| 3.3-V GTL+                                    | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 1.5-V HSTL class I                            | ✓                                   | <b>✓</b>              | <b>✓</b>                                                        |  |  |  |  |  |

| 1.5-V HSTL class II                           | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| 1.8-V HSTL class I                            | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| 1.8-V HSTL class II                           | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| SSTL-18 class I                               | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| SSTL-18 class II                              | ✓                                   |                       | ✓                                                               |  |  |  |  |  |

| SSTL-2 class I                                | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| SSTL-2 class II                               | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| SSTL-3 class I                                | ✓                                   | ✓                     | ✓                                                               |  |  |  |  |  |

| Table 6–56. EP1SGX10 Column Pin Global Clock External I/O Timing Parameters |         |                |       |                |       |                |      |  |

|-----------------------------------------------------------------------------|---------|----------------|-------|----------------|-------|----------------|------|--|

| Symbol                                                                      | -5 Spee | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |      |  |

|                                                                             | Min     | Max            | Min   | Max            | Min   | Max            | Unit |  |

| t <sub>INSU</sub>                                                           | 1.785   |                | 1.814 |                | 2.087 |                | ns   |  |

| t <sub>INH</sub>                                                            | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |

| t <sub>OUTCO</sub>                                                          | 2.000   | 5.057          | 2.000 | 5.438          | 2.000 | 6.214          | ns   |  |

| t <sub>INSUPLL</sub>                                                        | 0.988   |                | 0.936 |                | 1.066 |                | ns   |  |

| t <sub>INHPLL</sub>                                                         | 0.000   |                | 0.000 |                | 0.000 |                | ns   |  |

| toutcopll                                                                   | 0.500   | 2.634          | 0.500 | 2.774          | 0.500 | 3.162          | ns   |  |

| Table 6–57. EP1SGX10 Row Pin Fast Regional Clock External I/O Timing Parameters |         |         |                              |       |       |         |      |  |

|---------------------------------------------------------------------------------|---------|---------|------------------------------|-------|-------|---------|------|--|

| O. mahad                                                                        | -5 Spee | d Grade | -6 Speed Grade -7 Speed Grad |       |       | d Grade | 1124 |  |

| Symbol                                                                          | Min     | Max     | Min                          | Max   | Min   | Max     | Unit |  |

| t <sub>INSU</sub>                                                               | 2.194   |         | 2.384                        |       | 2.727 |         | ns   |  |

| t <sub>INH</sub>                                                                | 0.000   |         | 0.000                        |       | 0.000 |         | ns   |  |

| t <sub>OUTCO</sub>                                                              | 2.000   | 4.956   | 2.000                        | 4.971 | 2.000 | 5.463   | ns   |  |

| Table 6–58. EP1SGX10 Row Pin Regional Clock External I/O Timing Parameters |                |       |                |       |         |       |      |

|----------------------------------------------------------------------------|----------------|-------|----------------|-------|---------|-------|------|

| Symbol                                                                     | -5 Speed Grade |       | -6 Speed Grade |       | -7 Spee | 1114  |      |

|                                                                            | Min            | Max   | Min            | Max   | Min     | Max   | Unit |

| t <sub>INSU</sub>                                                          | 2.244          |       | 2.413          |       | 2.574   |       | ns   |

| t <sub>INH</sub>                                                           | 0.000          |       | 0.000          |       | 0.000   |       | ns   |

| t <sub>OUTCO</sub>                                                         | 2.000          | 4.906 | 2.000          | 4.942 | 2.000   | 5.616 | ns   |

| t <sub>INSUPLL</sub>                                                       | 1.126          |       | 1.186          |       | 1.352   |       | ns   |

| t <sub>INHPLL</sub>                                                        | 0.000          |       | 0.000          |       | 0.000   |       | ns   |

| toutcopll                                                                  | 0.500          | 2.804 | 0.500          | 2.627 | 0.500   | 2.765 | ns   |

| Table 6–59. EP1SGX10 Row Pin Global Clock External I/O Timing Parameters (Part 1 of 2) |                |     |         |         |         |      |        |  |  |

|----------------------------------------------------------------------------------------|----------------|-----|---------|---------|---------|------|--------|--|--|

| Symbol                                                                                 | -5 Speed Grade |     | -6 Spee | d Grade | -7 Spee | IIi4 |        |  |  |

|                                                                                        | Min            | Max | Min     | Max     | Min     | Max  | - Unit |  |  |

| t <sub>INSU</sub>                                                                      | 1.919          |     | 2.062   |         | 2.368   |      | ns     |  |  |

| t <sub>INH</sub>                                                                       | 0.000          |     | 0.000   |         | 0.000   |      | ns     |  |  |

| Table 6–87. High-Speed I/O Specifications (Part 2 of 4) Notes (1), (2)                             |                              |                |     |      |                |     |      |                |     |      |      |

|----------------------------------------------------------------------------------------------------|------------------------------|----------------|-----|------|----------------|-----|------|----------------|-----|------|------|

| Symbol                                                                                             | Conditions                   | -5 Speed Grade |     |      | -6 Speed Grade |     |      | -7 Speed Grade |     |      |      |

|                                                                                                    |                              | Min            | Тур | Max  | Min            | Тур | Max  | Min            | Тур | Max  | Unit |

| f <sub>HSDR</sub> Device                                                                           | J = 10                       | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| operation<br>(LVDS,                                                                                | J = 8                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| LVPECL,                                                                                            | J = 7                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| HyperTransport                                                                                     | J = 4                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| technology)                                                                                        | J = 2                        | 100            |     | 624  | 100            |     | 624  | 100            |     | 462  | Mbps |

|                                                                                                    | J = 1 (LVDS and LVPECL only) | 100            |     | 462  | 100            |     | 462  | 100            |     | 462  | Mbps |

| f <sub>HSDRDPA</sub> (LVDS,                                                                        | J=10                         | 300            |     | 1000 | 300            |     | 840  | 300            |     | 840  | Mbps |

| LVPECL)                                                                                            | J=8                          | 300            |     | 1000 | 300            |     | 840  | 300            |     | 840  | Mbps |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(PCML)<br>f <sub>HSCLK</sub> =<br>f <sub>HSDR</sub> / W | W = 1 to 30                  | 10             |     | 400  | 10             |     | 400  | 10             |     | 311  | MHz  |

| f <sub>HSDR</sub> Device                                                                           | <i>J</i> = 10                | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

| operation<br>(PCML)                                                                                | J = 8                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

| (I OWIE)                                                                                           | J = 7                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

|                                                                                                    | J = 4                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

|                                                                                                    | J = 2                        | 100            |     | 400  | 100            |     | 400  | 100            |     | 300  | Mbps |

|                                                                                                    | J = 1                        | 100            |     | 250  | 100            |     | 250  | 100            |     | 200  | Mbps |

| DPA Run<br>Length                                                                                  |                              |                |     | 6400 |                |     | 6400 |                |     | 6400 | UI   |

| DPA Jitter<br>Tolerance <sub>(p-p)</sub>                                                           | all data rates               |                |     | 0.44 |                |     | 0.44 |                |     | 0.44 | UI   |

| DPA Minimum<br>Eye opening<br>(p-p)                                                                |                              | 0.56           |     |      | 0.56           |     |      | 0.56           |     |      | UI   |

| DPA Receiver<br>Latency                                                                            |                              | 5              |     | 9    | 5              |     | 9    | 5              |     | 9    | (3)  |

| Table 6–90. Enhanced PLL Specifications for -7 Speed Grade (Part 2 of 3) |                                                                                                                   |     |     |                                                            |              |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|

| Symbol                                                                   | Parameter                                                                                                         |     | Тур | Max                                                        | Unit         |  |  |  |

| t <sub>FCOMP</sub>                                                       | External feedback clock compensation time (3)                                                                     |     |     | 6                                                          | ns           |  |  |  |

| f <sub>OUT</sub>                                                         | Output frequency for internal global or regional clock                                                            | 0.3 |     | 420                                                        | MHz          |  |  |  |

| f <sub>OUT_EXT</sub>                                                     | Output frequency for external clock (2)                                                                           | 0.3 |     | 434                                                        | MHz          |  |  |  |

| t <sub>OUTDUTY</sub>                                                     | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |  |

| t <sub>JITTER</sub>                                                      | Period jitter for external clock output (5)                                                                       |     |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |  |  |  |

| t <sub>CONFIG5,6</sub>                                                   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |

| t <sub>CONFIG11,12</sub>                                                 | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |

| t <sub>SCANCLK</sub>                                                     | scanclk frequency (4)                                                                                             |     |     | 22                                                         | MHz          |  |  |  |

| t <sub>DLOCK</sub>                                                       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) (10) | (8) |     | 100                                                        | μs           |  |  |  |

| t <sub>LOCK</sub>                                                        | Time required to lock from end of device configuration (10)                                                       | 10  |     | 400                                                        | μs           |  |  |  |

| f <sub>VCO</sub>                                                         | PLL internal VCO operating range                                                                                  | 300 |     | 600 (7)                                                    | MHz          |  |  |  |