Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                            |

|--------------------------------|------------------------------------------------------------|

| Product Status                 | Obsolete                                                   |

| Number of LABs/CLBs            | 2566                                                       |

| Number of Logic Elements/Cells | 25660                                                      |

| Total RAM Bits                 | 1944576                                                    |

| Number of I/O                  | 455                                                        |

| Number of Gates                | -                                                          |

| Voltage - Supply               | 1.425V ~ 1.575V                                            |

| Mounting Type                  | Surface Mount                                              |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                         |

| Package / Case                 | 672-BBGA                                                   |

| Supplier Device Package        | 672-FBGA (27x27)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25df672i6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 2–5. Receiver PLL & CRU Adjustable Parameters (Part 2 of 2) |                                               |  |  |

|-------------------------------------------------------------------|-----------------------------------------------|--|--|

| Multiplication factor (W)                                         | 2, 4, 5, 8, 10, 16, or 20 <i>(1)</i>          |  |  |

| PPM detector                                                      | 125, 250, 500, 1,000                          |  |  |

| Bandwidth Low, medium, high                                       |                                               |  |  |

| Run length detector                                               | 10-bit or 20-bit mode: 5 to 160 in steps of 5 |  |  |

|                                                                   | 8-bit or 16-bit mode: 4 to 128 in steps of 4  |  |  |

Note to Table 2-5:

(1) Multiplication factors 2, 4, and 5 can only be achieved with the use of the predivider on the REFCLKB port or if the CRU is trained with the low speed clock from the transmitter PLL.

The CRU has a built-in switchover circuit to select whether the voltage-controlled oscillator of the PLL is trained by the reference clock or the data. The optional port rx\_freqlocked monitors when the CRU is in locked to data mode.

In the automatic mode, the following conditions must be met for the CRU to switch from locked to reference to locked to data mode:

- The CRU PLL is within the prescribed PPM frequency threshold setting (125 PPM, 250 PPM, 500 PPM, 1,000 PPM) of the CRU reference clock.

- The reference clock and CRU PLL output are phase matched (phases are within .08 UI).

The automatic switchover circuit can be overridden by using the optional ports rx\_lockedtorefclk and rx\_locktodata. Table 2–6 shows the possible combinations of these two signals.

| Table 2–6. Possible Combinations of rx_lockedtorefclk & rx_locktodata |   |               |  |  |  |

|-----------------------------------------------------------------------|---|---------------|--|--|--|

| rx_locktodata rx_lockedtorefclk VCO (lock to mode)                    |   |               |  |  |  |

| 0                                                                     | 0 | Auto          |  |  |  |

| 0                                                                     | 1 | Reference CLK |  |  |  |

| 1                                                                     | х | DATA          |  |  |  |

If the rx\_lockedtorefclk and rx\_locktodata ports are not used, the default is auto mode.

#### XAUI Mode

In XAUI mode, the rate matcher adheres to clause 48 of the IEEE 802.3ae specification for clock rate compensation. The rate matcher performs clock compensation on columns of /R/ (/K28.0/), denoted by //R//. An //R// is added or deleted automatically based on the number of words in the FIFO buffer.

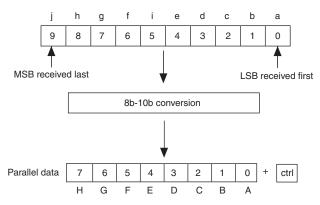

#### 8B/10B Decoder

The 8B/10B decoder converts the 10-bit encoded code group into 8-bit data and 1 control bit. The 8B/10B decoder can be bypassed. The following is a diagram of the conversion from a 10-bit encoded code group into 8-bit data + 1-bit control.

Figure 2-20. 8B/10B Decoder Conversion

There are two optional error status ports available in the 8B/10B decoder, rx\_errdetect and rx\_disperr. Table 2–7 shows the values of the ports from a given error. These status signals are aligned with the code group in which the error occurred.

| Table 2–7. Error Signal Values |              |            |  |  |  |

|--------------------------------|--------------|------------|--|--|--|

| Types of Errors                | rx_errdetect | rx_disperr |  |  |  |

| No errors                      | 1'b0         | 1'b0       |  |  |  |

| Invalid code groups            | 1'b1         | 1'b0       |  |  |  |

| Disparity errors               | 1'b1         | 1'b1       |  |  |  |

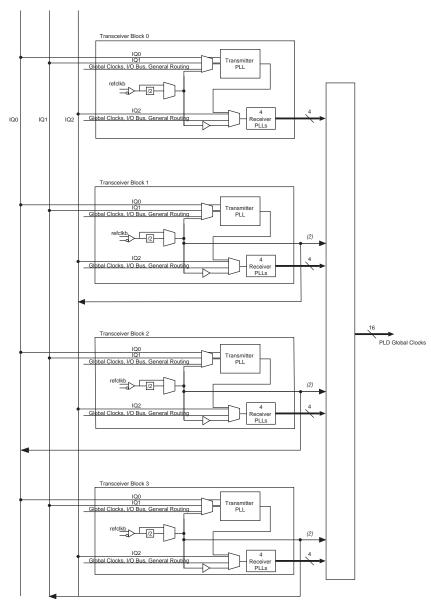

Figure 2–26. EP1SGX25F Device Inter-Transceiver & Global Clock Connections Note (1)

Notes to Figure 2–26:

- (1) IQ lines are inter-transceiver block lines.

- (2) If the /2 pre-divider is used, the path to drive the PLD logic array, local, or global clocks is not allowed.

- (3) There are four receiver PLLs in each transceiver block.

| Table 2–10. Possible Clocking Connections for Transceivers (Part 2 of 2) |                                              |              |  |  |  |  |  |

|--------------------------------------------------------------------------|----------------------------------------------|--------------|--|--|--|--|--|

| Destination                                                              |                                              |              |  |  |  |  |  |

| Source                                                                   | Transmitter Receiver GCLK RCLK FCLK IQ Lines |              |  |  |  |  |  |

| IQ lines                                                                 | <b>√</b> (2)                                 | <b>√</b> (2) |  |  |  |  |  |

Notes to Table 2-10:

- (1) REFCLKB from transceiver block 0 and transceiver block 4 does not drive the inter-transceiver lines or the GCLK lines

- (2) Inter-transceiver line 0 and inter-transceiver line 1 drive the transmitter PLL, while inter-transceiver line 2 drives the receiver PLLs.

## Other Transceiver Features

Other important features of the Stratix GX transceivers are the power down and reset capabilities, the external voltage reference and bias circuitry, and hot swapping.

#### Individual Power-Down & Reset for the Transmitter & Receiver

Stratix GX transceivers offer a power saving advantage with their ability to shut off functions that are not needed. The device can individually reset the receiver and transmitter blocks and the PLLs. The Stratix GX device can either globally power down and reset the transmitter and receiver channels or do each channel separately. Table 2–11 shows the connectivity between the reset signals and the Stratix GX logical blocks.

# 3. Source-Synchronous Signaling With DPA

SGX51003-1.1

### Introduction

Expansion in the telecommunications market and growth in Internet use requires systems to move more data faster than ever. To meet this demand, rely on solutions such as differential signaling and emerging high-speed interface standards including RapidIO, POS-PHY 4, SFI-4, or XSBI.

These new protocols support differential data rates up to 1 Gbps and higher. At these high data rates, it becomes more challenging to manage the skew between the clock and data signals. One solution to this challenge is to use CDR to eliminate skew between data channels and clock signals. Another potential solution, DPA, is beginning to be incorporated into some of these protocols.

The source-synchronous high-speed interface in Stratix GX devices is a dedicated circuit embedded into the PLD allowing for high-speed communications. The *High-Speed Source-Synchronous Differential I/O Interfaces in Stratix GX Devices* chapter of the *Stratix GX Device Handbook, Volume 2* provides information on the high-speed I/O standard features and functions of the Stratix GX device.

#### Stratix GX I/O Banks

Stratix GX devices contain 17 I/O banks. I/O banks one and two support high-speed LVDS, LVPECL, and 3.3-V PCML inputs and outputs. These two banks also incorporate an embedded dynamic phase aligner within the source-synchronous interface (see Figure 3–8 on page 3–10). The dynamic phase aligner corrects for the phase difference between the clock and data lines caused by skew. The dynamic phase aligner operates automatically and continuously without requiring a fixed training pattern, and allows the source-synchronous circuitry to capture data correctly regardless of the channel-to-clock skew.

## **Principles of SERDES Operation**

Stratix GX devices support source-synchronous differential signaling up to 1 Gbps in DPA mode, and up to 840 Mbps in non-DPA mode. Serial data is transmitted and received along with a low-frequency clock. The PLL can multiply the incoming low-frequency clock by a factor of 1 to 10. The SERDES factor *J* can be 8 or 10 for the DPA mode, or 4, 7, 8, or 10 for all other modes. The SERDES factor does not have to equal the clock

interconnects can drive and be driven by all types of architecture blocks similar to C4 interconnects. C8 interconnects can drive each other to extend their range as well as R8 interconnects for column-to-column connections. C8 interconnects are faster than two C4 interconnects.

C16 column interconnects span a length of 16 LABs and provide the fastest resource for long column connections between LABs, TriMatrix memory blocks, DSP blocks, and IOEs. C16 interconnects can cross M-RAM blocks and also drive to row and column interconnects at every fourth LAB. C16 interconnects drive LAB local interconnects via C4 and R4 interconnects and do not drive LAB local interconnects directly.

All embedded blocks communicate with the logic array similar to LAB-to-LAB interfaces. Each block (that is, TriMatrix memory and DSP blocks) connects to row and column interconnects and has local interconnect regions driven by row and column interconnects. These blocks also have direct link interconnects for fast connections to and from a neighboring LAB. All blocks are fed by the row LAB clocks, labclk [7..0].

| Table 4–8. M-RAM Block Configurations (True Dual-Port) |                                |          |          |   |  |  |  |

|--------------------------------------------------------|--------------------------------|----------|----------|---|--|--|--|

| Dout A                                                 |                                | Port B   |          |   |  |  |  |

| Port A                                                 | 64K × 9 32K × 18 16K × 36 8K × |          |          |   |  |  |  |

| 64K × 9                                                | <b>✓</b>                       | <b>✓</b> | <b>✓</b> | ✓ |  |  |  |

| 32K × 18                                               | ✓                              | ✓        | ✓        | ✓ |  |  |  |

| 16K × 36                                               | ✓                              | ✓        | ✓        | ✓ |  |  |  |

| 8K × 72                                                | <b>✓</b>                       | ✓        | <b>✓</b> | ✓ |  |  |  |

The read and write operation of the memory is controlled by the WREN signal, which sets the ports into either read or write modes. There is no separate read enable (RE) signal.

Writing into RAM is controlled by both the WREN and byte enable (byteena) signals for each port. The default value for the byteena signal is high, in which case writing is controlled only by the WREN signal. The byte enables are available for the ×18, ×36, and ×72 modes. In the ×144 simple dual-port mode, the two sets of byteena signals (byteena\_a and byteena\_b) are combined to form the necessary 16 byte enables. Tables 4–9 and 4–10 summarize the byte selection.

| Table 4–9. Byte Enable for M-RAM Blocks Notes (1), (2) |                                   |        |        |  |  |  |

|--------------------------------------------------------|-----------------------------------|--------|--------|--|--|--|

| byteena[30]                                            | byteena[30] datain ×18 datain ×36 |        |        |  |  |  |

| [0] = 1                                                | [80]                              | [80]   | [80]   |  |  |  |

| [1] = 1                                                | [179]                             | [179]  | [179]  |  |  |  |

| [2] = 1                                                | _                                 | [2618] | [2618] |  |  |  |

| [3] = 1                                                | -                                 | [3527] | [3527] |  |  |  |

| [4] = 1                                                | _                                 | _      | [4436] |  |  |  |

| [5] = 1                                                | _                                 | _      | [5345] |  |  |  |

| [6] = 1                                                | _                                 | _      | [6254] |  |  |  |

| [7] = 1                                                | _                                 | _      | [7163] |  |  |  |

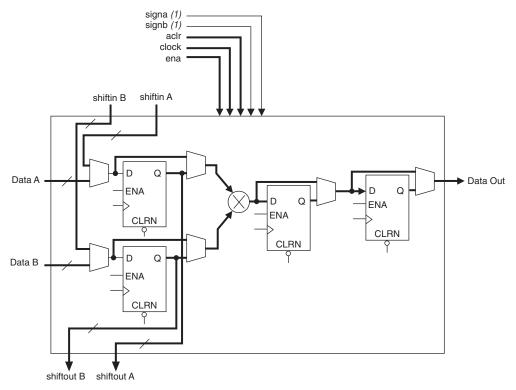

#### Input Registers

A bank of optional input registers is located at the input of each multiplier and multiplicand inputs to the multiplier. When these registers are configured for parallel data inputs, they are driven by regular routing resources. You can use a clock signal, asynchronous clear signal, and a clock enable signal to independently control each set of A and B inputs for each multiplier in the DSP block. You select these control signals from a set of four different clock [3..0], aclr[3..0], and ena[3..0] signals that drive the entire DSP block.

You can also configure the input registers for a shift register application. In this case, the input registers feed the multiplier and drive two dedicated shift output lines:  $\mathtt{shiftoutA}$  and  $\mathtt{shiftoutB}$ . The shift outputs of one multiplier block directly feed the adjacent multiplier block in the same DSP block (or the next DSP block) as shown in Figure 4–32, to form a shift register chain. This chain can terminate in any block, that is, you can create any length of shift register chain up to 224 registers. You can use the input shift registers for FIR filter applications. One set of shift inputs can provide data for a filter, and the other are coefficients that are optionally loaded in serial or parallel. When implementing  $9 \times 9$ - and  $18 \times 18$ -bit multipliers, you do not need to implement external shift registers in LAB LEs. You implement all the filter circuitry within the DSP block and its routing resources, saving LE and general routing resources for general logic. External registers are needed for shift register inputs when using  $36 \times 36$ -bit multipliers.

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D

Figure 4–33. Adder/Output Blocks Note (1)

#### Notes to Figure 4-33:

accum\_sload1 (2)

(1) Adder/output block shown in Figure 4–33 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

Accumulator Feedback

(2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

Figure 4–34. Simple Multiplier Mode

Note to Figure 4-34:

(1) These signals are not registered or registered once to match the data path pipeline.

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 4–35 shows the  $36 \times 36$ -bit multiply mode.

For FIR filters, the DSP block combines the four-multipliers adder mode with the shift register inputs. One set of shift inputs contains the filter data, while the other holds the coefficients loaded in serial or parallel. The input shift register eliminates the need for shift registers external to the DSP block (that is, implemented in LEs). This architecture simplifies filter design since the DSP block implements all of the filter circuitry.

One DSP block can implement an entire 18-bit FIR filter with up to four taps. For FIR filters larger than four taps, DSP blocks can be cascaded with additional adder stages implemented in LEs.

Table 4–15 shows the different number of multipliers possible in each DSP block mode according to size. These modes allow the DSP blocks to implement numerous applications for DSP including FFTs, complex FIR, FIR, and 2D FIR filters, equalizers, IIR, correlators, matrix multiplication and many other functions.

| Table 4–15. Multiplier Size & Configurations per DSP block |                                              |                                            |                                        |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------|--------------------------------------------|----------------------------------------|--|--|--|--|

| DSP Block Mode 9 × 9 18 × 18 36 × 36 (1)                   |                                              |                                            |                                        |  |  |  |  |

| Multiplier                                                 | Eight multipliers with eight product outputs | Four multipliers with four product outputs | One multiplier with one product output |  |  |  |  |

| Multiply-accumulator                                       | Two multiply and accumulate (52 bits)        | Two multiply and accumulate (52 bits)      | _                                      |  |  |  |  |

| Two-multipliers adder                                      | Four sums of two multiplier products each    | Two sums of two multiplier products each   | _                                      |  |  |  |  |

| Four-multipliers adder                                     | Two sums of four multiplier products each    | One sum of four multiplier products each   | -                                      |  |  |  |  |

Note to Table 4–15:

#### **DSP Block Interface**

Stratix GX device DSP block outputs can cascade down within the same DSP block column. Dedicated connections between DSP blocks provide fast connections between the shift register inputs to cascade the shift register chains. You can cascade DSP blocks for  $9 \times 9$ - or  $18 \times 18$ -bit FIR filters larger than four taps, with additional adder stages implemented in LEs. If the DSP block is configured as  $36 \times 36$  bits, the adder, subtractor, or accumulator stages are implemented in LEs. Each DSP block can route the shift register chain out of the block to cascade two full columns of DSP blocks.

The number of supported multiply functions shown is based on signed/signed or unsigned/unsigned implementations.

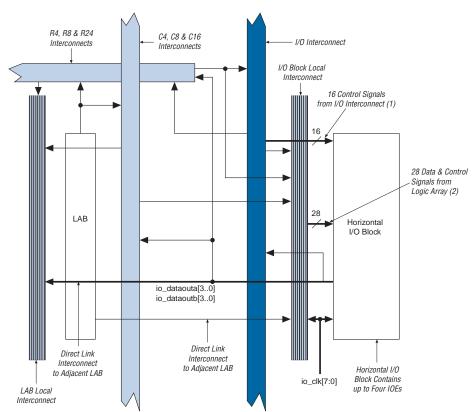

Figure 4-59. Row I/O Block Connection to the Interconnect

#### Notes to Figure 4-59:

- (1) The 16 control signals are composed of four output enables io\_boe[3..0], four clock enables io\_boe[3..0], four clocks io\_clk[3..0], and four clear signals io\_bclr[3..0].

- (2) The 28 data and control signals consist of eight data out lines: four lines each for DDR applications io\_dataouta[3..0] and io\_dataoutb[3..0], four output enables io\_coe[3..0], four input clock enables io\_cce\_in[3..0], four output clock enables io\_cce\_out[3..0], four clocks io\_cclk[3..0], and four clear signals io\_cclr[3..0].

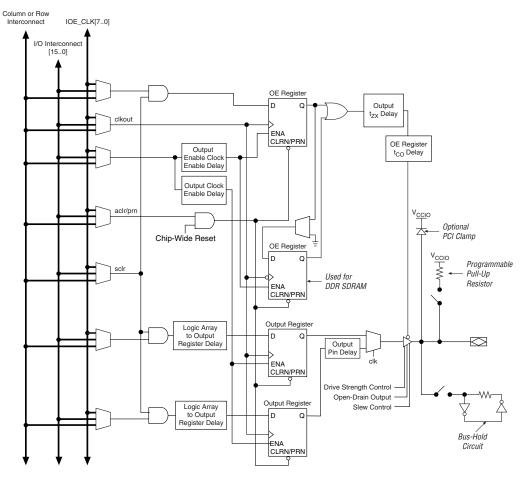

Figure 4–66. Stratix GX IOE in DDR Output I/O Configuration Notes (1), (2)

Notes to Figure 4-66:

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) The tristate is by default active high. It can, however, be designed to be active low.

Table 4–28 shows I/O standard support for each I/O bank.

| Table 4–28. I/O Support by Bank (Part 1 of 2) |                                     |                       |                                                                 |  |  |  |

|-----------------------------------------------|-------------------------------------|-----------------------|-----------------------------------------------------------------|--|--|--|

| I/O Standard                                  | Top & Bottom Banks<br>(3, 4, 7 & 8) | Left Banks<br>(1 & 2) | Enhanced PLL External<br>Clock Output Banks<br>(9, 10, 11 & 12) |  |  |  |

| LVTTL                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| LVCMOS                                        | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 2.5 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 1.8 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 1.5 V                                         | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 3.3-V PCI                                     | ✓                                   |                       | ✓                                                               |  |  |  |

| 3.3-V PCI-X 1.0                               | ✓                                   |                       | ✓                                                               |  |  |  |

| LVPECL                                        |                                     | ✓                     | ✓                                                               |  |  |  |

| 3.3-V PCML                                    |                                     | ✓                     | ✓                                                               |  |  |  |

| LVDS                                          |                                     | ✓                     | ✓                                                               |  |  |  |

| HyperTransport technology                     |                                     | ✓                     | ✓                                                               |  |  |  |

| Differential HSTL (clock inputs)              | ~                                   | ✓                     |                                                                 |  |  |  |

| Differential HSTL (clock outputs)             |                                     |                       | ✓                                                               |  |  |  |

| Differential SSTL (clock outputs)             |                                     |                       | <b>✓</b>                                                        |  |  |  |

| 3.3-V GTL                                     | ✓                                   |                       | ✓                                                               |  |  |  |

| 3.3-V GTL+                                    | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 1.5-V HSTL class I                            | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 1.5-V HSTL class II                           | ✓                                   |                       | ✓                                                               |  |  |  |

| 1.8-V HSTL class I                            | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| 1.8-V HSTL class II                           | ✓                                   |                       | ✓                                                               |  |  |  |

| SSTL-18 class I                               | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| SSTL-18 class II                              | ✓                                   |                       | ✓                                                               |  |  |  |

| SSTL-2 class I                                | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| SSTL-2 class II                               | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| SSTL-3 class I                                | ✓                                   | ✓                     | ✓                                                               |  |  |  |

| Table 4–28. I/O Support by Bank (Part 2 of 2)                                                                        |   |   |   |  |  |  |

|----------------------------------------------------------------------------------------------------------------------|---|---|---|--|--|--|

| I/O Standard Top & Bottom Banks (3, 4, 7 & 8) Left Banks (1 & 2) Enhanced PLL Exte Clock Output Ban (9, 10, 11 & 12) |   |   |   |  |  |  |

| SSTL-3 class II                                                                                                      | ✓ | ✓ | ✓ |  |  |  |

| AGP (1× and 2×)                                                                                                      | ✓ |   | ✓ |  |  |  |

| СТТ                                                                                                                  | ✓ | ✓ | ✓ |  |  |  |

Each I/O bank has its own VCCIO pins. A single device can support 1.5-, 1.8-, 2.5-, and 3.3-V interfaces; each bank can support a different standard independently. Each bank also has dedicated VREF pins to support any one of the voltage-referenced standards (such as SSTL-3) independently.

Each I/O bank can support multiple standards with the same  $V_{\rm CCIO}$  for input and output pins. Each bank can support one voltage-referenced I/O standard. For example, when  $V_{\rm CCIO}$  is 3.3 V, a bank can support LVTTL, LVCMOS, 3.3-V PCI, and SSTL-3 for inputs and outputs.

#### **Differential On-Chip Termination**

Stratix GX devices provide differential on-chip termination (LVDS I/O standard) to reduce reflections and maintain signal integrity. Differential on-chip termination simplifies board design by minimizing the number of external termination resistors required. Termination can be placed inside the package, eliminating small stubs that can still lead to reflections. The internal termination is designed using transistors in the linear region of operation.

Stratix GX devices support internal differential termination with a nominal resistance value of 137.5  $\Omega$  for LVDS input receiver buffers. LVPECL signals require an external termination resistor. Figure 4–70 shows the device with differential termination.

## 5. Configuration & Testing

SGX51005-1.0

## SignalTap Embedded Logic Analyzer

Stratix® GX devices feature the SignalTap® embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

## **Configuration**

The logic, circuitry, and interconnects in the Stratix GX architecture are configured with CMOS SRAM elements. Stratix GX devices are reconfigurable and are 100% tested prior to shipment. As a result, you do not have to generate test vectors for fault coverage purposes, and can instead focus on simulation and design verification. In addition, you do not need to manage inventories of different ASIC designs. Stratix GX devices can be configured on the board for the specific functionality required.

Stratix GX devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix GX devices via a serial data stream. Stratix GX devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix GX device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix GX devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix GX device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

## **Operating Modes**

The Stratix GX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power up,

You can implement the error detection CRC feature with existing circuitry in Stratix GX devices, eliminating the need for external logic. For Stratix GX devices, the CRC is computed by Quartus II and downloaded into the device as a part of the configuration bit stream. The CRC\_ERROR pin reports a soft error when configuration SRAM data is corrupted, triggering device reconfiguration.

#### **Custom-Built Circuitry**

Dedicated circuitry is built into Stratix GX devices to perform error detection automatically. This error detection circuitry constantly checks for errors in the configuration SRAM cells while the device is in user mode. You can monitor one external pin for the error and use it to trigger a reconfiguration cycle. You can select the desired time between checks by adjusting a built-in clock divider.

#### Software Interface

In the Quartus II software version 4.1 and later, you can turn on the automated error detection CRC feature in the **Device & Pin Options** dialog box. This dialog box allows you to enable the feature and set the internal frequency of the CRC between 400 kHz to 100 MHz. This controls the rate that the CRC circuitry verifies the internal configuration SRAM bits in the FPGA device.

For more information on CRC, refer to AN 357: Error Detection Using CRC in Altera FPGA Devices.

## Temperature-Sensing Diode

Stratix GX devices include a diode-connected transistor for use as a temperature sensor in power management. This diode is used with an external digital thermometer device such as a MAX1617A or MAX1619 from MAXIM Integrated Products. These devices steer bias current through the Stratix GX diode, measuring forward voltage and converting this reading to temperature in the form of an 8-bit signed number (7 bits plus sign). The external device's output represents the package temperature of the Stratix GX device and can be used for intelligent power management.

The diode requires two pins (tempdiodep and tempdioden) on the Stratix GX device to connect to the external temperature-sensing device, as shown in Figure 5–4. The temperature-sensing diode is a passive element and therefore can be used before the Stratix GX device is powered.

| Table 6–18       | Table 6–18. PCI-X Specifications (Part 2 of 2) |                             |                            |         |                            |       |  |  |

|------------------|------------------------------------------------|-----------------------------|----------------------------|---------|----------------------------|-------|--|--|

| Symbol           | Parameter                                      | Conditions                  | Minimum                    | Typical | Maximum                    | Units |  |  |

| V <sub>IPU</sub> | Input pull-up voltage                          |                             | 0.7 ×<br>V <sub>CCIO</sub> |         |                            | V     |  |  |

| V <sub>OH</sub>  | High-level output voltage                      | I <sub>OUT</sub> = -500 μA  | 0.9 ×<br>V <sub>CCIO</sub> |         |                            | V     |  |  |

| V <sub>OL</sub>  | Low-level output voltage                       | I <sub>OUT</sub> = 1,500 μA |                            |         | 0.1 ×<br>V <sub>CCIO</sub> | V     |  |  |

| Table 6-19       | Table 6–19. GTL+ I/O Specifications |                             |                        |         |                        |       |  |  |

|------------------|-------------------------------------|-----------------------------|------------------------|---------|------------------------|-------|--|--|

| Symbol           | Parameter                           | Conditions                  | Minimum                | Typical | Maximum                | Units |  |  |

| $V_{TT}$         | Termination voltage                 |                             | 1.35                   | 1.5     | 1.65                   | V     |  |  |

| V <sub>REF</sub> | Reference voltage                   |                             | 0.88                   | 1.0     | 1.12                   | V     |  |  |

| V <sub>IH</sub>  | High-level input voltage            |                             | V <sub>REF</sub> + 0.1 |         |                        | V     |  |  |

| V <sub>IL</sub>  | Low-level input voltage             |                             |                        |         | V <sub>REF</sub> – 0.1 | V     |  |  |

| V <sub>OL</sub>  | Low-level output voltage            | I <sub>OL</sub> = 36 mA (1) |                        |         | 0.65                   | V     |  |  |

| Table 6–20. GTL I/O Specifications |                          |                             |                         |         |                         |       |  |  |  |

|------------------------------------|--------------------------|-----------------------------|-------------------------|---------|-------------------------|-------|--|--|--|

| Symbol                             | Parameter                | Conditions                  | Minimum                 | Typical | Maximum                 | Units |  |  |  |

| $V_{TT}$                           | Termination voltage      |                             | 1.14                    | 1.2     | 1.26                    | V     |  |  |  |

| V <sub>REF</sub>                   | Reference voltage        |                             | 0.74                    | 0.8     | 0.86                    | V     |  |  |  |

| V <sub>IH</sub>                    | High-level input voltage |                             | V <sub>REF</sub> + 0.05 |         |                         | V     |  |  |  |

| V <sub>IL</sub>                    | Low-level input voltage  |                             |                         |         | V <sub>REF</sub> – 0.05 | V     |  |  |  |

| V <sub>OL</sub>                    | Low-level output voltage | I <sub>OL</sub> = 40 mA (1) |                         |         | 0.4                     | V     |  |  |  |

| Table 6–21. SSTL-18 Class I Specifications (Part 1 of 2) |                             |            |                          |           |                         |       |  |  |  |

|----------------------------------------------------------|-----------------------------|------------|--------------------------|-----------|-------------------------|-------|--|--|--|

| Symbol                                                   | Parameter                   | Conditions | Minimum                  | Typical   | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub>                                        | Output supply voltage       |            | 1.65                     | 1.8       | 1.95                    | V     |  |  |  |

| V <sub>REF</sub>                                         | Reference voltage           |            | 0.8                      | 0.9       | 1.0                     | V     |  |  |  |

| V <sub>TT</sub>                                          | Termination voltage         |            | $V_{REF} - 0.04$         | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V     |  |  |  |

| V <sub>IH(DC)</sub>                                      | High-level DC input voltage |            | V <sub>REF</sub> + 0.125 |           |                         | V     |  |  |  |

| Table 6–87. High-Speed I/O Specifications (Part 2 of 4) Notes (1), (2)                             |                              |                |     |      |                |     |      |                |     |      |      |

|----------------------------------------------------------------------------------------------------|------------------------------|----------------|-----|------|----------------|-----|------|----------------|-----|------|------|

| Oh.a.l                                                                                             | Conditions                   | -5 Speed Grade |     |      | -6 Speed Grade |     |      | -7 Speed Grade |     |      |      |

| Symbol                                                                                             |                              | Min            | Тур | Max  | Min            | Тур | Max  | Min            | Тур | Max  | Unit |

| f <sub>HSDR</sub> Device                                                                           | J = 10                       | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| operation<br>(LVDS,                                                                                | J = 8                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| LVPECL,                                                                                            | J = 7                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| HyperTransport                                                                                     | J = 4                        | 300            |     | 840  | 300            |     | 840  | 300            |     | 840  | Mbps |

| technology)                                                                                        | J = 2                        | 100            |     | 624  | 100            |     | 624  | 100            |     | 462  | Mbps |

|                                                                                                    | J = 1 (LVDS and LVPECL only) | 100            |     | 462  | 100            |     | 462  | 100            |     | 462  | Mbps |

| f <sub>HSDRDPA</sub> (LVDS,                                                                        | J=10                         | 300            |     | 1000 | 300            |     | 840  | 300            |     | 840  | Mbps |

| LVPECL)                                                                                            | J=8                          | 300            |     | 1000 | 300            |     | 840  | 300            |     | 840  | Mbps |

| f <sub>HSCLK</sub> (Clock<br>frequency)<br>(PCML)<br>f <sub>HSCLK</sub> =<br>f <sub>HSDR</sub> / W | W = 1 to 30                  | 10             |     | 400  | 10             |     | 400  | 10             |     | 311  | MHz  |

| f <sub>HSDR</sub> Device                                                                           | <i>J</i> = 10                | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

| operation<br>(PCML)                                                                                | J = 8                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

| (I OWIE)                                                                                           | J = 7                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

|                                                                                                    | J = 4                        | 300            |     | 400  | 300            |     | 400  | 300            |     | 311  | Mbps |

|                                                                                                    | J = 2                        | 100            |     | 400  | 100            |     | 400  | 100            |     | 300  | Mbps |

|                                                                                                    | J = 1                        | 100            |     | 250  | 100            |     | 250  | 100            |     | 200  | Mbps |

| DPA Run<br>Length                                                                                  |                              |                |     | 6400 |                |     | 6400 |                |     | 6400 | UI   |

| DPA Jitter<br>Tolerance <sub>(p-p)</sub>                                                           | all data rates               |                |     | 0.44 |                |     | 0.44 |                |     | 0.44 | UI   |

| DPA Minimum<br>Eye opening<br>(p-p)                                                                |                              | 0.56           |     |      | 0.56           |     |      | 0.56           |     |      | UI   |

| DPA Receiver<br>Latency                                                                            |                              | 5              |     | 9    | 5              |     | 9    | 5              |     | 9    | (3)  |

| Table 6–89. Enhanced PLL Specifications for -6 Speed Grades (Part 2 of 2) |                                                                                                                   |     |     |                                                            |              |  |  |

|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|

| Symbol                                                                    | Parameter                                                                                                         |     | Тур | Max                                                        | Unit         |  |  |

| f <sub>OUT</sub>                                                          | Output frequency for internal global or regional clock                                                            | 0.3 |     | 450                                                        | MHz          |  |  |

| f <sub>OUT_EXT</sub>                                                      | Output frequency for external clock (2)                                                                           | 0.3 |     | 500                                                        | MHz          |  |  |

| t <sub>OUTDUTY</sub>                                                      | Duty cycle for external clock output (when set to 50%)                                                            | 45  |     | 55                                                         | %            |  |  |

| t <sub>JITTER</sub>                                                       | Period jitter for external clock output (5)                                                                       |     |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |  |  |

| t <sub>CONFIG5,6</sub>                                                    | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>CONFIG11,12</sub>                                                  | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |

| t <sub>SCANCLK</sub>                                                      | scanclk frequency (4)                                                                                             |     |     | 22                                                         | MHz          |  |  |

| t <sub>DLOCK</sub>                                                        | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) (10) | (8) |     | 100                                                        | μs           |  |  |

| t <sub>LOCK</sub>                                                         | Time required to lock from end of device configuration (10)                                                       | 10  |     | 400                                                        | μѕ           |  |  |

| f <sub>VCO</sub>                                                          | PLL internal VCO operating range                                                                                  | 300 |     | 800 (7)                                                    | MHz          |  |  |

| t <sub>LSKEW</sub>                                                        | Clock skew between two external clock outputs driven by the same counter                                          |     | ±50 |                                                            | ps           |  |  |

| t <sub>SKEW</sub>                                                         | Clock skew between two external clock outputs driven by the different counters with the same settings             |     | ±75 |                                                            | ps           |  |  |

| f <sub>SS</sub>                                                           | Spread spectrum modulation frequency                                                                              | 30  |     | 150                                                        | kHz          |  |  |

| % spread                                                                  | Percentage spread for spread spectrum frequency (9)                                                               | 0.4 | 0.5 | 0.6                                                        | %            |  |  |

| t <sub>ARESET</sub>                                                       | Minimum pulse width on areset signal                                                                              | 10  |     |                                                            | ns           |  |  |

| Table 6–90. Enhanced PLL Specifications for -7 Speed Grade (Part 1 of 3) |                                          |       |     |          |      |  |  |  |

|--------------------------------------------------------------------------|------------------------------------------|-------|-----|----------|------|--|--|--|

| Symbol                                                                   | Parameter                                | Min   | Тур | Max      | Unit |  |  |  |

| f <sub>IN</sub>                                                          | Input clock frequency                    | 3 (1) |     | 565      | MHz  |  |  |  |

| f <sub>INDUTY</sub>                                                      | Input clock duty cycle                   | 40    |     | 60       | %    |  |  |  |

| f <sub>EINDUTY</sub>                                                     | External feedback clock input duty cycle | 40    |     | 60       | %    |  |  |  |

| t <sub>INJITTER</sub>                                                    | Input clock period jitter                |       |     | ±200 (2) | ps   |  |  |  |

| t <sub>EINJITTER</sub>                                                   | External feedback clock period jitter    |       |     | ±200 (2) | ps   |  |  |  |