Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

## **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 2566                                                         |

| Number of Logic Elements/Cells | 25660                                                        |

| Total RAM Bits                 | 1944576                                                      |

| Number of I/O                  | 607                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1020-BBGA                                                    |

| Supplier Device Package        | 1020-FBGA (33x33)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25ff1020c5n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2. Stratix GX Transceivers

SGX51002-1.1

# Transceiver Blocks

Stratix® GX devices incorporate dedicated embedded circuitry on the right side of the device, which contains up to 20 high-speed 3.1875-Gbps serial transceiver channels. Each Stratix GX transceiver block contains four full-duplex channels and supporting logic to transmit and receive high-speed serial data streams. The transceiver block uses the channels to deliver bidirectional point-to-point data transmissions with up to 3.1875 Gbps of data transition per channel.

There are up to 20 transceiver channels available on a single Stratix GX device. Table 2–1 shows the number of transceiver channels available on each Stratix GX device.

| Table 2–1. Stratix GX Transceiver Channels |                                |  |  |  |  |  |

|--------------------------------------------|--------------------------------|--|--|--|--|--|

| Device                                     | Number of Transceiver Channels |  |  |  |  |  |

| EP1SGX10C                                  | 4                              |  |  |  |  |  |

| EP1SGX10D                                  | 8                              |  |  |  |  |  |

| EP1SGX25C                                  | 4                              |  |  |  |  |  |

| EP1SGX25D                                  | 8                              |  |  |  |  |  |

| EP1SGX25F                                  | 16                             |  |  |  |  |  |

| EP1SGX40D                                  | 8                              |  |  |  |  |  |

| EP1SGX40G                                  | 20                             |  |  |  |  |  |

Figure 2–1 shows the elements of the transceiver block, including the four channels, supporting logic, and I/O buffers. Each transceiver channel consists of a receiver and transmitter. The supporting logic contains a transmitter PLL to generate a high-speed clock used by the four transmitters. The receiver PLL within each transceiver channel generates the receiver reference clocks. The supporting logic also contains state machines to manage rate matching for XAUI and GIGE applications, in addition to channel bonding for XAUI applications.

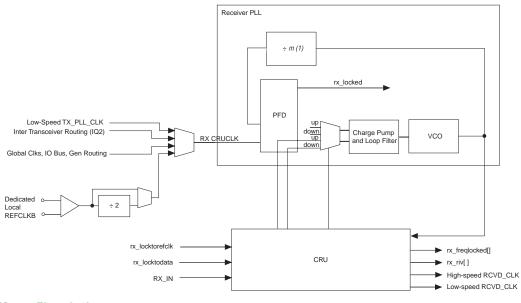

Figure 2-13. Receiver PLL & CRU Circuit

*Note to Figure 2–13:* (1) m = 8, 10 16, or 20.

The receiver PLLs and CRUs are capable of supporting up to 3.1875 Gbps. The input clock frequency for –5 and –6 speed grade devices is limited to 650 MHz if you use the REFCLKB pin or 325 MHz if you use the other clock routing resources. The maximum input clock frequency for –7 speed grade devices is 312.5 MHz if you use the REFCLKB pin or 156.25 MHz with the other clock routing resources. An optional RX\_LOCKED port (active low signal) is available to indicate whether the PLL is locked to the reference clock. The receiver PLL has a programmable loop bandwidth, which can be set to low, medium, or high. The loop bandwidth parameter can be statically set by the Quartus II software.

Table 2–5 lists the adjustable parameters of the receiver PLL and CRU. All the parameters listed are statically programmable in the Quartus II software.

| Table 2–5. Receiver PLL & CRU Adjustable Parameters (Part 1 of 2) |                         |  |  |  |  |  |

|-------------------------------------------------------------------|-------------------------|--|--|--|--|--|

| Parameter                                                         | Specifications          |  |  |  |  |  |

| Input reference frequency range                                   | 25 MHz to 650 MHz       |  |  |  |  |  |

| Data rate support                                                 | 500 Mbps to 3.1875 Gbps |  |  |  |  |  |

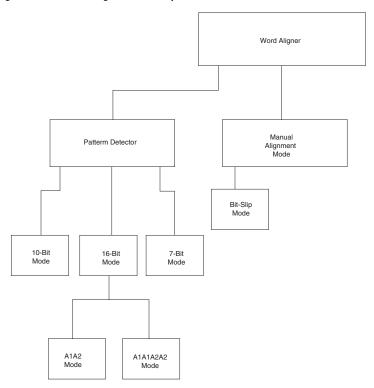

Figure 2-15. Word Aligner in Bit-Slip Mode

In the bit-slip mode, the byte boundary can be modified by a barrel shifter to slip the byte boundary one bit at a time via a user-controlled bit-slip port. The bit-slip mode supports both 8-bit and 10-bit data paths operating in a single or double-width mode.

The pattern detector is active in the bit-slip mode, and it detects the user-defined pattern that is specified in the MegaWizard® Plug-In Manager.

The bit-slip mode is available only in Custom mode and SONET mode.

Figure 2–16 shows the word aligner in 16-bit mode.

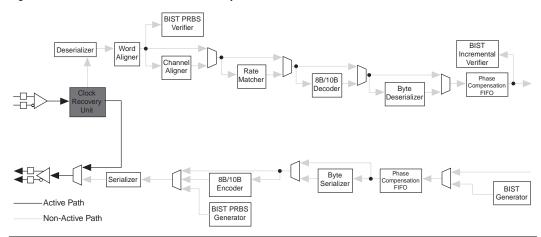

Figure 2-23. Data Path in Reverse Serial Loopback Mode

## **BIST (Built-In Self Test)**

The Stratix GX transceiver has built-in self test modes to aid in debug and testing. The BIST modes are set in the Stratix GX MegaWizard Plug-In Manager in the Quartus II software. Only one BIST mode can be set for any single instance of the transceiver block. The BIST mode applies to all channels used in a transceiver.

The following is a list of the available BIST modes:

- PRBS generator and verifier

- Incremental mode generator and verifier

- High-frequency generator

- Low-frequency generator

- Mixed-frequency generator

Figures 2–24 and 2–25 are diagrams of the BIST PRBS data path and the BIST incremental data path, respectively.

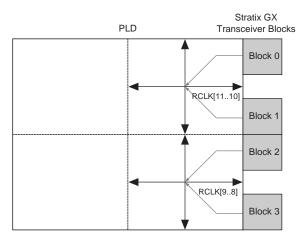

The receiver PLL can also drive the fast regional, regional clocks, and local routing adjacent to the associated transceiver block. Figures 2–28 through 2–31 show which fast regional and regional clock resource can be used by the recovered clock.

In the EP1SGX25 device, the receiver PLL recovered clocks from transceiver blocks 0 and 1 drive RCLK [1..0] while transceiver blocks 2 and 3 drive RCLK [7..6]. The regional clocks feed logic in their associated regions.

Figure 2–28. EP1SGX25 Receiver PLL Recovered Clock to Regional Clock Connection

In addition, the receiver PLL's recovered clocks can drive fast regional lines (FCLK) as shown Figure 2–29. The fast regional clocks can feed logic in their associated regions.

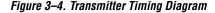

The logic array sends parallel data to the SERDES transmitter circuit when the TXLOADEN signal is asserted. This signal is generated by the high-speed counter circuitry of the logic array low-frequency clock's rising edge. The data is then transferred from the parallel register into the serial shift register by the TXLOADEN signal on the third rising edge of the high-frequency clock.

Figure 3–3 shows the block diagram of a single SERDES transmitter channel and Figure 3–4 shows the timing relationship between the data and clocks in Stratix GX devices in  $\times 10$  mode. W is the low-frequency multiplier and J is the data parallelization division factor.

Transmitter Circuit Parallel Serial Register Register -⊠ TXOUT+ PD9 PD9 PD8 -⊠ TXOUT-PD8 PD7 PD7 PD6 PD6 PD5 PD5 PD4 PD4 PD3 PD3 Stratix GX PD2 PD2 Logic Array PD1 PD1 PD0 PD0  $\times W$ Fast **TXLOADEN PLL**

Figure 3-3. Stratix GX High-Speed Interface Serialized in ×10 Mode

The DPA data-realignment circuitry allows further realignment beyond what the *J* multiplication factor allows. You can set the *J* multiplication factor to be 8 or 10. However, because data must be continuously clocked in on each low-speed clock cycle, the upcoming bit to be realigned and previous n-1 bits of data are selected each time the data realignment logic's counter passes n-1. At this point the data is selected entirely from bit-slip register 3 (see Figure 3–11) as the counter is reset to 0. The logic array receives a new valid byte of data on the next divided low speed clock cycle. Figure 3–11 shows the data realignment logic output selection from data in the data realignment register 2 and data realignment register 3 based on its current counter value upon continuous request of data slipping from the logic array.

Bit Slip Bit Slin Bit Slin Bit Slin Bit Slip Bit Slin Bit Slip Bit Slin Bit Slip Bit Slip Register 2 Register 3 D19 D9 D29 D19 D99 D89 D119 D99 D119 D109 D18 D8 D28 D18 D118 D118 D108 D18 D98 D98 D97 D17 D7 D27 D17 D97 D87 D117 D117 D107 D16 D6 D26 D16 D96 D86 D116 D96 D116 D106 One bit Seven more One more One more slipped bits slipped bit slipped bit slipped D15 D5 D25 D15 D95 D85 D115 D95 D115 D125 D14 D4 D24 D14 D94 D84 D114 D94 D114 D124 D13 D3 D23 D83 D113 D113 D13 D93 D93 D12 D2 D22 D12 D92 D82 D112 D92 D112 D102 D111 D11 D21 D11 D91 D81 D91 D111 D10 D0 D20 D10 D90 D80 D110 D90 D110 D100 Zero bits slipped One bit slipped. Eight bits slipped. Nine bits slipped. 10 bits slipped. Counter = 0 Counter = 1 Counter = 8 Counter = 9 Counter = 0 D10 is the upcoming D21 is the upcoming D98 is the upcoming D119 is the upcoming Real data will resume bit to be slipped. bit to be slipped. on the next byte.

Figure 3–11. DPA Data Realigner

Use the rx\_channel\_data\_align signal within the device to activate the data realigner. You can use internal logic or an external pin to control the rx channel data align signal. To ensure the rising edge of the rx channel data align signal is latched into the control logic, the rx channel data align signal should stay high for at least two lowfrequency clock cycles.

bit to be slipped.

bit to be slipped.

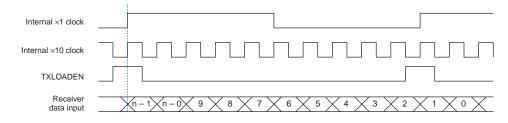

its own fan-out LUT. This provides another mechanism for improved fitting. The LE can also drive out registered and unregistered versions of the LUT output.

## **LUT Chain & Register Chain**

In addition to the three general routing outputs, the LEs within an LAB have LUT chain and register chain outputs. LUT chain connections allow LUTs within the same LAB to cascade together for wide input functions. Register chain outputs allow registers within the same LAB to cascade together. The register chain output allows an LAB to use LUTs for a single combinatorial function and the registers to be used for an unrelated shift register implementation. These resources speed up connections between LABs while saving local interconnect resources. See "MultiTrack Interconnect" on page 4–11 for more information on LUT chain and register chain connections.

## addnsub Signal

The LE's dynamic adder/subtractor feature saves logic resources by using one set of LEs to implement both an adder and a subtractor. This feature is controlled by the LAB-wide control signal addnsub. The addnsub signal sets the LAB to perform either A+B or A-B. The LUT computes addition, and subtraction is computed by adding the two's complement of the intended subtractor. The LAB-wide signal converts to two's complement by inverting the B bits within the LAB and setting carry-in = 1 to add one to the least significant bit (LSB). The LSB of an adder/subtractor must be placed in the first LE of the LAB, where the LAB-wide addnsub signal automatically sets the carry-in to 1. The Quartus II Compiler automatically places and uses the adder/subtractor feature when using adder/subtractor parameterized functions.

## **LE Operating Modes**

The Stratix GX LE can operate in one of the following modes:

- Normal mode

- Dynamic arithmetic mode

Each mode uses LE resources differently. In each mode, eight available inputs to the LE—the four data inputs from the LAB local interconnect; carry-in0 and carry-in1 from the previous LE; the LAB carry-in from the previous carry-chain LAB; and the register chain connection—are directed to different destinations to implement the desired logic function. LAB-wide signals provide clock, asynchronous clear, asynchronous preset load, synchronous clear, synchronous load, and

Figure 4–6. LE in Dynamic Arithmetic Mode

*Note to Figure 4–6:*

(1) The addnsub signal is tied to the carry input for the first LE of a carry chain only.

## Carry-Select Chain

The carry-select chain provides a very fast carry-select function between LEs in arithmetic mode. The carry-select chain uses the redundant carry calculation to increase the speed of carry functions. The LE is configured to calculate outputs for a possible carry-in of 1 and carry-in of 0 in parallel. The carry-in0 and carry-in1 signals from a lower-order bit feed forward into the higher-order bit via the parallel carry chain and feed into both the LUT and the next portion of the carry chain. Carry-select chains can begin in any LE within an LAB.

The speed advantage of the carry-select chain is in the parallel pre-computation of carry chains. Because the LAB carry-in selects the precomputed carry chain, not every LE is in the critical path. Only the propagation delay between LAB carry-in generation (LE 5 and LE 10) are now part of the critical path. This feature allows the Stratix GX architecture to implement high-speed counters, adders, multipliers, parity functions, and comparators of arbitrary width.

Figure 4–7 shows the carry-select circuitry in an LAB for a 10-bit full adder. One portion of the LUT generates the sum of two bits using the input signals and the appropriate carry-in bit; the sum is routed to the output of the LE. The register can be bypassed for simple adders or used

M4K RAM blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 4–6 summarizes the byte selection.

| Table 4–6. Byte Enable for M4K Blocks Notes (1), (2) |            |            |  |  |  |  |  |  |

|------------------------------------------------------|------------|------------|--|--|--|--|--|--|

| byteena[30]                                          | datain ×18 | datain ×36 |  |  |  |  |  |  |

| [0] = 1                                              | [80]       | [80]       |  |  |  |  |  |  |

| [1] = 1                                              | [179]      | [179]      |  |  |  |  |  |  |

| [2] = 1                                              | _          | [2618]     |  |  |  |  |  |  |

| [3] = 1                                              | _          | [3527]     |  |  |  |  |  |  |

### Notes to Table 4-6:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, that is, in ×16 and ×32 modes.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The eight labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 4–16.

The R4, R8, C4, C8, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 4–17 shows the M4K RAM block to logic array interface.

## Pipeline/Post Multiply Register

The output of  $9 \times 9$ - or  $18 \times 18$ -bit multipliers can optionally feed a register to pipeline multiply-accumulate and multiply-add/subtract functions. For  $36 \times 36$ -bit multipliers, this register pipelines the multiplier function.

## **Adder/Output Blocks**

The result of the multiplier sub-blocks are sent to the adder/output block which consist of an adder/subtractor/accumulator unit, summation unit, output select multiplexer, and output registers. The results are used to configure the adder/output block as a pure output, accumulator, a simple two-multiplier adder, four-multiplier adder, or final stage of the 36-bit multiplier. You can configure the adder/output block to use output registers in any mode, and must use output registers for the accumulator. The system cannot use adder/output blocks independently of the multiplier. Figure 4–33 shows the adder and output stages.

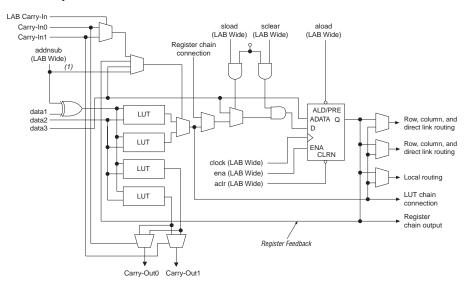

PLL5\_OUT[3..0] CLK14 (1) PLL5\_FB CLK15(2) CLK12 (1) CLK13 (2) E[0..3] PLL 5 PLL 11 (4) L0 L1 G0 G1 G2 G3 G0 G1 G2 G3 L0 L1 --> PLL11\_OUT ➤ RCLK10 RCLK11 Regional 5 RCLK2 ◀ Clocks RCLK3 ◀ ► G12 ► G13 ► G14 ► G15 Global Clocks ► G4 G5 → G6 ▶ G7 RCLK6 Regional ) Clocks RCLK7 ◀ ► RCLK12 ► RCLK13 L0 L1 G0 G1 G2 G3 G0 G1 G2 G3 L0 L1 PLL 6 PLL 12 (4) PLL6\_OUT[3..0] CLK6 (1) PLL6\_FB CLK7 (2) CLK4 (1) CLK5(2)

Figure 4–50. Global & Regional Clock Connections From Top Clock Pins & Enhanced PLL Outputs Note (1)

*Note to Figure 4–50:*

(1) PLLs 5, 6, 11, and 12 are enhanced PLLs.

pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

Table 4–20 shows the I/O standards supported by fast PLL input pins.

| Table 4–20. Fast PLL Port Input Pin I/O Standards |          |           |  |  |  |  |  |  |

|---------------------------------------------------|----------|-----------|--|--|--|--|--|--|

| I/O Chandand                                      | I        | nput      |  |  |  |  |  |  |

| I/O Standard                                      | INCLK    | PLLENABLE |  |  |  |  |  |  |

| LVTTL                                             | ✓        | ✓         |  |  |  |  |  |  |

| LVCMOS                                            | ✓        | ✓         |  |  |  |  |  |  |

| 2.5 V                                             | ✓        |           |  |  |  |  |  |  |

| 1.8 V                                             | ✓        |           |  |  |  |  |  |  |

| 1.5 V                                             | ✓        |           |  |  |  |  |  |  |

| 3.3-V PCI                                         |          |           |  |  |  |  |  |  |

| 3.3-V PCI-X                                       |          |           |  |  |  |  |  |  |

| LVPECL                                            | ✓        |           |  |  |  |  |  |  |

| 3.3-V PCML                                        | ✓        |           |  |  |  |  |  |  |

| LVDS                                              | ✓        |           |  |  |  |  |  |  |

| HyperTransport technology                         | ✓        |           |  |  |  |  |  |  |

| Differential HSTL                                 | ✓        |           |  |  |  |  |  |  |

| Differential SSTL                                 |          |           |  |  |  |  |  |  |

| 3.3-V GTL                                         | ✓        |           |  |  |  |  |  |  |

| 3.3-V GTL+                                        | ✓        |           |  |  |  |  |  |  |

| 1.5V HSTL class I                                 | ✓        |           |  |  |  |  |  |  |

| 1.5V HSTL class II                                | ✓        |           |  |  |  |  |  |  |

| SSTL-18 class I                                   | ✓        |           |  |  |  |  |  |  |

| SSTL-18 class II                                  | ✓        |           |  |  |  |  |  |  |

| SSTL-2 class I                                    | ✓        |           |  |  |  |  |  |  |

| SSTL-2 class II                                   | ✓        |           |  |  |  |  |  |  |

| SSTL-3 class I                                    | ✓        |           |  |  |  |  |  |  |

| SSTL-3 class II                                   | ✓        |           |  |  |  |  |  |  |

| AGP (1× and 2×)                                   | ✓        |           |  |  |  |  |  |  |

| CTT                                               | <b>✓</b> |           |  |  |  |  |  |  |

## Phase Shifting

Stratix GX device fast PLLs have advanced clock shift capability that enables programmable phase shifts. You can enter a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. You can perform phase shifting in time units with a resolution range of 150 to 400 ps. This resolution is a function of the VCO period.

## Control Signals

The fast PLL has the same lock output, pllenable input, and are set input control signals as the enhanced PLL.

For more information on high-speed differential I/O support, see the *High-Speed Source-Synchronous Differential I/O Interfaces in Stratix GX Devices* chapter of the *Stratix GX Device Handbook*, *Volume 2*.

## I/O Structure

IOEs provide many features, including:

- Dedicated differential and single-ended I/O buffers

- 3.3-V, 64-bit, 66-MHz PCI compliance

- 3.3-V, 64-bit, 133-MHz PCI-X 1.0 compliance

- Joint Test Action Group (JTAG) boundary-scan test (BST) support

- Differential on-chip termination for LVDS I/O standard

- Programmable pull-up during configuration

- Output drive strength control

- Slew-rate control

- Tri-state buffers

- Bus-hold circuitry

- Programmable pull-up resistors

- Programmable input and output delays

- Open-drain outputs

- DQ and DQS I/O pins

- Double-data rate (DDR) Registers

The IOE in Stratix GX devices contains a bidirectional I/O buffer, six registers, and a latch for a complete embedded bidirectional single data rate or DDR transfer. Figure 4–58 shows the Stratix GX IOE structure. The IOE contains two input registers (plus a latch), two output registers, and two output enable registers. The design can use both input registers and the latch to capture DDR input and both output registers to drive DDR outputs. Additionally, the design can use the output enable (OE) register for fast clock-to-output enable timing. The negative edge-clocked OE register is used for DDR SDRAM interfacing. The Quartus II software automatically duplicates a single OE register that controls multiple output or bidirectional pins.

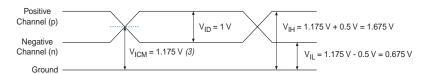

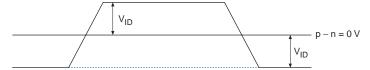

Figure 6-2. Receiver Input Waveform Example with Values

Single-Ended Waveform: What is Applied to the Pin (2)

Differential Waveform: As Seen by the Buffer

or by Subtraction on an Oscilloscope

## *Notes to Figure 6–2:*

- (1) The values in this figure are for example only.

- (2) These values must meet the voltages specified in the section "Operating Conditions" on page 6–1.

- (3) If internal termination is used, the common mode is generated after the pins.

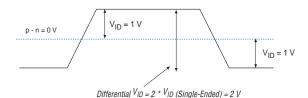

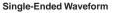

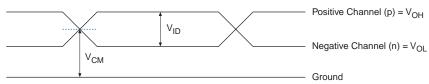

Figure 6-3. Transmitter Output Waveforms for Differential I/O Standards

## **Differential Waveform**

## (V<sub>ID</sub> (Differential) = 2 x V<sub>ID</sub> (single-ended))

| Table 6–35. Stratix GX Device Performance (Part 2 of 3) Notes (1), (2) |                                      |     |                               |               |                      |                      |                      |       |

|------------------------------------------------------------------------|--------------------------------------|-----|-------------------------------|---------------|----------------------|----------------------|----------------------|-------|

|                                                                        |                                      | F   | Resources L                   | Jsed          | Performance          |                      |                      |       |

|                                                                        | Applications                         | LEs | TriMatrix<br>Memory<br>Blocks | DSP<br>Blocks | -5<br>Speed<br>Grade | -6<br>Speed<br>Grade | -7<br>Speed<br>Grade | Units |

| TriMatrix memory                                                       | Simple dual-port RAM 32 × 18 bit     | 0   | 1                             | 0             | 317.76               | 277.62               | 241.48               | MHz   |

| M512 block                                                             | FIFO 32 × 18 bit                     | 30  | 1                             | 0             | 319.18               | 278.86               | 242.54               | MHz   |

| TriMatrix memory                                                       | Simple dual-port RAM 128 × 36 bit    | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |

| M4K block                                                              | True dual-port RAM 128 × 18 bit      | 0   | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |

|                                                                        | FIFO 128 × 36 bit                    | 34  | 1                             | 0             | 290.86               | 255.55               | 222.27               | MHz   |

| TriMatrix memory                                                       | Single port<br>RAM 4K × 144 bit      | 1   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |

| M-RAM<br>block                                                         | Simple dual-port<br>RAM 4K × 144 bit | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | MHz   |

|                                                                        | True dual-port<br>RAM 4K × 144 bit   | 0   | 1                             | 0             | 255.95               | 233.06               | 194.06               | MHz   |

|                                                                        | Single port<br>RAM 8K × 72 bit       | 0   | 1                             | 0             | 278.94               | 243.19               | 211.59               | MHz   |

|                                                                        | Simple dual-port<br>RAM 8K × 72 bit  | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |

|                                                                        | True dual-port<br>RAM 8K × 72 bit    | 0   | 1                             | 0             | 255.95               | 223.06               | 194.06               | MHz   |

|                                                                        | Single port<br>RAM 16K × 36 bit      | 0   | 1                             | 0             | 280.66               | 254.32               | 221.28               | MHz   |

|                                                                        | Simple dual-port<br>RAM 16K × 36 bit | 0   | 1                             | 0             | 269.83               | 237.69               | 206.82               | MHz   |

| Oh a l                                      | Conditions                                        |                                                                  | -5 Speed Grade                 |       |     | -6 Speed Grade |       |     | -7 Speed Grade |       |     | 1114 |     |

|---------------------------------------------|---------------------------------------------------|------------------------------------------------------------------|--------------------------------|-------|-----|----------------|-------|-----|----------------|-------|-----|------|-----|

| Symbol                                      |                                                   |                                                                  | Min                            | Тур   | Max | Min            | Тур   | Max | Min            | Тур   | Max | Unit |     |

| DPA Lock Time                               | Standard                                          | Train ing Patt ern                                               | Trans<br>ition<br>Den-<br>sity |       |     |                |       |     |                |       |     |      |     |

|                                             | SPI-4,<br>CSIX                                    | 0000<br>0000<br>0011<br>1111<br>1111                             | 10%                            | 256   |     |                | 256   |     |                | 256   |     |      | (4) |

|                                             | Rapid IO                                          | 0000<br>1111                                                     | 25%                            | 256   |     |                | 256   |     |                | 256   |     |      | (4) |

|                                             |                                                   | 1001<br>0000                                                     | 50%                            | 256   |     |                | 256   |     |                | 256   |     |      | (4) |

|                                             | Misc                                              | 1010<br>1010                                                     | 100<br>%                       | 256   |     |                | 256   |     |                | 256   |     |      | (4) |

|                                             |                                                   | 0101<br>0101                                                     |                                | 256   |     |                | 256   |     |                | 256   |     |      | (4) |

| TCCS                                        | All                                               |                                                                  | •                              |       |     | 200            |       |     | 200            |       |     | 300  | ps  |

| SW                                          | PCML ( <i>J</i> = 4, 7, 8, 10)                    |                                                                  |                                | 750   |     |                | 750   |     |                | 800   |     |      | ps  |

|                                             | PCML ( <i>J</i> = 2)                              |                                                                  |                                | 900   |     |                | 900   |     |                | 1,200 |     |      | ps  |

|                                             | PCML (J                                           | = 1)                                                             |                                | 1,500 |     |                | 1,500 |     |                | 1,700 |     |      | ps  |

|                                             | LVDS and $(J=1)$                                  | LVPE                                                             | CL                             | 500   |     |                | 500   |     |                | 550   |     |      | ps  |

|                                             | LVDS, LVI<br>HyperTrar<br>technolog<br>through 10 | $\begin{array}{c} \text{nsport} \\ \text{y} \ (J=2) \end{array}$ | 2                              | 440   |     |                | 440   |     |                | 500   |     |      | ps  |

| Input jitter<br>tolerance<br>(peak-to-peak) | All                                               |                                                                  |                                |       |     | 250            |       |     | 250            |       |     | 250  | ps  |

| Output jitter (peak-to-peak)                | All                                               |                                                                  |                                |       |     | 160            |       |     | 160            |       |     | 200  | ps  |

| Output t <sub>RISE</sub>                    | LVDS                                              |                                                                  |                                | 80    | 110 | 120            | 80    | 110 | 120            | 80    | 110 | 120  | ps  |

|                                             | HyperTrar<br>technolog                            | •                                                                |                                | 110   | 170 | 200            | 110   | 170 | 200            | 120   | 170 | 200  | ps  |

|                                             | LVPECL                                            |                                                                  |                                | 90    | 130 | 150            | 90    | 130 | 150            | 100   | 135 | 150  | ps  |

|                                             | PCML                                              |                                                                  |                                | 80    | 110 | 135            | 80    | 110 | 135            | 80    | 110 | 135  | ps  |

| Table 6-88               | Table 6–88. Enhanced PLL Specifications for -5 Speed Grades (Part 2 of 2)                                    |     |     |                                                            |              |  |  |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------|-----|-----|------------------------------------------------------------|--------------|--|--|--|--|

| Symbol                   | Parameter                                                                                                    | Min | Тур | Max                                                        | Unit         |  |  |  |  |

| toutduty                 | Duty cycle for external clock output (when set to 50%)                                                       | 45  |     | 55                                                         | %            |  |  |  |  |

| t <sub>JITTER</sub>      | Period jitter for external clock output (5)                                                                  |     |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |  |  |  |  |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                |     |     | 289/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                              |     |     | 193/f <sub>SCANCLK</sub>                                   |              |  |  |  |  |

| t <sub>SCANCLK</sub>     | scanclk frequency (4)                                                                                        |     |     | 22                                                         | MHz          |  |  |  |  |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) |     |     | 100                                                        | μs           |  |  |  |  |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration                                                       | 10  |     | 400                                                        | μs           |  |  |  |  |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                             | 300 |     | 800 (7)                                                    | MHz          |  |  |  |  |

| t <sub>LSKEW</sub>       | Clock skew between two external clock outputs driven by the same counter                                     |     | ±50 |                                                            | ps           |  |  |  |  |

| t <sub>SKEW</sub>        | Clock skew between two external clock outputs driven by the different counters with the same settings        |     | ±75 |                                                            | ps           |  |  |  |  |

| f <sub>SS</sub>          | Spread spectrum modulation frequency                                                                         | 30  |     | 150                                                        | kHz          |  |  |  |  |

| % spread                 | Percentage spread for spread spectrum frequency (9)                                                          | 0.4 | 0.5 | 0.6                                                        | %            |  |  |  |  |

| t <sub>ARESET</sub>      | Minimum pulse width on areset signal                                                                         | 10  |     |                                                            | ns           |  |  |  |  |

| Table 6-89             | . Enhanced PLL Specifications for -6 Sp       | ades  | (Part 1 of 2) |          |      |

|------------------------|-----------------------------------------------|-------|---------------|----------|------|

| Symbol                 | Parameter                                     | Min   | Тур           | Max      | Unit |

| f <sub>IN</sub>        | Input clock frequency                         | 3 (1) |               | 650      | MHz  |

| f <sub>INDUTY</sub>    | Input clock duty cycle                        | 40    |               | 60       | %    |

| f <sub>EINDUTY</sub>   | External feedback clock input duty cycle      | 40    |               | 60       | %    |

| t <sub>INJITTER</sub>  | Input clock period jitter                     |       |               | ±200 (2) | ps   |

| t <sub>EINJITTER</sub> | External feedback clock period jitter         |       |               | ±200 (2) | ps   |

| t <sub>FCOMP</sub>     | External feedback clock compensation time (3) |       |               | 6        | ns   |

| Table 6-89               | . Enhanced PLL Specifications for -6 Spe                                                                          | (Part 2 of 2) |     |                                                            |              |

|--------------------------|-------------------------------------------------------------------------------------------------------------------|---------------|-----|------------------------------------------------------------|--------------|

| Symbol                   | Parameter                                                                                                         | Min           | Тур | Max                                                        | Unit         |

| f <sub>OUT</sub>         | Output frequency for internal global or regional clock                                                            | 0.3           |     | 450                                                        | MHz          |

| f <sub>OUT_EXT</sub>     | Output frequency for external clock (2)                                                                           | 0.3           |     | 500                                                        | MHz          |

| t <sub>OUTDUTY</sub>     | Duty cycle for external clock output (when set to 50%)                                                            | 45            |     | 55                                                         | %            |

| t <sub>JITTER</sub>      | Period jitter for external clock output (5)                                                                       |               |     | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUI |

| t <sub>CONFIG5,6</sub>   | Time required to reconfigure the scan chains for PLLs 5 and 6                                                     |               |     | 289/f <sub>SCANCLK</sub>                                   |              |

| t <sub>CONFIG11,12</sub> | Time required to reconfigure the scan chains for PLLs 11 and 12                                                   |               |     | 193/f <sub>SCANCLK</sub>                                   |              |

| t <sub>SCANCLK</sub>     | scanclk frequency (4)                                                                                             |               |     | 22                                                         | MHz          |

| t <sub>DLOCK</sub>       | Time required to lock dynamically (after switchover or reconfiguring any non-post-scale counters/delays) (6) (10) | (8)           |     | 100                                                        | μs           |

| t <sub>LOCK</sub>        | Time required to lock from end of device configuration (10)                                                       | 10            |     | 400                                                        | μѕ           |

| f <sub>VCO</sub>         | PLL internal VCO operating range                                                                                  | 300           |     | 800 (7)                                                    | MHz          |

| t <sub>LSKEW</sub>       | Clock skew between two external clock outputs driven by the same counter                                          |               | ±50 |                                                            | ps           |

| t <sub>SKEW</sub>        | Clock skew between two external clock outputs driven by the different counters with the same settings             |               | ±75 |                                                            | ps           |

| f <sub>SS</sub>          | Spread spectrum modulation frequency                                                                              | 30            |     | 150                                                        | kHz          |

| % spread                 | Percentage spread for spread spectrum frequency (9)                                                               | 0.4           | 0.5 | 0.6                                                        | %            |

| t <sub>ARESET</sub>      | Minimum pulse width on areset signal                                                                              | 10            |     |                                                            | ns           |

| Table 6-90             | Table 6–90. Enhanced PLL Specifications for -7 Speed Grade (Part 1 of 3) |       |     |          |      |  |  |  |  |

|------------------------|--------------------------------------------------------------------------|-------|-----|----------|------|--|--|--|--|

| Symbol                 | Parameter                                                                | Min   | Тур | Max      | Unit |  |  |  |  |

| f <sub>IN</sub>        | Input clock frequency                                                    | 3 (1) |     | 565      | MHz  |  |  |  |  |

| f <sub>INDUTY</sub>    | Input clock duty cycle                                                   | 40    |     | 60       | %    |  |  |  |  |

| f <sub>EINDUTY</sub>   | External feedback clock input duty cycle                                 | 40    |     | 60       | %    |  |  |  |  |

| t <sub>INJITTER</sub>  | Input clock period jitter                                                |       |     | ±200 (2) | ps   |  |  |  |  |

| t <sub>EINJITTER</sub> | External feedback clock period jitter                                    |       |     | ±200 (2) | ps   |  |  |  |  |

Table 6–91 describes the Stratix GX device fast PLL specifications.

| Table 6–91. Fast PLL Specifications for -5 & -6 Speed Grade Devices |                                                            |           |                                                            |              |  |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------|-----------|------------------------------------------------------------|--------------|--|--|--|--|

| Symbol                                                              | Parameter                                                  | Min       | Max                                                        | Unit         |  |  |  |  |

| f <sub>IN</sub>                                                     | CLKIN frequency (for $m = 1$ ) (1)                         | 300       | 717                                                        | MHz          |  |  |  |  |

|                                                                     | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 1,000/ <i>m</i>                                            | MHz          |  |  |  |  |

|                                                                     | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 1,000/ <i>m</i>                                            | MHz          |  |  |  |  |

| f <sub>OUT</sub>                                                    | Output frequency for internal global or regional clock (2) | 9.4       | 420                                                        | MHz          |  |  |  |  |

| f <sub>OUT_EXT</sub>                                                | Output frequency for external clock                        | 9.375     | 717                                                        | MHz          |  |  |  |  |

| f <sub>VCO</sub>                                                    | VCO operating frequency                                    | 300       | 1,000                                                      | MHz          |  |  |  |  |

| t <sub>INDUTY</sub>                                                 | CLKIN duty cycle                                           | 40        | 60                                                         | %            |  |  |  |  |

| t <sub>INJITTER</sub>                                               | Period jitter for CLKIN pin                                |           | ±200                                                       | ps           |  |  |  |  |

| t <sub>DUTY</sub>                                                   | Duty cycle for DFFIO 1× CLKOUT pin (3)                     | 45        | 55                                                         | %            |  |  |  |  |

| t <sub>JITTER</sub>                                                 | Period jitter for DIFFIO clock out (3)                     |           | ±80                                                        | ps           |  |  |  |  |

|                                                                     | Period jitter for internal global or regional clock        |           | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |  |

| t <sub>LOCK</sub>                                                   | Time required for PLL to acquire lock                      | 10        | 100                                                        | μs           |  |  |  |  |

| m                                                                   | Multiplication factors for <i>m</i> counter (3)            | 1         | 32                                                         | Integer      |  |  |  |  |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0                                  | Multiplication factors for I0, I1, and g0 counter (4), (5) | 1         | 32                                                         | Integer      |  |  |  |  |

| t <sub>ARESET</sub>                                                 | Minimum pulse width on areset signal                       | 10        |                                                            | ns           |  |  |  |  |

| Symbol                | Parameter                                                  | Min       | Max           | Unit |

|-----------------------|------------------------------------------------------------|-----------|---------------|------|

| f <sub>IN</sub>       | CLKIN frequency (for $m = 1$ ) (1),                        | 300       | 640           | MHz  |

|                       | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 700/ <i>m</i> | MHz  |

|                       | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 700/ <i>m</i> | MHz  |

| f <sub>OUT</sub>      | Output frequency for internal global or regional clock (2) | 9.375     | 420           | MHz  |

| f <sub>OUT_EXT</sub>  | Output frequency for external clock                        | 9.4       | 500           | MHz  |

| f <sub>VCO</sub>      | VCO operating frequency                                    | 300       | 700           | MHz  |

| t <sub>INDUTY</sub>   | CLKIN duty cycle                                           | 40        | 60            | %    |

| t <sub>INJITTER</sub> | Period jitter for CLKIN pin                                |           | ±200          | ps   |