Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2566                                                        |

| Number of Logic Elements/Cells | 25660                                                       |

| Total RAM Bits                 | 1944576                                                     |

| Number of I/O                  | 607                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25ff1020c6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Pattern detector and word aligner supports programmable patterns

- 8B/10B encoder/decoder performs 8- to 10-bit encoding and 10to 8-bit decoding

- Rate matcher compliant with IEEE 802.3-2002 for GigE mode and with IEEE 802-3ae for XAUI mode

- Channel bonding compliant with IEEE 802.3ae (for XAUI mode only)

- Device can bypass some transceiver block features if necessary

#### ■ FPGA features are as follows:

- 10,570 to 41,250 logic elements (LEs); see Table 1–1

- Up to 3,423,744 RAM bits (427,968 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in-out (FIFO) buffers

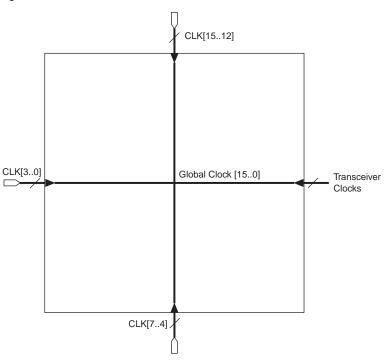

- Up to 16 global clock networks with up to 22 regional clock networks per device region

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to eight general usage phase-locked loops (four enhanced PLLs and four fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed source-synchronous differential I/O support on up to 45 channels for 1-Gbps performance

- Support for source-synchronous bus standards, including 10-Gigabit Ethernet XSBI, Parallel RapidIO, UTOPIA IV, Network Packet Streaming Interface (NPSI), HyperTransport™ technology, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for multiple intellectual property megafunctions from Altera<sup>®</sup> MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

- Dynamic phase alignment on LVDS receiver channels

| Table 1–1. Stratix GX Device Features  |                        |                                     |                        |  |  |  |

|----------------------------------------|------------------------|-------------------------------------|------------------------|--|--|--|

| Feature                                | EP1SGX10C<br>EP1SGX10D | EP1SGX25C<br>EP1SGX25D<br>EP1SGX25F | EP1SGX40D<br>EP1SGX40G |  |  |  |

| LEs                                    | 10,570                 | 25,660                              | 41,250                 |  |  |  |

| Transceiver channels                   | 4, 8                   | 4, 8, 16                            | 8, 20                  |  |  |  |

| Source-synchronous channels            | 22                     | 39                                  | 45                     |  |  |  |

| M512 RAM blocks (32 × 18 bits)         | 94                     | 224                                 | 384                    |  |  |  |

| M4K RAM blocks (128 × 36 bits)         | 60                     | 138                                 | 183                    |  |  |  |

| M-RAM blocks (4K ×144 bits)            | 1                      | 2                                   | 4                      |  |  |  |

| Total RAM bits                         | 920,448                | 1,944,576                           | 3,423,744              |  |  |  |

| Digital signal processing (DSP) blocks | 6                      | 10                                  | 14                     |  |  |  |

| Embedded multipliers (1)               | 48                     | 80                                  | 112                    |  |  |  |

| PLLs                                   | 4                      | 4                                   | 8                      |  |  |  |

#### Note to Table 1–1:

(1) This parameter lists the total number of 9- × 9-bit multipliers for each device. For the total number of 18- × 18-bit multipliers per device, divide the total number of 9- × 9-bit multipliers by 2. For the total number of 36- × 36-bit multipliers per device, decide the total number of 9- × 9-bit multipliers by 8.

Stratix GX devices are available in space-saving FineLine BGA® packages (refer to Tables 1–2 and 1–3), and in multiple speed grades (refer to Table 1–4). Stratix GX devices support vertical migration within the same package (that is, you can migrate between the EP1SGX10C and EP1SGX25C devices in the 672-pin FineLine BGA package). See the Stratix GX device pin tables for more information. Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type, to identify which I/O pins it is possible to migrate. The Quartus II software can automatically cross reference and place all pins for migration when given a device migration list.

| Table 1–2. Stratix GX Package Options & I/O Pin Counts (Part 1 of 2) Note (1) |     |  |  |  |

|-------------------------------------------------------------------------------|-----|--|--|--|

| Device 672-Pin FineLine BGA 1,020-Pin FineLine BGA                            |     |  |  |  |

| EP1SGX10C                                                                     | 362 |  |  |  |

| EP1SGX10D                                                                     | 362 |  |  |  |

| EP1SGX25C                                                                     | 455 |  |  |  |

### **Loopback Modes**

The Stratix GX transceiver has built-in loopback modes to aid in debug and testing. The loopback modes are set in the Stratix GX MegaWizard Plug-In Manager in the Quartus II software. Only one loopback mode can be set at any single instance of the transceiver block. The loopback mode applies to all used channels in a transceiver block.

The available loopback modes are:

- Serial loopback

- Parallel loopback

- Reverse serial loopback

### Serial Loopback

Serial loopback exercises all the transceiver logic except for the output buffer and input buffer. The loopback function is dynamically switchable through the <code>rx\_slpbk</code> port on a channel by channel basis. The  $V_{OD}$  of the output reduced. If you select 400 mV, the output is tri-stated when the serial loopback option is selected. Figure 2–21 shows the data path in serial loopback mode.

BIST PRBS

Verifier

Channel

Aligner

Cha

Figure 2-21. Data Path in Serial Loopback Mode

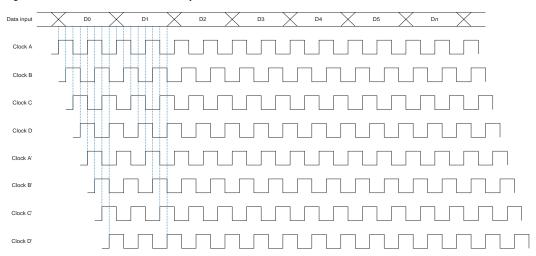

Figure 3-9. Fast PLL Clocks & Data Input

### Protocols, Training Pattern & DPA Lock Time

The dynamic phase aligner uses a fast PLL for clock multiplication, and the dynamic phase selector for the phase detection and alignment. The dynamic phase aligner uses the high-speed clock out of the dynamic phase selector to deserialize high-speed data and the receiver's source synchronous operations.

At each rising edge of the clock, the dynamic phase selector determines the phase difference between the clock and the data and automatically compensates for the phase difference between the data and clock.

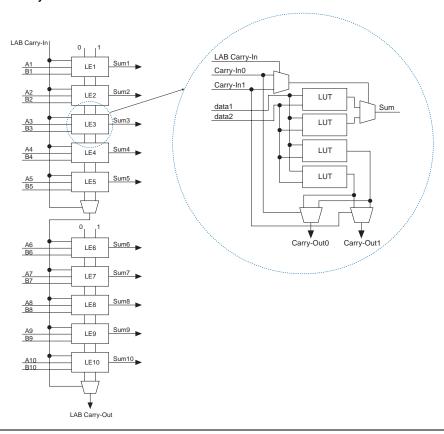

Figure 4-7. Carry Select Chain

## **Clear & Preset Logic Control**

LAB-wide signals control the logic for the register's clear and preset signals. The LE directly supports an asynchronous clear and preset function. The register preset is achieved through the asynchronous load of a logic high. The direct asynchronous preset does not require a NOT-gate push-back technique. Stratix GX devices support simultaneous preset/ asynchronous load, and clear signals. An asynchronous clear signal takes precedence if both signals are asserted simultaneously. Each LAB supports up to two clears and one preset signal.

In addition to the clear and preset ports, Stratix GX devices provide a chip-wide reset pin (DEV\_CLRn) that resets all registers in the device. An option set before compilation in the Quartus II software controls this pin. This chip-wide reset overrides all other control signals.

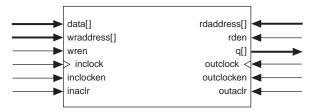

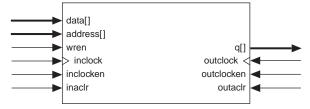

occurs or just read the don't care bits. Single-port memory supports non-simultaneous reads and writes, but the <code>q[]</code> port outputs the data once it has been written to the memory (if the outputs are not registered) or after the next rising edge of the clock (if the outputs are registered). For more information, see the <code>TriMatrix Embedded Memory Blocks in Stratix & Stratix GX Devices</code> chapter of the <code>Stratix GX Device Handbook, Volume 2. Figure 4–12</code> shows these different RAM memory port configurations for TriMatrix memory.

Figure 4–12. Simple Dual-Port & Single-Port Memory Configurations

### Simple Dual-Port Memory

### Single-Port Memory (1)

#### Note to Figure 4-12:

Two single-port memory blocks can be implemented in a single M4K block as long as each of the two independent block sizes is equal to or less than half of the M4K block size.

The memory blocks also enable mixed-width data ports for reading and writing to the RAM ports in dual-port RAM configuration. For example, the memory block can be written in  $\times 1$  mode at port A and read out in  $\times 16$  mode from port B.

TriMatrix memory architecture can implement pipelined RAM by registering both the input and output signals to the RAM block. All TriMatrix memory block inputs are registered providing synchronous write cycles. In synchronous operation, the memory block generates its own self-timed strobe write enable (WREN) signal derived from the global

M4K RAM blocks support byte writes when the write port has a data width of 16, 18, 32, or 36 bits. The byte enables allow the input data to be masked so the device can write to specific bytes. The unwritten bytes retain the previous written value. Table 4–6 summarizes the byte selection.

| Table 4–6. Byte Enable for M4K Blocks Notes (1), (2) |       |        |  |  |  |

|------------------------------------------------------|-------|--------|--|--|--|

| byteena[30] datain ×18 datain ×36                    |       |        |  |  |  |

| [0] = 1                                              | [80]  | [80]   |  |  |  |

| [1] = 1                                              | [179] | [179]  |  |  |  |

| [2] = 1                                              | _     | [2618] |  |  |  |

| [3] = 1                                              | _     | [3527] |  |  |  |

#### Notes to Table 4-6:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, that is, in ×16 and ×32 modes.

The M4K RAM blocks allow for different clocks on their inputs and outputs. Either of the two clocks feeding the block can clock M4K RAM block registers (renwe, address, byte enable, datain, and output registers). Only the output register can be bypassed. The eight labclk signals or local interconnects can drive the control signals for the A and B ports of the M4K RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals, as shown in Figure 4–16.

The R4, R8, C4, C8, and direct link interconnects from adjacent LABs drive the M4K RAM block local interconnect. The M4K RAM blocks can communicate with LABs on either the left or right side through these row resources or with LAB columns on either the right or left with the column resources. Up to 10 direct link input connections to the M4K RAM Block are possible from the left adjacent LABs and another 10 possible from the right adjacent LAB. M4K RAM block outputs can also connect to left and right LABs through 10 direct link interconnects each. Figure 4–17 shows the M4K RAM block to logic array interface.

| Table 4–10. M-RAM Combined Byte Selection for ×144 Mode Notes (1), (2) |             |  |  |

|------------------------------------------------------------------------|-------------|--|--|

| byteena[150]                                                           | datain ×144 |  |  |

| [0] = 1                                                                | [80]        |  |  |

| [1] = 1                                                                | [179]       |  |  |

| [2] = 1                                                                | [2618]      |  |  |

| [3] = 1                                                                | [3527]      |  |  |

| [4] = 1                                                                | [4436]      |  |  |

| [5] = 1                                                                | [5345]      |  |  |

| [6] = 1                                                                | [6254]      |  |  |

| [7] = 1                                                                | [7163]      |  |  |

| [8] = 1                                                                | [8072]      |  |  |

| [9] = 1                                                                | [8981]      |  |  |

| [10] = 1                                                               | [9890]      |  |  |

| [11] = 1                                                               | [10799]     |  |  |

| [12] = 1                                                               | [116108]    |  |  |

| [13] = 1                                                               | [125117]    |  |  |

| [14] = 1                                                               | [134126]    |  |  |

| [15] = 1                                                               | [143135]    |  |  |

#### Notes to Tables 4-9 and 4-10:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, that is, in  $\times 16$ ,  $\times 32$ ,  $\times 64$ , and  $\times 128$  modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 4–18.

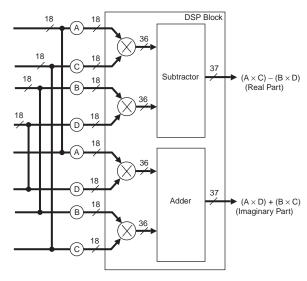

You can use the two-multipliers adder mode for complex multiplications, which are written as:

$$(a+jb)\times(c+jd) = [(a\times c) - (b\times d)] + j\times[(a\times d) + (b\times c)]$$

The two-multipliers adder mode allows a single DSP block to calculate the real part [(a × c) – (b × d)] using one subtractor and the imaginary part [(a × d) + (b × c)] using one adder, for data widths up to 18 bits. Two complex multiplications are possible for data widths up to 9 bits using four adder/subtractor/accumulator blocks. Figure 4–37 shows an 18-bit two-multipliers adder.

Figure 4-37. Two-Multipliers Adder Mode Implementing Complex Multiply

### Four-Multipliers Adder Mode

In the four-multipliers adder mode, the DSP block adds the results of two first -stage adder/subtractor blocks. One sum of four  $18 \times 18$ -bit multipliers or two different sums of two sets of four  $9 \times 9$ -bit multipliers can be implemented in a single DSP block. The product width for each multiplier must be the same size. The four-multipliers adder mode is useful for FIR filter applications. Figure 4–38 shows the four multipliers adder mode.

Figure 4-41. Global Clock Resources

### Regional Clock Network

There are four regional clock networks RCLK [3..0] within each quadrant of the Stratix GX device that are driven by the same dedicated CLK [7..0] and CLK [15..12] input pins, PLL outputs, or transceiver clocks. The regional clock networks only pertain to the quadrant they drive into. The regional clock networks provide the lowest clock delay and skew for logic contained within a single quadrant. The CLK clock pins symmetrically drive the RCLK networks within a particular quadrant, as shown in Figure 4–42.

| Table 4–18. Stratix GX Enhanced PLL & Fast PLL Features (Part 2 of 2) Notes (1)–(8) |                                                                 |     |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|--|--|

| Feature                                                                             | Fast PLL                                                        |     |  |  |

| Number of external clock outputs                                                    | Four differential/eight singled-ended or one single-ended $(6)$ | (7) |  |  |

| Number of feedback clock inputs                                                     | 4 (8)                                                           |     |  |  |

#### Notes to Table 4-18:

- (1) The maximum count value is 1024, with a 50% duty cycle setting on the counter. The maximum count value for any other duty cycle setting is 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the VCO period divided by 8.

- (4) For degree increments, Stratix GX devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7 and 8 have two output ports per PLL. PLLs 1 and 2 have three output ports per PLL.

- (6) Every Stratix GX device has two enhanced PLLs (PLLs 5 and 6) with eight single-ended or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EP1SGX40 devices each have one single-ended output.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix GX device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

Figure 4–48 shows a top-level diagram of the Stratix GX device and the PLL floorplan.

### External Clock Outputs

Enhanced PLLs 5 and 6 each support up to eight single-ended clock outputs (or four differential pairs). See Figure 4–54.

From IOE (1) > extclk0\_a e0 Counter From IOE (1) From IOE (1) e1 Counter From IOE (1) From IOE (1 extclk2\_a e2 Counter extclk2\_b From IOE (1) From IOE (1) e3 Counter extclk3\_b From IOE (1)

Figure 4-54. External Clock Outputs for PLLs 5 & 6

Notes to Figure 4-54:

- Each external clock output pin can be used as a general purpose output pin from the logic array. These pins are multiplexed with IOE outputs.

- (2) Two single-ended outputs are possible per output counter—either two outputs of the same frequency and phase or one shifted 180°.

Any of the four external output counters can drive the single-ended or differential clock outputs for PLLs 5 and 6. This means one counter or frequency can drive all output pins available from PLL 5 or PLL 6. Each

feedback for one of the dedicated external outputs, either one single-ended or one differential pair. In this mode, one *e* counter feeds back to the PLL FBIN input, becoming part of the feedback loop.

- Normal mode: If an internal clock is used in this mode, it is phase-aligned to the input clock pin. The external clock output pin has a phase delay relative to the clock input pin if connected in this mode. You define which internal clock output from the PLL should be phase-aligned to the internal clock pin.

- No compensation: In this mode, the PLL does not compensate for any clock networks or external clock outputs.

### Phase & Delay Shifting

Stratix GX device enhanced PLLs provide advanced programmable phase and clock delay shifting. For phase shifting, you can specify a phase shift (in degrees or time units) for each PLL clock output port or for all outputs together in one shift. Phase-shifting values in time units are allowed with a resolution range of 160 to 420 ps. This resolution is a function of frequency input and the multiplication and division factors. In other words, it is a function of the VCO period equal to one-eighth of the VCO period. Each clock output counter can choose a different phase of the VCO period from up to eight taps. You can use this clock output counter along with an initial setting on the post-scale counter to achieve a phase-shift range for the entire period of the output clock. The phase tap feedback to the *m* counter can shift all outputs to a single phase or delay. The Quartus II software automatically sets the phase taps and counter settings according to the phase shift entered.

In addition to the phase-shift feature, the fine tune clock delay shift feature provides advanced time delay shift control on each of the four PLL outputs. Each PLL output shifts in 250-ps increments for a range of  $-3.0\,\mathrm{ns}$  to  $+3.0\,\mathrm{ns}$  between any two outputs using discrete delay elements. Total delay shift between any two PLL outputs must be less than 3 ns. For example, shifts on outputs of -1 and +2 ns is allowed, but not -1 and  $+2.5\,\mathrm{ns}$ . There is some delay variation due to process, voltage, and temperature. Only the clock delay shift blocks can be controlled during system operation for dynamic clock delay control.

### Spread-Spectrum Clocking

The Stratix GX device's enhanced PLLs use spread-spectrum technology to reduce electromagnetic interference generation from a system by distributing the energy over a broader frequency range. The enhanced

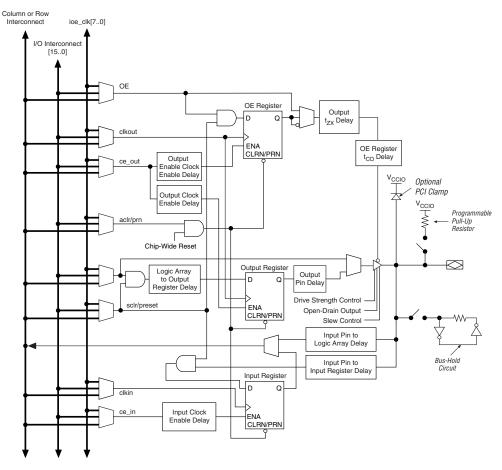

Figure 4–63. Stratix GX IOE in Bidirectional I/O Configuration Note (1)

*Note to Figure 4–63:*

(1) All input signals to the IOE can be inverted at the IOE.

The Stratix GX device IOE includes programmable delays that can be activated to ensure zero hold times, input IOE register-to-logic array register transfers, or logic array-to-output IOE register transfers.

A path in which a pin directly drives a register may require the delay to ensure zero hold time, whereas a path in which a pin drives a register through combinatorial logic may not require the delay. Programmable delays exist for decreasing input-pin-to-logic-array and IOE input register delays. The Quartus II Compiler can program these delays to automatically minimize setup time while providing a zero hold time.

### Slew-Rate Control

The output buffer for each Stratix GX device I/O pin has a programmable output slew-rate control that can be configured for low-noise or high-speed performance. A faster slew rate provides high-speed transitions for high-performance systems. However, these fast transitions may introduce noise transients into the system. A slow slew rate reduces system noise, but adds a nominal delay to rising and falling edges. Each I/O pin has an individual slew-rate control, allowing you to specify the slew rate on a pin-by-pin basis. The slew-rate control affects both the rising and falling edges.

### **Bus Hold**

Each Stratix GX device I/O pin provides an optional bus-hold feature. The bus-hold circuitry can weakly hold the signal on an I/O pin at its last-driven state. Since the bus-hold feature holds the last-driven state of the pin until the next input signal is present, an external pull-up or pull-down resistor is not needed to hold a signal level when the bus is tri-stated.

Table 4–25 shows bus hold support for different pin types.

| Table 4–25. Bus Hold Support |          |  |  |  |

|------------------------------|----------|--|--|--|

| Pin Type                     | Bus Hold |  |  |  |

| I/O pins                     | ✓        |  |  |  |

| CLK[150]                     |          |  |  |  |

| CLK[0,1,2,3,8,9,10,11]       |          |  |  |  |

| FCLK                         | <b>✓</b> |  |  |  |

| FPLL[710]CLK                 |          |  |  |  |

The bus-hold circuitry also pulls undriven pins away from the input threshold voltage where noise can cause unintended high-frequency switching. You can select this feature individually for each I/O pin. The bus-hold output drives no higher than  $V_{\rm CCIO}$  to prevent overdriving signals. If the bus-hold feature is enabled, the programmable pull-up option cannot be used. Disable the bus-hold feature when using opendrain outputs with the GTL+ I/O standard or when the I/O pin has been configured for differential signals.

and before and during configuration. Together, the configuration and initialization processes are called command mode. Normal device operation is called user mode.

A built-in weak pull-up resistor pulls all user I/O pins to  $V_{\text{CCIO}}$  before and during device configuration.

SRAM configuration elements allow Stratix GX devices to be reconfigured in-circuit by loading new configuration data into the device. With real-time reconfiguration, the device is forced into command mode with a device pin. The configuration process loads different configuration data, reinitializes the device, and resumes user-mode operation. You can perform in-field upgrades by distributing new configuration files either within the system or remotely.

### **Configuration Schemes**

You can load the configuration data for a Stratix GX device with one of five configuration schemes (see Table 5–1), chosen on the basis of the target application. You can use a configuration device, intelligent controller, or the JTAG port to configure a Stratix GX device. A configuration device can automatically configure a Stratix GX device at system power-up.

You can configure multiple Stratix GX devices in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 5–1. Data Sources for Configuration |                                                                                                         |  |  |  |

|-------------------------------------------|---------------------------------------------------------------------------------------------------------|--|--|--|

| Configuration Scheme                      | Data Source                                                                                             |  |  |  |

| Configuration device                      | Enhanced or EPC2 configuration device                                                                   |  |  |  |

| Passive serial (PS)                       | ByteBlasterMV <sup>™</sup> or MasterBlaster <sup>™</sup> download cable or serial data source           |  |  |  |

| Passive parallel asynchronous (PPA)       | Parallel data source                                                                                    |  |  |  |

| Fast passive parallel                     | Parallel data source                                                                                    |  |  |  |

| JTAG                                      | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam or JBC file (.jam or .jbc) |  |  |  |

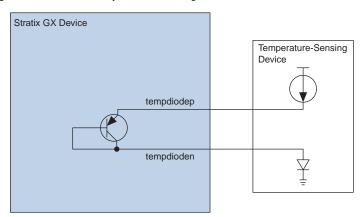

Figure 5-4. External Temperature-Sensing Diode

Table 5–2 shows the specifications for bias voltage and current of the Stratix GX temperature-sensing diode.

| Table 5–2. Temperature-Sensing Diode Electrical Characteristics |     |     |     |    |  |  |  |  |

|-----------------------------------------------------------------|-----|-----|-----|----|--|--|--|--|

| Parameter Minimum Typical Maximum Units                         |     |     |     |    |  |  |  |  |

| I <sub>BIAS</sub> high                                          | 80  | 100 | 120 | μΑ |  |  |  |  |

| I <sub>BIAS</sub> low                                           | 8   | 10  | 12  | μΑ |  |  |  |  |

| $V_{BP} - V_{BN}$                                               | 0.3 |     | 0.9 | V  |  |  |  |  |

| V <sub>BN</sub>                                                 |     | 0.7 |     | V  |  |  |  |  |

| Series resistance                                               |     |     | 3   | W  |  |  |  |  |

The temperature-sensing diode works for the entire operating range shown in Figure 5–5.

| Table 6–2. Stratix GX Device Recommended Operating Conditions (Part 2 of 2)       Note (7), (12), (13) |                                |                    |         |                   |      |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------|--------------------|---------|-------------------|------|--|

| Symbol                                                                                                 | Parameter                      | Conditions         | Minimum | Maximum           | Unit |  |

| Vo                                                                                                     | Output voltage                 |                    | 0       | V <sub>CCIO</sub> | V    |  |

| T <sub>J</sub>                                                                                         | Operating junction temperature | For commercial use | 0       | 85                | ° C  |  |

|                                                                                                        |                                | For industrial use | -40     | 100               | ° C  |  |

| Table 6–3.                    | Table 6–3. Stratix GX Device DC Operating Conditions   Note (12) |                                |         |         |         |      |

|-------------------------------|------------------------------------------------------------------|--------------------------------|---------|---------|---------|------|

| Symbol                        | Parameter                                                        | Conditions                     | Minimum | Typical | Maximum | Unit |

| l <sub>i</sub>                | Input pin leakage current                                        | $V_I = V_{CCIOmax}$ to 0 V (8) | -10     |         | 10      | μА   |

| l <sub>OZ</sub>               | Tri-stated I/O pin leakage current                               | $V_O = V_{CCIOmax}$ to 0 V (8) | -10     |         | 10      | μА   |

| R <sub>CONF</sub>             | Value of I/O pin pull-                                           | V <sub>CCIO</sub> = 3.0 V (9)  | 20      |         | 50      | kΩ   |

| up resistor before and during | V <sub>CCIO</sub> = 2.375 V (9)                                  | 30                             |         | 80      | kΩ      |      |

|                               | configuration                                                    | V <sub>CCIO</sub> = 1.71 V (9) | 60      |         | 150     | kΩ   |

| Table 6–4. Stratix GX Transceiver Block Absolute Maximum Ratings |                                              |                           |         |                     |       |  |  |

|------------------------------------------------------------------|----------------------------------------------|---------------------------|---------|---------------------|-------|--|--|

| Symbol                                                           | Parameter                                    | Conditions                | Minimum | Maximum             | Units |  |  |

| V <sub>CCA</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 4.6                 | ٧     |  |  |

| V <sub>CCP</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | ٧     |  |  |

| V <sub>CCR</sub>                                                 | Transceiver block supply Voltage             | Commercial and industrial | -0.5    | 2.4                 | ٧     |  |  |

| V <sub>CCT</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | V     |  |  |

| V <sub>CCG</sub>                                                 | Transceiver block supply voltage             | Commercial and industrial | -0.5    | 2.4                 | V     |  |  |

| Receiver input voltage                                           | V <sub>ICM</sub> ±V <sub>ID</sub> single / 2 | Commercial and industrial |         | 1.675<br>(10), (13) | ٧     |  |  |

| refclkb input<br>voltage                                         | V <sub>ICM</sub> ±V <sub>ID</sub> single / 2 | Commercial and industrial |         | 1.675<br>(10), (13) | V     |  |  |

| Symbol                                      | Conditions                                                                  |                                      |                                | -5 Speed Grade |     |     | -6 Speed Grade |     |     | -7 Speed Grade |     |     | 11   |

|---------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------|--------------------------------|----------------|-----|-----|----------------|-----|-----|----------------|-----|-----|------|

|                                             |                                                                             |                                      |                                | Min            | Тур | Max | Min            | Тур | Max | Min            | Тур | Max | Unit |

| DPA Lock Time                               | Standard                                                                    | Train ing Patt ern                   | Trans<br>ition<br>Den-<br>sity |                |     |     |                |     |     |                |     |     |      |

|                                             | SPI-4,<br>CSIX                                                              | 0000<br>0000<br>0011<br>1111<br>1111 | 10%                            | 256            |     |     | 256            |     |     | 256            |     |     | (4)  |

|                                             | Rapid IO                                                                    | 0000<br>1111                         | 25%                            | 256            |     |     | 256            |     |     | 256            |     |     | (4)  |

|                                             |                                                                             | 1001<br>0000                         | 50%                            | 256            |     |     | 256            |     |     | 256            |     |     | (4)  |

|                                             | Misc                                                                        | 1010<br>1010                         | 100<br>%                       | 256            |     |     | 256            |     |     | 256            |     |     | (4)  |

|                                             |                                                                             | 0101<br>0101                         |                                | 256            |     |     | 256            |     |     | 256            |     |     | (4)  |

| TCCS                                        | All                                                                         |                                      | •                              |                |     | 200 |                |     | 200 |                |     | 300 | ps   |

| SW                                          | PCML ( <i>J</i> = 4, 7, 8, 10)                                              |                                      |                                | 750            |     |     | 750            |     |     | 800            |     |     | ps   |

|                                             | PCML ( <i>J</i> = 2)                                                        |                                      |                                | 900            |     |     | 900            |     |     | 1,200          |     |     | ps   |

|                                             | PCML ( <i>J</i> = 1)                                                        |                                      |                                | 1,500          |     |     | 1,500          |     |     | 1,700          |     |     | ps   |

|                                             | LVDS and LVPECL (J = 1)                                                     |                                      |                                | 500            |     |     | 500            |     |     | 550            |     |     | ps   |

|                                             | LVDS, LVPECL,<br>HyperTransport<br>technology ( <i>J</i> = 2<br>through 10) |                                      |                                | 440            |     |     | 440            |     |     | 500            |     |     | ps   |

| Input jitter<br>tolerance<br>(peak-to-peak) | All                                                                         |                                      |                                |                |     | 250 |                |     | 250 |                |     | 250 | ps   |

| Output jitter<br>(peak-to-peak)             | All                                                                         |                                      |                                |                |     | 160 |                |     | 160 |                |     | 200 | ps   |

| Output t <sub>RISE</sub>                    | LVDS                                                                        |                                      |                                | 80             | 110 | 120 | 80             | 110 | 120 | 80             | 110 | 120 | ps   |

|                                             | HyperTransport technology                                                   |                                      |                                | 110            | 170 | 200 | 110            | 170 | 200 | 120            | 170 | 200 | ps   |

|                                             | LVPECL                                                                      |                                      |                                | 90             | 130 | 150 | 90             | 130 | 150 | 100            | 135 | 150 | ps   |

|                                             | PCML                                                                        |                                      |                                | 80             | 110 | 135 | 80             | 110 | 135 | 80             | 110 | 135 | ps   |

| Symbol                             | Symbol Parameter                                           |    | Max                                                        | Unit         |

|------------------------------------|------------------------------------------------------------|----|------------------------------------------------------------|--------------|

| t <sub>DUTY</sub>                  | Duty cycle for DFFIO 1× CLKOUT pin (3)                     | 45 | 55                                                         | %            |

| t <sub>JITTER</sub>                | Period jitter for DIFFIO clock out (3)                     |    | ±80                                                        | ps           |

|                                    | Period jitter for internal global or regional clock        |    | ±100 ps for >200 MHz outclk<br>±20 mUI for <200 MHz outclk | ps or<br>mUl |

| t <sub>LOCK</sub>                  | Time required for PLL to acquire lock                      | 10 | 100                                                        | μs           |

| m                                  | Multiplication factors for <i>m</i> counter (4)            | 1  | 32                                                         | Integer      |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0 | Multiplication factors for 10, 11, and g0 counter (4), (5) | 1  | 32                                                         | Integer      |

| t <sub>ARESET</sub>                | Minimum pulse width on areset signal                       | 10 |                                                            | ns           |

#### *Notes to Tables 6-91 & 6-92:*

- (1) See "Maximum Input & Output Clock Rates" on page 6–54.

- (2) When using the SERDES, high-speed differential I/O mode supports a maximum output frequency of 210 MHz to the global or regional clocks (that is, the maximum data rate 840 Mbps divided by the smallest SERDES J factor of 4).

- (3) This parameter is for high-speed differential I/O mode only.

- (4) These counters have a maximum of 32 if programmed for 50/50 duty cycle. Otherwise, they have a maximum of 16.

- (5) High-speed differential I/O mode supports W = 1 to 16 and J = 4, 7, 8, or 10.

# **DLL Jitter**

Table 6–93 reports the jitter for the DLL in the DQS phase-shift reference circuit.

| Table 6–93. DLL Jitter for DQS Phase Shift Reference Circuit |                 |  |  |  |  |

|--------------------------------------------------------------|-----------------|--|--|--|--|

| Frequency (MHz)                                              | DLL Jitter (ps) |  |  |  |  |

| 197 to 200                                                   | ± 100           |  |  |  |  |

| 160 to 196                                                   | ± 300           |  |  |  |  |

| 100 to 159                                                   | ± 500           |  |  |  |  |