Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

# **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 2566                                                        |

| Number of Logic Elements/Cells | 25660                                                       |

| Total RAM Bits                 | 1944576                                                     |

| Number of I/O                  | 607                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | -40°C ~ 100°C (TJ)                                          |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx25ff1020i6 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Pattern detector and word aligner supports programmable patterns

- 8B/10B encoder/decoder performs 8- to 10-bit encoding and 10to 8-bit decoding

- Rate matcher compliant with IEEE 802.3-2002 for GigE mode and with IEEE 802-3ae for XAUI mode

- Channel bonding compliant with IEEE 802.3ae (for XAUI mode only)

- Device can bypass some transceiver block features if necessary

### ■ FPGA features are as follows:

- 10,570 to 41,250 logic elements (LEs); see Table 1–1

- Up to 3,423,744 RAM bits (427,968 bytes) available without reducing logic resources

- TriMatrix<sup>™</sup> memory consisting of three RAM block sizes to implement true dual-port memory and first-in-out (FIFO) buffers

- Up to 16 global clock networks with up to 22 regional clock networks per device region

- High-speed DSP blocks provide dedicated implementation of multipliers (faster than 300 MHz), multiply-accumulate functions, and finite impulse response (FIR) filters

- Up to eight general usage phase-locked loops (four enhanced PLLs and four fast PLLs) per device provide spread spectrum, programmable bandwidth, clock switchover, real-time PLL reconfiguration, and advanced multiplication and phase shifting

- Support for numerous single-ended and differential I/O standards

- High-speed source-synchronous differential I/O support on up to 45 channels for 1-Gbps performance

- Support for source-synchronous bus standards, including 10-Gigabit Ethernet XSBI, Parallel RapidIO, UTOPIA IV, Network Packet Streaming Interface (NPSI), HyperTransport™ technology, SPI-4 Phase 2 (POS-PHY Level 4), and SFI-4

- Support for high-speed external memory, including zero bus turnaround (ZBT) SRAM, quad data rate (QDR and QDRII) SRAM, double data rate (DDR) SDRAM, DDR fast cycle RAM (FCRAM), and single data rate (SDR) SDRAM

- Support for multiple intellectual property megafunctions from Altera<sup>®</sup> MegaCore<sup>®</sup> functions and Altera Megafunction Partners Program (AMPP<sup>SM</sup>) megafunctions

- Support for remote configuration updates

- Dynamic phase alignment on LVDS receiver channels

| Table 1–1. Stratix GX Device Features  |                        |                                     |                        |  |

|----------------------------------------|------------------------|-------------------------------------|------------------------|--|

| Feature                                | EP1SGX10C<br>EP1SGX10D | EP1SGX25C<br>EP1SGX25D<br>EP1SGX25F | EP1SGX40D<br>EP1SGX40G |  |

| LEs                                    | 10,570                 | 25,660                              | 41,250                 |  |

| Transceiver channels                   | 4, 8                   | 4, 8, 16                            | 8, 20                  |  |

| Source-synchronous channels            | 22                     | 39                                  | 45                     |  |

| M512 RAM blocks (32 × 18 bits)         | 94                     | 224                                 | 384                    |  |

| M4K RAM blocks (128 × 36 bits)         | 60                     | 138                                 | 183                    |  |

| M-RAM blocks (4K ×144 bits)            | 1                      | 2                                   | 4                      |  |

| Total RAM bits                         | 920,448                | 1,944,576                           | 3,423,744              |  |

| Digital signal processing (DSP) blocks | 6                      | 10                                  | 14                     |  |

| Embedded multipliers (1)               | 48                     | 80                                  | 112                    |  |

| PLLs                                   | 4                      | 4                                   | 8                      |  |

### Note to Table 1–1:

(1) This parameter lists the total number of 9- × 9-bit multipliers for each device. For the total number of 18- × 18-bit multipliers per device, divide the total number of 9- × 9-bit multipliers by 2. For the total number of 36- × 36-bit multipliers per device, decide the total number of 9- × 9-bit multipliers by 8.

Stratix GX devices are available in space-saving FineLine BGA® packages (refer to Tables 1–2 and 1–3), and in multiple speed grades (refer to Table 1–4). Stratix GX devices support vertical migration within the same package (that is, you can migrate between the EP1SGX10C and EP1SGX25C devices in the 672-pin FineLine BGA package). See the Stratix GX device pin tables for more information. Vertical migration means that you can migrate to devices whose dedicated pins, configuration pins, and power pins are the same for a given package across device densities. For I/O pin migration across densities, you must cross-reference the available I/O pins using the device pin-outs for all planned densities of a given package type, to identify which I/O pins it is possible to migrate. The Quartus II software can automatically cross reference and place all pins for migration when given a device migration list.

| Table 1–2. Stratix GX Package Options & I/O Pin Counts (Part 1 of 2) Note (1) |     |  |  |  |  |  |  |

|-------------------------------------------------------------------------------|-----|--|--|--|--|--|--|

| Device 672-Pin FineLine BGA 1,020-Pin FineLine BG                             |     |  |  |  |  |  |  |

| EP1SGX10C                                                                     | 362 |  |  |  |  |  |  |

| EP1SGX10D                                                                     | 362 |  |  |  |  |  |  |

| EP1SGX25C                                                                     | 455 |  |  |  |  |  |  |

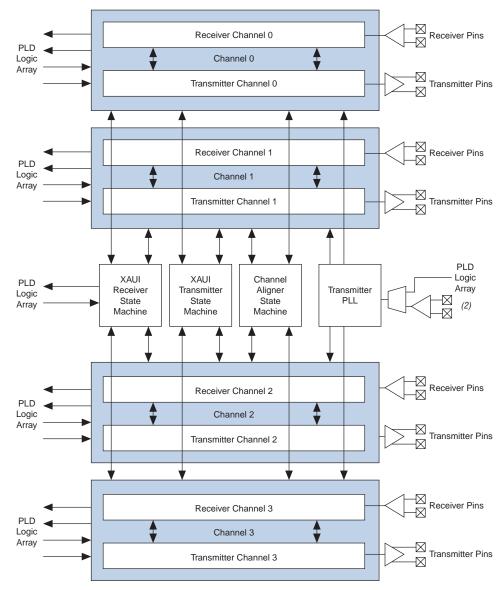

Figure 2–1. Stratix GX Transceiver Block Note (1)

### *Notes to Figure 2–1:*

- (1) Each receiver channel has its own PLL and CRU, which are not shown in this diagram. For more information, refer to the section "Receiver Path" on page 2–13.

- (2) For possible transmitter PLL clock inputs, refer to the section "Transmitter Path" on page 2–5.

### **XAUI Mode**

The transmit state machine translates the XAUI XGMII code group to the XAUI PCS code group. Table 2–3 shows the code conversion.

| Table 2-3. | Code Conversion                           |                                        |                         |

|------------|-------------------------------------------|----------------------------------------|-------------------------|

| XGMII TXC  | XGMII TXD                                 | PCS Code-Group                         | Description             |

| 0          | 00 through FF                             | Dxx.y                                  | Normal data             |

| 1          | 07                                        | K28.0 or K28.3 or<br>K28.5             | Idle in   I             |

| 1          | 07                                        | K28.5                                  | Idle in   T             |

| 1          | 9C                                        | K28.4                                  | Sequence                |

| 1          | FB                                        | K27.7                                  | Start                   |

| 1          | FD                                        | K29.7                                  | Terminate               |

| 1          | FE                                        | K30.7                                  | Error                   |

| 1          | See IEEE 802.3<br>reserved code<br>groups | See IEEE 802.3<br>reserved code groups | Reserved code groups    |

| 1          | Other value                               | K30.7                                  | Invalid XGMII character |

The XAUI PCS idle code groups, /K28.0/ (/R/) and /K28.5/ (/K/), are automatically randomized based on a PRBS7 pattern with an  $x^7+x^6+1$  polynomial. The /K28.3/ (/A/) code group is automatically generated between 16 and 31 idle code groups. The idle randomization on the /A/, /K/, and /R/ code groups are done automatically by the transmit state machine.

### Serializer (Parallel-to-Serial Converter)

The serializer converts the parallel 8-bit or 10-bit data into a serial stream, transmitting the LSB first. The serialized stream is then fed to the transmit buffer. Figure 2–5 is a diagram of the serializer.

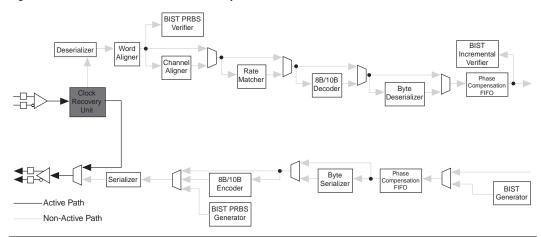

Figure 2-23. Data Path in Reverse Serial Loopback Mode

# **BIST (Built-In Self Test)**

The Stratix GX transceiver has built-in self test modes to aid in debug and testing. The BIST modes are set in the Stratix GX MegaWizard Plug-In Manager in the Quartus II software. Only one BIST mode can be set for any single instance of the transceiver block. The BIST mode applies to all channels used in a transceiver.

The following is a list of the available BIST modes:

- PRBS generator and verifier

- Incremental mode generator and verifier

- High-frequency generator

- Low-frequency generator

- Mixed-frequency generator

Figures 2–24 and 2–25 are diagrams of the BIST PRBS data path and the BIST incremental data path, respectively.

# 3. Source-Synchronous Signaling With DPA

SGX51003-1.1

# Introduction

Expansion in the telecommunications market and growth in Internet use requires systems to move more data faster than ever. To meet this demand, rely on solutions such as differential signaling and emerging high-speed interface standards including RapidIO, POS-PHY 4, SFI-4, or XSBI.

These new protocols support differential data rates up to 1 Gbps and higher. At these high data rates, it becomes more challenging to manage the skew between the clock and data signals. One solution to this challenge is to use CDR to eliminate skew between data channels and clock signals. Another potential solution, DPA, is beginning to be incorporated into some of these protocols.

The source-synchronous high-speed interface in Stratix GX devices is a dedicated circuit embedded into the PLD allowing for high-speed communications. The *High-Speed Source-Synchronous Differential I/O Interfaces in Stratix GX Devices* chapter of the *Stratix GX Device Handbook, Volume 2* provides information on the high-speed I/O standard features and functions of the Stratix GX device.

## Stratix GX I/O Banks

Stratix GX devices contain 17 I/O banks. I/O banks one and two support high-speed LVDS, LVPECL, and 3.3-V PCML inputs and outputs. These two banks also incorporate an embedded dynamic phase aligner within the source-synchronous interface (see Figure 3–8 on page 3–10). The dynamic phase aligner corrects for the phase difference between the clock and data lines caused by skew. The dynamic phase aligner operates automatically and continuously without requiring a fixed training pattern, and allows the source-synchronous circuitry to capture data correctly regardless of the channel-to-clock skew.

# **Principles of SERDES Operation**

Stratix GX devices support source-synchronous differential signaling up to 1 Gbps in DPA mode, and up to 840 Mbps in non-DPA mode. Serial data is transmitted and received along with a low-frequency clock. The PLL can multiply the incoming low-frequency clock by a factor of 1 to 10. The SERDES factor *J* can be 8 or 10 for the DPA mode, or 4, 7, 8, or 10 for all other modes. The SERDES factor does not have to equal the clock

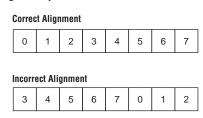

Figure 3–10. Misaligned Captured Bits

The dynamic phase selector and synchronizer align the clock and data based on the power-up of both communicating devices, and the channel to channel skew. However, the dynamic phase selector and synchronizer cannot determine the byte boundary, and the data may need to be byte-aligned. The dynamic phase aligner's data realignment circuitry shifts data bits to correct bit misalignments.

The Stratix GX circuitry contains a data-realignment feature controlled by the logic array. Stratix GX devices perform data realignment on the parallel data after the deserialization block. The data realignment can be performed per channel for more flexibility. The data alignment operation requires a state machine to recognize a specific pattern. The procedure requires the bits to be slipped on the data stream to correctly align the incoming data to the start of the byte boundary.

The DPA uses its realignment circuitry and the global clock for data realignment. Either a device pin or the logic array asserts the internal rx\_channel\_data\_align node to activate the DPA data-realignment circuitry. Switching this node from low to high activates the realignment circuitry and the data being transferred to the logic array is shifted by one bit. The data realignment block cannot be bypassed. However, if the rx\_channel\_data\_align is not turned on (through the altvlds MegaWizard Plug-In Manager), or when it is not toggled, it only acts as a register latency.

A state machine and additional logic can monitor the incoming parallel data and compare it against a known pattern. If the incoming data pattern does not match the known pattern, you can activate the rx\_channel\_data\_align node again. Repeat this process until the realigner detects the desired match between the known data pattern and incoming parallel data pattern.

| Table 4–2. TriMatrix Memory Features (Part 2 of 2) |                                                                        |                                                                                                  |                                                                                                                  |  |  |  |  |  |

|----------------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Memory Feature                                     | M512 RAM Block<br>(32 × 18 Bits)                                       | M4K RAM Block<br>(128 × 36 Bits)                                                                 | M-RAM Block<br>(4K × 144 Bits)                                                                                   |  |  |  |  |  |

| Configurations                                     | 512 ×1<br>256 × 2<br>128 × 4<br>64 × 8<br>64 × 9<br>32 × 16<br>32 × 18 | 4K × 1<br>2K × 2<br>1K × 4<br>512 × 8<br>512 × 9<br>256 × 16<br>256 × 18<br>128 × 32<br>128 × 36 | 64K × 8<br>64K × 9<br>32K × 16<br>32K × 18<br>16K × 32<br>16K × 36<br>8K × 64<br>8K × 72<br>4K × 128<br>4K × 144 |  |  |  |  |  |

*Notes to Table 4–2:*

- (1) See the DC & Switching Characteristics chapter of the Stratix GX Device Handbook, Volume 1 for maximum performance information.

- (2) The M-RAM block does not support memory initializations. However, the M-RAM block can emulate a ROM function using a dual-port RAM bock. The Stratix GX device must write to the dual-port memory once and then disable the write-enable ports afterwards.

# **Memory Modes**

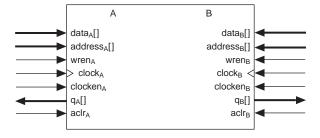

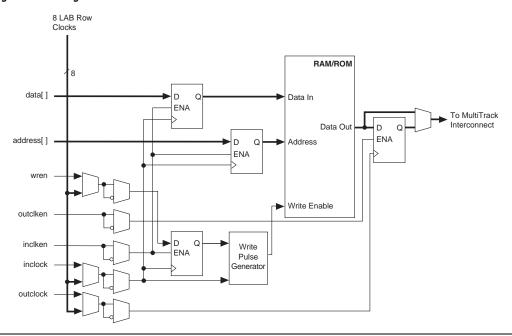

TriMatrix memory blocks include input registers that synchronize writes and output registers to pipeline designs and improve system performance. M4K and M-RAM memory blocks offer a true dual-port mode to support any combination of two-port operations: two reads, two writes, or one read and one write at two different clock frequencies. Figure 4–11 shows true dual-port memory.

Figure 4-11. True Dual-Port Memory Configuration

In addition to true dual-port memory, the memory blocks support simple dual-port and single-port RAM. Simple dual-port memory supports a simultaneous read and write and can either read old data before the write

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 4–4 and 4–5 summarize the possible M4K RAM block configurations.

| Table 4–4. M4 | Table 4–4. M4K RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |          |             |          |  |  |  |

|---------------|------------------------------------------------------------|------------|----------|----------|----------|----------|----------|-------------|----------|--|--|--|

|               |                                                            | Write Port |          |          |          |          |          |             |          |  |  |  |

| Read Port     | 4K 1                                                       | 2K × 2     | 1K ° 4   | 512 ° 8  | 256 ° 16 | 128 ° 32 | 512 ° 9  | 256 ° 18    | 128 ° 36 |  |  |  |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |  |  |  |

| 512 × 9       |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |  |  |  |

| 256 × 18      |                                                            |            |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |  |  |  |

| 128 × 36      |                                                            |            |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |  |  |  |

| Table 4–5. M4K RAM | able 4–5. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |  |  |  |  |

|--------------------|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|--|--|--|--|

| Dowl A             |                                                         | Port B   |          |          |          |          |          |  |  |  |  |

| Port A             | 4K × 1                                                  | 2K × 2   | 1K × 4   | 512 × 8  | 256 × 16 | 512 × 9  | 256 × 18 |  |  |  |  |

| 4K × 1             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |  |  |

| 2K <b>x</b> 2      | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 1K × 4             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 512 <b>x</b> 8     | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 256 × 16           | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |  |  |

| 512 <b>x</b> 9     |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |

| 256 × 18           |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |  |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

Figure 4-27. Single-Port Mode

# Digital Signal Processing Block

The most commonly used DSP functions are finite impulse response (FIR) filters, complex FIR filters, infinite impulse response (IIR) filters, fast Fourier transform (FFT) functions, direct cosine transform (DCT) functions, and correlators. All of these blocks have the same fundamental building block: the multiplier. Additionally, some applications need specialized operations such as multiply-add and multiply-accumulate operations. Stratix GX devices provide DSP blocks to meet the arithmetic requirements of these functions.

Each Stratix GX device has two columns of DSP blocks to efficiently implement DSP functions faster than LE-based implementations. Larger Stratix GX devices have more DSP blocks per column (see Table 4–12). Each DSP block can be configured to support up to:

- Eight 9 × 9-bit multipliers

- Four 18 × 18-bit multipliers

- One 36 × 36-bit multiplier

As indicated, the Stratix GX DSP block can support one 36 × 36-bit multiplier in a single DSP block. This is true for any matched sign multiplications (either unsigned by unsigned or signed by signed), but

Accumulator Feedback accum\_sload0 (2) Result A ■ overflow0 Adder/ Subtractor/ addnsub1 (2) Accumulator1 Output Selection Multiplexer Result B signa (2) Summation Output signb (2) Register Block Result C Adder/ addnsub3 (2) Subtractor/ Accumulator2 overflow1 Result D

Figure 4–33. Adder/Output Blocks Note (1)

### Notes to Figure 4-33:

accum\_sload1 (2)

(1) Adder/output block shown in Figure 4–33 is in 18 × 18-bit mode. In 9 × 9-bit mode, there are four adder/subtractor blocks and two summation blocks.

Accumulator Feedback

(2) These signals are either not registered, registered once, or registered twice to match the data path pipeline.

Fast Clock Fast Clock [1..0]

FCLK[1..0] FCLK[1..0]

FCLK[1..0] FCLK[1..0]

Figure 4–43. EP1SGX25 & EP1SGX10 Device Fast Clock Pin Connections to Fast Regional Clocks

| Table 4–27. Stratix GX Supported I/O Standards (Part 2 of 2) |                    |                                                       |                                                      |                                                           |  |  |  |  |

|--------------------------------------------------------------|--------------------|-------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|

| I/O Standard Type                                            |                    | Input Reference<br>Voltage (V <sub>REF</sub> )<br>(V) | Output Supply<br>Voltage (V <sub>CCIO</sub> )<br>(V) | Board<br>Termination<br>Voltage (V <sub>TT</sub> )<br>(V) |  |  |  |  |

| SSTL-3 class I and II                                        | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

| AGP (1× and 2×)                                              | Voltage-referenced | 1.32                                                  | 3.3                                                  | N/A                                                       |  |  |  |  |

| CTT                                                          | Voltage-referenced | 1.5                                                   | 3.3                                                  | 1.5                                                       |  |  |  |  |

### Notes to Table 4-27:

- (1) This I/O standard is only available on input and output clock pins.

- (2) This I/O standard is only available on output column clock pins.

For more information on I/O standards supported by Stratix GX devices, see the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter of the *Stratix GX Device Handbook*, *Volume 2*.

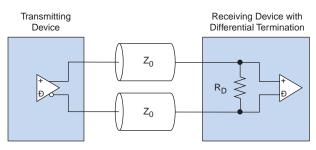

Stratix GX devices contain eight I/O banks in addition to the four enhanced PLL external clock out banks, as shown in Figure 4–69. The four I/O banks on the right and left of the device contain circuitry to support high-speed differential I/O for LVDS, LVPECL, 3.3-V PCML, and HyperTransport inputs and outputs. These banks support all I/O standards listed in Table 4–27 except PCI I/O pins or PCI-X 1.0, GTL, SSTL-18 Class II, and HSTL Class II outputs. The top and bottom I/O banks support all single-ended I/O standards. Additionally, Stratix GX devices support four enhanced PLL external clock output banks, allowing clock output capabilities such as differential support for SSTL and HSTL. Table 4–28 shows I/O standard support for each I/O bank.

Figure 4-70. LVDS Input Differential On-Chip Termination

I/O banks on the left and right side of the device support LVDS receiver (far-end) differential termination.

Table 4–29 shows the Stratix GX device differential termination support.

| Table 4–29. Differential Termination Supported by I/O Banks |                      |                                     |                    |  |  |  |

|-------------------------------------------------------------|----------------------|-------------------------------------|--------------------|--|--|--|

| Differential Termination Support                            | I/O Standard Support | Top & Bottom<br>Banks (3, 4, 7 & 8) | Left Banks (1 & 2) |  |  |  |

| Differential termination (1), (2)                           | LVDS                 |                                     | <b>✓</b>           |  |  |  |

Notes to Table 4-29:

- (1) Clock pin CLK0, CLK2, CLK9, CLK11, and pins FPLL [7..10] CLK do not support differential termination.

- (2) Differential termination is only supported for LVDS because of a 3.3-V V<sub>CCIO</sub>.

Table 4–30 shows the termination support for different pin types.

| Table 4–30. Differential Termination Support Across Pin Types |                |  |  |  |  |

|---------------------------------------------------------------|----------------|--|--|--|--|

| Pin Type                                                      | R <sub>D</sub> |  |  |  |  |

| Top and bottom I/O banks (3, 4, 7, and 8)                     |                |  |  |  |  |

| DIFFIO_RX[]                                                   | <b>✓</b>       |  |  |  |  |

| CLK[0,2,9,11],CLK[4-7],CLK[12-15]                             |                |  |  |  |  |

| CLK[1,3,8,10]                                                 | <b>✓</b>       |  |  |  |  |

| FCLK                                                          |                |  |  |  |  |

| FPLL[710]CLK                                                  |                |  |  |  |  |

The differential on-chip resistance at the receiver input buffer is 118  $\Omega\!\pm\!20$  %.

| Table 6–7. S                       | Table 6–7. Stratix GX Transceiver Block AC Specification (Part 6 of 7) |                                  |        |                                                     |      |     |                                        |     |     |      |     |

|------------------------------------|------------------------------------------------------------------------|----------------------------------|--------|-----------------------------------------------------|------|-----|----------------------------------------|-----|-----|------|-----|

| Symbol /<br>Description            | Conditions                                                             | -5 Commercial<br>Speed Grade (1) |        | -6 Commercial &<br>Industrial Speed<br>Grade<br>(1) |      |     | -7 Commercial & Industrial Speed Grade |     |     | Unit |     |

|                                    |                                                                        | Min                              | Тур    | Max                                                 | Min  | Тур | Max                                    | Min | Тур | Max  |     |

| XAUI Transmi                       | tter Jitter using 8B,                                                  | /10B E                           | ncoded | CJPAT                                               | Note | (9) |                                        |     |     |      |     |

| Deterministic jitter               | 3.125 Gbps<br>Pre-emphasis = 0                                         |                                  |        | 0.15                                                |      |     | 0.15                                   |     |     | N/A  | UI  |

| Total jitter                       | V <sub>OD</sub> = 1,200 mV                                             |                                  |        | 0.32                                                |      |     | 0.32                                   |     |     | N/A  | UI  |

| Jitter transfer bandwidth (10)     | Low bandwidth<br>setting at<br>3.125 Gbps                              |                                  | 3      |                                                     |      | 3   |                                        |     |     | N/A  | MHz |

|                                    | High bandwidth setting at 3.125 Gbps                                   |                                  | 4.7    |                                                     |      | 4.7 |                                        |     |     | N/A  | MHz |

|                                    | Low bandwidth setting at 2.5 Gbps                                      |                                  | 3.2    |                                                     |      | 3.2 |                                        |     |     | 3.2  | MHz |

|                                    | High bandwidth setting at 2.5 Gbps                                     |                                  | 4.3    |                                                     |      | 4.3 |                                        |     |     | 4.3  | MHz |

| Output t <sub>RISE</sub>           | 20% to 80%                                                             | 60                               |        | 130                                                 | 60   |     | 130                                    | 60  |     | 130  | ps  |

| Output t <sub>FALL</sub>           | 80% to 20%                                                             | 60                               |        | 130                                                 | 60   |     | 130                                    | 60  |     | 130  | ps  |

| Transmit                           | Single width                                                           | 3                                |        | 8                                                   | 3    |     | 8                                      | 3   |     | 8    | (3) |

| latency (11)                       | Double width                                                           | 3                                |        | 7                                                   | 3    |     | 7                                      | 3   |     | 7    | (3) |

| Intra<br>differential<br>pair skew |                                                                        |                                  |        | 10                                                  |      |     | 10                                     |     |     | 10   | ps  |

| Channel to channel skew            | Within a single quadrant                                               |                                  |        | 50                                                  |      |     | 50                                     |     |     | 50   | ps  |

| Table 6–26. SSTL-3 Class II Specifications (Part 2 of 2) |                           |                                |                       |         |                       |       |  |  |  |

|----------------------------------------------------------|---------------------------|--------------------------------|-----------------------|---------|-----------------------|-------|--|--|--|

| Symbol                                                   | Parameter                 | Conditions                     | Minimum               | Typical | Maximum               | Units |  |  |  |

| V <sub>IL</sub>                                          | Low-level input voltage   |                                | -0.3                  |         | $V_{REF} - 0.2$       | V     |  |  |  |

| V <sub>OH</sub>                                          | High-level output voltage | $I_{OH} = -16 \text{ mA } (1)$ | V <sub>TT</sub> + 0.8 |         |                       | V     |  |  |  |

| V <sub>OL</sub>                                          | Low-level output voltage  | I <sub>OL</sub> = 16 mA (1)    |                       |         | V <sub>TT</sub> – 0.8 | V     |  |  |  |

| Table 6–27. 3.3-V AGP 2× Specifications |                              |                             |                             |         |                             |       |  |  |

|-----------------------------------------|------------------------------|-----------------------------|-----------------------------|---------|-----------------------------|-------|--|--|

| Symbol                                  | Parameter                    | Conditions                  | Minimum                     | Typical | Maximum                     | Units |  |  |

| V <sub>CCIO</sub>                       | Output supply voltage        |                             | 3.15                        | 3.3     | 3.45                        | ٧     |  |  |

| $V_{REF}$                               | Reference voltage            |                             | 0.39 ×<br>V <sub>CCIO</sub> |         | 0.41 ×<br>V <sub>CCIO</sub> | V     |  |  |

| V <sub>IH</sub>                         | High-level input voltage (2) |                             | 0.5 × V <sub>CCIO</sub>     |         | V <sub>CCIO</sub> + 0.5     | V     |  |  |

| V <sub>IL</sub>                         | Low-level input voltage (2)  |                             |                             |         | $0.3 \times V_{CCIO}$       | V     |  |  |

| V <sub>OH</sub>                         | High-level output voltage    | $I_{OUT} = -0.5 \text{ mA}$ | 0.9 × V <sub>CCIO</sub>     |         | 3.6                         | V     |  |  |

| V <sub>OL</sub>                         | Low-level output voltage     | I <sub>OUT</sub> = 1.5 mA   |                             |         | 0.1 × V <sub>CCIO</sub>     | ٧     |  |  |

| Table 6–28.       | Table 6–28. 3.3-V AGP 1× Specifications |                             |                         |         |                              |       |  |  |  |

|-------------------|-----------------------------------------|-----------------------------|-------------------------|---------|------------------------------|-------|--|--|--|

| Symbol            | Parameter                               | Conditions                  | Minimum                 | Typical | Maximum                      | Units |  |  |  |

| V <sub>CCIO</sub> | Output supply voltage                   |                             | 3.15                    | 3.3     | 3.45                         | V     |  |  |  |

| V <sub>IH</sub>   | High-level input voltage (2)            |                             | 0.5 × V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5      | V     |  |  |  |

| V <sub>IL</sub>   | Low-level input voltage (2)             |                             |                         |         | $0.3 \times V_{\text{CCIO}}$ | V     |  |  |  |

| V <sub>OH</sub>   | High-level output voltage               | $I_{OUT} = -0.5 \text{ mA}$ | 0.9 × V <sub>CCIO</sub> |         | 3.6                          | V     |  |  |  |

| V <sub>OL</sub>   | Low-level output voltage                | I <sub>OUT</sub> = 1.5 mA   |                         |         | 0.1 × V <sub>CCIO</sub>      | V     |  |  |  |

| Table 6–29. 1.5-V HSTL Class I Specifications (Part 1 of 2) |                             |            |                        |         |                        |       |  |  |

|-------------------------------------------------------------|-----------------------------|------------|------------------------|---------|------------------------|-------|--|--|

| Symbol                                                      | Parameter                   | Conditions | Minimum                | Typical | Maximum                | Units |  |  |

| V <sub>CCIO</sub>                                           | Output supply voltage       |            | 1.4                    | 1.5     | 1.6                    | V     |  |  |

| V <sub>REF</sub>                                            | Input reference voltage     |            | 0.68                   | 0.75    | 0.9                    | V     |  |  |

| V <sub>TT</sub>                                             | Termination voltage         |            | 0.7                    | 0.75    | 0.8                    | V     |  |  |

| V <sub>IH</sub> (DC)                                        | DC high-level input voltage |            | V <sub>REF</sub> + 0.1 |         |                        | V     |  |  |

| V <sub>IL</sub> (DC)                                        | DC low-level input voltage  |            | -0.3                   |         | V <sub>REF</sub> - 0.1 | V     |  |  |

| V <sub>IH</sub> (AC)                                        | AC high-level input voltage |            | V <sub>REF</sub> + 0.2 |         |                        | V     |  |  |

| V <sub>IL</sub> (AC)                                        | AC low-level input voltage  |            |                        |         | V <sub>REF</sub> - 0.2 | V     |  |  |

| Table 6–48. M4K Block Internal Timing Microparameters (Part 2 of 2) |                |       |                |       |                |       |      |  |  |

|---------------------------------------------------------------------|----------------|-------|----------------|-------|----------------|-------|------|--|--|

| 0                                                                   | -5 Speed Grade |       | -6 Speed Grade |       | -7 Speed Grade |       | Hait |  |  |

| Symbol                                                              | Min            | Max   | Min            | Max   | Min            | Max   | Unit |  |  |

| t <sub>M4KDATACO1</sub>                                             |                | 571   |                | 635   |                | 729   | ps   |  |  |

| t <sub>M4KDATACO2</sub>                                             |                | 3,984 |                | 4,507 |                | 5,182 | ps   |  |  |

| t <sub>M4KCLKHL</sub>                                               | 150            |       | 167            |       | 192            |       | ps   |  |  |

| t <sub>M4KCLR</sub>                                                 | 170            |       | 189            |       | 255            |       | ps   |  |  |

| Table 6–49. M-RAM Block Internal Timing Microparameters |     |       |     |       |     |         |      |  |  |

|---------------------------------------------------------|-----|-------|-----|-------|-----|---------|------|--|--|

| O. mahal                                                | -5  |       | -   | 6     | -   | II.m.:A |      |  |  |

| Symbol                                                  | Min | Max   | Min | Max   | Min | Max     | Unit |  |  |

| t <sub>MRAMRC</sub>                                     |     | 4,364 |     | 4,838 |     | 5,562   | ps   |  |  |

| t <sub>MRAMWC</sub>                                     |     | 3,654 |     | 4,127 |     | 4,746   | ps   |  |  |

| t <sub>MRAMWERESU</sub>                                 | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMWERH</sub>                                   | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMDATASU</sub>                                 | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMDATAH</sub>                                  | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMWADDRASU</sub>                               | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMWADDRH</sub>                                 | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMRADDRASU</sub>                               | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMRADDRH</sub>                                 | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMDATABSU</sub>                                | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMDATABH</sub>                                 | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMADDRBSU</sub>                                | 25  |       | 25  |       | 28  |         | ps   |  |  |

| t <sub>MRAMADDRBH</sub>                                 | 18  |       | 20  |       | 23  |         | ps   |  |  |

| t <sub>MRAMDATACO1</sub>                                |     | 1,038 |     | 1,053 |     | 1,210   | ps   |  |  |

| t <sub>MRAMDATACO2</sub>                                |     | 4,362 |     | 4,939 |     | 5,678   | ps   |  |  |

| t <sub>MRAMCLKHL</sub>                                  | 270 |       | 300 |       | 345 |         | ps   |  |  |

| t <sub>MRAMCLR</sub>                                    | 135 |       | 150 |       | 172 |         | ps   |  |  |

| Table 6–74. Stratix GX I/O Standard Output Delay Adders for Fast Slew Rate on Column Pins (Part 2 of 2) |                |      |                |      |                |      |        |  |

|---------------------------------------------------------------------------------------------------------|----------------|------|----------------|------|----------------|------|--------|--|

| Standard                                                                                                | -5 Speed Grade |      | -6 Speed Grade |      | -7 Speed Grade |      |        |  |

|                                                                                                         | Min            | Max  | Min            | Max  | Min            | Max  | - Unit |  |

| GTL+                                                                                                    |                | -110 |                | -115 |                | -133 | ps     |  |

| 3.3-V PCI                                                                                               |                | -230 |                | -241 |                | -277 | ps     |  |

| 3.3-V PCI-X 1.0                                                                                         |                | -230 |                | -241 |                | -277 | ps     |  |

| Compact PCI                                                                                             |                | -230 |                | -241 |                | -277 | ps     |  |

| AGP 1×                                                                                                  |                | -30  |                | -31  |                | -36  | ps     |  |

| AGP 2×                                                                                                  |                | -30  |                | -31  |                | -36  | ps     |  |

| CTT                                                                                                     |                | 50   |                | 53   |                | 61   | ps     |  |

| SSTL-3 class I                                                                                          |                | 90   |                | 95   |                | 109  | ps     |  |

| SSTL-3 class II                                                                                         |                | -50  |                | -52  |                | -60  | ps     |  |

| SSTL-2 class I                                                                                          |                | 100  |                | 105  |                | 120  | ps     |  |

| SSTL-2 class II                                                                                         |                | 20   |                | 21   |                | 24   | ps     |  |

| SSTL-18 class I                                                                                         |                | 230  |                | 242  |                | 278  | ps     |  |

| SSTL-18 class II                                                                                        |                | 0    |                | 0    |                | 0    | ps     |  |

| 1.5-V HSTL class I                                                                                      |                | 380  |                | 399  |                | 459  | ps     |  |

| 1.5-V HSTL class II                                                                                     |                | 190  |                | 200  |                | 230  | ps     |  |

| 1.8-V HSTL class I                                                                                      |                | 380  |                | 399  |                | 459  | ps     |  |

| 1.8-V HSTL class II                                                                                     |                | 390  |                | 410  |                | 471  | ps     |  |

| Table 6–75. Stratix GX I/O Standard Output Delay Adders for Fast Slew Rate on Row Pins (Part 1 of 2) |       |                |     |                |     |                |     |        |  |

|------------------------------------------------------------------------------------------------------|-------|----------------|-----|----------------|-----|----------------|-----|--------|--|

| Standard -                                                                                           |       | -5 Speed Grade |     | -6 Speed Grade |     | -7 Speed Grade |     | 11-24  |  |

|                                                                                                      |       | Min            | Max | Min            | Max | Min            | Max | - Unit |  |

| LVCMOS                                                                                               | 2 mA  |                | 570 |                | 599 |                | 689 | ps     |  |

|                                                                                                      | 4 mA  |                | 570 |                | 599 |                | 689 | ps     |  |

|                                                                                                      | 8 mA  |                | 350 |                | 368 |                | 423 | ps     |  |

|                                                                                                      | 12 mA |                | 130 |                | 137 |                | 157 | ps     |  |

|                                                                                                      | 24 mA |                | 0   |                | 0   |                | 0   | ps     |  |

| 3.3-V LVTTL                                                                                          | 4 mA  |                | 570 |                | 599 |                | 689 | ps     |  |

|                                                                                                      | 8 mA  |                | 350 |                | 368 |                | 423 | ps     |  |

|                                                                                                      | 12 mA |                | 130 |                | 137 |                | 157 | ps     |  |

|                                                                                                      | 16 mA |                | 70  |                | 74  |                | 85  | ps     |  |

|                                                                                                      | 24 mA |                | 0   |                | 0   |                | 0   | ps     |  |

Table 6–91 describes the Stratix GX device fast PLL specifications.

| Table 6–91. Fast PLL Specifications for -5 & -6 Speed Grade Devices |                                                            |           |                                                            |              |  |  |  |

|---------------------------------------------------------------------|------------------------------------------------------------|-----------|------------------------------------------------------------|--------------|--|--|--|

| Symbol                                                              | Parameter                                                  | Min       | Max                                                        | Unit         |  |  |  |

| f <sub>IN</sub>                                                     | CLKIN frequency (for $m = 1$ ) (1)                         | 300       | 717                                                        | MHz          |  |  |  |

|                                                                     | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 1,000/ <i>m</i>                                            | MHz          |  |  |  |

|                                                                     | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 1,000/ <i>m</i>                                            | MHz          |  |  |  |

| f <sub>OUT</sub>                                                    | Output frequency for internal global or regional clock (2) | 9.4       | 420                                                        | MHz          |  |  |  |

| f <sub>OUT_EXT</sub>                                                | Output frequency for external clock                        | 9.375     | 717                                                        | MHz          |  |  |  |

| $f_{VCO}$                                                           | VCO operating frequency                                    | 300       | 1,000                                                      | MHz          |  |  |  |

| t <sub>INDUTY</sub>                                                 | CLKIN duty cycle                                           | 40        | 60                                                         | %            |  |  |  |

| t <sub>INJITTER</sub>                                               | Period jitter for CLKIN pin                                |           | ±200                                                       | ps           |  |  |  |

| t <sub>DUTY</sub>                                                   | Duty cycle for DFFIO 1× CLKOUT pin (3)                     | 45        | 55                                                         | %            |  |  |  |

| t <sub>JITTER</sub>                                                 | Period jitter for DIFFIO clock out (3)                     |           | ±80                                                        | ps           |  |  |  |

|                                                                     | Period jitter for internal global or regional clock        |           | ±100 ps for >200-MHz outclk<br>±20 mUI for <200-MHz outclk | ps or<br>mUI |  |  |  |

| t <sub>LOCK</sub>                                                   | Time required for PLL to acquire lock                      | 10        | 100                                                        | μs           |  |  |  |

| m                                                                   | Multiplication factors for <i>m</i> counter (3)            | 1         | 32                                                         | Integer      |  |  |  |

| <i>l</i> 0, <i>l</i> 1, <i>g</i> 0                                  | Multiplication factors for I0, I1, and g0 counter (4), (5) | 1         | 32                                                         | Integer      |  |  |  |

| t <sub>ARESET</sub>                                                 | Minimum pulse width on areset signal                       | 10        |                                                            | ns           |  |  |  |

| Symbol                                       | Parameter                                                  | Min       | Max           | Unit |

|----------------------------------------------|------------------------------------------------------------|-----------|---------------|------|

| $f_{IN}$ CLKIN frequency (for $m = 1$ ) (1), |                                                            | 300       | 640           | MHz  |

|                                              | CLKIN frequency (for $m = 2$ to 19)                        | 300/<br>m | 700/ <i>m</i> | MHz  |

|                                              | CLKIN frequency (for $m = 20$ to 32)                       | 10        | 700/ <i>m</i> | MHz  |

| f <sub>OUT</sub>                             | Output frequency for internal global or regional clock (2) | 9.375     | 420           | MHz  |

| f <sub>OUT_EXT</sub>                         | Output frequency for external clock                        | 9.4       | 500           | MHz  |

| f <sub>VCO</sub>                             | VCO operating frequency                                    | 300       | 700           | MHz  |

| t <sub>INDUTY</sub>                          | CLKIN duty cycle                                           | 40        | 60            | %    |

| t <sub>INJITTER</sub>                        | Period jitter for CLKIN pin                                |           | ±200          | ps   |