Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 4125                                                        |

| Number of Logic Elements/Cells | 41250                                                       |

| Total RAM Bits                 | 3423744                                                     |

| Number of I/O                  | 624                                                         |

| Number of Gates                | -                                                           |

| Voltage - Supply               | 1.425V ~ 1.575V                                             |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx40df1020c5 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## $\textbf{Revision History} \qquad \text{The table below shows the revision history for Chapters 1 through 7}.$

| Chapter(s) | Date / Version         | Changes Made                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                                                                                                                           |

|------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 2          | June 2006, v1.1        | <ul> <li>Updated "Serial Loopback" section.</li> <li>Updated Figures 2–1 through 2–3.</li> <li>Updated Figure 2–13.</li> <li>Updated Figures 2–26 and 2–27.</li> </ul>                                                                                                |                                                                                                                                                                                                                                                                                                                                                    |

|            | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 3          | August 2005,<br>v1.1   | Added Note (3) to Figure 3-7.                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                    |

| 4          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 5          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 6          | June 2006, v1.2        | <ul> <li>Updated "Operating Conditions" section.</li> <li>Updated Table 6-4.</li> <li>Updated note 3 in Table 6-6.</li> <li>Added note 12 in Table 6-7.</li> <li>Updated Figure 6-1.</li> <li>Added Figure 6-2.</li> <li>Updated Tables 6-13 through 6-16.</li> </ul> | <ul> <li>Changed V<sub>OD</sub> to V<sub>ID</sub> for receiver input voltage and refclkb input voltage in Table 6–4.</li> <li>Changed value for undershoot during transition from -0.5 V to -2.0 V in note 3 of Table 6–6.</li> <li>Changed value of V<sub>OCM</sub> from mV to V in Table 6–15.</li> <li>Changed unit value of W to Ω.</li> </ul> |

|            | August 2005,<br>v1.1   | Updated Tables 6-7 and 6-50.                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |

| 7          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

Section I–2 Altera Corporation

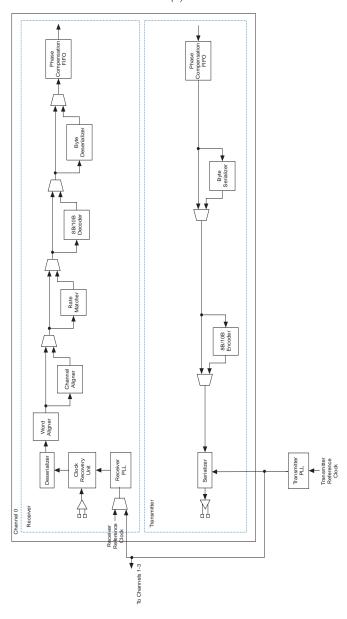

Figure 2–2. Stratix GX Transceiver Channel Note (1)

Note to Figure 2–2:

(1) There are four transceiver channels in a transceiver block.

| Table 2–5. Receiver PLL & CRU Adjustable Parameters (Part 2 of 2) |                                               |  |  |

|-------------------------------------------------------------------|-----------------------------------------------|--|--|

| Multiplication factor (W)                                         | 2, 4, 5, 8, 10, 16, or 20 <i>(1)</i>          |  |  |

| PPM detector                                                      | 125, 250, 500, 1,000                          |  |  |

| Bandwidth                                                         | Low, medium, high                             |  |  |

| Run length detector                                               | 10-bit or 20-bit mode: 5 to 160 in steps of 5 |  |  |

|                                                                   | 8-bit or 16-bit mode: 4 to 128 in steps of 4  |  |  |

Note to Table 2-5:

(1) Multiplication factors 2, 4, and 5 can only be achieved with the use of the predivider on the REFCLKB port or if the CRU is trained with the low speed clock from the transmitter PLL.

The CRU has a built-in switchover circuit to select whether the voltage-controlled oscillator of the PLL is trained by the reference clock or the data. The optional port rx\_freqlocked monitors when the CRU is in locked to data mode.

In the automatic mode, the following conditions must be met for the CRU to switch from locked to reference to locked to data mode:

- The CRU PLL is within the prescribed PPM frequency threshold setting (125 PPM, 250 PPM, 500 PPM, 1,000 PPM) of the CRU reference clock.

- The reference clock and CRU PLL output are phase matched (phases are within .08 UI).

The automatic switchover circuit can be overridden by using the optional ports rx\_lockedtorefclk and rx\_locktodata. Table 2–6 shows the possible combinations of these two signals.

| Table 2–6. Possible Combinations of rx_lockedtorefclk & rx_locktodata |                   |                    |  |  |

|-----------------------------------------------------------------------|-------------------|--------------------|--|--|

| rx_locktodata                                                         | rx_lockedtorefclk | VCO (lock to mode) |  |  |

| 0                                                                     | 0                 | Auto               |  |  |

| 0                                                                     | 1                 | Reference CLK      |  |  |

| 1                                                                     | х                 | DATA               |  |  |

If the rx\_lockedtorefclk and rx\_locktodata ports are not used, the default is auto mode.

Figure 2-16. Word Aligner in 16-Bit Mode

In the 16-bit mode, the word aligner and pattern detector automatically aligns and detects a user-defined 16-bit alignment pattern. This pattern can be in the format of A1A2 or A1A1A2A2 (for the SONET protocol). The re-alignment of the byte boundary can be done via a user-controlled port. The 16-bit mode supports only the 8-bit data path in a single-width or double-width mode.

The 16-bit mode is available only for the Custom mode and SONET mode. The A1A1A2A2 word alignment pattern option is available only for the SONET mode and cannot be used in the Custom mode.

Figure 2–17 shows the word aligner in 10-bit mode.

#### XAUI Mode

In XAUI mode, the rate matcher adheres to clause 48 of the IEEE 802.3ae specification for clock rate compensation. The rate matcher performs clock compensation on columns of /R/ (/K28.0/), denoted by //R//. An //R// is added or deleted automatically based on the number of words in the FIFO buffer.

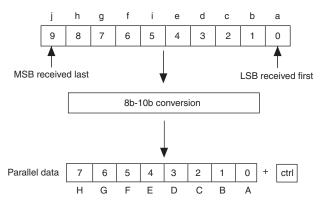

#### 8B/10B Decoder

The 8B/10B decoder converts the 10-bit encoded code group into 8-bit data and 1 control bit. The 8B/10B decoder can be bypassed. The following is a diagram of the conversion from a 10-bit encoded code group into 8-bit data + 1-bit control.

Figure 2-20. 8B/10B Decoder Conversion

There are two optional error status ports available in the 8B/10B decoder, rx\_errdetect and rx\_disperr. Table 2–7 shows the values of the ports from a given error. These status signals are aligned with the code group in which the error occurred.

| Table 2–7. Error Signal Values          |      |      |  |  |

|-----------------------------------------|------|------|--|--|

| Types of Errors rx_errdetect rx_disperr |      |      |  |  |

| No errors                               | 1'b0 | 1'b0 |  |  |

| Invalid code groups                     | 1'b1 | 1'b0 |  |  |

| Disparity errors                        | 1'b1 | 1'b1 |  |  |

The DPA data-realignment circuitry allows further realignment beyond what the *J* multiplication factor allows. You can set the *J* multiplication factor to be 8 or 10. However, because data must be continuously clocked in on each low-speed clock cycle, the upcoming bit to be realigned and previous n-1 bits of data are selected each time the data realignment logic's counter passes n-1. At this point the data is selected entirely from bit-slip register 3 (see Figure 3–11) as the counter is reset to 0. The logic array receives a new valid byte of data on the next divided low speed clock cycle. Figure 3–11 shows the data realignment logic output selection from data in the data realignment register 2 and data realignment register 3 based on its current counter value upon continuous request of data slipping from the logic array.

Bit Slip Bit Slin Bit Slin Bit Slin Bit Slip Bit Slin Bit Slip Bit Slin Bit Slip Bit Slip Register 2 Register 3 D19 D9 D29 D19 D99 D89 D119 D99 D119 D109 D18 D8 D28 D18 D118 D118 D108 D18 D98 D98 D97 D17 D7 D27 D17 D97 D87 D117 D117 D107 D16 D6 D26 D16 D96 D86 D116 D96 D116 D106 One bit Seven more One more One more slipped bits slipped bit slipped bit slipped D15 D5 D25 D15 D95 D85 D115 D95 D115 D125 D14 D4 D24 D14 D94 D84 D114 D94 D114 D124 D13 D3 D23 D83 D113 D113 D13 D93 D93 D12 D2 D22 D12 D92 D82 D112 D92 D112 D102 D111 D11 D21 D11 D91 D81 D91 D111 D10 D0 D20 D10 D90 D80 D110 D90 D110 D100 Zero bits slipped One bit slipped. Eight bits slipped. Nine bits slipped. 10 bits slipped. Counter = 0 Counter = 1 Counter = 8 Counter = 9 Counter = 0 D10 is the upcoming D21 is the upcoming D98 is the upcoming D119 is the upcoming Real data will resume bit to be slipped. bit to be slipped. on the next byte.

Figure 3–11. DPA Data Realigner

Use the rx\_channel\_data\_align signal within the device to activate the data realigner. You can use internal logic or an external pin to control the rx channel data align signal. To ensure the rising edge of the rx channel data align signal is latched into the control logic, the rx channel data align signal should stay high for at least two lowfrequency clock cycles.

bit to be slipped.

bit to be slipped.

### 4. Stratix GX Architecture

SGX51004-1.0

### Logic Array Blocks

Each LAB consists of 10 LEs, LE carry chains, LAB control signals, local interconnect, LUT chain, and register chain connection lines. The local interconnect transfers signals between LEs in the same LAB. LUT chain connections transfer the output of one LE's LUT to the adjacent LE for fast sequential LUT connections within the same LAB. Register chain connections transfer the output of one LE's register to the adjacent LE's register within an LAB. The Quartus® II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of local, LUT chain, and register chain connections for performance and area efficiency. Figure 4–1 shows the Stratix® GX LAB.

Row Interconnects of Variable Speed & Length \* ◂ 7 interconnect from Direct link adiacent block interconnect from adjacent block Direct link Direct link interconnect to interconnect to adjacent block adjacent block Local Interconnect Interconnect is Driven from Either Side by Variable Speed & Length Columns & LABs. & from Above by Row

Figure 4-1. Stratix GX LAB Structure

#### LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB local interconnect is driven by column and row interconnects and LE outputs within the same LAB. Neighboring LABs, M512 RAM blocks,

for accumulator functions. Another portion of the LUT generates carry-out bits. An LAB-wide carry in bit selects which chain to use for the addition of given inputs. The carry-in signal for each chain, carry-in0 or carry-in1, selects the carry-out to carry forward to the carry-in signal of the next-higher-order bit. The final carry-out signal is routed to an LE, where it is fed to local, row, or column interconnects.

The Quartus II Compiler automatically creates carry chain logic during design processing, or you can create it manually during design entry. Parameterized functions such as LPM functions automatically take advantage of carry chains for the appropriate functions.

The Quartus II Compiler creates carry chains longer than 10 LEs by linking LABs together automatically. For enhanced fitting, a long carry chain runs vertically allowing fast horizontal connections to  $\operatorname{TriMatrix}^{\text{TM}}$  memory and DSP blocks. A carry chain can continue as far as a full column.

The memory address depths and output widths can be configured as  $4,096 \times 1, 2,048 \times 2, 1,024 \times 4,512 \times 8$  (or  $512 \times 9$  bits),  $256 \times 16$  (or  $256 \times 18$  bits), and  $128 \times 32$  (or  $128 \times 36$  bits). The  $128 \times 32$ - or 36-bit configuration is not available in the true dual-port mode. Mixed-width configurations are also possible, allowing different read and write widths. Tables 4–4 and 4–5 summarize the possible M4K RAM block configurations.

| Table 4–4. M4 | Table 4–4. M4K RAM Block Configurations (Simple Dual-Port) |          |          |          |          |          |          |             |          |

|---------------|------------------------------------------------------------|----------|----------|----------|----------|----------|----------|-------------|----------|

| Dood Dout     | Write Port                                                 |          |          |          |          |          |          |             |          |

| Read Port     | 4K 1                                                       | 2K × 2   | 1K ° 4   | 512 ° 8  | 256 ° 16 | 128 ° 32 | 512 ° 9  | 256 ° 18    | 128 ° 36 |

| 4K × 1        | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 2K × 2        | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 1K × 4        | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 8       | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 256 × 16      | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 128 × 32      | <b>✓</b>                                                   | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |             |          |

| 512 × 9       |                                                            |          |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 256 × 18      |                                                            |          |          |          |          |          | <b>✓</b> | <b>✓</b>    | <b>✓</b> |

| 128 × 36      |                                                            |          |          |          |          |          | <b>✓</b> | <b>&gt;</b> | <b>✓</b> |

| Table 4–5. M4K RAM | able 4–5. M4K RAM Block Configurations (True Dual-Port) |          |          |          |          |          |          |  |  |

|--------------------|---------------------------------------------------------|----------|----------|----------|----------|----------|----------|--|--|

| Dowl A             |                                                         | Port B   |          |          |          |          |          |  |  |

| Port A             | 4K × 1                                                  | 2K × 2   | 1K × 4   | 256 × 16 | 512 × 9  | 256 × 18 |          |  |  |

| 4K × 1             | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |  |

| 2K <b>x</b> 2      | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |

| 1K × 4             | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |

| 512 <b>x</b> 8     | ✓                                                       | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |

| 256 × 16           | <b>✓</b>                                                | <b>✓</b> | <b>✓</b> | ✓        | <b>✓</b> |          |          |  |  |

| 512 <b>x</b> 9     |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |

| 256 × 18           |                                                         |          |          |          |          | <b>✓</b> | <b>✓</b> |  |  |

When the M4K RAM block is configured as a shift register block, you can create a shift register up to 4,608 bits ( $w \times m \times n$ ).

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as 64K × 8 (or 64K × 9 bits), 32K × 16 (or 32K × 18 bits), 16K × 32 (or 16K × 36 bits), 8K × 64 (or 8K × 72 bits), and 4K × 128 (or 4K × 144 bits). The 4K × 128 configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 4–7 and 4–8 summarize the possible M-RAM block configurations:

| Table 4–7. M-RAM Block Configurations (Simple Dual-Port) |            |          |          |          |          |  |  |  |

|----------------------------------------------------------|------------|----------|----------|----------|----------|--|--|--|

|                                                          | Write Port |          |          |          |          |  |  |  |

| Read Port                                                | 64K × 9    | 32K × 18 | 16K × 36 | 8K × 72  | 4K × 144 |  |  |  |

| 64K × 9                                                  | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |  |  |  |

| 32K × 18                                                 | <b>✓</b>   | ✓        | ✓        | ✓        |          |  |  |  |

| 16K × 36                                                 | ✓          | ✓        | ✓        | <b>✓</b> |          |  |  |  |

| 8K × 72                                                  | ✓          | ✓        | <b>✓</b> | <b>✓</b> |          |  |  |  |

| 4K × 144                                                 |            |          |          |          | ✓        |  |  |  |

| Table 4–10. M-RAM Combined Byte | <b>Table 4–10. M-RAM Combined Byte Selection for ×144 Mode</b> Notes (1), (2) |  |  |  |  |

|---------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

| byteena[150]                    | datain ×144                                                                   |  |  |  |  |

| [0] = 1                         | [80]                                                                          |  |  |  |  |

| [1] = 1                         | [179]                                                                         |  |  |  |  |

| [2] = 1                         | [2618]                                                                        |  |  |  |  |

| [3] = 1                         | [3527]                                                                        |  |  |  |  |

| [4] = 1                         | [4436]                                                                        |  |  |  |  |

| [5] = 1                         | [5345]                                                                        |  |  |  |  |

| [6] = 1                         | [6254]                                                                        |  |  |  |  |

| [7] = 1                         | [7163]                                                                        |  |  |  |  |

| [8] = 1                         | [8072]                                                                        |  |  |  |  |

| [9] = 1                         | [8981]                                                                        |  |  |  |  |

| [10] = 1                        | [9890]                                                                        |  |  |  |  |

| [11] = 1                        | [10799]                                                                       |  |  |  |  |

| [12] = 1                        | [116108]                                                                      |  |  |  |  |

| [13] = 1                        | [125117]                                                                      |  |  |  |  |

| [14] = 1                        | [134126]                                                                      |  |  |  |  |

| [15] = 1                        | [143135]                                                                      |  |  |  |  |

#### Notes to Tables 4-9 and 4-10:

- (1) Any combination of byte enables is possible.

- (2) Byte enables can be used in the same manner with 8-bit words, that is, in  $\times 16$ ,  $\times 32$ ,  $\times 64$ , and  $\times 128$  modes.

Similar to all RAM blocks, M-RAM blocks can have different clocks on their inputs and outputs. All input registers—renwe, datain, address, and byte enable registers—are clocked together from either of the two clocks feeding the block. The output register can be bypassed. The eight labclk signals or local interconnect can drive the control signals for the A and B ports of the M-RAM block. LEs can also control the clock\_a, clock\_b, renwe\_a, renwe\_b, clr\_a, clr\_b, clocken\_a, and clocken\_b signals as shown in Figure 4–18.

| Table 4–18. Stratix GX Enhanced PLL & Fast PLL Features (Part 2 of 2) Notes (1)–(8) |                                                                 |     |  |  |

|-------------------------------------------------------------------------------------|-----------------------------------------------------------------|-----|--|--|

| Feature                                                                             | Fast PLL                                                        |     |  |  |

| Number of external clock outputs                                                    | Four differential/eight singled-ended or one single-ended $(6)$ | (7) |  |  |

| Number of feedback clock inputs                                                     | 4 (8)                                                           |     |  |  |

#### Notes to Table 4-18:

- (1) The maximum count value is 1024, with a 50% duty cycle setting on the counter. The maximum count value for any other duty cycle setting is 512.

- (2) For fast PLLs, *m* and post-scale counters range from 1 to 32.

- (3) The smallest phase shift is determined by the VCO period divided by 8.

- (4) For degree increments, Stratix GX devices can shift all output frequencies in increments of at least 45°. Smaller degree increments are possible depending on the frequency and divide parameters.

- (5) PLLs 7 and 8 have two output ports per PLL. PLLs 1 and 2 have three output ports per PLL.

- (6) Every Stratix GX device has two enhanced PLLs (PLLs 5 and 6) with eight single-ended or four differential outputs each. Two additional enhanced PLLs (PLLs 11 and 12) in EP1SGX40 devices each have one single-ended output.

- (7) Fast PLLs can drive to any I/O pin as an external clock. For high-speed differential I/O pins, the device uses a data channel to generate txclkout.

- (8) Every Stratix GX device has two enhanced PLLs with one single-ended or differential external feedback input per PLL.

Figure 4–48 shows a top-level diagram of the Stratix GX device and the PLL floorplan.

pair of output pins (four pins total) has dedicated VCC and GND pins to reduce the output clock's overall jitter by providing improved isolation from switching I/O pins.

For PLLs 5 and 6, each pin of a single-ended output pair can either be in phase or 180° out of phase. The clock output pin pairs support the same I/O standards as standard output pins (in the top and bottom banks) as well as LVDS, LVPECL, 3.3-V PCML, HyperTransport technology, differential HSTL, and differential SSTL. Table 4–19 shows which I/O standards the enhanced PLL clock pins support. When in single-ended or differential mode, the two outputs operate off the same power supply. Both outputs use the same standards in single-ended mode to maintain performance. You can also use the external clock output pins as user output pins if external enhanced PLL clocking is not needed.

| I/O Otomdová              |          | Output   |           |        |

|---------------------------|----------|----------|-----------|--------|

| I/O Standard              | INCLK    | FBIN     | PLLENABLE | EXTCLK |

| LVTTL                     | <b>✓</b> | ✓        | <b>✓</b>  | ✓      |

| LVCMOS                    | ✓        | ✓        | ✓         | ✓      |

| 2.5 V                     | ✓        | ✓        |           | ✓      |

| 1.8 V                     | ✓        | ✓        |           | ✓      |

| 1.5 V                     | ✓        | <b>✓</b> |           | ✓      |

| 3.3-V PCI                 | ✓        | ✓        |           | ✓      |

| 3.3-V PCI-X               | ✓        | ✓        |           | ✓      |

| LVPECL                    | <b>✓</b> | <b>✓</b> |           | ✓      |

| 3.3-V PCML                | ✓        | ✓        |           | ✓      |

| LVDS                      | <b>✓</b> | <b>✓</b> |           | ✓      |

| HyperTransport technology | <b>✓</b> | <b>✓</b> |           | ✓      |

| Differential HSTL         | ✓        |          |           | ✓      |

| Differential SSTL         |          |          |           | ✓      |

| 3.3-V GTL                 | ✓        | ✓        |           | ✓      |

| 3.3-V GTL+                | ✓        | ✓        |           | ✓      |

| 1.5-V HSTL class I        | ✓        | ✓        |           | ✓      |

| 1.5-V HSTL class II       | ✓        | ✓        |           | ✓      |

| SSTL-18 class I           | ✓        | ✓        |           | ✓      |

| SSTL-18 class II          | ✓        | ✓        |           | ✓      |

| SSTL-2 class I            | ✓        | ✓        |           | ✓      |

| SSTL-2 class II           | ✓        | ✓        |           | ✓      |

PLL typically provides 0.5% down spread modulation using a triangular profile. The modulation frequency is programmable. Enabling spread spectrum for a PLL affects all of its outputs.

#### Lock Detect

The lock output indicates that there is a stable clock output signal in phase with the reference clock. Without any additional circuitry, the lock signal may toggle as the PLL begins tracking the reference clock. You may need to gate the lock signal for use as a system control. The lock signal from the locked port can drive the logic array or an output pin.

Whenever the PLL loses lock for any reason (be it excessive inclk jitter, clock switchover, PLL reconfiguration, power supply noise etc.), the PLL must be reset with the areset signal for correct phase shift operation. If the phase relationship between the input clock versus output clock, and between different output clocks from the PLL is not important in the design, then the PLL need not be reset.

See the *Stratix GX FPGA Errata Sheet* for more information on implementing the gated lock signal in the design.

### Programmable Duty Cycle

The programmable duty cycle allows enhanced PLLs to generate clock outputs with a variable duty cycle. This feature is supported on each enhanced PLL post-scale counter (g0..g3, l0..l3, e0..e3). The duty cycle setting is achieved by a low and high time count setting for the post-scale dividers. The Quartus II software uses the frequency input and the required multiply or divide rate to determine the duty cycle choices.

#### Advanced Clear & Enable Control

There are several control signals for clearing and enabling PLLs and their outputs. You can use these signals to control PLL resynchronization and gate PLL output clocks for low-power applications.

The pllenable pin is a dedicated pin that enables/disables PLLs. When the pllenable pin is low, the clock output ports are driven by GND and all the PLLs go out of lock. When the pllenable pin goes high again, the PLLs relock and resynchronize to the input clocks. You can choose which PLLs are controlled by the pllenable signal by connecting the pllenable input port of the altpll megafunction to the common pllenable input pin.

Stratix GX devices have an I/O interconnect similar to the R4 and C4 interconnect to drive high-fanout signals to and from the I/O blocks. There are 16 signals that drive into the I/O blocks composed of four output enables <code>io\_boe[3..0]</code>, four clock enables <code>io\_bce[3..0]</code>, four clocks <code>io\_bclk[3..0]</code>, and four clear signals <code>io\_bclr[3..0]</code>. The pin's <code>datain</code> signals can drive the IO interconnect, which in turn drives the logic array or other I/O blocks. In addition, the control and data signals can be driven from the logic array, providing a slower but more flexible routing resource. The row or column IOE clocks, <code>io\_clk[7..0]</code>, provide a dedicated routing resource for low-skew, high-speed clocks. I/O clocks are generated from regional, global, or fast regional clocks (see "PLLs & Clock Networks" on page 4–68). Figure 4–61 illustrates the signal paths through the I/O block.

Row or Column io clk[7..0] io boef3..01 To Other io bcef3..01 From I/O 10Fs Interconnect io\_bclk[3..0] io bclrf3..01 io datain0 To Logic io\_datain1 ◀ Array oe ce\_in ce\_out io coe Control aclr/preset IOE io\_cce\_in Signal Selection sclr io\_cce\_out From Logic clk\_in io cclr Array clk\_out io\_cclk io dataout0 io\_dataout1

Figure 4-61. Signal Path Through the I/O Block

Each IOE contains its own control signal selection for the following control signals: oe, ce\_in, ce\_out, aclr/preset, sclr/preset, clk\_in, and clk\_out. Figure 4–62 illustrates the control signal selection.

2.5-V, or 3.3-V power supply, depending on the output requirements. The output levels are compatible with systems of the same voltage as the power supply (for example, when VCCIO pins are connected to a 1.5-V power supply, the output levels are compatible with 1.5-V systems). When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

| Table 4–32. Stratix GX MultiVolt I/O Support Note (1) |                  |          |              |              |                   |              |              |              |          |          |

|-------------------------------------------------------|------------------|----------|--------------|--------------|-------------------|--------------|--------------|--------------|----------|----------|

| V <sub>CCIO</sub> (V)                                 | Input Signal (5) |          |              |              | Output Signal (6) |              |              |              |          |          |

|                                                       | 1.5 V            | 1.8 V    | 2.5 V        | 3.3 V        | 5.0 V             | 1.5 V        | 1.8 V        | 2.5 V        | 3.3 V    | 5.0 V    |

| 1.5                                                   | <b>✓</b>         | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |                   | <b>✓</b>     |              |              |          |          |

| 1.8                                                   | <b>√</b> (2)     | <b>✓</b> | <b>√</b> (2) | <b>√</b> (2) |                   | <b>√</b> (3) | <b>✓</b>     |              |          |          |

| 2.5                                                   |                  |          | <b>✓</b>     | <b>✓</b>     |                   | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b>     |          |          |

| 3.3                                                   |                  |          | <b>✓</b> (2) | <b>✓</b>     | <b>√</b> (4)      | <b>√</b> (3) | <b>√</b> (3) | <b>√</b> (3) | <b>✓</b> | <b>✓</b> |

#### Notes to Table 4-32:

- (1) To drive inputs higher than V<sub>CCIO</sub> but less than 4.1 V, disable the PCI clamping diode. However, to drive 5.0-V inputs to the device, enable the PCI clamping diode to prevent V<sub>1</sub> from rising above 4.0 V.

- (2) The input pin current may be slightly higher than the typical value.

- (3) Although  $V_{CCIO}$  specifies the voltage necessary for the Stratix GX device to drive out, a receiving device powered at a different level can still interface with the Stratix GX device if it has inputs that tolerate the  $V_{CCIO}$  value.

- (4) Stratix GX devices can be 5.0-V tolerant with the use of an external resistor and the internal PCI clamp diode.

- (5) This is the external signal that is driving the Stratix GX device.

- (6) This represents the system voltage that Stratix GX supports when a VCCIO pin is connected to a specific voltage level. For example, when VCCIO is 3.3 V and if the I/O standard is LVTTL/LVCMOS, the output high of the signal coming out from Stratix GX is 3.3 V and is compatible with 3.3-V or 5.0-V systems.

### Power Sequencing & Hot Socketing

Because Stratix GX devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the VCCIO and VCCINT power supplies may be powered in any order.

Signals can be driven into Stratix GX devices before and during power up without damaging the device. In addition, Stratix GX devices do not drive out during power up. Once operating conditions are reached and the device is configured, Stratix GX devices operate as specified by the user. For more information, see the *Selectable I/O Standards in Stratix & Stratix GX Devices* chapter of the *Stratix GX Device Handbook*, *Volume 2*.

## 5. Configuration & Testing

SGX51005-1.0

## SignalTap Embedded Logic Analyzer

Stratix® GX devices feature the SignalTap® embedded logic analyzer, which monitors design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry. You can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages, such as FineLine BGA® packages, because it can be difficult to add a connection to a pin during the debugging process after a board is designed and manufactured.

### **Configuration**

The logic, circuitry, and interconnects in the Stratix GX architecture are configured with CMOS SRAM elements. Stratix GX devices are reconfigurable and are 100% tested prior to shipment. As a result, you do not have to generate test vectors for fault coverage purposes, and can instead focus on simulation and design verification. In addition, you do not need to manage inventories of different ASIC designs. Stratix GX devices can be configured on the board for the specific functionality required.

Stratix GX devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable configuration devices that configure Stratix GX devices via a serial data stream. Stratix GX devices can be configured in under 100 ms using 8-bit parallel data at 100 MHz. The Stratix GX device's optimized interface allows microprocessors to configure it serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat Stratix GX devices as memory and configure them by writing to a virtual memory location, making reconfiguration easy. After a Stratix GX device has been configured, it can be reconfigured in-circuit by resetting the device and loading new data. Real-time changes can be made during system operation, enabling innovative reconfigurable computing applications.

### **Operating Modes**

The Stratix GX architecture uses SRAM configuration elements that require configuration data to be loaded each time the circuit powers up. The process of physically loading the SRAM data into the device is called configuration. During initialization, which occurs immediately after configuration, the device resets registers, enables I/O pins, and begins to operate as a logic device. The I/O pins are tri-stated during power up,

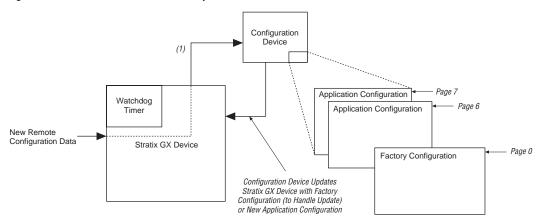

Figure 5-1. Stratix GX Device Remote Update

#### Note to Figure 5-1:

(1) When the Stratix GX device is configured with the factory configuration, it can handle update data from EPC16, EPC8, or EPC4 configuration device pages and point to the next page in the configuration device.

| Table 6–14. 3.3-V PCML Specifications |                                                 |            |         |                   |         |       |  |  |  |

|---------------------------------------|-------------------------------------------------|------------|---------|-------------------|---------|-------|--|--|--|

| Symbol Parameter                      |                                                 | Conditions | Minimum | Typical           | Maximum | Units |  |  |  |

| $V_{\text{CCIO}}$                     | I/O supply voltage                              |            | 3.135   | 3.3               | 3.465   | V     |  |  |  |

| V <sub>ID</sub>                       | Input differential voltage swing (single-ended) |            | 300     |                   | 600     | mV    |  |  |  |

| V <sub>ICM</sub>                      | Input common mode voltage                       |            | 1.5     |                   | 3.465   | V     |  |  |  |

| V <sub>OD</sub>                       | Output differential voltage (single-ended)      |            | 300     | 370               | 500     | mV    |  |  |  |

| $\Delta V_{OD}$                       | Change in V <sub>OD</sub> between high and low  |            |         |                   | 50      | mV    |  |  |  |

| V <sub>OCM</sub>                      | Output common mode voltage                      |            | 2.5     | 2.85              | 3.3     | V     |  |  |  |

| $\Delta V_{OCM}$                      | Change in V <sub>OCM</sub> between high and low |            |         |                   | 50      | mV    |  |  |  |

| V <sub>T</sub>                        | Output termination voltage                      |            |         | V <sub>CCIO</sub> |         | V     |  |  |  |

| R <sub>1</sub>                        | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω     |  |  |  |

| R <sub>2</sub>                        | Output external pull-up resistors               |            | 45      | 50                | 55      | Ω     |  |  |  |

| Table 6–15. LVPECL Specifications |                                                 |                        |         |         |         |       |  |  |  |

|-----------------------------------|-------------------------------------------------|------------------------|---------|---------|---------|-------|--|--|--|

| Symbol                            | Parameter                                       | Conditions             | Minimum | Typical | Maximum | Units |  |  |  |

| V <sub>CCIO</sub>                 | I/O supply voltage                              |                        | 3.135   | 3.3     | 3.465   | V     |  |  |  |

| V <sub>ID</sub>                   | Input differential voltage swing (single-ended) |                        | 300     |         | 1,000   | mV    |  |  |  |

| V <sub>ICM</sub>                  | Input common mode voltage                       |                        | 1       |         | 2       | V     |  |  |  |

| V <sub>OD</sub>                   | Differential output voltage (single ended)      | R <sub>L</sub> = 100 Ω | 525     | 700     | 970     | mV    |  |  |  |

| V <sub>OCM</sub>                  | Output common mode voltage                      | R <sub>L</sub> = 100 Ω | 1.5     | 1.7     | 1.9     | V     |  |  |  |

| R <sub>L</sub>                    | Receiver differential input resistor, external  |                        | 90      | 100     | 110     | Ω     |  |  |  |

| Table 6–45. IOE Internal Timing Microparameters |                |       |         |         |                |       |         |  |  |

|-------------------------------------------------|----------------|-------|---------|---------|----------------|-------|---------|--|--|

| Symbol                                          | -5 Speed Grade |       | -6 Spee | d Grade | -7 Speed Grade |       | II.m.:A |  |  |

|                                                 | Min            | Max   | Min     | Max     | Min            | Max   | Unit    |  |  |

| t <sub>SU</sub>                                 | 64             |       | 68      |         | 68             |       | ps      |  |  |

| t <sub>H</sub>                                  | 76             |       | 80      |         | 80             |       | ps      |  |  |

| t <sub>CO</sub>                                 |                | 162   |         | 171     |                | 171   | ps      |  |  |

| t <sub>PIN2COMBOUT_R</sub>                      |                | 1,038 |         | 1,093   |                | 1,256 | ps      |  |  |

| t <sub>PIN2COMBOUT_C</sub>                      |                | 927   |         | 976     |                | 1,122 | ps      |  |  |

| t <sub>COMBIN2PIN_R</sub>                       |                | 2,944 |         | 3,099   |                | 3,563 | ps      |  |  |

| t <sub>COMBIN2PIN_C</sub>                       |                | 3,189 |         | 3,357   |                | 3,860 | ps      |  |  |

| t <sub>CLR</sub>                                | 262            |       | 276     |         | 317            |       | ps      |  |  |

| t <sub>PRE</sub>                                | 262            |       | 276     |         | 317            |       | ps      |  |  |

| t <sub>CLKHL</sub>                              | 90             |       | 95      |         | 109            |       | ps      |  |  |

| Table 6–46. DSP Block Internal Timing Microparameters |                   |       |       |             |                   |       |      |  |  |

|-------------------------------------------------------|-------------------|-------|-------|-------------|-------------------|-------|------|--|--|

| Symbol                                                | -5 Speed<br>Grade |       |       | peed<br>ade | -7 Speed<br>Grade |       | Unit |  |  |

|                                                       | Min               | Max   | Min   | Max         | Min               | Max   |      |  |  |

| t <sub>SU</sub>                                       | 0                 |       | 0     |             | 0                 |       | ps   |  |  |

| t <sub>H</sub>                                        | 67                |       | 75    |             | 86                |       | ps   |  |  |

| t <sub>CO</sub>                                       |                   | 142   |       | 158         |                   | 181   | ps   |  |  |

| t <sub>INREG2PIPE18</sub>                             |                   | 2,613 |       | 2,982       |                   | 3,429 | ps   |  |  |

| t <sub>INREG2PIPE9</sub>                              |                   | 3,390 |       | 3,993       |                   | 4,591 | ps   |  |  |

| t <sub>PIPE2OUTREG2ADD</sub>                          |                   | 2,002 |       | 2,203       |                   | 2,533 | ps   |  |  |

| t <sub>PIPE2OUTREG4ADD</sub>                          |                   | 2,899 |       | 3,189       |                   | 3,667 | ps   |  |  |

| t <sub>PD9</sub>                                      |                   | 3,709 |       | 4,081       |                   | 4,692 | ps   |  |  |

| t <sub>PD18</sub>                                     |                   | 4,795 |       | 5,275       |                   | 6,065 | ps   |  |  |

| t <sub>PD36</sub>                                     |                   | 7,495 |       | 8,245       |                   | 9,481 | ps   |  |  |

| t <sub>CLR</sub>                                      | 450               |       | 500   |             | 575               |       | ps   |  |  |

| t <sub>CLKHL</sub>                                    | 1,350             |       | 1,500 |             | 1,724             |       | ps   |  |  |