Welcome to **E-XFL.COM**

## Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 4125                                                         |

| Number of Logic Elements/Cells | 41250                                                        |

| Total RAM Bits                 | 3423744                                                      |

| Number of I/O                  | 624                                                          |

| Number of Gates                | -                                                            |

| Voltage - Supply               | 1.425V ~ 1.575V                                              |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 1020-BBGA                                                    |

| Supplier Device Package        | 1020-FBGA (33x33)                                            |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep1sgx40gf1020c6n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### $\textbf{Revision History} \qquad \text{The table below shows the revision history for Chapters 1 through 7}.$

| Chapter(s) | Date / Version         | Changes Made                                                                                                                                                                                                                                                          | Comments                                                                                                                                                                                                                                                                                                                                           |

|------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 2          | June 2006, v1.1        | <ul> <li>Updated "Serial Loopback" section.</li> <li>Updated Figures 2–1 through 2–3.</li> <li>Updated Figure 2–13.</li> <li>Updated Figures 2–26 and 2–27.</li> </ul>                                                                                                |                                                                                                                                                                                                                                                                                                                                                    |

|            | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 3          | August 2005,<br>v1.1   | Added Note (3) to Figure 3-7.                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                    |

| 4          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 5          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

| 6          | June 2006, v1.2        | <ul> <li>Updated "Operating Conditions" section.</li> <li>Updated Table 6-4.</li> <li>Updated note 3 in Table 6-6.</li> <li>Added note 12 in Table 6-7.</li> <li>Updated Figure 6-1.</li> <li>Added Figure 6-2.</li> <li>Updated Tables 6-13 through 6-16.</li> </ul> | <ul> <li>Changed V<sub>OD</sub> to V<sub>ID</sub> for receiver input voltage and refclkb input voltage in Table 6–4.</li> <li>Changed value for undershoot during transition from -0.5 V to -2.0 V in note 3 of Table 6–6.</li> <li>Changed value of V<sub>OCM</sub> from mV to V in Table 6–15.</li> <li>Changed unit value of W to Ω.</li> </ul> |

|            | August 2005,<br>v1.1   | Updated Tables 6-7 and 6-50.                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                    |

| 7          | February 2005,<br>v1.0 | Initial Release.                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                    |

Section I–2 Altera Corporation

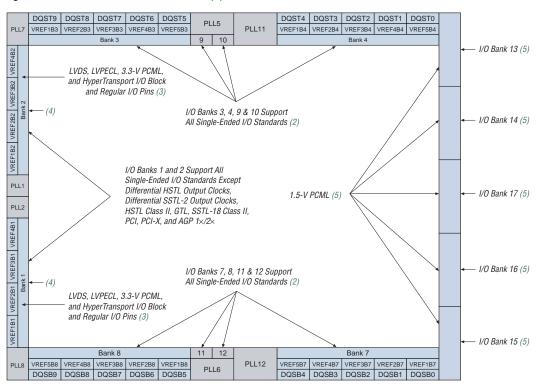

Figure 1–1. Stratix GX I/O Blocks Note (1)

#### Notes to Figure 1–1:

- (1) Figure 1–1 is a top view of the Stratix GX silicon die.

- (2) Banks 9 through 12 are enhanced PLL external clock output banks.

- (3) If the high-speed differential I/O pins are not used for high-speed differential signaling, they can support all of the I/O standards except HSTL class I and II, GTL, SSTL-18 Class II, PCI, PCI-X, and AGP 1×/2×.

- (4) For guidelines for placing single-ended I/O pads next to differential I/O pads, see the Selectable I/O Standards in Stratix & Stratix GX Devices chapter of the Stratix GX Device Handbook, Volume 2.

- (5) These I/O banks in Stratix GX devices also support the LVDS, LVPECL, and 3.3-V PCML I/O standards on reference clocks and receiver input pins (AC coupled).

# FPGA Functional Description

Stratix GX devices contain a two-dimensional row- and column-based architecture to implement custom logic. A series of column and row interconnects of varying length and speed provide signal interconnects between logic array blocks (LABs), memory block structures, and DSP blocks.

#### XAUI Mode

In XAUI mode, the rate matcher adheres to clause 48 of the IEEE 802.3ae specification for clock rate compensation. The rate matcher performs clock compensation on columns of /R/ (/K28.0/), denoted by //R//. An //R// is added or deleted automatically based on the number of words in the FIFO buffer.

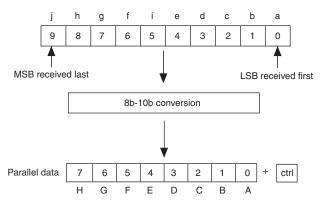

#### 8B/10B Decoder

The 8B/10B decoder converts the 10-bit encoded code group into 8-bit data and 1 control bit. The 8B/10B decoder can be bypassed. The following is a diagram of the conversion from a 10-bit encoded code group into 8-bit data + 1-bit control.

Figure 2-20. 8B/10B Decoder Conversion

There are two optional error status ports available in the 8B/10B decoder, rx\_errdetect and rx\_disperr. Table 2–7 shows the values of the ports from a given error. These status signals are aligned with the code group in which the error occurred.

| Table 2–7. Error Signal Values          |      |      |  |  |  |

|-----------------------------------------|------|------|--|--|--|

| Types of Errors rx_errdetect rx_disperr |      |      |  |  |  |

| No errors                               | 1'b0 | 1'b0 |  |  |  |

| Invalid code groups                     | 1'b1 | 1'b0 |  |  |  |

| Disparity errors                        | 1'b1 | 1'b1 |  |  |  |

Figure 2-23. Data Path in Reverse Serial Loopback Mode

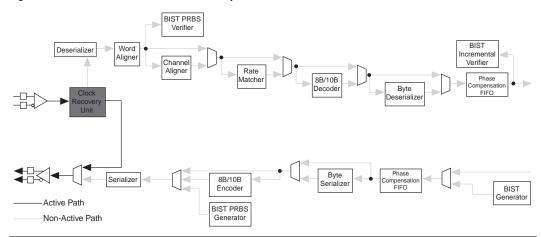

#### **BIST (Built-In Self Test)**

The Stratix GX transceiver has built-in self test modes to aid in debug and testing. The BIST modes are set in the Stratix GX MegaWizard Plug-In Manager in the Quartus II software. Only one BIST mode can be set for any single instance of the transceiver block. The BIST mode applies to all channels used in a transceiver.

The following is a list of the available BIST modes:

- PRBS generator and verifier

- Incremental mode generator and verifier

- High-frequency generator

- Low-frequency generator

- Mixed-frequency generator

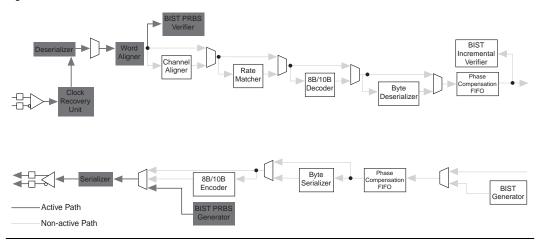

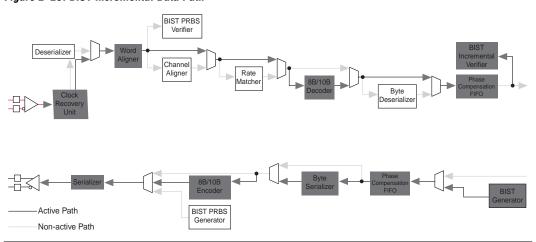

Figures 2–24 and 2–25 are diagrams of the BIST PRBS data path and the BIST incremental data path, respectively.

Figure 2-24. BIST PRBS Data Path

Figure 2-25. BIST Incremental Data Path

Table 2–9 shows the BIST data output and verifier alignment pattern.

| Table 2–9. BIST Data Output & Verifier Alignment Pattern (Part 1 of 2) |                    |                             |                  |  |  |  |

|------------------------------------------------------------------------|--------------------|-----------------------------|------------------|--|--|--|

| BIST Mode Output Polynomials Verifier Word Alignment Pattern           |                    |                             |                  |  |  |  |

| PRBS 8-bit                                                             | 2 <sup>8</sup> – 1 | $x^8 + x^7 + x^5 + x^3 + 1$ | 1000000011111111 |  |  |  |

| PRBS 10-bit                                                            | 210 - 1            | $x^{10} + x^7 + 1$          | 1111111111       |  |  |  |

The DPA data-realignment circuitry allows further realignment beyond what the *J* multiplication factor allows. You can set the *J* multiplication factor to be 8 or 10. However, because data must be continuously clocked in on each low-speed clock cycle, the upcoming bit to be realigned and previous n-1 bits of data are selected each time the data realignment logic's counter passes n-1. At this point the data is selected entirely from bit-slip register 3 (see Figure 3–11) as the counter is reset to 0. The logic array receives a new valid byte of data on the next divided low speed clock cycle. Figure 3–11 shows the data realignment logic output selection from data in the data realignment register 2 and data realignment register 3 based on its current counter value upon continuous request of data slipping from the logic array.

Bit Slip Bit Slin Bit Slin Bit Slin Bit Slip Bit Slin Bit Slip Bit Slin Bit Slip Bit Slip Register 2 Register 3 D19 D9 D29 D19 D99 D89 D119 D99 D119 D109 D18 D8 D28 D18 D118 D118 D108 D18 D98 D98 D97 D17 D7 D27 D17 D97 D87 D117 D117 D107 D16 D6 D26 D16 D96 D86 D116 D96 D116 D106 One bit Seven more One more One more slipped bits slipped bit slipped bit slipped D15 D5 D25 D15 D95 D85 D115 D95 D115 D125 D14 D4 D24 D14 D94 D84 D114 D94 D114 D124 D13 D3 D23 D83 D113 D113 D13 D93 D93 D12 D2 D22 D12 D92 D82 D112 D92 D112 D102 D111 D11 D21 D11 D91 D81 D91 D111 D10 D0 D20 D10 D90 D80 D110 D90 D110 D100 Zero bits slipped One bit slipped. Eight bits slipped. Nine bits slipped. 10 bits slipped. Counter = 0 Counter = 1 Counter = 8 Counter = 9 Counter = 0 D10 is the upcoming D21 is the upcoming D98 is the upcoming D119 is the upcoming Real data will resume bit to be slipped. bit to be slipped. on the next byte.

Figure 3–11. DPA Data Realigner

Use the rx\_channel\_data\_align signal within the device to activate the data realigner. You can use internal logic or an external pin to control the rx channel data align signal. To ensure the rising edge of the rx channel data align signal is latched into the control logic, the rx channel data align signal should stay high for at least two lowfrequency clock cycles.

bit to be slipped.

bit to be slipped.

LAB and do not drive directly to LAB local interconnects. R24 row interconnects drive LAB local interconnects via R4 and C4 interconnects. R24 interconnects can drive R24, R4, C16, and C4 interconnects.

The column interconnect operates similarly to the row interconnect and vertically routes signals to and from LABs, TriMatrix memory, DSP blocks, and IOEs. Each column of LABs is served by a dedicated column interconnect, which vertically routes signals to and from LABs, TriMatrix memory and DSP blocks, and horizontal IOEs. These column resources include:

- LUT chain interconnects within an LAB

- Register chain interconnects within an LAB

- C4 interconnects traversing a distance of four blocks in up and down direction

- C8 interconnects traversing a distance of eight blocks in up and down direction

- C16 column interconnects for high-speed vertical routing through the device

Stratix GX devices include an enhanced interconnect structure within LABs for routing LE output to LE input connections faster using LUT chain connections and register chain connections. The LUT chain connection allows the combinatorial output of an LE to directly drive the fast input of the LE right below it, bypassing the local interconnect. These resources can be used as a high-speed connection for wide fan-in functions from LE 1 to LE 10 in the same LAB. The register chain connection allows the register output of one LE to connect directly to the register input of the next LE in the LAB for fast shift registers. The Quartus II Compiler automatically takes advantage of these resources to improve utilization and performance. Figure 4–9 shows the LUT chain and register chain interconnects.

single block of RAM ideal for data packet storage. The different-sized blocks allow Stratix GX devices to efficiently support variable-sized memory in designs.

The Quartus II software automatically partitions the user-defined memory into the embedded memory blocks using the most efficient size combinations. You can also manually assign the memory to a specific block size or a mixture of block sizes.

#### M512 RAM Block

The M512 RAM block is a simple dual-port memory block and is useful for implementing small FIFO buffers, DSP, and clock domain transfer applications. Each block contains 576 RAM bits (including parity bits). M512 RAM blocks can be configured in the following modes:

- Simple dual-port RAM

- Single-port RAM

- FIFO

- ROM

- Shift register

When configured as RAM or ROM, you can use an initialization file to pre-load the memory contents.

The memory address depths and output widths can be configured as  $512 \times 1,256 \times 2,128 \times 4,64 \times 8$  ( $64 \times 9$  bits with parity), and  $32 \times 16$  ( $32 \times 18$  bits with parity). Mixed-width configurations are also possible, allowing different read and write widths. Table 4–3 summarizes the possible M512 RAM block configurations.

| Table 4-3 | Table 4–3. M512 RAM Block Configurations (Simple Dual-Port RAM) |            |          |          |          |          |          |  |

|-----------|-----------------------------------------------------------------|------------|----------|----------|----------|----------|----------|--|

|           |                                                                 | Write Port |          |          |          |          |          |  |

| Read Port | 512 × 1                                                         | 256 × 2    | 128 × 4  | 64 × 8   | 32 × 16  | 64 × 9   | 32 × 18  |  |

| 512 × 1   | <b>✓</b>                                                        | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |

| 256 × 2   | <b>✓</b>                                                        | <b>✓</b>   | <b>✓</b> | <b>✓</b> | <b>✓</b> |          |          |  |

| 128 × 4   | <b>✓</b>                                                        | <b>✓</b>   | <b>✓</b> |          | <b>✓</b> |          |          |  |

| 64 × 8    | <b>✓</b>                                                        | <b>✓</b>   |          | <b>✓</b> |          |          |          |  |

| 32 × 16   | <b>✓</b>                                                        | <b>✓</b>   | <b>✓</b> |          | <b>✓</b> |          |          |  |

| 64 × 9    |                                                                 |            |          |          |          | <b>✓</b> |          |  |

| 32 × 18   |                                                                 |            |          |          |          |          | <b>✓</b> |  |

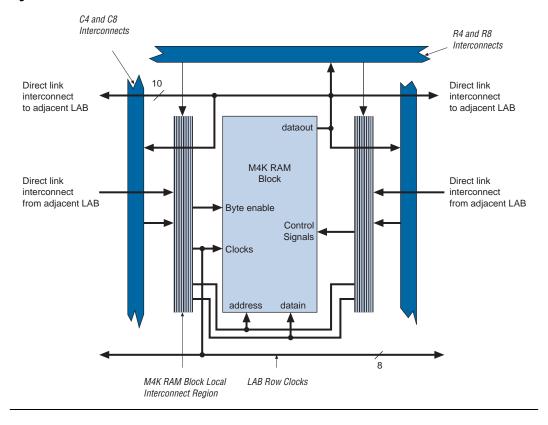

Figure 4-16. M4K RAM Block Control Signals

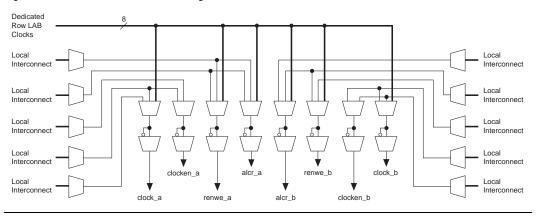

Figure 4-17. M4K RAM Block LAB Row Interface

#### M-RAM Block

The largest TriMatrix memory block, the M-RAM block, is useful for applications where a large volume of data must be stored on-chip. Each block contains 589,824 RAM bits (including parity bits). The M-RAM block can be configured in the following modes:

- True dual-port RAM

- Simple dual-port RAM

- Single-port RAM

- FIFO RAM

You cannot use an initialization file to initialize the contents of a M-RAM block. All M-RAM block contents power up to an undefined value. Only synchronous operation is supported in the M-RAM block, so all inputs are registered. Output registers can be bypassed. The memory address and output width can be configured as 64K × 8 (or 64K × 9 bits), 32K × 16 (or 32K × 18 bits), 16K × 32 (or 16K × 36 bits), 8K × 64 (or 8K × 72 bits), and 4K × 128 (or 4K × 144 bits). The 4K × 128 configuration is unavailable in true dual-port mode because there are a total of 144 data output drivers in the block. Mixed-width configurations are also possible, allowing different read and write widths. Tables 4–7 and 4–8 summarize the possible M-RAM block configurations:

| Table 4–7. M-RAM Block Configurations (Simple Dual-Port) |                                                  |          |            |          |   |  |  |

|----------------------------------------------------------|--------------------------------------------------|----------|------------|----------|---|--|--|

| Dood Dow                                                 |                                                  |          | Write Port |          |   |  |  |

| Read Port                                                | 64K × 9   32K × 18   16K × 36   8K × 72   4K × 1 |          |            |          |   |  |  |

| 64K × 9                                                  | <b>✓</b>                                         | <b>✓</b> | <b>✓</b>   | <b>✓</b> |   |  |  |

| 32K × 18                                                 | <b>✓</b>                                         | ✓        | ✓          | ✓        |   |  |  |

| 16K × 36                                                 | ✓                                                | ✓        | ✓          | <b>✓</b> |   |  |  |

| 8K × 72                                                  | ✓                                                | ✓        | <b>✓</b>   | <b>✓</b> |   |  |  |

| 4K × 144                                                 |                                                  |          |            |          | ✓ |  |  |

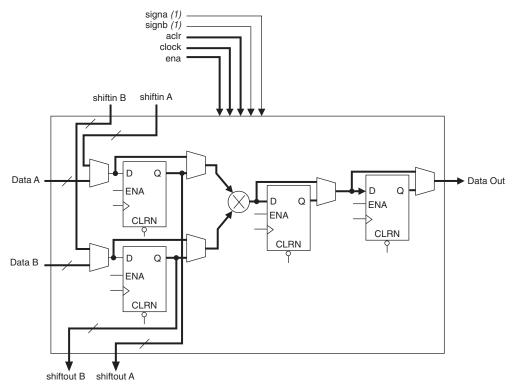

#### Adder/Subtractor/Accumulator

The adder/subtractor/accumulator is the first level of the adder/output block and can be used as an accumulator or as an adder/subtractor.

#### Adder/Subtractor

Each adder/subtractor/accumulator block can perform addition or subtraction using the addnsub independent control signal for each first-level adder in  $18 \times 18$ -bit mode. There are two addnsub [1..0] signals available in a DSP block for any configuration. For  $9 \times 9$ -bit mode, one addnsub [1..0] signal controls the top two one-level adders and another addnsub [1..0] signal controls the bottom two one-level adders. A high addnsub signal indicates addition, and a low signal indicates subtraction. The addnsub control signal can be unregistered or registered once or twice when feeding the adder blocks to match data path pipelines.

The signa and signb signals serve the same function as the multiplier block signa and signb signals. The only difference is that these signals can be registered up to two times. These signals are tied to the same signa and signb signals from the multiplier and must be connected to the same clocks and control signals.

#### Accumulator

When configured for accumulation, the adder/output block output feeds back to the accumulator as shown in Figure 4–33. The accum\_sload[1..0] signal synchronously loads the multiplier result to the accumulator output. This signal can be unregistered or registered once or twice. Additionally, the overflow signal indicates the accumulator has overflowed or underflowed in accumulation mode. This signal is always registered and must be externally latched in LEs if the design requires a latched overflow signal.

#### Summation

The output of the adder/subtractor/accumulator block feeds to an optional summation block. This block sums the outputs of the DSP block multipliers. In 9  $\times$  9-bit mode, there are two summation blocks providing the sums of two sets of four 9  $\times$  9-bit multipliers. In 18  $\times$  18-bit mode, there is one summation providing the sum of one set of four 18  $\times$  18-bit multipliers.

Figure 4–34. Simple Multiplier Mode

Note to Figure 4-34:

(1) These signals are not registered or registered once to match the data path pipeline.

DSP blocks can also implement one  $36 \times 36$ -bit multiplier in multiplier mode. DSP blocks use four  $18 \times 18$ -bit multipliers combined with dedicated adder and internal shift circuitry to achieve 36-bit multiplication. The input shift register feature is not available for the  $36 \times 36$ -bit multiplier. In  $36 \times 36$ -bit mode, the device can use the register that is normally a multiplier-result-output register as a pipeline stage for the  $36 \times 36$ -bit multiplier. Figure 4–35 shows the  $36 \times 36$ -bit multiply mode.

#### Clock Multiplication & Division

Each Stratix GX device enhanced PLL provides clock synthesis for PLL output ports using  $m/(n \times \text{post-scale counter})$  scaling factors. The input clock is divided by a pre-scale divider, *n*, and is then multiplied by the *m* feedback factor. The control loop drives the VCO to match  $f_{IN} \times (m/n)$ . Each output port has a unique post-scale counter that divides down the high-frequency VCO. For multiple PLL outputs with different frequencies, the VCO is set to the least common multiple of the output frequencies that meets its frequency specifications. Then, the post-scale dividers scale down the output frequency for each output port. For example, if output frequencies required from one PLL are 33 and 66 MHz, set the VCO to 330 MHz (the least common multiple in the VCO's range). There is one pre-scale divider, *n*, and one multiply divider, *m*, per PLL, with a range of 1 to 512 on each. There are two post-scale dividers (*l*) for regional clock output ports, four counters (g) for global clock output ports, and up to four counters (e) for external clock outputs, all ranging from 1 to 512. The Quartus II software automatically chooses the appropriate scaling factors according to the input frequency, multiplication, and division values entered.

#### Clock Switchover

To effectively develop high-reliability network systems, clocking schemes must support multiple clocks to provide redundancy. For this reason, Stratix GX device enhanced PLLs support a flexible clock switchover capability. Figure 4–52 shows a block diagram of the switchover circuit. The switchover circuit is configurable, so you can define how to implement it. Clock-sense circuitry automatically switches from the primary to secondary clock for PLL reference when the primary clock signal is not present.

pin. The I/O standards supported by any particular bank determines what standards are possible for an external clock output driven by the fast PLL in that bank.

Table 4–20 shows the I/O standards supported by fast PLL input pins.

| Table 4–20. Fast PLL Port Input Pin I/O Standards |          |           |  |  |  |

|---------------------------------------------------|----------|-----------|--|--|--|

| I/O Chandand                                      | Input    |           |  |  |  |

| I/O Standard                                      | INCLK    | PLLENABLE |  |  |  |

| LVTTL                                             | ✓        | ✓         |  |  |  |

| LVCMOS                                            | ✓        | ✓         |  |  |  |

| 2.5 V                                             | ✓        |           |  |  |  |

| 1.8 V                                             | ✓        |           |  |  |  |

| 1.5 V                                             | ✓        |           |  |  |  |

| 3.3-V PCI                                         |          |           |  |  |  |

| 3.3-V PCI-X                                       |          |           |  |  |  |

| LVPECL                                            | ✓        |           |  |  |  |

| 3.3-V PCML                                        | ✓        |           |  |  |  |

| LVDS                                              | ✓        |           |  |  |  |

| HyperTransport technology                         | ✓        |           |  |  |  |

| Differential HSTL                                 | ✓        |           |  |  |  |

| Differential SSTL                                 |          |           |  |  |  |

| 3.3-V GTL                                         | ✓        |           |  |  |  |

| 3.3-V GTL+                                        | ✓        |           |  |  |  |

| 1.5V HSTL class I                                 | ✓        |           |  |  |  |

| 1.5V HSTL class II                                | ✓        |           |  |  |  |

| SSTL-18 class I                                   | ✓        |           |  |  |  |

| SSTL-18 class II                                  | ✓        |           |  |  |  |

| SSTL-2 class I                                    | ✓        |           |  |  |  |

| SSTL-2 class II                                   | ✓        |           |  |  |  |

| SSTL-3 class I                                    | ✓        |           |  |  |  |

| SSTL-3 class II                                   | ✓        |           |  |  |  |

| AGP (1× and 2×)                                   | ✓        |           |  |  |  |

| CTT                                               | <b>✓</b> |           |  |  |  |

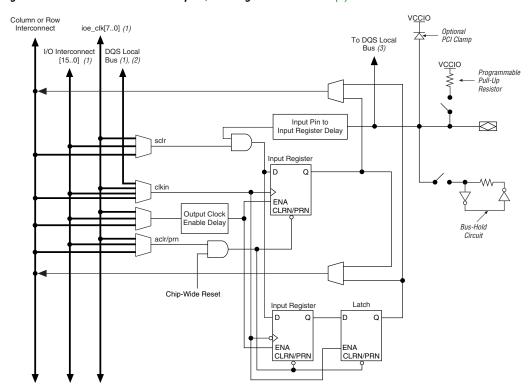

When using the IOE for DDR inputs, the two input registers clock double rate input data on alternating edges. An input latch is also used within the IOE for DDR input acquisition. The latch holds the data that is present during the clock high times. This allows both bits of data to be synchronous with the same clock edge (either rising or falling). Figure 4–64 shows an IOE configured for DDR input. Figure 4–65 shows the DDR input timing diagram.

Figure 4–64. Stratix GX IOE in DDR Input I/O Configuration Note (1)

*Notes to Figure 4–64:*

- (1) All input signals to the IOE can be inverted at the IOE.

- (2) This signal connection is only allowed on dedicated DQ function pins.

- (3) This signal is for dedicated DQS function pins only.

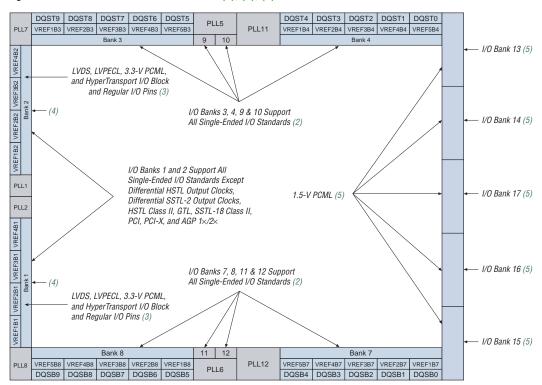

**Figure 4–69. Stratix GX I/O Banks** Notes (1), (2), (3)

#### Notes to Figure 4–69:

- (1) Figure 4–69 is a top view of the Stratix GX silicon die.

- (2) Banks 9 through 12 are enhanced PLL external clock output banks.

- (3) If the high-speed differential I/O pins are not used for high-speed differential signaling, they can support all of the I/O standards except HSTL class I and II, GTL, SSTL-18 Class II, PCI, PCI-X, and AGP 1×/2×.

- (4) For guidelines for placing single-ended I/O pads next to differential I/O pads, see the Selectable I/O Standards in Stratix & Stratix GX Devices chapter in the Stratix GX Device Handbook, Volume 2.

- (5) These I/O banks in Stratix GX devices also support the LVDS, LVPECL, and 3.3-V PCML I/O standards on reference clocks and receiver input pins (AC coupled)

| JTAG Instruction       | Description                                                                                                                                                                                                                                                                     |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLAMP (1)              | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation while holding I/O pins to a state defined by the data in the boundary-scan register. |

| ICR instructions       | Used when configuring a Stratix GX device through the JTAG port with a MasterBlaster™ or ByteBlasterMV™ download cable, or when using a .jam file or .jbc file with an embedded processor.                                                                                      |

| PULSE_NCONFIG          | Emulates pulsing the nCONFIG pin low to trigger reconfiguration even though the physical pin is unaffected.                                                                                                                                                                     |

| CONFIG_IO              | Allows the IOE standards to be configured through the JTAG chain. Stops configuration if executed during configuration. Can be executed before or after configuration.                                                                                                          |

| SignalTap instructions | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                                                                  |

#### Note to Table 4-33:

(1) Bus hold and weak pull-up resistor features override the high-impedance state of HIGHZ, CLAMP, and EXTEST.

The Stratix GX device instruction register length is 10 bits, and the USERCODE register length is 32 bits. Tables 4–34 and 4–35 show the boundary-scan register length and IDCODE information for Stratix GX devices.

| Table 4–34. Stratix GX Boundary-Scan Register Length |       |  |  |  |

|------------------------------------------------------|-------|--|--|--|

| Device Boundary-Scan Register Length                 |       |  |  |  |

| EP1SGX10                                             | 1,029 |  |  |  |

| EP1SGX25                                             | 1,665 |  |  |  |

| EP1SGX40                                             | 1,941 |  |  |  |

| Table 4–35. 32-Bit Stratix GX Device IDCODE (Part 1 of 2) |                  |                       |                                    |                 |  |  |

|-----------------------------------------------------------|------------------|-----------------------|------------------------------------|-----------------|--|--|

| IDCODE (32 Bits) (1)                                      |                  |                       |                                    |                 |  |  |

| Device                                                    | Version (4 Bits) | Part Number (16 Bits) | Manufacturer Identity<br>(11 Bits) | LSB (1 Bit) (2) |  |  |

| EP1SGX10                                                  | 0000             | 0010 0000 0100 0001   | 000 0110 1110                      | 1               |  |  |

| EP1SGX25                                                  | 0000             | 0010 0000 0100 0011   | 000 0110 1110                      | 1               |  |  |

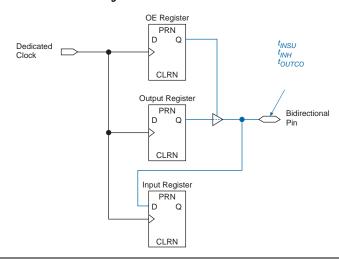

Figure 6-6. External Timing in Stratix GX Devices

All external I/O timing parameters shown are for 3.3-V LVTTL or LVCMOS I/O standards with the maximum current strength. For external I/O timing using standards other than LVTTL or LVCMOS use the I/O standard input and output delay adders in Tables 6–72 through 6–76.

Table 6–51 shows the external I/O timing parameters when using fast regional clock networks.

| Table 6-51. Stratix GX Fast Regional Clock External I/O Timing Parameters         Notes (1), (2) |                                                                                                                             |                           |  |  |  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|

| Symbol                                                                                           | Parameter                                                                                                                   | Conditions                |  |  |  |

| t <sub>INSU</sub>                                                                                | Setup time for input or bidirectional pin using column IOE input register with fast regional clock fed by FCLK pin          |                           |  |  |  |

| t <sub>INH</sub>                                                                                 | Hold time for input or bidirectional pin using column IOE input register with fast regional clock fed by FCLK pin           |                           |  |  |  |

| t <sub>OUTCO</sub>                                                                               | Clock-to-output delay output or bidirectional pin using column IOE output register with fast regional clock fed by FCLK pin | C <sub>LOAD</sub> = 10 pF |  |  |  |

#### Notes to Table 6-51:

- (1) These timing parameters are sample-tested only.

- (2) These timing parameters are for column IOE pins. Row IOE pins are 100- to 250-ps slower depending on device and speed grade and whether it is t<sub>CO</sub> or t<sub>SU</sub>. You should use the Quartus II software to verify the external timing for any pin.

The scaling factors for output pin timing in Table 6–80 are shown in units of time per pF unit of capacitance (ps/pF). Add this delay to the combinational timing path for output or bidirectional pins in addition to the "I/O Adder" delays shown in Tables 6–72 through 6–77 and the "IOE Programmable Delays" in Tables 6–78 and 6–79.

| Table 6–80. Output Delay Adder for Loading on LVTTL/LVCMOS Output Buffers |       |             |                |                |             |            |  |

|---------------------------------------------------------------------------|-------|-------------|----------------|----------------|-------------|------------|--|

| LVTTL/LVCMOS Standards                                                    |       |             |                |                |             |            |  |

| Conditions Output Pin Adder Delay (ps/pF)                                 |       |             |                |                |             |            |  |

| Parameter                                                                 | Value | 3.3-V LVTTL | 2.5-V LVTTL    | 1.8-V LVTTL    | 1.5-V LVTTL | LVCMOS     |  |

|                                                                           | 24 mA | 15          | -              | _              | -           | 8          |  |

|                                                                           | 16 mA | 25          | 18             | -              | -           | -          |  |

| Drive Strongth                                                            | 12 mA | 30          | 25             | 25             | -           | 15         |  |

| Drive Strength                                                            | 8 mA  | 50          | 35             | 40             | 35          | 20         |  |

|                                                                           | 4 mA  | 60          | -              | -              | 80          | 30         |  |

|                                                                           | 2 mA  | _           | 75             | 120            | 160         | 60         |  |

|                                                                           |       | SSTL/       | HSTL Standard  | S              |             |            |  |

| Conditi                                                                   | one   |             | Output P       | in Adder Delay | (ps/pF)     |            |  |

| Contain                                                                   | olio  | SSTL-3      | SSTL-2         | SSTL-1.8       | 1.5-V HSTL  | 1.8-V HSTL |  |

| Class                                                                     |       | 25          | 25             | 25             | 25          | 25         |  |

| Class                                                                     | s II  | 25          | 20             | 25             | 20          | 20         |  |

|                                                                           |       | GTL+/GTL    | /CTT/PCI Stand | ards           |             |            |  |

| Conditions Out                                                            |       |             |                | in Adder Delay | (ps/pF)     |            |  |

| Parameter                                                                 | Value | GTL+        | GTL            | CTT            | PCI         | AGP        |  |

| V <sub>CCIO</sub> voltage                                                 | 3.3 V | 18          | 18             | 25             | 20          | 20         |  |

| level                                                                     | 2.5 V | 15          | 18             | -              | -           | -          |  |