### Microchip Technology - PIC24F04KA200-I/P Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014110                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                     |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                 |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 4KB (1.375K x 24)                                                           |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                 |

| Data Converters            | A/D 7x10b                                                                   |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Through Hole                                                                |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                     |

| Supplier Device Package    | 14-PDIP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04ka200-i-p |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

|         | Device Overview                                             |       |

|---------|-------------------------------------------------------------|-------|

| 2.0 0   | Suidelines for Getting Started with 16-Bit Microcontrollers | 15    |

| 3.0 C   |                                                             | 19    |

| 4.0 N   | Nemory Organization                                         | 25    |

| 5.0 F   | Flash Program Memory                                        | 43    |

|         | Resets                                                      |       |

| 7.0 li  | nterrupt Controller                                         | 57    |

| 8.0 C   | Dscillator Configuration                                    | 81    |

| 9.0 F   | Power-Saving Features                                       | 91    |

| 10.0 l/ | /O Ports                                                    | 99    |

| 11.0 T  | Fimer1                                                      | . 101 |

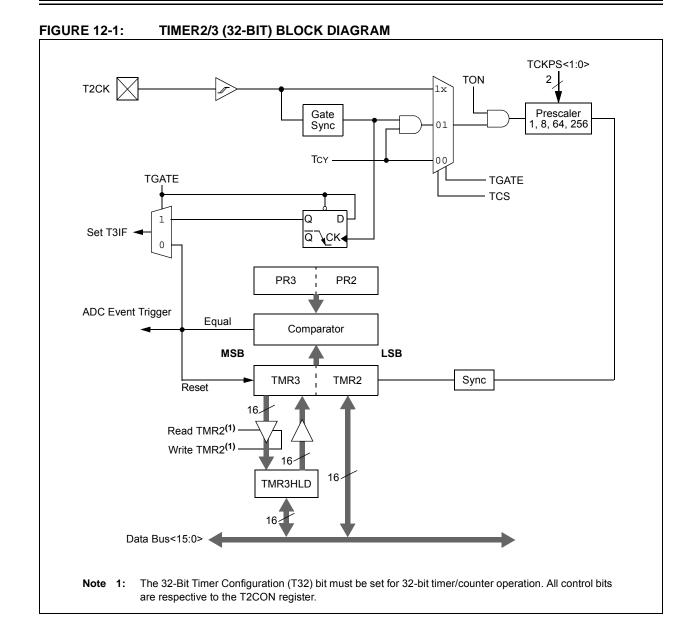

| 12.0 T  | Fimer2/3                                                    | . 103 |

| 13.0 lı | nput Capture                                                | . 109 |

|         | Dutput Compare                                              |       |

|         | Serial Peripheral Interface (SPI)                           |       |

|         | nter-Integrated Circuit (I <sup>2</sup> C™)                 |       |

|         | Jniversal Asynchronous Receiver Transmitter (UART)          |       |

|         | High/Low-Voltage Detect (HLVD)                              |       |

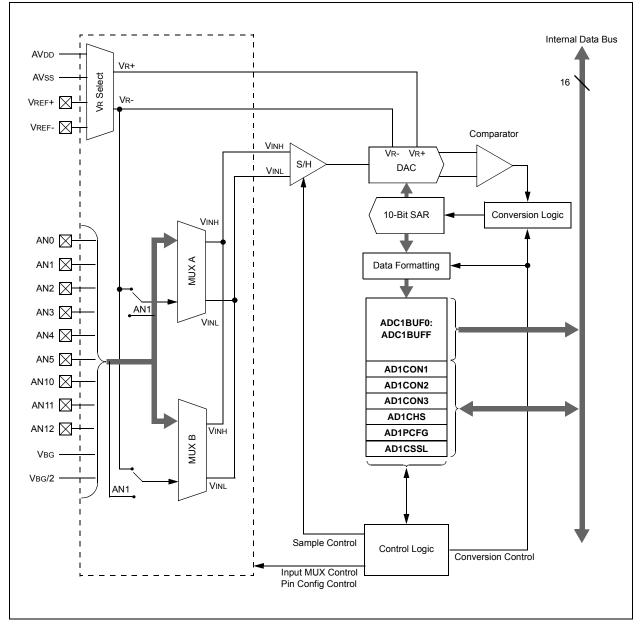

|         | 0-Bit High-Speed A/D Converter                              |       |

|         | Comparator Module                                           |       |

|         | Comparator Voltage Reference                                |       |

|         | Charge Time Measurement Unit (CTMU)                         |       |

|         | Special Features                                            |       |

| 24.0 C  | Development Support                                         | . 173 |

|         | nstruction Set Summary                                      |       |

| 26.0 E  | Electrical Characteristics                                  | . 185 |

|         | Packaging Information                                       |       |

| Append  | dix A: Revision History                                     | . 213 |

|         |                                                             |       |

|         | crochip Web Site                                            |       |

|         | ner Change Notification Service                             |       |

|         | ner Support                                                 |       |

| Produc  | t Identification System                                     | . 221 |

| IABLE 4      | -15: | ADC R  | EGISTI            |        | •                     |                       |        |        |          |            |       |       |        |        |        |        |        |            |

|--------------|------|--------|-------------------|--------|-----------------------|-----------------------|--------|--------|----------|------------|-------|-------|--------|--------|--------|--------|--------|------------|

| File<br>Name | Addr | Bit 15 | Bit 14            | Bit 13 | Bit 12                | Bit 11                | Bit 10 | Bit 9  | Bit 8    | Bit 7      | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

| ADC1BUF0     | 0300 |        | ADC Data Buffer 0 |        |                       |                       |        |        |          |            |       |       |        | xxxx   |        |        |        |            |

| ADC1BUF1     | 0302 |        | ADC Data Buffer 1 |        |                       |                       |        |        |          |            |       |       | xxxx   |        |        |        |        |            |

| ADC1BUF2     | 0304 |        | ADC Data Buffer 2 |        |                       |                       |        |        |          |            |       |       | xxxx   |        |        |        |        |            |

| ADC1BUF3     | 0306 |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 3 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF4     | 0308 |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 4 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF5     | 030A |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 5 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF6     | 030C |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 6 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF7     | 030E |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 7 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF8     | 0310 |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 8 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUF9     | 0312 |        |                   |        |                       |                       |        |        | ADC Data | a Buffer 9 |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFA     | 0314 |        |                   |        |                       |                       |        |        | ADC Data | Buffer 10  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFB     | 0316 |        |                   |        |                       |                       |        |        | ADC Data | Buffer 11  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFC     | 0318 |        |                   |        |                       |                       |        |        | ADC Data | Buffer 12  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFD     | 031A |        |                   |        |                       |                       |        |        | ADC Data | Buffer 13  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFE     | 031C |        |                   |        |                       |                       |        |        | ADC Data | Buffer 14  |       |       |        |        |        |        |        | xxxx       |

| ADC1BUFF     | 031E |        |                   |        |                       |                       |        |        | ADC Data | Buffer 15  |       |       |        |        |        | T      | 1      | xxxx       |

| AD1CON1      | 0320 | ADON   |                   | ADSIDL | _                     | —                     | —      | FORM1  | FORM0    | SSRC2      | SSRC1 | SSRC0 | _      | _      | ASAM   | SAMP   | DONE   | 0000       |

| AD1CON2      | 0322 | VCFG2  | VCFG1             | VCFG0  | OFFCAL                | —                     | CSCNA  | _      | —        | BUFS       | _     | SMPI3 | SMPI2  | SMPI1  | SMPI0  | BUFM   | ALTS   | 0000       |

| AD1CON3      | 0324 | ADRC   | _                 | _      | SAMC4                 | SAMC3                 | SAMC2  | SAMC1  | SAMC0    | _          | _     | ADCS5 | ADCS4  | ADCS3  | ADCS2  | ADCS1  | ADCS0  | 0000       |

| AD1CHS       | 0328 | CH0NB  |                   |        | _                     | CH0SB3                | CH0SB2 | CH0SB1 | CH0SB0   | CH0NA      | _     | _     | CH0SA4 | CH0SA3 | CH0SA2 | CH0SA1 | CH0SA0 | 0000       |

| AD1PCFG      | 032C | _      | —                 | —      | PCFG12 <sup>(1)</sup> |                       |        | _      | —        | —          | _     | PCFG5 | PCFG4  | PCFG3  | PCFG2  | PCFG1  | PCFG0  | 0000       |

| AD1CSSL      | 0330 | —      |                   | _      | CSSL12 <sup>(1)</sup> | CSSL11 <sup>(1)</sup> | CSSL10 | _      | —        | —          | _     | CSSL5 | CSSL4  | CSSL3  | CSSL2  | CSSL1  | CSSL0  | 0000       |

### TABLE 4-15: ADC REGISTER MAP

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: These bits are not implemented on 14-pin devices.

### TABLE 4-16: CTMU REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10   | Bit 9   | Bit 8  | Bit 7   | Bit 6    | Bit 5    | Bit 4   | Bit 3    | Bit 2    | Bit 1    | Bit 0    | All<br>Resets |

|--------------|------|--------|--------|----------|--------|--------|----------|---------|--------|---------|----------|----------|---------|----------|----------|----------|----------|---------------|

| CTMUCON      | 033C | CTMUEN | —      | CTMUSIDL | TGEN   | EDGEN  | EDGSEQEN | IDISSEN | CTTRIG | EDG2POL | EDG2SEL1 | EDG2SEL0 | EDG1POL | EDG1SEL1 | EDG1SEL0 | EDG2STAT | EDG1STAT | 0000          |

| CTMUICON     | 033E | ITRIM5 | ITRIM4 | ITRIM3   | ITRIM2 | ITRIM1 | ITRIM0   | IRNG1   | IRNG0  | _       | _        | _        | _       | _        | _        | _        | _        | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

## 5.2 RTSP Operation

The PIC24F Flash program memory array is organized into rows of 32 instructions or 96 bytes. RTSP allows the user to erase blocks of 1 row, 2 rows and 4 rows (32, 64 and 128 instructions) at a time and to program one row at a time. It is also possible to program single words.

The 1-row (96 bytes), 2-row (192 bytes) and 4-row (384 bytes) erase blocks and single row write block (96 bytes) are edge-aligned, from the beginning of program memory.

When data is written to program memory using TBLWT instructions, the data is not written directly to memory. Instead, data written using table writes is stored in holding latches until the programming sequence is executed.

Any number of TBLWT instructions can be executed and a write will be successfully performed. However, 32 TBLWT instructions are required to write the full row of memory.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register.

Data can be loaded in any order and the holding registers can be written to multiple times before performing a write operation. Subsequent writes, however, will wipe out any previous writes.

| Note: | Writing to a location multiple times without |

|-------|----------------------------------------------|

|       | erasing it is not recommended.               |

All of the table write operations are single-word writes (two instruction cycles), because only the buffers are written. A programming cycle is required for programming each row.

### 5.3 Enhanced In-Circuit Serial Programming

Enhanced ICSP uses an on-board bootloader, known as the program executive, to manage the programming process. Using an SPI data frame format, the program executive can erase, program and verify program memory. For more information on Enhanced ICSP, see the device programming specification.

### 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory: NVMCON and NVMKEY.

The NVMCON register (Register 5-1) controls the blocks that need to be erased, which memory type is to be programmed and when the programming cycle starts.

NVMKEY is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.5 "Programming Operations"** for further details.

### 5.5 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. During a programming or erase operation, the processor stalls (waits) until the operation is finished. Setting the WR bit (NVMCON<15>) starts the operation and the WR bit is automatically cleared when the operation is finished.

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. Note that the system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code will also depend on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| Reset Type         | Clock Source | SYSRST Delay | System Clock<br>Delay | Notes      |

|--------------------|--------------|--------------|-----------------------|------------|

| POR <sup>(6)</sup> | EC           | TPOR + TPWRT | _                     | 1, 2       |

|                    | FRC, FRCDIV  | TPOR + TPWRT | TFRC                  | 1, 2, 3    |

|                    | LPRC         | TPOR + TPWRT | TLPRC                 | 1, 2, 3    |

|                    | ECPLL        | TPOR + TPWRT | TLOCK                 | 1, 2, 4    |

|                    | FRCPLL       | TPOR + TPWRT | TFRC + TLOCK          | 1, 2, 3, 4 |

|                    | XT, HS, SOSC | TPOR+ TPWRT  | Tost                  | 1, 2, 5    |

|                    | XTPLL, HSPLL | TPOR + TPWRT | TOST + TLOCK          | 1, 2, 4, 5 |

| BOR                | EC           | TPWRT        | —                     | 2          |

|                    | FRC, FRCDIV  | Tpwrt        | TFRC                  | 2, 3       |

|                    | LPRC         | Tpwrt        | TLPRC                 | 2, 3       |

|                    | ECPLL        | Tpwrt        | TLOCK                 | 2, 4       |

|                    | FRCPLL       | Tpwrt        | TFRC + TLOCK          | 2, 3, 4    |

|                    | XT, HS, SOSC | Tpwrt        | Tost                  | 2, 5       |

|                    | XTPLL, HSPLL | TPWRT        | TFRC + TLOCK          | 2, 3, 4    |

| All Others         | Any Clock    | _            | —                     | None       |

### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay.

2: TPWRT = 64 ms nominal if the Power-up Timer is enabled; otherwise, it is zero.

3: TFRC and TLPRC = RC Oscillator start-up times.

**4:** TLOCK = PLL lock time.

**5:** TOST = Oscillator Start-up Timer (OST). A 10-bit counter waits 1024 oscillator periods before releasing oscillator clock to the system.

6: If Two-Speed Start-up is enabled, regardless of the Primary Oscillator selected, the device starts with FRC, and in such cases, FRC start-up time is valid.

Note: For detailed operating frequency and timing specifications, see Section 26.0 "Electrical Characteristics".

## 6.3 Brown-out Reset (BOR)

The PIC24F04KA201 family devices implement a BOR circuit, which provides the user several configuration and power-saving options. The BOR is controlled by the <BORV1:BORV0> and (BOREN<1:0>) Configuration bits (FPOR<6:5,1:0>). There are a total of four BOR configurations, which are provided in Table 6.3.1.

The BOR threshold is set by the BORV<1:0> bits. If BOR is enabled (any values of BOREN<1:0>, except '00'), any drop of VDD below the set threshold point will reset the device. The chip will remain in BOR until VDD rises above threshold.

If the Power-up Timer is enabled, it will be invoked after VDD rises above the threshold; it, then, will keep the chip in Reset for an additional time delay, TPWRT, if VDD drops below the threshold while the power-up timer is running. The chip goes back into a BOR and the Power-up Timer will be initialized. Once VDD rises above the threshold, the Power-up Timer will execute the additional time delay.

BOR and the Power-up Timer are independently configured. Enabling the BOR Reset does not automatically enable the PWRT.

### 6.3.1 SOFTWARE ENABLED BOR

When BOREN<1:0> = 01, the BOR can be enabled or disabled by the user in software. This is done with the control bit, SBOREN (RCON<13>). Setting SBOREN enables the BOR to function as previously described. Clearing the SBOREN disables the BOR entirely. The SBOREN bit operates only in this mode; otherwise, it is read as '0'.

Placing BOR under software control gives the user the additional flexibility of tailoring the application to its environment without having to reprogram the device to change the BOR configuration. It also allows the user to tailor the incremental current that the BOR consumes. While the BOR current is typically very small, it may have some impact in low-power applications.

| Note: | Even when the BOR is under software           |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       | control, the BOR Reset voltage level is still |  |  |  |  |  |  |  |  |

|       | set by the BORV1:BORV0 Configuration          |  |  |  |  |  |  |  |  |

|       | bits. It can not be changed in software.      |  |  |  |  |  |  |  |  |

### 6.3.2 DETECTING BOR

When BOR is enabled, the BOR bit (RCON<1>) is always reset to '1' on any BOR or POR event. This makes it difficult to determine if a BOR event has occurred just by reading the state of BOR alone. A more reliable method is to simultaneously check the state of both POR and BOR. This assumes that the POR and BOR bits are reset to '0' in the software immediately after any POR event. If the BOR bit is '1' while POR is '0', it can be reliably assumed that a BOR event has occurred.

Note: Even when the device exits from Deep Sleep mode, both the POR and BOR are set.

### 6.3.3 DISABLING BOR IN SLEEP MODE

When BOREN<1:0> = 10, BOR remains under hardware control and operates as previously described. However, whenever the device enters Sleep mode, BOR is automatically disabled. When the device returns to any other operating mode, BOR is automatically re-enabled.

This mode allows for applications to recover from brown-out situations, while actively executing code, when the device requires BOR protection the most. At the same time, it saves additional power in Sleep mode by eliminating the small incremental BOR current.

### 6.3.4 DEEP SLEEP BOR (DSBOR)

Deep Sleep BOR is a very low-power BOR circuitry. Due to low current consumption, accuracy may vary. DSBOR occurs anywhere between 1.55V and 1.95V.

DSBOR is selected in configuration through the BORV<1:0> (FPOR<6:5>) bits = 00.

DSBOR re-arms the POR anywhere between 1.55V and 1.95V; however, below 1.55V, the POR is asserted.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1

| U-0    | U-0 | R/W-0, HS | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----------|-----|-----|-----|-----|-------|

| —      | —   | INT2IF    |     |     | —   | —   | —     |

| bit 15 |     |           |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | R/W-0, HS | R/W-0, HS | R/W-0, HS | R/W-0   | R/W-0   |

|-------|-----|-----|-----------|-----------|-----------|---------|---------|

| _     | —   | —   | INT1IF    | CNIF      | CMIF      | MI2C1IF | SI2C1IF |

| bit 7 |     |     |           |           |           |         | bit 0   |

| Legend:           | HS = Hardware Settable bit |                             |                    |

|-------------------|----------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit           | U = Unimplemented bit, read | 1 as '0'           |

| -n = Value at POR | '1' = Bit is set           | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                |

|-----------|-----------------------------------------------------------|

| bit 13    | INT2IF: External Interrupt 2 Flag Status bit              |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 12-5  | Unimplemented: Read as '0'                                |

| bit 4     | INT1IF: External Interrupt 1 Flag Status bit              |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 3     | CNIF: Input Change Notification Interrupt Flag Status bit |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 2     | CMIF: Comparator Interrupt Flag Status bit                |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 1     | MI2C1IF: Master I2C1 Event Interrupt Flag Status bit      |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

| bit 0     | SI2C1IF: Slave I2C1 Event Interrupt Flag Status bit       |

|           | 1 = Interrupt request has occurred                        |

|           | 0 = Interrupt request has not occurred                    |

|           |                                                           |

| REGISTER     | 7-17: IPC7:        | INTERRUPT          | PRIORITY (        | CONTROL RE                         | GISTER 7 |                    |       |  |  |  |

|--------------|--------------------|--------------------|-------------------|------------------------------------|----------|--------------------|-------|--|--|--|

| U-0          | U-0                | U-0                | U-0               | U-0                                | U-0      | U-0                | U-0   |  |  |  |

| _            | —                  | —                  | _                 | _                                  | —        | —                  | —     |  |  |  |

| bit 15       |                    |                    |                   |                                    |          |                    | bit 8 |  |  |  |

|              |                    |                    |                   |                                    |          |                    |       |  |  |  |

| U-0          | R/W-1              | R/W-0              | R/W-0             | U-0                                | U-0      | U-0                | U-0   |  |  |  |

|              | INT2IP2            | INT2IP1            | INT2IP0           | —                                  | —        | —                  |       |  |  |  |

| bit 7        |                    |                    |                   |                                    |          |                    | bit 0 |  |  |  |

|              |                    |                    |                   |                                    |          |                    |       |  |  |  |

| Legend:      |                    |                    |                   |                                    |          |                    |       |  |  |  |

| R = Readab   | le bit             | W = Writable       | bit               | U = Unimplemented bit, read as '0' |          |                    |       |  |  |  |

| -n = Value a | t POR              | '1' = Bit is set   |                   | '0' = Bit is clea                  | ared     | x = Bit is unknown |       |  |  |  |

|              |                    |                    |                   |                                    |          |                    |       |  |  |  |

| bit 15-7     | Unimplemen         | ted: Read as '     | 0'                |                                    |          |                    |       |  |  |  |

| bit 6-4      | INT2IP<2:0>:       | External Intern    | rupt 2 Priority b | oits                               |          |                    |       |  |  |  |

|              | 111 = Interru      | ot is priority 7 ( | highest priority  | interrupt)                         |          |                    |       |  |  |  |

|              | •                  |                    |                   |                                    |          |                    |       |  |  |  |

|              | •                  |                    |                   |                                    |          |                    |       |  |  |  |

|              | •<br>001 = Interru | at is priority 1   |                   |                                    |          |                    |       |  |  |  |

|              |                    | ot source is dis   | abled             |                                    |          |                    |       |  |  |  |

| bit 3-0      |                    | ted: Read as '     |                   |                                    |          |                    |       |  |  |  |

|              | -                  |                    |                   |                                    |          |                    |       |  |  |  |

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

| bit 7 | CLKLOCK: Clock Selection Lock Enabled bit<br><u>If FSCM is enabled (FCKSM1 = 1):</u><br>1 = Clock and PLL selections are locked<br>0 = Clock and PLL selections are not locked and may be modified by setting the OSWEN bit<br><u>If FSCM is disabled (FCKSM1 = 0):</u><br>Clock and PLL selections are never locked and may be modified by setting the OSWEN bit. |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 5 | LOCK: PLL Lock Status bit <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                           |

|       | <ul> <li>1 = PLL module is in lock or PLL module start-up timer is satisfied</li> <li>0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled</li> </ul>                                                                                                                                                                                   |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 3 | CF: Clock Fail Detect bit                                                                                                                                                                                                                                                                                                                                          |

|       | <ul><li>1 = FSCM has detected a clock failure</li><li>0 = No clock failure has been detected</li></ul>                                                                                                                                                                                                                                                             |

| bit 2 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                         |

| bit 1 | SOSCEN: 32 kHz Secondary Oscillator (SOSC) Enable bit                                                                                                                                                                                                                                                                                                              |

|       | <ul><li>1 = Enable secondary oscillator</li><li>0 = Disable secondary oscillator</li></ul>                                                                                                                                                                                                                                                                         |

| bit 0 | OSWEN: Oscillator Switch Enable bit                                                                                                                                                                                                                                                                                                                                |

|       | <ul> <li>1 = Initiate an oscillator switch to clock source specified by NOSC&lt;2:0&gt; bits</li> <li>0 = Oscillator switch is complete</li> </ul>                                                                                                                                                                                                                 |

- Note 1: Reset values for these bits are determined by the FNOSC Configuration bits.

- 2: Also resets to '0' during any valid clock switch or whenever a non-PLL Clock mode is selected.

### DS30009937C-page 104

### REGISTER 16-1: I2C1CON: I2C1 CONTROL REGISTER (CONTINUED)

| bit 5 | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master; applicable during master receive)                                                                      |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | Value that will be transmitted when the software initiates an Acknowledge sequence.<br>1 = Sends NACK during Acknowledge<br>0 = Sends ACK during Acknowledge                   |

|       |                                                                                                                                                                                |

| bit 4 | <b>ACKEN:</b> Acknowledge Sequence Enable bit (when operating as I <sup>2</sup> C master; applicable during master receive)                                                    |

|       | 1 = Initiates Acknowledge sequence on SDA1 and SCL1 pins and transmits ACKDT data bit; hardware clear at end of master Acknowledge sequence                                    |

|       | 0 = Acknowledge sequence not in progress                                                                                                                                       |

| bit 3 | RCEN: Receive Enable bit (when operating as I <sup>2</sup> C master)                                                                                                           |

|       | <ul> <li>1 = Enables Receive mode for I<sup>2</sup>C; hardware clear at end of eighth bit of master receive data byte</li> <li>0 = Receive sequence not in progress</li> </ul> |

| bit 2 | <b>PEN:</b> Stop Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                              |

|       | 1 = Initiates Stop condition on SDA1 and SCL1 pins; hardware clear at end of master Stop sequence<br>0 = Stop condition not in progress                                        |

| bit 1 | <b>RSEN:</b> Repeated Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                   |

|       | 1 = Initiates Repeated Start condition on SDA1 and SCL1 pins; hardware clear at end of master Repeated Start sequence                                                          |

|       | 0 = Repeated Start condition not in progress                                                                                                                                   |

| bit 0 | SEN: Start Condition Enable bit (when operating as I <sup>2</sup> C master)                                                                                                    |

|       | <ul> <li>1 = Initiates Start condition on SDA1 and SCL1 pins; hardware clear at end of master Start sequence</li> <li>0 = Start condition not in progress</li> </ul>           |

### FIGURE 19-1: 10-BIT HIGH-SPEED A/D CONVERTER BLOCK DIAGRAM

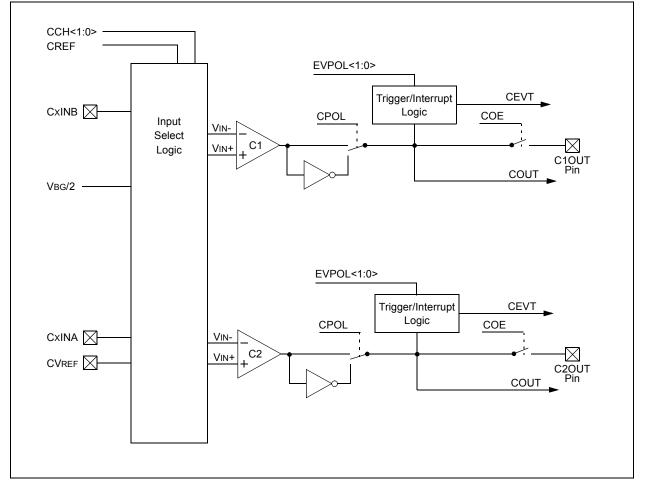

## 20.0 COMPARATOR MODULE

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Comparator module, refer to the *"PIC24F Family Reference Manual"*, Section 19. "Comparator Module" (DS39710).

The comparator module provides two dual input comparators. The inputs to the comparator can be configured to use any one of four external analog inputs, as well as a voltage reference input from either the internal band gap reference divided by 2 (VBG/2) or the comparator voltage reference generator.

The comparator outputs may be directly connected to the CxOUT pins. When the respective COE equals '1', the I/O pad logic makes the unsynchronized output of the comparator available on the pin.

A simplified block diagram of the module is displayed in Figure 20-1. Diagrams of the possible individual comparator configurations are displayed in Figure 20-2.

Each comparator has its own control register, CMxCON (Register 20-1), for enabling and configuring its operation. The output and event status of all three comparators is provided in the CMSTAT register (Register 20-2).

### FIGURE 20-1: COMPARATOR MODULE BLOCK DIAGRAM

| R/P-1                                                                    | U-0 | U-0              | U-0 | U-0               | R/P-1  | R/P-1              | R/P-1  |  |  |

|--------------------------------------------------------------------------|-----|------------------|-----|-------------------|--------|--------------------|--------|--|--|

| IESO                                                                     | —   | _                | —   | —                 | FNOSC2 | FNOSC1             | FNOSC0 |  |  |

| bit 7 bit 0                                                              |     |                  |     |                   |        |                    |        |  |  |

|                                                                          |     |                  |     |                   |        |                    |        |  |  |

| Legend:                                                                  |     |                  |     |                   |        |                    |        |  |  |

| R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0' |     |                  |     | l as '0'          |        |                    |        |  |  |

| -n = Value at POR                                                        |     | '1' = Bit is set |     | '0' = Bit is clea | ared   | x = Bit is unknown |        |  |  |

| bit 7 IESO: Internal External Switchov | ver bit |

|----------------------------------------|---------|

|----------------------------------------|---------|

1 = Internal External Switchover mode enabled (Two-Speed Start-up enabled)

**REGISTER 23-2: FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER**

0 = Internal External Switchover mode disabled (Two-Speed Start-up disabled)

bit 6-3 Unimplemented: Read as '0'

bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

000 = Fast RC oscillator (FRC)

001 = Fast RC oscillator with divide-by-N with PLL module (FRCDIV+PLL)

010 = Primary oscillator (XT, HS, EC)

011 = Primary oscillator with PLL module (HS+PLL, EC+PLL)

100 = Secondary oscillator (SOSC)

101 = Low-Power RC oscillator (LPRC)

110 = 500 kHz Low-Power FRC oscillator with divide-by-N (LPFRCDIV)

111 = 8 MHz FRC oscillator with divide-by-N (FRCDIV)

| R/P-1         | R/P-1                             | U-0                                | U-0            | R/P-1             | R/P-1             | R/P-1           | R/P-1        |

|---------------|-----------------------------------|------------------------------------|----------------|-------------------|-------------------|-----------------|--------------|

| DSWDTEN       | DSLPBOR                           | —                                  |                | DSWDTPS3          | DSWDTPS2          | DSWDTPS1        | DSWDTPS0     |

| bit 7         |                                   |                                    |                |                   |                   |                 | bit 0        |

|               |                                   |                                    |                |                   |                   |                 |              |

| Legend:       |                                   |                                    |                |                   |                   |                 |              |

| R = Readable  | e bit                             | P = Programn                       | hable bit      | U = Unimplem      | nented bit, read  | l as '0'        |              |

| -n = Value at | POR                               | '1' = Bit is set                   |                | '0' = Bit is clea | ared              | x = Bit is unkr | iown         |

|               |                                   |                                    |                |                   |                   |                 |              |

| bit 7         |                                   | eep Sleep Wate                     | chaog Timer E  | nable bit         |                   |                 |              |

|               | 1 = DSWDT er<br>0 = DSWDT di      |                                    |                |                   |                   |                 |              |

| bit 6         | DSLPBOR: De                       | ep Sleep/Low-F                     | Power BOR En   | able bit (does no | ot affect operati | on in non Deep  | Sleep modes) |

|               |                                   | p BOR enabled                      |                |                   |                   |                 |              |

|               | 0 = Deep Slee                     | p BOR disabled                     | l in Deep Slee | p                 |                   |                 |              |

| bit 5-4       | Unimplement                       | ed: Read as '0'                    |                |                   |                   |                 |              |

| bit 3-0       |                                   |                                    | •              | mer Postscale S   |                   |                 |              |

|               |                                   |                                    |                | approximate b     | ase time unit o   | f 1 ms.         |              |

|               |                                   | 7,483,648 (25.7<br>870,912 (6.4 da |                | al                |                   |                 |              |

|               |                                   | 217,728 (38.5 h                    | • •            |                   |                   |                 |              |

|               |                                   | 54,432 (9.6 hou                    | ,              |                   |                   |                 |              |

|               |                                   | 8,608 (2.4 hour                    | ,              |                   |                   |                 |              |

|               |                                   | 7,152 (36 minut                    |                |                   |                   |                 |              |

|               |                                   | 288 (9 minutes)<br>072 (135 secon  |                |                   |                   |                 |              |

|               |                                   | 68 (34 seconds                     | ,              |                   |                   |                 |              |

|               |                                   | 2 (8.5 seconds)                    |                |                   |                   |                 |              |

|               |                                   | 8 (2.1 seconds)                    |                |                   |                   |                 |              |

|               |                                   | (528 ms) nomin                     |                |                   |                   |                 |              |

|               |                                   | (132 ms) nomin                     | al             |                   |                   |                 |              |

|               | 0010 = 1:32(3)<br>0001 = 1:8(8.3) | 3 ms) nominal                      |                |                   |                   |                 |              |

|               | UUUL - 1.0 (0.                    | JIIJJIUUUUU                        |                |                   |                   |                 |              |

## REGISTER 23-7: FDS: DEEP SLEEP CONFIGURATION REGISTER

## 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## 26.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC24F04KA201 family electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24F04KA201 family are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these, or any other conditions above the parameters indicated in the operation listings of this specification, is not implied.

## Absolute Maximum Ratings<sup>(†)</sup>

| Ambient temperature under bias                                     | 40°C to +125°C       |

|--------------------------------------------------------------------|----------------------|

| Storage temperature                                                | 65°C to +150°C       |

| Voltage on VDD with respect to Vss                                 | -0.3V to +5.0V       |

| Voltage on any combined analog and digital pin with respect to Vss | 0.3V to (VDD + 0.3V) |

| Voltage on any digital only pin with respect to Vss                | 0.3V to (VDD + 0.3V) |

| Voltage on MCLR/VPP pin with respect to Vss                        | -0.3V to +9.0V       |

| Maximum current out of Vss pin                                     |                      |

| Maximum current into Vod pin <sup>(1)</sup>                        |                      |

| Maximum output current sunk by any I/O pin                         |                      |

| Maximum output current sourced by any I/O pin                      |                      |

| Maximum current sunk by all ports                                  |                      |

| Maximum current sourced by all ports <sup>(1)</sup>                | 200 mA               |

Note 1: Maximum allowable current is a function of device maximum power dissipation (see Table 26-1).

†NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

### TABLE 26-3: DC CHARACTERISTICS: TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CH        | ARACTER | Standard Operating Conditions: 1.8V to 3.6V (unless otherwise statOperating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |                    |     |       |                                   |

|--------------|---------|-----------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-----|-------|-----------------------------------|

| Param<br>No. | Symbol  | Characteristic                                                                                                                                | Min  | Typ <sup>(1)</sup> | Max | Units | Conditions                        |

| DC10         | Vdd     | Supply Voltage                                                                                                                                | 1.8  | _                  | 3.6 | V     |                                   |

| DC12         | Vdr     | RAM Data Retention<br>Voltage <sup>(2)</sup>                                                                                                  | 1.5  | _                  | —   | V     |                                   |

| DC16         | VPOR    | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal                                                                              | Vss  | —                  | 0.7 | V     |                                   |

| DC17         | Svdd    | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal                                                                           | 0.05 | _                  | _   | V/ms  | 0-3.3V in 0.1s<br>0-2.5V in 60 ms |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: This is the limit to which VDD can be lowered without losing RAM data.

### TABLE 26-4: HIGH/LOW–VOLTAGE DETECT CHARACTERISTICS

## Standard Operating Conditions (unless otherwise stated)

Operating temperature  $-40^{\circ}C \le TA \le +85^{\circ}C$  for industrial

| Param<br>No. | Symbol | Charact             | Min               | Тур  | Max  | Units | Conditions |  |

|--------------|--------|---------------------|-------------------|------|------|-------|------------|--|

| DC18         | Vhlvd  | HLVD Voltage on VDD | HLVDL<3:0> = 0000 | _    | 1.85 | 1.94  | V          |  |

|              |        | Transition          | HLVDL<3:0> = 0001 | 1.81 | 1.90 | 2.00  | V          |  |

|              |        |                     | HLVDL<3:0> = 0010 | 1.85 | 1.95 | 2.05  | V          |  |

|              |        |                     | HLVDL<3:0> = 0011 | 1.90 | 2.00 | 2.10  | V          |  |

|              |        | HLVDL<3:0> = 0100   | 1.95              | 2.05 | 2.15 | V     |            |  |

|              |        |                     | HLVDL<3:0> = 0101 | 2.06 | 2.17 | 2.28  | V          |  |

|              |        |                     | HLVDL<3:0> = 0110 | 2.12 | 2.23 | 2.34  | V          |  |

|              |        |                     | HLVDL<3:0> = 0111 | 2.24 | 2.36 | 2.48  | V          |  |

|              |        |                     | HLVDL<3:0> = 1000 | 2.31 | 2.43 | 2.55  | V          |  |

|              |        |                     | HLVDL<3:0> = 1001 | 2.47 | 2.60 | 2.73  | V          |  |

|              |        |                     | HLVDL<3:0> = 1010 | 2.64 | 2.78 | 2.92  | V          |  |

|              |        |                     | HLVDL<3:0> = 1011 | 2.74 | 2.88 | 3.02  | V          |  |

|              |        |                     | HLVDL<3:0> = 1100 | 2.85 | 3.00 | 3.15  | V          |  |

|              |        |                     | HLVDL<3:0> = 1101 | 2.96 | 3.12 | 3.28  | V          |  |

|              |        |                     | HLVDL<3:0> = 1110 | 3.22 | 3.39 | 3.56  | V          |  |

### TABLE 26-20:PLL CLOCK TIMING SPECIFICATIONS (VDD = 1.8V TO 3.6V)

|              |       |                                  | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |            |     |                             |  |

|--------------|-------|----------------------------------|------------------------------------------------------|---|------------|-----|-----------------------------|--|

| Param<br>No. | Sym   | Characteristic <sup>(1)</sup>    | Min Typ <sup>(2)</sup> Max Units                     |   | Conditions |     |                             |  |

| OS50         | Fplli | PLL Input Frequency Range        | 4                                                    | — | 8          | MHz | ECPLL, HSPLL modes          |  |

| OS51         | Fsys  | PLL Output Frequency Range       | 16                                                   | — | 32         | MHz |                             |  |

| OS52         | TLOCK | PLL Start-up Time<br>(Lock Time) | —                                                    | — | 2          | ms  |                             |  |

| OS53         | DCLK  | CLKO Stability (Jitter)          | -2                                                   | 1 | 2          | %   | Measured over 100 ms period |  |

Note 1: These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

### TABLE 26-21: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| АС СНА       | RACTERISTICS            | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                              |                                                 |  |  |

|--------------|-------------------------|------------------------------------------------------|-----|-----|-------|----------------------------------------------|-------------------------------------------------|--|--|

| Param<br>No. | Characteristic          | Min                                                  | Тур | Max | Units | Units Conditions                             |                                                 |  |  |

|              | Internal FRC Accuracy @ | 2 8 MHz <sup>(1</sup>                                | )   |     |       |                                              |                                                 |  |  |

| F20          | FRC                     | -2                                                   | _   | 2   | %     | +25°C                                        | 3.0V < VDD < 3.6V                               |  |  |

|              |                         | -5                                                   | _   | 5   | %     | $-40^\circ C \le T \text{A} \le +85^\circ C$ | $3.0^{\circ} \leq 0.0^{\circ} \leq 3.0^{\circ}$ |  |  |

Note 1: Frequency calibrated at +25°C and 3.3V. OSCTUN bits can be used to compensate for temperature drift.

### TABLE 26-22: AC CHARACTERISTICS: INTERNAL RC ACCURACY

| AC CHA       | ARACTERISTICS                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |    |      |                                                             |                                                 |  |  |

|--------------|-------------------------------------------------------|------------------------------------------------------|---|----|------|-------------------------------------------------------------|-------------------------------------------------|--|--|

| Param<br>No. | Characteristic   Min   Typ   Max   Units   Conditions |                                                      |   |    | ions |                                                             |                                                 |  |  |

|              | LPRC @ 31 kHz <sup>(1)</sup>                          |                                                      |   |    |      |                                                             |                                                 |  |  |

| F21          |                                                       | -15                                                  | _ | 15 | %    | +25°C                                                       | 3.0V < VDD < 3.6V                               |  |  |

|              |                                                       | -15                                                  | _ | 15 | %    | $\text{-40}^\circ C \leq \text{TA} \leq \text{+85}^\circ C$ | $3.0^{\circ} \ge ^{\circ}$ UU $\ge 3.0^{\circ}$ |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

NOTES:

### U

| UART                                      | 133 |

|-------------------------------------------|-----|

| Baud Rate Generator (BRG)                 |     |

| Break and Sync Transmit Sequence          | 135 |

| IrDA Support                              |     |

| Operation of U1CTS and U1RTS Control Pins | 135 |

| Receiving in 8-Bit or 9-Bit Data Mode     | 135 |

| Transmitting in 8-Bit Data Mode           |     |

| Transmitting in 9-Bit Data Mode           |     |

## W

| Watchdog Timer       |     |

|----------------------|-----|

| Deep Sleep (DSWDT)   | 171 |

| Watchdog Timer (WDT) | 170 |

| Windowed Operation   | 170 |

| WWW Address          | 218 |

| WWW, On-Line Support | 5   |