Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Detalls                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 12                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 7x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 14-TSSOP (0.173", 4.40mm Width)                                              |

| Supplier Device Package    | 14-TSSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04ka200-i-st |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

|         | Device Overview                                             |       |

|---------|-------------------------------------------------------------|-------|

| 2.0 0   | Suidelines for Getting Started with 16-Bit Microcontrollers | 15    |

| 3.0 C   |                                                             | 19    |

| 4.0 N   | Nemory Organization                                         | 25    |

| 5.0 F   | Flash Program Memory                                        | 43    |

|         | Resets                                                      |       |

| 7.0 li  | nterrupt Controller                                         | 57    |

| 8.0 C   | Dscillator Configuration                                    | 81    |

| 9.0 F   | Power-Saving Features                                       | 91    |

| 10.0 l/ | /O Ports                                                    | 99    |

| 11.0 T  | Fimer1                                                      | . 101 |

| 12.0 T  | Fimer2/3                                                    | . 103 |

| 13.0 lı | nput Capture                                                | . 109 |

|         | Dutput Compare                                              |       |

|         | Serial Peripheral Interface (SPI)                           |       |

|         | nter-Integrated Circuit (I <sup>2</sup> C™)                 |       |

|         | Jniversal Asynchronous Receiver Transmitter (UART)          |       |

|         | High/Low-Voltage Detect (HLVD)                              |       |

|         | 0-Bit High-Speed A/D Converter                              |       |

|         | Comparator Module                                           |       |

|         | Comparator Voltage Reference                                |       |

|         | Charge Time Measurement Unit (CTMU)                         |       |

|         | Special Features                                            |       |

| 24.0 C  | Development Support                                         | . 173 |

|         | nstruction Set Summary                                      |       |

| 26.0 E  | Electrical Characteristics                                  | . 185 |

|         | Packaging Information                                       |       |

| Append  | dix A: Revision History                                     | . 213 |

|         |                                                             |       |

|         | crochip Web Site                                            |       |

|         | ner Change Notification Service                             |       |

|         | ner Support                                                 |       |

| Produc  | t Identification System                                     | . 221 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### Customer Notification System

Register on our web site at www.microchip.com to receive the most current information on all of our products.

## 2.2 Power Supply Pins

#### 2.2.1 DECOUPLING CAPACITORS

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS, is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A 0.1  $\mu$ F (100 nF), 10-20V capacitor is recommended. The capacitor should be a low-ESR device with a resonance frequency in the range of 200 MHz and higher. Ceramic capacitors are recommended.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is no greater than 0.25 inch (6 mm).

- Handling high-frequency noise: If the board is experiencing high-frequency noise (upward of tens of MHz), add a second ceramic type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to each primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible (e.g., 0.1  $\mu$ F in parallel with 0.001  $\mu$ F).

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB trace inductance.

#### 2.2.2 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including microcontrollers to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

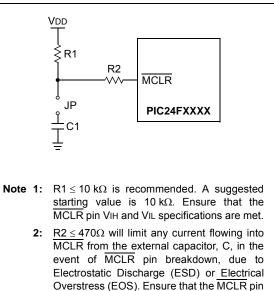

## 2.3 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions: device Reset, and device programming and debugging. If programming and debugging are not required in the end application, a direct connection to VDD may be all that is required. The addition of other components, to help increase the application's resistance to spurious Resets from voltage sags, may be beneficial. A typical configuration is shown in Figure 2-1. Other circuit designs may be implemented depending on the application's requirements.

During programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R1 and C1 will need to be adjusted based on the application and PCB requirements. For example, it is recommended that the capacitor, C1, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations by using a jumper (Figure 2-2). The jumper is replaced for normal run-time operations.

Any components associated with the  $\overline{\text{MCLR}}$  pin should be placed within 0.25 inch (6 mm) of the pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

VIH and VIL specifications are met.

## 3.0 CPU

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the CPU, refer to the "PIC24F Family Reference Manual", Section 2. "CPU" (DS39703).

The PIC24F CPU has a 16-bit (data) modified Harvard architecture with an enhanced instruction set and a 24-bit instruction word with a variable length opcode field. The Program Counter (PC) is 23 bits wide and addresses up to 4M instructions of user program memory space. A single-cycle instruction prefetch mechanism is used to help maintain throughput and provides predictable execution. All instructions execute in a single cycle, with the exception of instructions that change the program flow, the double-word move (MOV.D) instruction and the table instructions. Overhead-free program loop constructs are supported using the REPEAT instructions, which are interruptible at any point.

PIC24F devices have sixteen, 16-bit working registers in the programmer's model. Each of the working registers can act as a data, address or address offset register. The 16<sup>th</sup> working register (W15) operates as a Software Stack Pointer (SSP) for interrupts and calls.

The upper 32 Kbytes of the data space memory map can optionally be mapped into program space at any 16K word boundary of program memory defined by the 8-bit Program Space Visibility Page Address (PSVPAG) register. The program to data space mapping feature lets any instruction access program space as if it were data space.

The Instruction Set Architecture (ISA) has been significantly enhanced beyond that of the PIC18, but maintains an acceptable level of backward compatibility. All PIC18 instructions and addressing modes are supported, either directly, or through simple macros. Many of the ISA enhancements have been driven by compiler efficiency needs.

The core supports Inherent (no operand), Relative, Literal, Memory Direct and three groups of addressing modes. All modes support Register Direct and various Register Indirect modes. Each group offers up to seven addressing modes. Instructions are associated with predefined addressing modes depending upon their functional requirements. For most instructions, the core is capable of executing a data (or program data) memory read, a working register (data) read, a data memory write and a program (instruction) memory read per instruction cycle. As a result, three parameter instructions can be supported, allowing trinary operations (that is, A + B = C) to be executed in a single cycle.

A high-speed, 17-bit by 17-bit multiplier has been included to significantly enhance the core arithmetic capability and throughput. The multiplier supports Signed, Unsigned and Mixed mode, 16-bit by 16-bit or 8-bit by 8-bit integer multiplication. All multiply instructions execute in a single cycle.

The 16-bit ALU has been enhanced with integer divide assist hardware that supports an iterative non-restoring divide algorithm. It operates in conjunction with the REPEAT instruction looping mechanism and a selection of iterative divide instructions to support 32-bit (or 16-bit), divided by 16-bit integer signed and unsigned division. All divide operations require 19 cycles to complete but are interruptible at any cycle boundary.

The PIC24F has a vectored exception scheme with up to eight sources of non-maskable traps and up to 118 interrupt sources. Each interrupt source can be assigned to one of seven priority levels.

A block diagram of the CPU is illustrated in Figure 3-1.

## 3.1 Programmer's Model

Figure 3-2 displays the programmer's model for the PIC24F. All registers in the programmer's model are memory mapped and can be manipulated directly by instructions.

Table 3-1 provides a description of each register. All registers associated with the programmer's model are memory mapped.

## 3.3.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn), and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

## 3.3.3 MULTI-BIT SHIFT SUPPORT

The PIC24F ALU supports both single bit and single-cycle, multi-bit arithmetic and logic shifts. Multi-bit shifts are implemented using a shifter block, capable of performing up to a 15-bit arithmetic right shift, or up to a 15-bit left shift, in a single cycle. All multi-bit shift instructions only support Register Direct Addressing for both the operand source and result destination.

A full summary of instructions that use the shift operation is provided below in Table 3-2.

### TABLE 3-2: INSTRUCTIONS THAT USE THE SINGLE AND MULTI-BIT SHIFT OPERATION

| Instruction | nstruction Description                                      |  |  |  |

|-------------|-------------------------------------------------------------|--|--|--|

| ASR         | Arithmetic shift right source register by one or more bits. |  |  |  |

| SL          | Shift left source register by one or more bits.             |  |  |  |

| LSR         | Logical shift right source register by one or more bits.    |  |  |  |

| TABLE 4-3: | CPU CORE REGISTERS MAP |  |

|------------|------------------------|--|

| IABLE        | 4-3. | CFUC   |        | EGISTE |        |        |        |        |             |               |           |             |                |             |             |       |       |               |

|--------------|------|--------|--------|--------|--------|--------|--------|--------|-------------|---------------|-----------|-------------|----------------|-------------|-------------|-------|-------|---------------|

| File<br>Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8       | Bit 7         | Bit 6     | Bit 5       | Bit 4          | Bit 3       | Bit 2       | Bit 1 | Bit 0 | All<br>Resets |

| WREG0        | 0000 |        |        |        |        |        |        |        | Working     | Register 0    |           |             |                |             |             |       |       | 0000          |

| WREG1        | 0002 |        |        |        |        |        |        |        | Working     | Register 1    |           |             |                |             |             |       |       | 0000          |

| WREG2        | 0004 |        |        |        |        |        |        |        | Working     | Register 2    |           |             |                |             |             |       |       | 0000          |

| WREG3        | 0006 |        |        |        |        |        |        |        | Working     | Register 3    |           |             |                |             |             |       |       | 0000          |

| WREG4        | 0008 |        |        |        |        |        |        |        | Working     | Register 4    |           |             |                |             |             |       |       | 0000          |

| WREG5        | 000A |        |        |        |        |        |        |        | Working     | Register 5    |           |             |                |             |             |       |       | 0000          |

| WREG6        | 000C |        |        |        |        |        |        |        | Working     | Register 6    |           |             |                |             |             |       |       | 0000          |

| WREG7        | 000E |        |        |        |        |        |        |        | Working     | Register 7    |           |             |                |             |             |       |       | 0000          |

| WREG8        | 0010 |        |        |        |        |        |        |        | Working     | Register 8    |           |             |                |             |             |       |       | 0000          |

| WREG9        | 0012 |        |        |        |        |        |        |        | Working     | Register 9    |           |             |                |             |             |       |       | 0000          |

| WREG10       | 0014 |        |        |        |        |        |        |        | Working F   | Register 10   |           |             |                |             |             |       |       | 0000          |

| WREG11       | 0016 |        |        |        |        |        |        |        | Working F   | Register 11   |           |             |                |             |             |       |       | 0000          |

| WREG12       | 0018 |        |        |        |        |        |        |        | Working F   | Register 12   |           |             |                |             |             |       |       | 0000          |

| WREG13       | 001A |        |        |        |        |        |        |        | Working F   | Register 13   |           |             |                |             |             |       |       | 0000          |

| WREG14       | 001C |        |        |        |        |        |        |        | Working F   | Register 14   |           |             |                |             |             |       |       | 0000          |

| WREG15       | 001E |        |        |        |        |        |        |        | Working F   | Register 15   |           |             |                |             |             |       |       | 0800          |

| SPLIM        | 0020 |        |        |        |        |        |        | Stack  | Pointer Lin | nit Value Re  | egister   |             |                |             |             |       |       | xxxx          |

| PCL          | 002E |        |        |        |        |        |        | Progra | am Counter  | Low Byte R    | Register  |             |                |             |             |       |       | 0000          |

| PCH          | 0030 | —      | —      | _      | _      | _      | _      | —      | —           |               |           | Progra      | m Counter      | Register Hi | gh Byte     |       |       | 0000          |

| TBLPAG       | 0032 | —      | —      | _      | _      | _      | _      | —      | —           |               |           | Table N     | lemory Pag     | e Address   | Register    |       |       | 0000          |

| PSVPAG       | 0034 | —      | —      | _      | _      | _      | _      | —      | —           |               | P         | Program Spa | ace Visibility | / Page Add  | ress Regist | er    |       | 0000          |

| RCOUNT       | 0036 |        |        |        |        |        |        | REP    | EAT Loop (  | Counter Reg   | gister    |             |                |             |             |       |       | xxxx          |

| SR           | 0042 | —      | —      | —      | —      | —      | —      | —      | DC          | IPL2          | IPL1      | IPL0        | RA             | Ν           | OV          | Z     | С     | 0000          |

| CORCON       | 0044 | _      | _      | _      | _      | _      | _      | _      | —           | _             | _         | _           | —              | IPL3        | PSV         | _     | _     | 0000          |

| DISICNT      | 0052 | _      | _      |        |        |        |        |        | Disab       | le Interrupts | Counter R | egister     |                |             |             |       |       | xxxx          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

NOTES:

## 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Interrupt Controller, refer to the "PIC24F Family Reference Manual", Section 8. "Interrupts" (DS39707).

The PIC24F interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the CPU. It has the following features:

- Up to eight processor exceptions and software traps

- · Seven user-selectable priority levels

- · Interrupt Vector Table (IVT) with up to 118 vectors

- Unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- · Fixed interrupt entry and return latencies

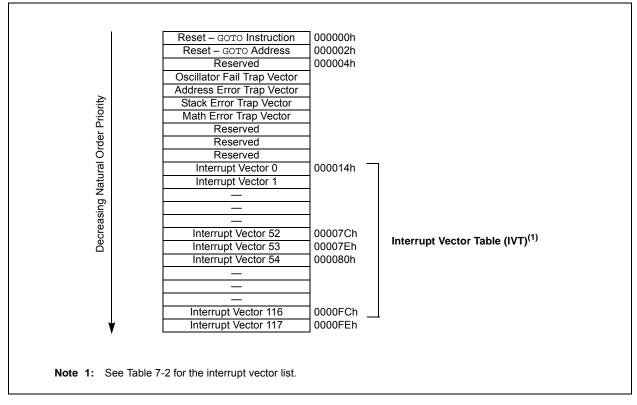

## 7.1 Interrupt Vector (IVT) Table

The IVT is displayed in Figure 7-1. The IVT resides in the program memory, starting at location 000004h. The IVT contains 126 vectors, consisting of eight non-maskable trap vectors, plus, up to 118 sources of interrupt. In general, each interrupt source has its own vector.

Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24F04KA201 family devices implement non-maskable traps and unique interrupts; these are summarized in Table 7-1 and Table 7-2.

## 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24F devices clear their registers in response to a Reset, which forces the Program Counter (PC) to zero. The microcontroller then begins program execution at location 000000h. The user programs a GOTO instruction at the Reset address, which redirects the program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

### FIGURE 7-1: PIC24F INTERRUPT VECTOR TABLE

| U-0          | U-0           | R/W-0                           | U-0        | U-0               | U-0             | U-0             | U-0     |

|--------------|---------------|---------------------------------|------------|-------------------|-----------------|-----------------|---------|

|              |               | INT2IE                          |            | —                 |                 | —               | _       |

| bit 15       | ·             |                                 |            |                   |                 |                 | bit 8   |

|              |               |                                 |            |                   |                 |                 |         |

| U-0          | U-0           | U-0                             | R/W-0      | R/W-0             | R/W-0           | R/W-0           | R/W-0   |

|              | —             | —                               | INT1IE     | CNIE              | CMIE            | MI2C1IE         | SI2C1IE |

| bit 7        |               |                                 |            |                   |                 |                 | bit (   |

| Legend:      |               |                                 |            |                   |                 |                 |         |

| R = Readab   | ole bit       | W = Writable                    | bit        | U = Unimplem      | ented bit, read | d as '0'        |         |

| -n = Value a | t POR         | '1' = Bit is set                |            | '0' = Bit is clea | ared            | x = Bit is unkn | iown    |

|              |               |                                 |            |                   |                 |                 |         |

| bit 15-14    | Unimplemen    | ted: Read as '                  | 0'         |                   |                 |                 |         |

| bit 13       | INT2IE: Exter | mal Interrupt 2                 | Enable bit |                   |                 |                 |         |

|              |               | equest enable                   |            |                   |                 |                 |         |

|              | •             | request not ena                 |            |                   |                 |                 |         |

| bit 12-5     | •             | ted: Read as '                  |            |                   |                 |                 |         |

| bit 4        |               | mal Interrupt 1                 |            |                   |                 |                 |         |

|              |               | equest enable                   |            |                   |                 |                 |         |

|              | •             | request not ena                 |            |                   |                 |                 |         |

| bit 3        | •             | Change Notifica                 |            | nable bit         |                 |                 |         |

|              |               | equest enable<br>equest not ena |            |                   |                 |                 |         |

| bit 2        | •             | arator Interrupt                |            |                   |                 |                 |         |

| DILZ         |               | request enable                  |            |                   |                 |                 |         |

|              |               | request enable                  |            |                   |                 |                 |         |

| bit 1        | •             | ster I2C1 Even                  |            | hle Status hit    |                 |                 |         |

|              |               | request has oc                  | •          |                   |                 |                 |         |

|              |               | request has not                 |            |                   |                 |                 |         |

| bit 0        |               | ve I2C1 Event                   |            | e Status bit      |                 |                 |         |

| -            |               | request has oc                  | -          |                   |                 |                 |         |

|              |               | equest has occ                  | uneu       |                   |                 |                 |         |

## REGISTER 7-9: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

## 12.0 TIMER2/3

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer2/3 module is a 32-bit timer, which can also be configured as two independent 16-bit timers with selectable operating modes.

As a 32-bit timer, Timer2/3 operates in three modes:

- Two independent 16-bit timers (Timer2 and Timer3) with all 16-bit operating modes (except Asynchronous Counter mode)

- · Single 32-bit timer

- · Single 32-bit synchronous counter

- They also support these features:

- Timer gate operation

- Selectable prescaler settings

- · Timer operation during Idle and Sleep modes

- · Interrupt on a 32-bit Period register match

- ADC Event Trigger

Individually, both of the 16-bit timers can function as synchronous timers or counters. They also offer the features listed above, except for the ADC event trigger (this is implemented only with Timer3). The operating modes and enabled features are determined by setting the appropriate bit(s) in the T2CON and T3CON registers. T2CON and T3CON are provided in generic form in Register 12-1 and Register 12-2, respectively.

For 32-bit timer/counter operation, Timer2 is the least significant word (lsw) and Timer3 is the most significant word (msw) of the 32-bit timer.

| Note: | For 32-bit operation, T3CON control bits     |

|-------|----------------------------------------------|

|       | are ignored. Only T2CON control bits are     |

|       | used for setup and control. Timer2 clock     |

|       | and gate inputs are utilized for the 32-bit  |

|       | timer modules, but an interrupt is generated |

|       | with the Timer3 interrupt flags.             |

To configure Timer2/3 for 32-bit operation:

- 1. Set the T32 bit (T2CON<3> = 1).

- 2. Select the prescaler ratio for Timer2 using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value. PR3 will contain the msw of the value while PR2 contains the lsw.

- 5. If interrupts are required, set the interrupt enable bit, T3IE; use the priority bits, T3IP<2:0>, to set the interrupt priority.

While Timer2 controls the timer, the interrupt appears as a Timer3 interrupt.

6. Set the TON bit (= 1).

The timer value, at any point, is stored in the register pair, TMR<3:2>. TMR3 always contains the msw of the count, while TMR2 contains the lsw.

To configure any of the timers for individual 16-bit operation:

- 1. Clear the T32 bit in T2CON<3>.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits.

- 4. Load the timer period value into the PRx register.

- 5. If interrupts are required, set the interrupt enable bit, TxIE; use the priority bits, TxIP<2:0>, to set the interrupt priority.

- 6. Set the TON bit (TxCON<15> = 1).

| R/W-0              | U-0                            | R/W-0                       | U-0                   | U-0                          | U-0           | U-0                | U-0             |

|--------------------|--------------------------------|-----------------------------|-----------------------|------------------------------|---------------|--------------------|-----------------|

| TON <sup>(1)</sup> |                                | TSIDL <sup>(1)</sup>        | _                     | _                            |               |                    |                 |

| bit 15             |                                |                             |                       |                              |               |                    | bit 8           |

|                    |                                |                             |                       |                              |               |                    |                 |

| U-0                | R/W-0                          | R/W-0                       | R/W-0                 | U-0                          | U-0           | R/W-0              | U-0             |

| _                  | TGATE <sup>(1)</sup>           | TCKPS1 <sup>(1)</sup>       | TCKPS0 <sup>(1)</sup> | —                            |               | TCS <sup>(1)</sup> |                 |

| bit 7              |                                |                             |                       |                              |               |                    | bit 0           |

|                    |                                |                             |                       |                              |               |                    |                 |

| Legend:            | bla b:t                        |                             | -:4                   |                              | antad bit was | d aa '0'           |                 |

| R = Readal         |                                | W = Writable                | JIC                   | U = Unimplem                 |               |                    |                 |

| -n = Value a       | at POR                         | '1' = Bit is set            |                       | '0' = Bit is clea            | red           | x = Bit is unkno   | own             |

| bit 15             | TON: Timer3                    | On hit(1)                   |                       |                              |               |                    |                 |

| DIL 15             | 1 = Starts 16                  |                             |                       |                              |               |                    |                 |

|                    | 0 = Stops 16                   |                             |                       |                              |               |                    |                 |

| bit 14             | Unimplemen                     | ted: Read as 'o             | )'                    |                              |               |                    |                 |

| bit 13             | TSIDL: Stop i                  | n Idle Mode bit             | (1)                   |                              |               |                    |                 |

|                    |                                |                             |                       | vice enters Idle             | mode          |                    |                 |

|                    | 0 = Continue                   | module operati              | on in Idle mod        | e                            |               |                    |                 |

| bit 12-7           | •                              | ted: Read as '0             |                       |                              |               |                    |                 |

| bit 6              |                                | er3 Gated Time              | Accumulation          | Enable bit <sup>(1)</sup>    |               |                    |                 |

|                    | When TCS =                     |                             |                       |                              |               |                    |                 |

|                    | This bit is igno<br>When TCS = |                             |                       |                              |               |                    |                 |

|                    |                                | <u>o.</u><br>ne accumulatio | n enabled             |                              |               |                    |                 |

|                    |                                | ne accumulatio              |                       |                              |               |                    |                 |

| bit 5-4            | TCKPS<1:0>                     | : Timer3 Input (            | Clock Prescale        | e Select bits <sup>(1)</sup> |               |                    |                 |

|                    | 11 = 1:256                     |                             |                       |                              |               |                    |                 |

|                    | 10 = 1:64                      |                             |                       |                              |               |                    |                 |

|                    | 01 = 1:8<br>00 = 1:1           |                             |                       |                              |               |                    |                 |

| bit 3-2            |                                | ted: Read as '0             | )'                    |                              |               |                    |                 |

| bit 1              | •                              | Clock Source S              |                       |                              |               |                    |                 |

|                    |                                | clock from the              |                       | he rising edge)              |               |                    |                 |

|                    | 0 = Internal o                 |                             |                       | 5 5 7                        |               |                    |                 |

| bit 0              | Unimplemen                     | ted: Read as 'o             | )'                    |                              |               |                    |                 |

| Note 1:            | When 32-bit operation          | ation is enabled            | (T2CON<3>=            | = 1) these hits h            | ave no effect | on Timor? opora    | tion: all timor |

## REGISTER 12-2: T3CON: TIMER3 CONTROL REGISTER

**Note 1:** When 32-bit operation is enabled (T2CON<3> = 1), these bits have no effect on Timer3 operation; all timer functions are set through T2CON.

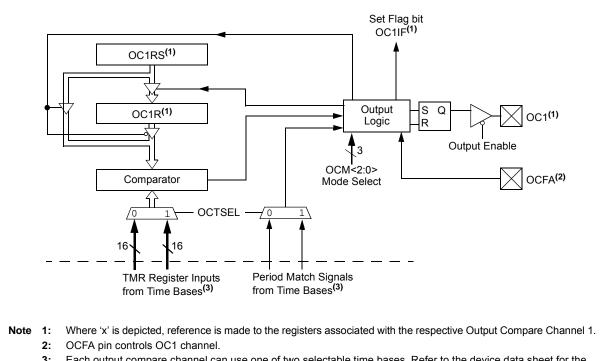

**3:** Each output compare channel can use one of two selectable time bases. Refer to the device data sheet for the time bases associated with the module.

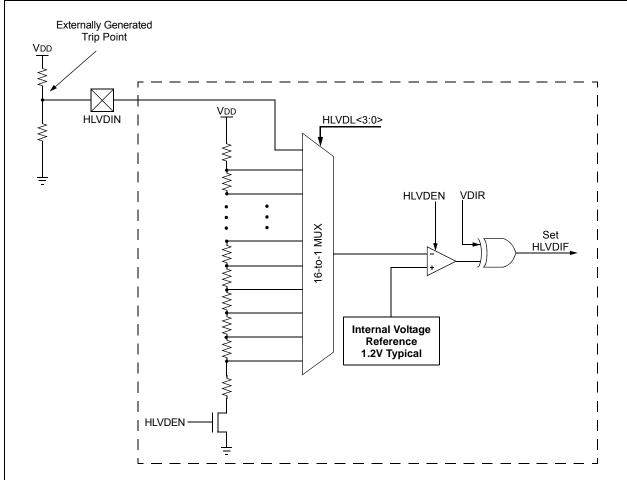

## 18.0 HIGH/LOW-VOLTAGE DETECT (HLVD)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the High/Low-Voltage Detect, refer to the "PIC24F Family Reference Manual", Section 36. "High-Level Integration with Programmable High/Low-Voltage Detect (HLVD)" (DS39725).

The High/Low-Voltage Detect module (HLVD) is a programmable circuit that allows the user to specify both the device voltage trip point and the direction of change.

An interrupt flag is set if the device experiences an excursion past the trip point in the direction of change. If the interrupt is enabled, the program execution will branch to the interrupt vector address and the software can then respond to the interrupt.

The HLVD Control register (see Register 18-1) completely controls the operation of the HLVD module. This allows the circuitry to be "turned off" by the user under software control, which minimizes the current consumption for the device.

## FIGURE 18-1: HIGH/LOW-VOLTAGE DETECT (HLVD) MODULE BLOCK DIAGRAM

| U-0               | U-0                                                                                                         | U-0                                                       | U-0                                                                                                                             | U-0                                          | U-0             | U-0             | U-0   |

|-------------------|-------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------|-----------------|-------|

| _                 | _                                                                                                           | _                                                         | —                                                                                                                               | _                                            | —               |                 | —     |

| bit 15            |                                                                                                             |                                                           | ·                                                                                                                               |                                              |                 | ·               | bit   |

| R/W-0             | R/W-0                                                                                                       | R/W-0                                                     | R/W-0                                                                                                                           | R/W-0                                        | R/W-0           | R/W-0           | R/W-0 |

| CVREN             | CVROE                                                                                                       | CVRR                                                      | CVRSS                                                                                                                           | CVR3                                         | CVR2            | CVR1            | CVR0  |

| bit 7             | •                                                                                                           |                                                           |                                                                                                                                 |                                              |                 |                 | bit   |

| Legend:           |                                                                                                             |                                                           |                                                                                                                                 |                                              |                 |                 |       |

| R = Readab        | le bit                                                                                                      | W = Writable                                              | bit                                                                                                                             | U = Unimplem                                 | nented bit, rea | d as '0'        |       |

| -n = Value a      | It POR                                                                                                      | '1' = Bit is set                                          |                                                                                                                                 | '0' = Bit is clea                            | ared            | x = Bit is unkr | nown  |

| bit 15-8<br>bit 7 | -                                                                                                           | nted: Read as '<br>nparator Voltag                        |                                                                                                                                 | nable bit                                    |                 |                 |       |

|                   | 1 = CVREF C                                                                                                 | ircuit powered o                                          | on                                                                                                                              |                                              |                 |                 |       |

| bit 6             | 1 = CVREF V                                                                                                 | nparator VREF (<br>oltage level is o<br>oltage level is d | utput on CVRE                                                                                                                   | F pin                                        |                 |                 |       |

| bit 5             | CVRR: Comp<br>1 = CVRSRC                                                                                    | parator VREF Ra                                           | ange Selection<br>e 0 to 0.625 C                                                                                                | -                                            |                 |                 |       |

| bit 4             | 1 = Compara                                                                                                 |                                                           | ource CVRSRC                                                                                                                    | on bit<br>: = VREF+ – VRE<br>: = AVDD – AVSS |                 |                 |       |

| bit 3-0           | CVR3:CVR0<br>When CVRR<br>CVREF = (CV<br>When CVRR<br>CVREF = 1/4<br>When CVRR<br>CVREF = ((CV<br>When CVRR |                                                           | REF Value Sele<br><u>S = 0:</u><br>CVRSRC)<br><u>S = 0:</u><br>/R<3:0>/32) *<br><u>S = 1:</u><br>CVRSRC)) + VF<br><u>S = 1:</u> | ection 0 ≤ CVR<<br>(CVRSRC)<br>REF-          | <3:0> ≤ 15 bits |                 |       |

### REGISTER 21-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

## 24.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16 and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 24.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 24.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 24.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

### TABLE 25-2: INSTRUCTION SET OVERVIEW (CONTINUED)

| Assembly<br>Mnemonic |        | Assembly Syntax | Description                             | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|----------------------|--------|-----------------|-----------------------------------------|---------------|----------------|--------------------------|

| PWRSAV               | PWRSAV | #lit1           | Go into Sleep or Idle mode              | 1             | 1              | WDTO, Sleep              |

| RCALL                | RCALL  | Expr            | Relative Call                           | 1             | 2              | None                     |

|                      | RCALL  | Wn              | Computed Call                           | 1             | 2              | None                     |

| REPEAT               | REPEAT | #lit14          | Repeat Next Instruction lit14 + 1 times | 1             | 1              | None                     |

|                      | REPEAT | Wn              | Repeat Next Instruction (Wn) + 1 times  | 1             | 1              | None                     |

| RESET                | RESET  |                 | Software Device Reset                   | 1             | 1              | None                     |

| RETFIE               | RETFIE |                 | Return from Interrupt                   | 1             | 3 (2)          | None                     |

| RETLW                | RETLW  | #lit10,Wn       | Return with Literal in Wn               | 1             | 3 (2)          | None                     |

| RETURN               | RETURN |                 | Return from Subroutine                  | 1             | 3 (2)          | None                     |

| RLC                  | RLC    | f               | f = Rotate Left through Carry f         | 1             | 1              | C, N, Z                  |

|                      | RLC    | f,WREG          | WREG = Rotate Left through Carry f      | 1             | 1              | C, N, Z                  |

|                      | RLC    | Ws,Wd           | Wd = Rotate Left through Carry Ws       | 1             | 1              | C, N, Z                  |

| RLNC                 | RLNC   | f               | f = Rotate Left (No Carry) f            | 1             | 1              | N, Z                     |

|                      | RLNC   | f,WREG          | WREG = Rotate Left (No Carry) f         | 1             | 1              | N, Z                     |

|                      | RLNC   | Ws,Wd           | Wd = Rotate Left (No Carry) Ws          | 1             | 1              | N, Z                     |

| RRC                  | RRC    | f               | f = Rotate Right through Carry f        | 1             | 1              | C, N, Z                  |

|                      | RRC    | f,WREG          | WREG = Rotate Right through Carry f     | 1             | 1              | C, N, Z                  |

|                      | RRC    | Ws,Wd           | Wd = Rotate Right through Carry Ws      | 1             | 1              | C, N, Z                  |

| RRNC                 | RRNC   | f               | f = Rotate Right (No Carry) f           | 1             | 1              | N, Z                     |

| lauto                | RRNC   | f,WREG          | WREG = Rotate Right (No Carry) f        | 1             | 1              | N, Z                     |

|                      | RRNC   | Ws,Wd           | Wd = Rotate Right (No Carry) Ws         | 1             | 1              | N, Z                     |

| SE                   | SE     | Ws, Wnd         | Wnd = Sign-Extended Ws                  | 1             | 1              | C, N, Z                  |

| SETM                 | SETM   | f               | f = FFFFh                               | 1             | 1              | None                     |

| 3E1M                 | SETM   | WREG            | WREG = FFFFh                            | 1             | 1              | None                     |

|                      | SETM   | WREG            | Ws = FFFFh                              | 1             | 1              | None                     |

| SL                   | SLIM   | f               | f = Left Shift f                        | 1             | 1              | C, N, OV, Z              |

| 21                   | SL     |                 | WREG = Left Shift f                     | 1             | 1              | C, N, OV, Z              |

|                      | -      | f,WREG          | WREG - Left Shift Ws                    | 1             | 1              |                          |

|                      | SL     | Ws,Wd           |                                         |               |                | C, N, OV, Z              |

|                      | SL     | Wb,Wns,Wnd      | Wnd = Left Shift Wb by Wns              | 1             | 1              | N, Z                     |

|                      | SL     | Wb,#lit5,Wnd    | Wnd = Left Shift Wb by lit5             | 1             | 1              | N, Z                     |

| SUB                  | SUB    | f               | f = f – WREG                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | f,WREG          | WREG = f – WREG                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | #lit10,Wn       | Wn = Wn – lit10                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,Ws,Wd        | Wd = Wb – Ws                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUB    | Wb,#lit5,Wd     | Wd = Wb – lit5                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBB                 | SUBB   | f               | $f = f - WREG - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | f,WREG          | WREG = $f - WREG - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | #lit10,Wn       | $Wn = Wn - lit10 - (\overline{C})$      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,Ws,Wd        | $Wd = Wb - Ws - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBB   | Wb,#lit5,Wd     | $Wd = Wb - lit5 - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SUBR                 | SUBR   | f               | f = WREG – f                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | f,WREG          | WREG = WREG – f                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,Ws,Wd        | Wd = Ws – Wb                            | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBR   | Wb,#lit5,Wd     | Wd = lit5 – Wb                          | 1             | 1              | C, DC, N, OV, Z          |

| SUBBR                | SUBBR  | f               | $f = WREG - f - (\overline{C})$         | 1             | 1              | C, DC, N, OV, Z          |

| JULIA                |        |                 | $WREG = WREG - f - (\overline{C})$      |               |                |                          |

|                      | SUBBR  | f,WREG          |                                         | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,Ws,Wd        | Wd = Ws - Wb - (C)                      | 1             | 1              | C, DC, N, OV, Z          |

|                      | SUBBR  | Wb,#lit5,Wd     | $Wd = lit5 - Wb - (\overline{C})$       | 1             | 1              | C, DC, N, OV, Z          |

| SWAP                 | SWAP.b | Wn              | Wn = Nibble Swap Wn                     | 1             | 1              | None                     |

|                      | SWAP   | Wn              | Wn = Byte Swap Wn                       | 1             | 1              | None                     |

| TBLRDH               | TBLRDH | Ws,Wd           | Read Prog<23:16> to Wd<7:0>             | 1             | 2              | None                     |

## 26.2 AC Characteristics and Timing Parameters

The information contained in this section defines the PIC24F04KA201 family AC characteristics and timing parameters.

#### TABLE 26-17: TEMPERATURE AND VOLTAGE SPECIFICATIONS – AC

|                    | Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)          |

|--------------------|--------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial    |

|                    | Operating voltage VDD range as described in Section 26.1 "DC Characteristics". |

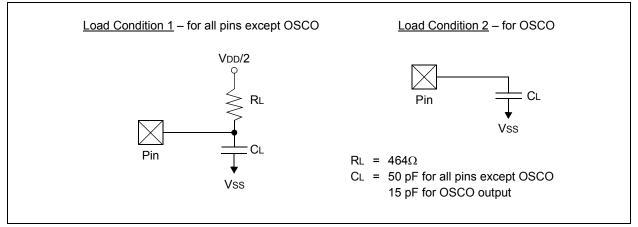

### FIGURE 26-2: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 26-18: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| Param<br>No. | Symbol | Characteristic        | Min | Typ <sup>(1)</sup> | Max | Units | Conditions                                                         |

|--------------|--------|-----------------------|-----|--------------------|-----|-------|--------------------------------------------------------------------|

| DO50         | Cosc2  | OSCO/CLKO Pin         | _   | —                  | 15  | pF    | In XT and HS modes when<br>external clock is used to drive<br>OSCI |

| DO56         | Сю     | All I/O Pins and OSCO | —   | —                  | 50  | pF    | EC mode                                                            |

| DO58         | Св     | SCLx, SDAx            | —   | —                  | 400 | pF    | In l <sup>2</sup> C™ mode                                          |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

20-Lead SSOP

Example

## 20-Lead SOIC (.300")

Example

20-Lead QFN

Example

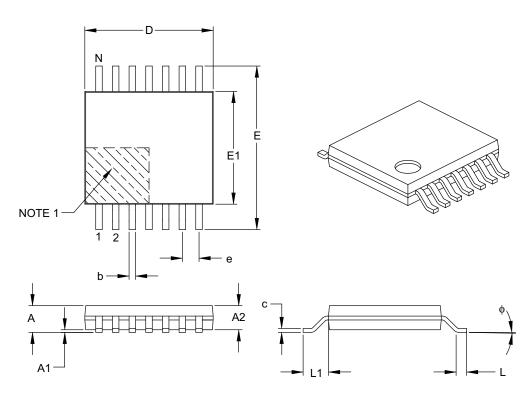

## 14-Lead Plastic Thin Shrink Small Outline (ST) – 4.4 mm Body [TSSOP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units | MILLIMETERS |      |      |

|--------------------------|-------|-------------|------|------|

| Dimension Limits         |       | MIN         | NOM  | MAX  |

| Number of Pins           | N     | 14          |      |      |

| Pitch                    | е     | 0.65 BSC    |      |      |

| Overall Height           | А     | -           | -    | 1.20 |

| Molded Package Thickness | A2    | 0.80        | 1.00 | 1.05 |

| Standoff                 | A1    | 0.05        | -    | 0.15 |

| Overall Width            | E     | 6.40 BSC    |      |      |

| Molded Package Width     | E1    | 4.30        | 4.40 | 4.50 |

| Molded Package Length    | D     | 4.90        | 5.00 | 5.10 |

| Foot Length              | L     | 0.45        | 0.60 | 0.75 |

| Footprint                | L1    | 1.00 REF    |      |      |

| Foot Angle               | ф     | 0°          | -    | 8°   |

| Lead Thickness           | С     | 0.09        | -    | 0.20 |

| Lead Width               | b     | 0.19        | _    | 0.30 |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-087B

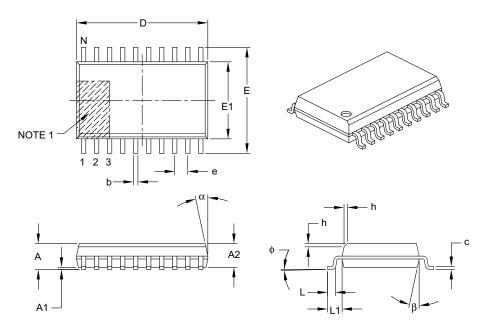

## 20-Lead Plastic Small Outline (SO) – Wide, 7.50 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                    |    | MILLIMETERS |     |      |

|--------------------------|----|-------------|-----|------|

| Dimension Limits         |    | MIN         | NOM | MAX  |

| Number of Pins           | N  | 20          |     |      |

| Pitch                    | е  | 1.27 BSC    |     |      |

| Overall Height           | A  | -           | -   | 2.65 |

| Molded Package Thickness | A2 | 2.05        | -   | -    |

| Standoff §               | A1 | 0.10        | -   | 0.30 |

| Overall Width            | E  | 10.30 BSC   |     |      |

| Molded Package Width     | E1 | 7.50 BSC    |     |      |

| Overall Length           | D  | 12.80 BSC   |     |      |

| Chamfer (optional)       | h  | 0.25        | -   | 0.75 |

| Foot Length              | L  | 0.40        | -   | 1.27 |

| Footprint                | L1 | 1.40 REF    |     |      |

| Foot Angle               | φ  | 0°          | -   | 8°   |

| Lead Thickness           | С  | 0.20        | -   | 0.33 |

| Lead Width               | b  | 0.31        | -   | 0.51 |

| Mold Draft Angle Top     | α  | 5°          | -   | 15°  |

| Mold Draft Angle Bottom  | β  | 5°          | -   | 15°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-094B