Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 16-Bit                                                                       |

| Speed                      | 32MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                      |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                  |

| Number of I/O              | 18                                                                           |

| Program Memory Size        | 4KB (1.375K x 24)                                                            |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 512 x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                  |

| Data Converters            | A/D 9x10b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 20-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 20-VQFN (5x5)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04ka201-i-mq |

### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC® devices and improve data space memory usage efficiency, the PIC24F instruction set supports both word and byte operations. As a consequence of byte accessibility, all EA calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word, which contains the byte, using the LSB of any EA to determine which byte to select. The selected byte is placed onto the LSB of the data path. That is, the data memory and the registers are organized as two parallel, byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register, which matches the byte address.

All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap will be generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed, but the write will not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the LSB. The MSB is not modified.

A sign-extend instruction (SE) is provided to allow the users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSB of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

Although most instructions are capable of operating on word or byte data sizes, it should be noted that some instructions operate only on words.

#### 4.2.3 NEAR DATA SPACE

The 8-Kbyte area between 0000h and 1FFFh is referred to as the near data space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. The remainder of the data space is addressable indirectly. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing (MDA) with a 16-bit address field. For PIC24F04KA201 family devices, the entire implemented data memory lies in Near Data Space (NDS).

#### 4.2.4 SFR SPACE

The first 2 Kbytes of the near data space, from 0000h to 07FFh, are primarily occupied with Special Function Registers (SFRs). These are used by the PIC24F core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control and are generally grouped together by that module. Much of the SFR space contains unused addresses; these are read as '0'. The SFR space, where the SFRs are actually implemented, is provided in Table 4-2. Each implemented area indicates a 32-byte region where at least one address is implemented as an SFR. A complete listing of implemented SFRs, including their addresses, is provided in Table 4-3 through Table 4-21.

TABLE 4-2: IMPLEMENTED REGIONS OF SFR DATA SPACE

|      | SFR Space Address |      |                |         |         |          |      |      |  |  |  |  |

|------|-------------------|------|----------------|---------|---------|----------|------|------|--|--|--|--|

|      | xx00              | xx20 | xx40           | xx60    | xx80    | xxA0     | xxC0 | xxE0 |  |  |  |  |

| 000h |                   | Cor  | re re          | ICN     | In      | terrupts |      | _    |  |  |  |  |

| 100h | Tim               | ners | Capture        | _       | Compare | _        | _    | _    |  |  |  |  |

| 200h | I <sup>2</sup> C™ | UART | SPI            |         | _       | _        | I/   | 0    |  |  |  |  |

| 300h | ADC/              | СМТИ | _              | _       | _       | _        | _    | _    |  |  |  |  |

| 400h | _                 | _    | _              | _       | _       | _        | _    | _    |  |  |  |  |

| 500h | _                 | _    | _              | _       | _       | _        | _    | _    |  |  |  |  |

| 600h | _                 | Comp | _              | _       |         | _        |      |      |  |  |  |  |

| 700h | _                 | _    | System/DS/HLVD | NVM/PMD | _       | _        | _    | _    |  |  |  |  |

**Legend:** — = No implemented SFRs in this block.

NOTES:

TABLE 7-1: TRAP VECTOR DETAILS

| Vector Number | IVT Address | AIVT Address | Trap Source        |

|---------------|-------------|--------------|--------------------|

| 0             | 000004h     | 000104h      | Reserved           |

| 1             | 000006h     | 000106h      | Oscillator Failure |

| 2             | 000008h     | 000108h      | Address Error      |

| 3             | 00000Ah     | 00010Ah      | Stack Error        |

| 4             | 00000Ch     | 00010Ch      | Math Error         |

| 5             | 00000Eh     | 00010Eh      | Reserved           |

| 6             | 000010h     | 000110h      | Reserved           |

| 7             | 000012h     | 000112h      | Reserved           |

TABLE 7-2: IMPLEMENTED INTERRUPT VECTORS

| Interment Course             | Vector | IVT Address | AIVT    | Interrupt Bit Locations |          |             |  |

|------------------------------|--------|-------------|---------|-------------------------|----------|-------------|--|

| Interrupt Source             | Number | IVI Address | Address | Flag                    | Enable   | Priority    |  |

| ADC1 Conversion Done         | 13     | 00002Eh     | 00012Eh | IFS0<13>                | IEC0<13> | IPC3<6:4>   |  |

| Comparator Event             | 18     | 000038h     | 000138h | IFS1<2>                 | IEC1<2>  | IPC4<10:8>  |  |

| СТМИ                         | 77     | 0000AEh     | 0001AEh | IFS4<13>                | IEC4<13> | IPC19<6:4>  |  |

| External Interrupt 0         | 0      | 000014h     | 000114h | IFS0<0>                 | IEC0<0>  | IPC0<2:0>   |  |

| External Interrupt 1         | 20     | 00003Ch     | 00013Ch | IFS1<4>                 | IEC1<4>  | IPC5<2:0>   |  |

| External Interrupt 2         | 29     | 00004Eh     | 00014Eh | IFS1<13>                | IEC1<13> | IPC7<6:4>   |  |

| I2C1 Master Event            | 17     | 000036h     | 000136h | IFS1<1>                 | IEC1<1>  | IPC4<6:4>   |  |

| I2C1 Slave Event             | 16     | 000034h     | 000134h | IFS1<0>                 | IEC1<0>  | IPC4<2:0>   |  |

| Input Capture1               | 1      | 000016h     | 000116h | IFS0<1>                 | IEC0<1>  | IPC0<6:4>   |  |

| Input Change Notification    | 19     | 00003Ah     | 00013Ah | IFS1<3>                 | IEC1<3>  | IPC4<14:12> |  |

| HLVD High/Low-Voltage Detect | 72     | 0000A4h     | 0001A4h | IFS4<8>                 | IEC4<8>  | IPC17<2:0>  |  |

| NVM – NVM Write Complete     | 15     | 000032h     | 000132h | IFS0<15>                | IEC0<15> | IPC3<14:12> |  |

| Output Compare 1             | 2      | 000018h     | 000118h | IFS0<2>                 | IEC0<2>  | IPC0<10:8>  |  |

| SPI1 Error                   | 9      | 000026h     | 000126h | IFS0<9>                 | IEC0<9>  | IPC2<6:4>   |  |

| SPI1 Event                   | 10     | 000028h     | 000128h | IFS0<10>                | IEC0<10> | IPC2<10:8>  |  |

| Timer1                       | 3      | 00001Ah     | 00011Ah | IFS0<3>                 | IEC0<3>  | IPC0<14:12> |  |

| Timer2                       | 7      | 000022h     | 000122h | IFS0<7>                 | IEC0<7>  | IPC1<14:12> |  |

| Timer3                       | 8      | 000024h     | 000124h | IFS0<8>                 | IEC0<8>  | IPC2<2:0>   |  |

| UART1 Error                  | 65     | 000096h     | 000196h | IFS4<1>                 | IEC4<1>  | IPC16<6:4>  |  |

| UART1 Receiver               | 11     | 00002Ah     | 00012Ah | IFS0<11>                | IEC0<11> | IPC2<14:12> |  |

| UART1 Transmitter            | 12     | 00002Ch     | 00012Ch | IFS0<12>                | IEC0<12> | IPC3<2:0>   |  |

#### REGISTER 7-12: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| U-0    | R/W-1 | R/W-0 | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-------|-------|-------|-----|-----|-----|-------|

| _      | T2IP2 | T2IP1 | T2IP0 | _   | _   | _   | _     |

| bit 15 |       |       |       |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **Unimplemented:** Read as '0'

bit 14-12 T2IP<2:0>: Timer2 Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

.

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 11-0 **Unimplemented:** Read as '0'

#### REGISTER 8-4: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER

| R/W-0  | U-0 | R/W-0  | R/W-0 | R/W-0  | R/W-0  | R/W-0  | R/W-0  |

|--------|-----|--------|-------|--------|--------|--------|--------|

| ROEN   | _   | ROSSLP | ROSEL | RODIV3 | RODIV2 | RODIV1 | RODIV0 |

| bit 15 |     |        |       |        |        |        | bit 8  |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-----|-----|-----|-----|-----|-----|-------|

| _     | _   | _   | _   | _   | _   | _   | _     |

| bit 7 |     |     |     |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 ROEN: Reference Oscillator Output Enable bit

1 = Reference oscillator enabled on REFO pin

0 = Reference oscillator disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 ROSSLP: Reference Oscillator Output Stop in Sleep bit

1 = Reference oscillator continues to run in Sleep

0 = Reference oscillator is disabled in Sleep

bit 12 ROSEL: Reference Oscillator Source Select bit

1 = Primary oscillator used as the base clock<sup>(1)</sup>

0 = System clock used as the base clock; base clock reflects any clock switching of the device

bit 11-8 RODIV3:RODIV0: Reference Oscillator Divisor Select bits

1111 = Base clock value divided by 32,768

1110 = Base clock value divided by 16,384

1101 = Base clock value divided by 8,192

1100 = Base clock value divided by 4,096

1011 = Base clock value divided by 2,048

1010 = Base clock value divided by 1,024

1001 = Base clock value divided by 512

1000 = Base clock value divided by 256

0111 = Base clock value divided by 128

0110 = Base clock value divided by 64

0101 = Base clock value divided by 32

0100 = Base clock value divided by 16

0011 = Base clock value divided by 8

0010 = Base clock value divided by 4

0001 = Base clock value divided by 2

0000 = Base clock value

bit 7-0 **Unimplemented:** Read as '0'

**Note 1:** The crystal oscillator must be enabled using the FOSC<2:0> bits; the crystal maintains the operation in Sleep mode.

NOTES:

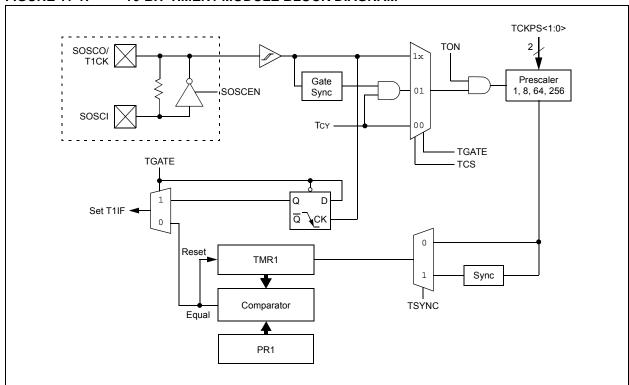

#### 11.0 TIMER1

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on Timers, refer to the "PIC24F Family Reference Manual", Section 14. "Timers" (DS39704).

The Timer1 module is a 16-bit timer which can operate as a free-running, interval timer/counter. Timer1 can operate in three modes:

- · 16-Bit Timer

- · 16-Bit Synchronous Counter

- · 16-Bit Asynchronous Counter

Timer1 also supports these features:

- · Timer Gate Operation

- · Selectable Prescaler Settings

- Timer Operation during CPU Idle and Sleep modes

- Interrupt on 16-Bit Period Register Match or Falling Edge of External Gate Signal

Figure 11-1 presents a block diagram of the 16-bit Timer1 module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1).

- Select the timer prescaler ratio using the TCKPS<1:0> bits.

- Set the Clock and Gating modes using the TCS and TGATE bits.

- Set or clear the TSYNC bit to configure synchronous or asynchronous operation.

- Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

FIGURE 11-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

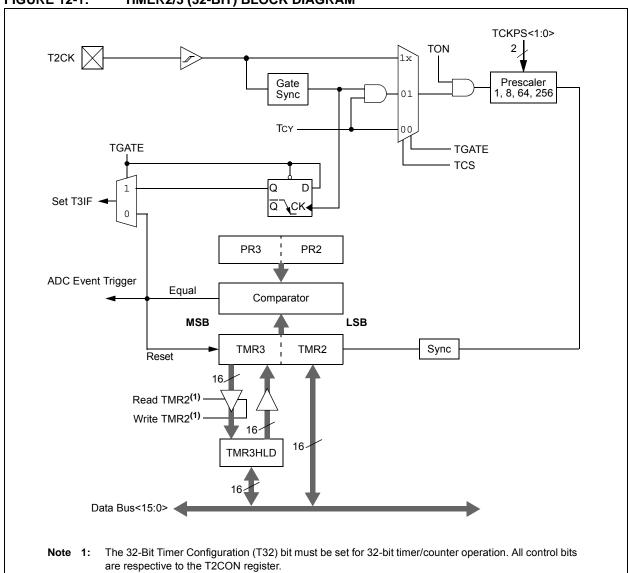

FIGURE 12-1: TIMER2/3 (32-BIT) BLOCK DIAGRAM

#### EXAMPLE 14-1: PWM PERIOD AND DUTY CYCLE CALCULATIONS<sup>(1)</sup>

1. Find the Timer Period register value for a desired PWM frequency of 52.08 kHz, where Fosc = 8 MHz with PLL (32 MHz device clock rate) and a Timer2 prescaler setting of 1:1.

PWM Period = 1/PWM Frequency = 1/52.08 kHz = 19.2 μs

PWM Period = (PR2 + 1) • Tcy • (Timer 2 Prescale Value)

19.2

$$\mu$$

s = (PR2 + 1) • 62.5 ns • 1

PR2 = 306

2. Find the maximum resolution of the duty cycle that can be used with a 52.08 kHz frequency and a 32 MHz device clock rate:

PWM Resolution = log<sub>10</sub>(FCY/FPWM)/log<sub>10</sub>2) bits

=  $(\log_{10}(16 \text{ MHz}/52.08 \text{ kHz})/\log_{10}2) \text{ bits}$

= 8.3 bits

Note 1: Based on Tcy = 2 \* Tosc, Doze mode and PLL are disabled.

#### TABLE 14-1: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 4 MIPS (FCY = 4 MHz)<sup>(1)</sup>

| PWM Frequency         | 7.6 Hz | 61 Hz | 122 Hz | 977 Hz | 3.9 kHz | 31.3 kHz | 125 kHz |

|-----------------------|--------|-------|--------|--------|---------|----------|---------|

| Timer Prescaler Ratio | 8      | 1     | 1      | 1      | 1       | 1        | 1       |

| Period Register Value | FFFFh  | FFFFh | 7FFFh  | 0FFFh  | 03FFh   | 007Fh    | 001Fh   |

| Resolution (bits)     | 16     | 16    | 15     | 12     | 10      | 7        | 5       |

**Note 1:** Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

#### TABLE 14-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS AT 16 MIPS (FcY = 16 MHz)<sup>(1)</sup>

| PWM Frequency         | 30.5 Hz | 244 Hz | 488 Hz | 3.9 kHz | 15.6 kHz | 125 kHz | 500 kHz |

|-----------------------|---------|--------|--------|---------|----------|---------|---------|

| Timer Prescaler Ratio | 8       | 1      | 1      | 1       | 1        | 1       | 1       |

| Period Register Value | FFFFh   | FFFFh  | 7FFFh  | 0FFFh   | 03FFh    | 007Fh   | 001Fh   |

| Resolution (bits)     | 16      | 16     | 15     | 12      | 10       | 7       | 5       |

Note 1: Based on Fcy = Fosc/2, Doze mode and PLL are disabled.

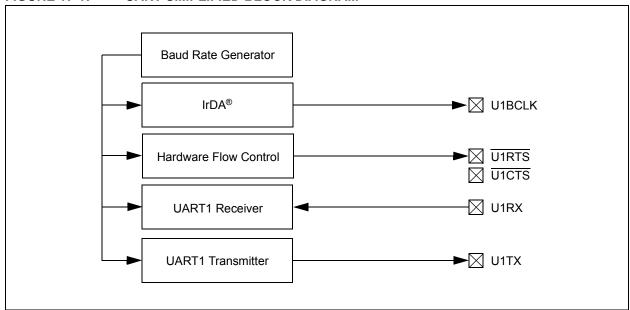

# 17.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Universal Asynchronous Receiver Transmitter, refer to the "PIC24F Family Reference Manual", Section 21. "UART" (DS39708).

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in this PIC24F device family. The UART is a full-duplex asynchronous system that can communicate with peripheral devices, such as personal computers, LIN, RS-232 and RS-485 interfaces. This module also supports a hardware flow control option with the U1CTS and U1RTS pins, and also includes an IrDA® encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8-Bit or 9-Bit Data Transmission through the U1TX and U1RX pins

- · Even, Odd or No Parity Options (for 8-bit data)

- · One or Two Stop bits

- Hardware Flow Control Option with U1CTS and U1RTS pins

- Fully Integrated Baud Rate Generator (IBRG) with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep, First-In-First-Out (FIFO) Transmit Data Buffer

- · 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit mode with Address Detect (9<sup>th</sup> bit = 1)

- · Transmit and Receive Interrupts

- · Loopback mode for Diagnostic Support

- · Support for Sync and Break Characters

- · Supports Automatic Baud Rate Detection

- · IrDA Encoder and Decoder Logic

- 16x Baud Clock Output for IrDA Support

A simplified block diagram of the UART is displayed in Figure 17-1. The UART module consists of these important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- · Asynchronous Receiver

#### REGISTER 17-2: U1STA: UART1 STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                           |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect.</li> <li>0 = Address Detect mode disabled</li> </ul>                   |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                       |

|       | 1 = Receiver is Idle                                                                                                                                                       |

|       | 0 = Receiver is active                                                                                                                                                     |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                  |

|       | <ul><li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Parity error has not been detected</li></ul>   |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                 |

|       | <ul><li>1 = Framing error has been detected for the current character (character at the top of the receive FIFO)</li><li>0 = Framing error has not been detected</li></ul> |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                            |

|       | 1 = Receive buffer has overflowed                                                                                                                                          |

|       | 0 = Receive buffer has not overflowed (clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset the receiver buffer and the RSR to the empty state)    |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                       |

|       | <ul><li>1 = Receive buffer has data; at least one more character can be read</li><li>0 = Receive buffer is empty</li></ul>                                                 |

NOTES:

#### FOSCSEL: OSCILLATOR SELECTION CONFIGURATION REGISTER REGISTER 23-2:

| R/P-1 | U-0 | U-0 | U-0 | U-0 | R/P-1  | R/P-1  | R/P-1  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| IESO  | _   | _   | _   | _   | FNOSC2 | FNOSC1 | FNOSC0 |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit P = Programmable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 IESO: Internal External Switchover bit

1 = Internal External Switchover mode enabled (Two-Speed Start-up enabled)

0 = Internal External Switchover mode disabled (Two-Speed Start-up disabled)

bit 6-3 Unimplemented: Read as '0'

bit 2-0 FNOSC<2:0>: Oscillator Selection bits

000 = Fast RC oscillator (FRC)

001 = Fast RC oscillator with divide-by-N with PLL module (FRCDIV+PLL)

010 = Primary oscillator (XT, HS, EC)

011 = Primary oscillator with PLL module (HS+PLL, EC+PLL)

100 = Secondary oscillator (SOSC)

101 = Low-Power RC oscillator (LPRC)

110 = 500 kHz Low-Power FRC oscillator with divide-by-N (LPFRCDIV)

111 = 8 MHz FRC oscillator with divide-by-N (FRCDIV)

#### 24.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 24.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 24.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 24.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a full-speed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming™ (ICSP™).

#### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

#### TABLE 26-25: ADC CONVERSION TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS |        |                                                   | Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |      |          |       |                                       |

|--------------------|--------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|------|----------|-------|---------------------------------------|

| Param<br>No.       | Symbol | Characteristic                                    | Min.                                                                                                                           | Тур  | Max.     | Units | Conditions                            |

| Clock Parameters   |        |                                                   |                                                                                                                                |      |          |       |                                       |

| AD50               | TAD    | ADC Clock Period                                  | 75                                                                                                                             | _    | _        | ns    | Tcy = 75 ns, AD1CON3 in default state |

| AD51               | Trc    | ADC Internal RC Oscillator<br>Period              | _                                                                                                                              | 250  | _        | ns    |                                       |

|                    |        | Con                                               | version F                                                                                                                      | Rate |          |       |                                       |

| AD55               | TCONV  | Conversion Time                                   | _                                                                                                                              | 12   | _        | TAD   |                                       |

| AD56               | FCNV   | Throughput Rate                                   | _                                                                                                                              | _    | 500      | ksps  | $AVDD \geq 2.7V$                      |

| AD57               | TSAMP  | Sample Time                                       | _                                                                                                                              | 1    | _        | TAD   |                                       |

| AD58               | TACQ   | Acquisition Time                                  | 750                                                                                                                            | _    | _        | ns    | (Note 2)                              |

| AD59               | Tswc   | Switching Time from Convert to Sample             | _                                                                                                                              | _    | (Note 3) |       |                                       |

| AD60               | TDIS   | Discharge Time                                    | 0.5                                                                                                                            | _    | _        | TAD   |                                       |

| Clock Parameters   |        |                                                   |                                                                                                                                |      |          |       |                                       |

| AD61               | TPSS   | Sample Start Delay from Setting Sample bit (SAMP) | 2                                                                                                                              | _    | 3        | TAD   |                                       |

**Note 1:** Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

<sup>2:</sup> The time for the holding capacitor to acquire the "New" input voltage when the voltage changes full scale after the conversion (VDD to Vss or Vss to VDD).

<sup>3:</sup> On the following cycle of the device clock.

TABLE 26-26: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER AND BROWN-OUT RESET TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                          | Standard Operating Conditions: 1.8V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial |                    |      |       |                 |

|--------------------|--------|----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|------|-------|-----------------|

| Param<br>No.       | Symbol | Characteristic                                           | Min.                                                                                                                                                                   | Typ <sup>(1)</sup> | Max. | Units | Conditions      |

| SY10               | TmcL   | MCLR Pulse Width (low)                                   | 2                                                                                                                                                                      | _                  | _    | μS    |                 |

| SY11               | TPWRT  | Power-up Timer Period                                    | 50                                                                                                                                                                     | 64                 | 90   | ms    |                 |

| SY12               | TPOR   | Power-on Reset Delay                                     | 1                                                                                                                                                                      | 5                  | 10   | μS    |                 |

| SY13               | Tioz   | I/O High-Impedance from MCLR Low or Watchdog Timer Reset | _                                                                                                                                                                      | _                  | 100  | ns    |                 |

| SY20               | TWDT   | Watchdog Timer Time-out Period                           | 0.85                                                                                                                                                                   | 1.0                | 1.15 | ms    | 1.32 prescaler  |

|                    |        |                                                          | 3.4                                                                                                                                                                    | 4.0                | 4.6  | ms    | 1:128 prescaler |

| SY25               | TBOR   | Brown-out Reset Pulse Width                              | 1                                                                                                                                                                      | _                  | _    | μS    |                 |

| SY35               | TFSCM  | Fail-Safe Clock Monitor Delay                            | _                                                                                                                                                                      | 2                  | 2.3  | μS    |                 |

| SY45               | TRST   | Configuration Update Time                                | _                                                                                                                                                                      | 20                 | _    | μS    |                 |

|                    | TVREG  | On-Chip Voltage Regulator<br>Output Delay                | _                                                                                                                                                                      | 10                 | _    | μS    |                 |

| SY55               | TLOCK  | PLL Start-up Time                                        | _                                                                                                                                                                      | 1                  | _    | ms    |                 |

| SY65               | Tost   | Oscillator Start-up Time                                 |                                                                                                                                                                        | 1024               | _    | Tosc  |                 |

| SY75               | TFRC   | Fast RC Oscillator Start-up Time                         |                                                                                                                                                                        | 1                  | 1.5  | μS    |                 |

| SY85               | TLPRC  | Low-Power Oscillator Start-up<br>Time                    | _                                                                                                                                                                      | _                  | 100  | μS    |                 |

**Note 1:** Data in "Typ" column is at 3.3V, +25°C unless otherwise stated.

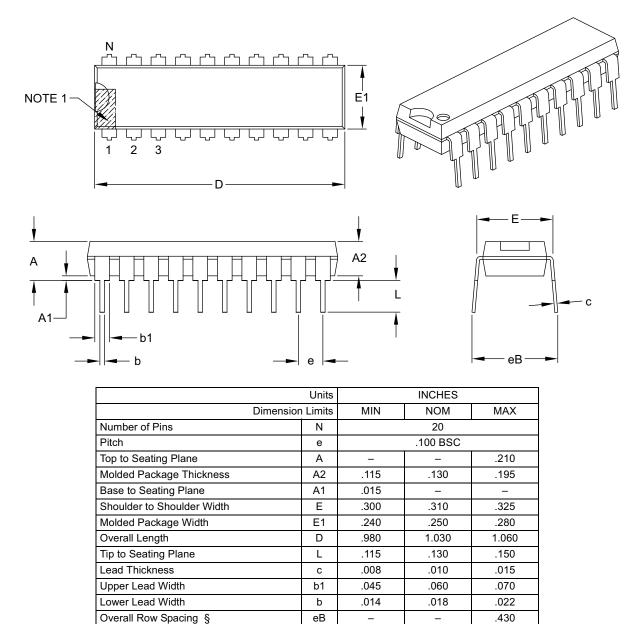

#### 27.2 Package Details

The following sections give the technical details of the packages.

#### 14-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | INCHES           |          |      |      |

|----------------------------|------------------|----------|------|------|

|                            | Dimension Limits | MIN      | NOM  | MAX  |

| Number of Pins             | N                | 14       |      |      |

| Pitch                      | е                | .100 BSC |      |      |

| Top to Seating Plane       | A                | _        | _    | .210 |

| Molded Package Thickness   | A2               | .115     | .130 | .195 |

| Base to Seating Plane      | A1               | .015     | _    | -    |

| Shoulder to Shoulder Width | E                | .290     | .310 | .325 |

| Molded Package Width       | E1               | .240     | .250 | .280 |

| Overall Length             | D                | .735     | .750 | .775 |

| Tip to Seating Plane       | L                | .115     | .130 | .150 |

| Lead Thickness             | С                | .008     | .010 | .015 |

| Upper Lead Width           | b1               | .045     | .060 | .070 |

| Lower Lead Width           | b                | .014     | .018 | .022 |

| Overall Row Spacing §      |                  | _        | _    | .430 |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-005B

### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B

#### **INDEX**

| A                                                 | C                                               |

|---------------------------------------------------|-------------------------------------------------|

| A/D                                               | C Compilers                                     |

| 10-Bit High-Speed A/D Converter143                | MPLAB XC Compilers                              |

| Conversion Timing Requirements                    | Charge Time Measurement Unit. See CTMU.         |

| Module Specifications                             | Code Examples                                   |

| Reset, Watchdog Timer, Oscillator Start-up Timer, | Erasing a Program Memory Row,                   |

| Power-up Timer and Brown-out Reset                | 'C' Language Code47                             |

| Timing Requirements                               | Erasing a Program Memory Row,                   |

| A/D Converter                                     | Assembly Language Code                          |

| Analog Input Model150                             | I/O Port Write/Read100                          |

| Transfer Function                                 | Initiating a Programming Sequence,              |

| AC Characteristics                                | 'C' Language Code49                             |

|                                                   | Initiating a Programming Sequence,              |

| Capacitive Loading Requirements on                | Assembly Language Code                          |

| Output Pins                                       | ,                                               |

| Comparator                                        | Loading the Write Buffers, 'C' Language Code 48 |

| Comparator Voltage Reference Settling Time 196    | Loading the Write Buffers,                      |

| CTMU Current Source                               | Assembly Language Code                          |

| Internal RC Accuracy                              | Programming a Single Word of                    |

| Load Conditions and Requirements                  | Flash Program Memory                            |

| Temperature and Voltage Specifications            | PWRSAV Instruction Syntax91                     |

| Assembler                                         | Sequence for Clock Switching                    |

| MPASM Assembler174                                | Code Protection                                 |

| В                                                 | Comparator 153                                  |

|                                                   | Comparator Voltage Reference                    |

| Baud Rate Generator                               | Configuring157                                  |

| Setting as a Bus Master127                        | Configuration Bits                              |

| Block Diagrams                                    | Core Features7                                  |

| 10-Bit High-Speed A/D Converter144                | CPU                                             |

| 16-Bit Timer1101                                  | ALU23                                           |

| Accessing Program Memory with                     | Control Registers22                             |

| Table Instructions40                              | Core Registers20                                |

| CALL Stack Frame37                                | Programmer's Model19                            |

| Comparator Module153                              | CTMU                                            |

| Comparator Voltage Reference                      | Measuring Capacitance 159                       |

| CPU Programmer's Model21                          | Measuring Time 160                              |

| CTMU Connections and Internal Configuration       | Pulse Delay and Generation 160                  |

| for Capacitance Measurement                       | Customer Change Notification Service            |

| CTMU Typical Connections and Internal             | Customer Notification Service                   |

| Configuration for Pulse Delay Generation 160      | Customer Support                                |

| CTMU Typical Connections and Internal             | _                                               |

| Configuration for Time Measurement                | D                                               |

| Data Access From Program Space                    | Data Memory                                     |

| Address Generation                                | Address Space27                                 |

| High/Low-Voltage Detect (HLVD)141                 | Memory Map27                                    |

| I <sup>2</sup> C Module126                        | Near Data Space28                               |

| Individual Comparator Configurations              | Organization28                                  |

| Input Capture                                     | SFR Space                                       |

| Output Compare                                    | Software Stack                                  |

| PIC24F CPU Core                                   | Space Width                                     |

| PIC24F04KA201 Family (General)                    | DC Characteristics                              |

| PSV Operation41                                   | Brown-out Reset Trip Points                     |

| Reset System51                                    | Comparator                                      |

| Shared I/O Port Structure                         | Comparator Voltage Reference                    |

|                                                   | ·                                               |

| Simplified UART                                   | High/Low-Voltage Detect                         |

| SPI1 Module (Enhanced Buffer Mode)                | I/O Pin Input Specifications                    |

| SPI1 Module (Standard Buffer Mode)                | I/O Pin Output Specifications                   |

| System Clock                                      | Idle Current IDLE                               |

| Timer2 (16-Bit Synchronous Mode)                  | Operating Current IDD                           |

| Timer2/3 (32-Bit Mode)                            | Power-Down Current IPD                          |

| Timer3 (16-Bit Synchronous Mode)                  | Program Memory                                  |

| Watchdog Timer (WDT)                              | Temperature and Voltage Specifications          |

| Brown-out Reset (BOR)55                           | Deep Sleep BOR (DSBOR)56                        |

### **Worldwide Sales and Service**

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX Tel: 512-257-3370

Boston

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago

Itasca, IL Tel: 630-285-0071 Fax: 630-285-0075

Cleveland Independence, OH

Tel: 216-447-0464 Fax: 216-447-0643

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit Novi. MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis

Noblesville, IN Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

Asia Pacific Office

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon Hong Kong

Tel: 852-2943-5100 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8569-7000 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Chongqing

Tel: 86-23-8980-9588 Fax: 86-23-8980-9500

China - Hangzhou

Tel: 86-571-8792-8115 Fax: 86-571-8792-8116

China - Hong Kong SAR

Tel: 852-2943-5100 Fax: 852-2401-3431

**China - Nanjing** Tel: 86-25-8473-2460

Fax: 86-25-8473-2470

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8864-2200 Fax: 86-755-8203-1760

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7252 Fax: 86-29-8833-7256

China - Xiamen

Tel: 86-592-2388138 Fax: 86-592-2388130

China - Zhuhai

Tel: 86-756-3210040 Fax: 86-756-3210049

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-3090-4444 Fax: 91-80-3090-4123

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-3019-1500

Japan - Osaka

Tel: 81-6-6152-7160 Fax: 81-6-6152-9310

Japan - Tokyo

Tel: 81-3-6880- 3770 Fax: 81-3-6880-3771

Korea - Daegu

Tel: 82-53-744-4301 Fax: 82-53-744-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Kuala Lumpur

Tel: 60-3-6201-9857 Fax: 60-3-6201-9859

Malaysia - Penang

Tel: 60-4-227-8870 Fax: 60-4-227-4068

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850

Taiwan - Hsin Chu

Tel: 886-3-5778-366 Fax: 886-3-5770-955

Taiwan - Kaohsiung

Tel: 886-7-213-7830

Taiwan - Taipei

Tel: 886-2-2508-8600 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### EUROPE

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393

Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Dusseldorf

Tel: 49-2129-3766400

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

**Germany - Pforzheim** Tel: 49-7231-424750

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Italy - Venice

Tel: 39-049-7625286

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Poland - Warsaw

Tel: 48-22-3325737

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91

Sweden - Stockholm

Tel: 46-8-5090-4654

**UK - Wokingham** Tel: 44-118-921-5800 Fax: 44-118-921-5820

03/25/14