Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                               |

|----------------------------|-------------------------------------------------------------------------------|

| Product Status             | Active                                                                        |

| Core Processor             | PIC                                                                           |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 32MHz                                                                         |

| Connectivity               | I²C, IrDA, SPI, UART/USART                                                    |

| Peripherals                | Brown-out Detect/Reset, HLVD, POR, PWM, WDT                                   |

| Number of I/O              | 18                                                                            |

| Program Memory Size        | 4KB (1.375K x 24)                                                             |

| Program Memory Type        | FLASH                                                                         |

| EEPROM Size                | -                                                                             |

| RAM Size                   | 512 x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                   |

| Data Converters            | A/D 9x10b                                                                     |

| Oscillator Type            | Internal                                                                      |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                             |

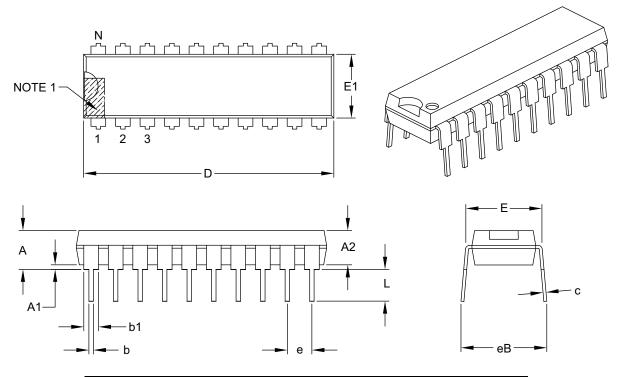

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                                                |

| Supplier Device Package    | 20-SSOP                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24f04ka201t-i-ss |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

#### **CPU Control Registers** 3.2

#### **REGISTER 3-1:** SR: ALU STATUS REGISTER

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | R/W-0, HSC |

|--------|-----|-----|-----|-----|-----|-----|------------|

| —      |     |     | —   | —   | —   | —   | DC         |

| bit 15 |     |     |     |     |     |     | bit 8      |

| R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R/W-0, HSC <sup>(1)</sup> | R-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC | R/W-0, HSC |

|---------------------------|---------------------------|---------------------------|----------|------------|------------|------------|------------|

| IPL2 <sup>(2)</sup>       | IPL1 <sup>(2)</sup>       | IPL0 <sup>(2)</sup>       | RA       | N          | OV         | Z          | С          |

| bit 7                     |                           |                           |          |            |            |            | bit 0      |

| Legend:           | HSC = Hardware Settable/ | Clearable bit              |                    |

|-------------------|--------------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared       | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8    | DC: ALU Half Carry/Borrow bit                                                                                                                                                                                                                                                             |

| bit o    | <ul> <li>1 = A carry-out from the 4<sup>th</sup> low-order bit (for byte-sized data) or 8<sup>th</sup> low-order bit (for word-sized data) of the result occurred</li> <li>0 = No carry-out from the 4<sup>th</sup> or 8<sup>th</sup> low-order bit of the result has occurred</li> </ul> |

|          | •                                                                                                                                                                                                                                                                                         |

| bit 7-5  | IPL<2:0>: CPU Interrupt Priority Level Status bits <sup>(1,2)</sup><br>111 = CPU interrupt priority level is 7 (15); user interrupts disabled                                                                                                                                             |

|          | 110 = CPU interrupt priority level is 6 (14)                                                                                                                                                                                                                                              |

|          | 101 = CPU Interrupt priority Level is 5 (13)                                                                                                                                                                                                                                              |

|          | 100 = CPU interrupt priority level is 4 (12)                                                                                                                                                                                                                                              |

|          | 011 = CPU interrupt priority level is 3 (11)                                                                                                                                                                                                                                              |

|          | 010 = CPU interrupt priority level is 2 (10)                                                                                                                                                                                                                                              |

|          | 001 = CPU interrupt priority level is 1 (9)<br>000 = CPU interrupt priority level is 0 (8)                                                                                                                                                                                                |

| L:L 4    |                                                                                                                                                                                                                                                                                           |

| bit 4    | RA: REPEAT Loop Active bit                                                                                                                                                                                                                                                                |

|          | 1 = REPEAT loop in progress<br>0 = REPEAT loop not in progress                                                                                                                                                                                                                            |

| bit 3    |                                                                                                                                                                                                                                                                                           |

| DILS     | N: ALU Negative bit                                                                                                                                                                                                                                                                       |

|          | 1 = Result was negative<br>0 = Result was non-negative (zero or positive)                                                                                                                                                                                                                 |

| bit 2    | <b>OV:</b> ALU Overflow bit                                                                                                                                                                                                                                                               |

|          | 1 = Overflow occurred for signed (2's complement) arithmetic in this arithmetic operation                                                                                                                                                                                                 |

|          | 0 = No  overflow has occurred                                                                                                                                                                                                                                                             |

| bit 1    | Z: ALU Zero bit                                                                                                                                                                                                                                                                           |

|          | 1 = An operation, which effects the Z bit, has set it at some time in the past                                                                                                                                                                                                            |

|          | 0 = The most recent operation, which effects the Z bit, has cleared it (i.e., a non-zero result)                                                                                                                                                                                          |

| bit 0    | C: ALU Carry/Borrow bit                                                                                                                                                                                                                                                                   |

|          | 1 = A carry-out from the Most Significant bit (MSb) of the result occurred                                                                                                                                                                                                                |

|          | 0 = No carry-out from the Most Significant bit (MSb) of the result occurred                                                                                                                                                                                                               |

| Note 1:  | The IPL Status bits are read-only when NSTDIS (INTCON1<15>) = $1$ .                                                                                                                                                                                                                       |

| 2:       | The IPL Status bits are concatenated with the IPL3 bit (CORCON<3>) to form the CPU Interrupt Priority                                                                                                                                                                                     |

|          |                                                                                                                                                                                                                                                                                           |

#### REGISTER 3-2: CORCON: CPU CONTROL REGISTER

| U-0    | U-0 | U-0 U-0 |   | U-0 | U-0 | U-0 | U-0   |

|--------|-----|---------|---|-----|-----|-----|-------|

| —      | —   | _       | — | _   | —   | —   | —     |

| bit 15 |     |         |   |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0                 | R/C-0, HSC | R/W-0 | U-0 | U-0   |

|-------|-----|-----|---------------------|------------|-------|-----|-------|

| —     |     |     | IPL3 <sup>(1)</sup> | PSV        | —     | —   |       |

| bit 7 |     |     |                     |            |       |     | bit 0 |

| Legend:           | HSC = Hardware Settable/C | learable bit                       |                    |  |  |  |  |

|-------------------|---------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 15-4 | Unimplemented: Read as '0'                                                                                                    |

|----------|-------------------------------------------------------------------------------------------------------------------------------|

| bit 3    | IPL3: CPU Interrupt Priority Level Status bit <sup>(1)</sup>                                                                  |

|          | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |

| bit 2    | <b>PSV:</b> Program Space Visibility in Data Space Enable bit                                                                 |

|          | <ul><li>1 = Program space visible in data space</li><li>0 = Program space not visible in data space</li></ul>                 |

| bit 1-0  | Unimplemented: Read as '0'                                                                                                    |

**Note 1:** User interrupts are disabled when IPL3 = 1.

#### 3.3 Arithmetic Logic Unit (ALU)

The PIC24F ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the SR register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

The PIC24F CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware division for 16-bit divisor.

#### 3.3.1 MULTIPLIER

The ALU contains a high-speed, 17-bit x 17-bit multiplier. It supports unsigned, signed or mixed sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

| File Name | Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                    | Bit 7 | Bit 6 | Bit 5      | Bit 4       | Bit 3        | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|------|---------|--------|---------|--------|--------|--------|--------|--------------------------|-------|-------|------------|-------------|--------------|-------|-------|-------|---------------|

| I2C1RCV   | 0200 | —       | _      | _       | —      | _      | —      | —      | _                        |       |       |            | I2C1 Recei  | ve Register  |       |       |       | 0000          |

| I2C1TRN   | 0202 | _       | _      | _       | _      | _      | _      | _      | – I2C1 Transmit Register |       |       |            |             |              | OOFF  |       |       |               |

| I2C1BRG   | 0204 | _       | _      | _       | _      | _      | _      | _      |                          |       | Ľ     | 2C1 Baud F | Rate Genera | ator Registe | r     |       |       | 0000          |

| I2C1CON   | 0206 | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN                     | GCEN  | STREN | ACKDT      | ACKEN       | RCEN         | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT  | 0208 | ACKSTAT | TRSTAT | _       | —      | _      | BCL    | GCSTAT | ADD10                    | IWCOL | I2COV | D/A        | Р           | S            | R/W   | RBF   | TBF   | 0000          |

| I2C1ADD   | 020A | _       | _      | —       | —      | _      | _      |        | I2C1 Address Register 00 |       |       |            |             |              |       |       | 0000  |               |

| I2C1MSK   | 020C | _       | _      | _       | _      | _      | _      | AMSK9  | AMSK8                    | AMSK7 | AMSK6 | AMSK5      | AMSK4       | AMSK3        | AMSK2 | AMSK1 | AMSK0 | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

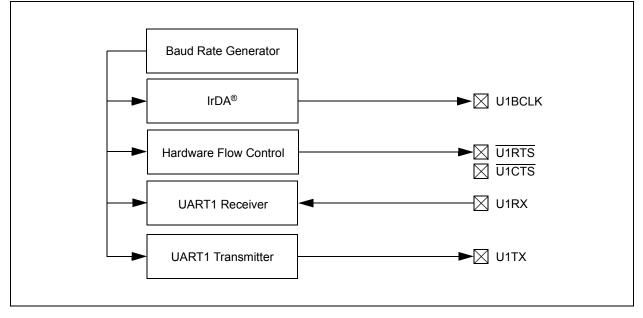

#### TABLE 4-10: UART REGISTER MAP

| File<br>Name | Addr | Bit 15   | Bit 14 | Bit 13   | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8      | Bit 7         | Bit 6    | Bit 5     | Bit 4        | Bit 3 | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|--------------|------|----------|--------|----------|--------|--------|--------|---------|------------|---------------|----------|-----------|--------------|-------|--------|--------|-------|---------------|

| U1MODE       | 0220 | UARTEN   | —      | USIDL    | IREN   | RTSMD  | _      | UEN1    | UEN0       | WAKE          | LPBACK   | ABAUD     | RXINV        | BRGH  | PDSEL1 | PDSEL0 | STSEL | 0000          |

| U1STA        | 0222 | UTXISEL1 | UTXINV | UTXISEL0 | _      | UTXBRK | UTXEN  | UTXBF   | TRMT       | URXISEL1      | URXISEL0 | ADDEN     | RIDLE        | PERR  | FERR   | OERR   | URXDA | 0110          |

| U1TXREG      | 0224 | _        | _      | _        | _      | _      |        | _       |            |               |          | UART1 Tra | ansmit Regis | ster  |        |        |       | 0000          |

| U1RXREG      | 0226 | _        | _      | _        | _      | _      |        | _       |            |               |          | UART1 Re  | ceive Regis  | ster  |        |        |       | 0000          |

| U1BRG        | 0228 |          |        |          |        |        |        | Baud Ra | ate Genera | tor Prescaler | Register |           |              |       |        |        |       | 0000          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-11: SPI REGISTER MAP

| File<br>Name | Addr | Bit 15 | Bit 14                       | Bit 13  | Bit 12 | Bit 11 | Bit 10  | Bit 9   | Bit 8   | Bit 7 | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|--------------|------|--------|------------------------------|---------|--------|--------|---------|---------|---------|-------|--------|--------|--------|--------|--------|--------|--------|---------------|

| SPI1STAT     | 0240 | SPIEN  | _                            | SPISIDL |        | _      | SPIBEC2 | SPIBEC1 | SPIBEC0 | SRMPT | SPIROV | SRXMPT | SISEL2 | SISEL1 | SISEL0 | SPITBF | SPIRBF | 0000          |

| SPI1CON1     | 0242 | -      | _                            | _       | DISSCK | DISSDO | MODE16  | SMP     | CKE     | SSEN  | CKP    | MSTEN  | SPRE2  | SPRE1  | SPRE0  | PPRE1  | PPRE0  | 0000          |

| SPI1CON2     | 0244 | FRMEN  | SPIFSD                       | SPIFPOL | —      | —      | _       | _       | —       | _     | —      | —      | _      | —      | —      | SPIFE  | SPIBEN | 0000          |

| SPI1BUF      | 0248 |        | SPI1 Transmit/Receive Buffer |         |        |        |         |         |         |       |        |        |        |        | 0000   |        |        |               |

**Legend:** — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

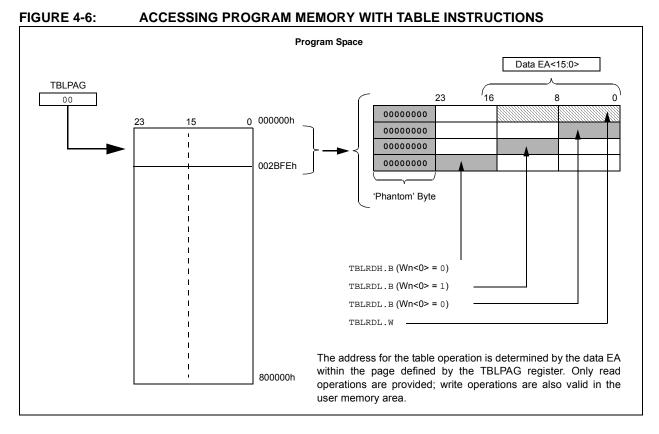

#### 4.3.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program memory without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by 2 for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit word-wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word, and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word-sized (16-bit) data to and from program space. Both function as either byte or word operations.

- TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when byte select is '1'; the lower byte is selected when it is '0'.

- TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom' byte, will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D < 7:0 > of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (byte select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Memory Page Address register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

Note: Only table read operations will execute in the configuration memory space, and only then, in implemented areas such as the Device ID. Table write operations are not allowed.

#### 4.3.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into an 8K word page (in PIC24F08KA1XX devices) and a 16K word page (in PIC24F16KA1XX devices) of the program space. This provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the MSb of the data space EA is '1', and PSV is enabled by setting the PSV bit in the CPU Control (CORCON<2>) register. The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page Address register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits.

By incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads from this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 8000h and higher, maps directly into a corresponding program memory address (see Figure 4-7), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space locations used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions will require one instruction cycle in addition to the specified execution time. All other instructions will require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

### 8.4 Clock Switching Operation

With few limitations, applications are free to switch between any of the four clock sources (POSC, SOSC, FRC and LPRC) under software control and at any time. To limit the possible side effects that could result from this flexibility, PIC24F devices have a safeguard lock built into the switching process.

Note: The primary oscillator mode has three different submodes (XT, HS and EC), which are determined by the POSCMDx Configuration bits. While an application can switch to and from primary oscillator mode in software, it cannot switch between the different primary submodes without reprogramming the device.

### 8.4.1 ENABLING CLOCK SWITCHING

To enable clock switching, the FCKSM1 Configuration bit in the FOSC Configuration register must be programmed to '0'. (Refer to **Section 23.1 "Configuration Bits"** for further details.) If the FCKSM1 Configuration bit is unprogrammed ('1'), the clock switching function and FSCM function are disabled. This is the default setting.

The NOSCx control bits (OSCCON<10:8>) do not control the clock selection when clock switching is disabled. However, the COSCx bits (OSCCON<14:12>) will reflect the clock source selected by the FNOSCx Configuration bits.

The OSWEN control bit (OSCCON<0>) has no effect when clock switching is disabled; it is held at '0' at all times.

#### 8.4.2 OSCILLATOR SWITCHING SEQUENCE

At a minimum, performing a clock switch requires this basic sequence:

- 1. If desired, read the COSCx bits (OSCCON<14:12>), to determine the current oscillator source.

- 2. Perform the unlock sequence to allow a write to the OSCCON register high byte.

- 3. Write the appropriate value to the NOSCx bits (OSCCON<10:8>) for the new oscillator source.

- 4. Perform the unlock sequence to allow a write to the OSCCON register low byte.

- 5. Set the OSWEN bit to initiate the oscillator switch.

Once the basic sequence is completed, the system clock hardware responds automatically as follows:

- 1. The clock switching hardware compares the COSCx bits with the new value of the NOSCx bits. If they are the same, then the clock switch is a redundant operation. In this case, the OSWEN bit is cleared automatically and the clock switch is aborted.

- If a valid clock switch has been initiated, the LOCK (OSCCON<5>) and CF (OSCCON<3>) bits are cleared.

- The new oscillator is turned on by the hardware if it is not currently running. If a crystal oscillator must be turned on, the hardware will wait until the OST expires. If the new source is using the PLL, then the hardware waits until a PLL lock is detected (LOCK = 1).

- 4. The hardware waits for 10 clock cycles from the new clock source and then performs the clock switch.

- 5. The hardware clears the OSWEN bit to indicate a successful clock transition. In addition, the NOSCx bits value is transferred to the COSCx bits.

- The old clock source is turned off at this time, with the exception of LPRC (if WDT or FSCM with LPRC as a clock source is enabled) or SOSC (if SOSCEN remains enabled).

Note 1: The processor will continue to execute code throughout the clock switching sequence. Timing-sensitive code should not be executed during this time.

2: Direct clock switches between any primary oscillator mode with PLL and FRCPLL mode are not permitted. This applies to clock switches in either direction. In these instances, the application must switch to FRC mode as a transition clock source between the two PLL modes.

#### 9.2.4.5 Deep Sleep WDT

To enable the DSWDT in Deep Sleep mode, program the Configuration bit, DSWDTEN (FDS<7>). The device Watchdog Timer (WDT) need not be enabled for the DSWDT to function. Entry into Deep Sleep mode automatically resets the DSWDT.

The DSWDT clock source is selected by the DSWDTOSC Configuration bit (FDS<4>). The postscaler options are programmed by the DSWDTPS<3:0> Configuration bits (FDS<3:0>). The minimum time-out period that can be achieved is 2.1 ms and the maximum is 25.7 days. For more details on the FDS Configuration register and DSWDT configuration options, refer to **Section 23.0 "Special Features"**.

### 9.2.4.6 Switching Clocks in Deep Sleep Mode

The DSWDT may run from either SOSC or the LPRC clock source. This allows the DSWDT to run without requiring both the LPRC and SOSC to be enabled together, reducing power consumption.

Under certain circumstances, it is possible for the DSWDT clock source to be off when entering Deep Sleep mode. In this case, the clock source is turned on automatically (if DSWDT is enabled), without the need for software intervention. However, this can cause a delay in the start of the DSWDT counters. In order to avoid this delay when using SOSC as a clock source, the application can activate SOSC prior to entering Deep Sleep mode.

#### 9.2.4.7 Checking and Clearing the Status of Deep Sleep

Upon entry into Deep Sleep mode, the status bit, DPSLP (RCON<10>), becomes set and must be cleared by the software.

On power-up, the software should read this status bit to determine if the Reset was due to an exit from Deep Sleep mode and clear the bit if it is set. Of the four possible combinations of DPSLP and POR bit states, three cases can be considered:

- Both the DPSLP and POR bits are cleared. In this case, the Reset was due to some event other than a Deep Sleep mode exit.

- The DPSLP bit is clear, but the POR bit is set. This is a normal POR.

- Both the DPSLP and POR bits are set. This means that Deep Sleep mode was entered, the device was powered down and Deep Sleep mode was exited.

### 9.2.4.8 Power-on Resets (PORs)

VDD voltage is monitored to produce PORs. Since exiting from Deep Sleep functionally looks like a POR, the technique described in **Section 9.2.4.7** "**Checking and Clearing the Status of Deep Sleep**" should be used to distinguish between Deep Sleep and a true POR event.

When a true POR occurs, the entire device including all Deep Sleep logic, (Deep Sleep registers, DSWDT, etc.) is reset.

#### 9.2.4.9 Summary of Deep Sleep Sequence

To review, these are the necessary steps involved in invoking and exiting Deep Sleep mode:

- 1. Device exits Reset and begins to execute its application code.

- 2. If DSWDT functionality is required, program the appropriate Configuration bit.

- 3. Select the appropriate clock(s) for the DSWDT (optional).

- 4. Enable and configure the DSWDT (optional).

- 5. Write context data to the DSGPRx registers (optional).

- 6. Enable the INT0 interrupt (optional).

- 7. Set the DSEN bit in the DSCON register.

- 8. Enter Deep Sleep by issuing a PWRSV #SLEEP\_MODE command.

- 9. Device exits Deep Sleep when a wake-up event occurs.

- 10. The DSEN bit is automatically cleared.

- 11. Read and clear the DPSLP status bit in RCON, and the DSWAKE status bits.

- 12. Read the DSGPRx registers (optional).

- 13. Once all state related configurations are complete, clear the RELEASE bit.

- 14. Application resumes normal operation.

## 10.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORT, LAT and TRIS registers for data control, each port pin can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

## 10.2 Configuring Analog Port Pins

The use of the AD1PCFG and TRIS registers control the operation of the A/D port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) will be converted.

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level). Analog levels on any pin that is defined as a digital input (including the ANx pins) may cause the input buffer to consume current that exceeds the device specifications.

### 10.2.1 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

## 10.3 Input Change Notification

The input change notification function of the I/O ports allows the PIC24F04KA201 family of devices to generate interrupt requests to the processor in response to a change of state on selected input pins. This feature is capable of detecting input change of states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 17 external signals (11 on 14-pin devices) that may be selected (enabled) for generating an interrupt request on a change of state.

There are six control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the interrupt enable control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up/pull-down connected to it. The pull-ups act as a current source that is connected to the pin and the pull-downs act as a current sink to eliminate the need for external resistors when push button or keypad devices are connected.

On any pin, only the pull-up resistor or the pull-down resistor should be enabled, but not both of them. If the push button or the keypad is connected to VDD, enable the pull-down, or if they are connected to VSS, enable the pull-up resistors. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the control bits for each of the CN pins.

Setting any of the control bits enables the weak pull-ups for the corresponding pins. The pull-downs are enabled separately using the CNPD1 and CNPD2 registers, which contain the control bits for each of the CN pins. Setting any of the control bits enables the weak pull-downs for the corresponding pins.

When the internal pull-up is selected, the pin uses VDD as the pull-up source voltage. When the internal pull-down is selected, the pins are pulled down to Vss by an internal resistor. Make sure that there is no external pull-up source/pull-down sink when the internal pull-ups/pull-downs are enabled.

Note: Pull-ups and pull-downs on change notification pins should always be disabled whenever the port pin is configured as a digital output.

### EXAMPLE 10-1: PORT WRITE/READ EXAMPLE

| MOV 0xFF00, W0;<br>MOV W0, TRISBB;                                                | //Configure PORTB<15:8> as inputs and PORTB<7:0> as outputs                                                                                          |

|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| NOP;                                                                              | //Delay 1 cycle                                                                                                                                      |

| BTSS PORTB, #13;                                                                  | //Next Instruction                                                                                                                                   |

| <pre>Equivalent 'C' Code TRISB = 0xFF00; NOP(); if(PORTBbits.RB13 == 1) { }</pre> | <pre>//Configure PORTB&lt;15:8&gt; as inputs and PORTB&lt;7:0&gt; as outputs //Delay 1 cycle // execute following code if PORTB pin 13 is set.</pre> |

#### REGISTER 14-2: PADCFG1: PAD CONFIGURATION CONTROL REGISTER

| U-0                                | U-0 | U-0 | U-0                                | U-0                    | U-0               | U-0 | U-0   |

|------------------------------------|-----|-----|------------------------------------|------------------------|-------------------|-----|-------|

|                                    | —   | —   | —                                  | —                      |                   | —   | —     |

| bit 15                             |     |     |                                    |                        |                   |     | bit 8 |

|                                    |     |     |                                    |                        |                   |     |       |

| U-0                                | U-0 | U-0 | R/W-0                              | R/W-0                  | U-0               | U-0 | R/W-0 |

|                                    | _   |     | SMBUSDEL <sup>(2)</sup>            | OC1TRIS <sup>(1)</sup> | —                 | —   | —     |

| bit 7                              |     |     |                                    |                        |                   |     | bit 0 |

|                                    |     |     |                                    |                        |                   |     |       |

| Legend:                            |     |     |                                    |                        |                   |     |       |

| R = Readable bit W = Writable bit  |     |     | U = Unimplemented bit, read as '0' |                        |                   |     |       |

| -n = Value at POR '1' = Bit is set |     |     | '0' = Bit is clear                 | red                    | x = Bit is unknow | /n  |       |

bit 15-5 Unimplemented: Read as '0'

bit 3 **OC1TRIS:** OC1 Output Tri-State Select bit<sup>(1)</sup>

1 = OC1 output will not be active on the pin; OCPWM1 can still be used for internal triggers

0 = OC1 output will be active on the pin based on the OCPWM1 module settings

#### bit 2-0 Unimplemented: Read as '0'

**Note 1:** To enable the actual OC1 output, the OCPWM1 module has to be enabled.

2: Bit 4 is described in Section 16.0 "Inter-Integrated Circuit (I2C<sup>™</sup>)".

## 16.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C<sup>™</sup>)

Note: This data sheet summarizes the features of this group of PIC24F devices. It is not intended to be a comprehensive reference source. For more information on the Inter-Integrated Circuit, refer to the "PIC24F Family Reference Manual", Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C™)" (DS39702).

The Inter-Integrated Circuit  $(I^2C^{TM})$  module is a serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial data EEPROMs, display drivers, A/D Converters, etc.

The I<sup>2</sup>C module supports these features:

- Independent master and slave logic

- 7-bit and 10-bit device addresses

- General call address, as defined in the I<sup>2</sup>C protocol

- Clock stretching to provide delays for the processor to respond to a slave data request

- Both 100 kHz and 400 kHz bus specifications

- · Configurable address masking

- Multi-Master modes to prevent loss of messages in arbitration

- Bus Repeater mode, allowing the acceptance of all messages as a slave regardless of the address

- Automatic SCL

Figure 16-1 illustrates a block diagram of the module.

### 16.1 Pin Remapping Options

The  $l^2$ C module is tied to a fixed pin. To allow flexibility with peripheral multiplexing, the l2C1 module in 20-pin devices can be reassigned to the alternate pins, designated as SCL1 and SDA1 during device configuration.

Pin assignment is controlled by the I2C1SEL Configuration bit. Programming this bit (= 0) multiplexes the module to the SCL1 and SDA1 pins.

## 16.2 Communicating as a Master in a Single Master Environment

The details of sending a message in Master mode depends on the communications protocol for the device being communicated with. Typically, the sequence of events is as follows:

- 1. Assert a Start condition on SDA1 and SCL1.

- 2. Send the I<sup>2</sup>C device address byte to the slave with a write indication.

- 3. Wait for and verify an Acknowledge from the slave.

- 4. Send the first data byte (sometimes known as the command) to the slave.

- 5. Wait for and verify an Acknowledge from the slave.

- 6. Send the serial memory address low byte to the slave.

- 7. Repeat steps 4 and 5 until all data bytes are sent.

- 8. Assert a Repeated Start condition on SDA1 and SCL1.

- 9. Send the device address byte to the slave with a read indication.

- 10. Wait for and verify an Acknowledge from the slave.

- 11. Enable master reception to receive serial memory data.

- 12. Generate an ACK or NACK condition at the end of a received byte of data.

- 13. Generate a Stop condition on SDA1 and SCL1.

|                         | U-0                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                           | R/W-1 HC                                                                                                                                                                          | R/W-0                                                                                 | R/W-0                                  | R/W-0             | R/W-0          |  |  |  |  |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------|-------------------|----------------|--|--|--|--|

| I2CEN                   | —                                                                                                                                                                                                                                                        | I2CSIDL                                                                                                                                                                                                                                                                                         | SCLREL                                                                                                                                                                            | IPMIEN                                                                                | A10M                                   | DISSLW            | SMEN           |  |  |  |  |

| bit 15                  |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   | bit 8          |  |  |  |  |

| R/W-0                   | R/W-0                                                                                                                                                                                                                                                    | R/W-0                                                                                                                                                                                                                                                                                           | R/W-0, HC                                                                                                                                                                         | R/W-0, HC                                                                             | R/W-0, HC                              | R/W-0, HC         | R/W-0, HC      |  |  |  |  |

| GCEN                    | STREN                                                                                                                                                                                                                                                    | ACKDT                                                                                                                                                                                                                                                                                           | ACKEN                                                                                                                                                                             | RCEN                                                                                  | PEN                                    | RSEN              | SEN            |  |  |  |  |

| bit 7                   | OTILLIN                                                                                                                                                                                                                                                  | AOILD I                                                                                                                                                                                                                                                                                         | AOREN                                                                                                                                                                             | ROLIN                                                                                 |                                        | ROLIN             | bit C          |  |  |  |  |

|                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

| Legend:                 |                                                                                                                                                                                                                                                          | HC = Hardwa                                                                                                                                                                                                                                                                                     | re Clearable bit                                                                                                                                                                  |                                                                                       |                                        |                   |                |  |  |  |  |

| R = Readal              | ole bit                                                                                                                                                                                                                                                  | W = Writable                                                                                                                                                                                                                                                                                    | bit                                                                                                                                                                               | U = Unimplem                                                                          | nented bit, read                       | as '0'            |                |  |  |  |  |

| -n = Value a            | at POR                                                                                                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                                                                                                                |                                                                                                                                                                                   | '0' = Bit is clea                                                                     | ared                                   | x = Bit is unkn   | own            |  |  |  |  |

|                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

| bit 15                  | <b>I2CEN:</b> I2C1                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                 | <b>.</b>                                                                                                                                                                          |                                                                                       |                                        |                   |                |  |  |  |  |

|                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 | e and configure<br>e; all l <sup>2</sup> C™ pins                                                                                                                                  |                                                                                       |                                        |                   | i              |  |  |  |  |

| bit 14                  |                                                                                                                                                                                                                                                          | ted: Read as '                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                   |                                                                                       | .,                                     |                   |                |  |  |  |  |

| bit 13                  | -                                                                                                                                                                                                                                                        | p in Idle Mode                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

|                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 | eration when de<br>tion in Idle mod                                                                                                                                               |                                                                                       | Idle mode                              |                   |                |  |  |  |  |

| bit 12                  |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 | ntrol bit (when o                                                                                                                                                                 |                                                                                       | C slave)                               |                   |                |  |  |  |  |

|                         | 1 = Releases                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       | Slave)                                 |                   |                |  |  |  |  |

|                         | 0 = Holds SCL1 clock low (clock stretch)                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

|                         | <u> If STREN = 1</u>                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

|                         | •                                                                                                                                                                                                                                                        | •                                                                                                                                                                                                                                                                                               | write '0' to initi<br>ion. Hardware o                                                                                                                                             |                                                                                       |                                        | ,                 | dware clear a  |  |  |  |  |

|                         | If STREN = 0<br>Bit is R/S (i.e.,                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                 | nly write '1' to rel                                                                                                                                                              | ease clock). Har                                                                      | dware clear at b                       | beginning of slav | e transmission |  |  |  |  |

| bit 11                  | IPMIEN: Intel                                                                                                                                                                                                                                            | ligent Periphera                                                                                                                                                                                                                                                                                | al Management                                                                                                                                                                     | Interface (IPM                                                                        | l) Enable bit                          |                   |                |  |  |  |  |

|                         | IPMIEN: Intelligent Peripheral Management Interface (IPMI) Enable bit<br>1 = IPMI Support mode is enabled; all addresses Acknowledged                                                                                                                    |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   |                                                                                       |                                        |                   |                |  |  |  |  |

|                         |                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                   | esses Acknowle                                                                        |                                        |                   |                |  |  |  |  |

| bit 10                  | 0 = IPMI Sup                                                                                                                                                                                                                                             | port mode is di                                                                                                                                                                                                                                                                                 | sabled                                                                                                                                                                            |                                                                                       | Jugou                                  |                   |                |  |  |  |  |

| bit 10                  | 0 = IPMI Sup<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD                                                                                                                                                                                                       | port mode is di<br>Slave Address<br>is a 10-bit slav                                                                                                                                                                                                                                            | sabled<br>ing bit<br>e address                                                                                                                                                    | SSES ACKNOWIE                                                                         |                                        |                   |                |  |  |  |  |

|                         | 0 = IPMI Sup<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD                                                                                                                                                                                        | oort mode is di<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave                                                                                                                                                                                                                        | sabled<br>ing bit<br>e address<br>address                                                                                                                                         | SSES ACKITOWIG                                                                        |                                        |                   |                |  |  |  |  |

| bit 10<br>bit 9         | 0 = IPMI Sup<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW:</b> Diss                                                                                                                                                                 | oort mode is di<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate                                                                                                                                                                                                      | sabled<br>ing bit<br>e address<br>address<br>Control bit                                                                                                                          | SSES ACKHOWIG                                                                         |                                        |                   |                |  |  |  |  |

|                         | 0 = IPMI Supp<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW:</b> Disa<br>1 = Slew rate                                                                                                                                               | oort mode is di<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave                                                                                                                                                                                                                        | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d                                                                                                                     | SSES ACKHOWIG                                                                         |                                        |                   |                |  |  |  |  |

|                         | 0 = IPMI Sup<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW:</b> Diss<br>1 = Slew rate<br>0 = Slew rate                                                                                                                               | port mode is dia<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable                                                                                                                                                                                  | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d                                                                                                                     | SSES ACKHOWIG                                                                         |                                        |                   |                |  |  |  |  |

| bit 9                   | 0 = IPMI Supp<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW:</b> Disa<br>1 = Slew rate<br>0 = Slew rate<br><b>SMEN:</b> SMBu<br>1 = Enables J                                                                                        | oort mode is di<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>us Input Levels<br>/O pin threshol                                                                                                                           | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d<br>d<br>bit<br>ds compliant wit                                                                                     |                                                                                       |                                        |                   |                |  |  |  |  |

| bit 9                   | 0 = IPMI Supp<br><b>A10M:</b> 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW:</b> Disa<br>1 = Slew rate<br>0 = Slew rate<br><b>SMEN:</b> SMBu<br>1 = Enables II<br>0 = Disables 1                                                                     | port mode is dia<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>is Input Levels<br>(O pin thresholic<br>the SMBus input                                                                                                     | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d<br>d<br>bit<br>ds compliant wit<br>ut thresholds                                                                    | th the SMBus s                                                                        | pecification                           |                   |                |  |  |  |  |

| bit 9<br>bit 8          | 0 = IPMI Supj<br><b>A10M</b> : 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br><b>DISSLW</b> : Disa<br>1 = Slew rate<br>0 = Slew rate<br><b>SMEN</b> : SMBu<br>1 = Enables I<br>0 = Disables 1<br><b>GCEN</b> : Gene<br>1 = Enables<br>reception                 | port mode is dia<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>is Input Levels<br>(O pin threshold<br>the SMBus input<br>ral Call Enable<br>interrupt when                                                                 | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d<br>bit<br>ds compliant wit<br>ut thresholds<br>bit (when opera<br>a general call a                                  | th the SMBus s<br>ating as I <sup>2</sup> C sla <sup>,</sup>                          | pecification                           | 1RSR (module      | is enabled fo  |  |  |  |  |

| bit 9<br>bit 8          | 0 = IPMI Sup<br>A10M: 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br>DISSLW: Disa<br>1 = Slew rate<br>0 = Slew rate<br>SMEN: SMBu<br>1 = Enables I<br>0 = Disables 1<br>GCEN: Gene<br>1 = Enables<br>reception<br>0 = General                                   | port mode is dia<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>is Input Levels<br>(O pin threshold<br>the SMBus input<br>ral Call Enable<br>interrupt when<br>()<br>call address dis                                       | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d<br>d<br>bit<br>ds compliant wit<br>at thresholds<br>bit (when opera<br>a general call a                             | th the SMBus s<br>ating as I <sup>2</sup> C sla<br>address is rece                    | pecification<br>ve)<br>ived in the I2C | 1RSR (module      | is enabled fo  |  |  |  |  |

| bit 9<br>bit 8          | 0 = IPMI Sup<br>A10M: 10-Bit<br>1 = I2C1ADD<br>0 = I2C1ADD<br>DISSLW: Disa<br>1 = Slew rate<br>0 = Slew rate<br>SMEN: SMBu<br>1 = Enables I<br>0 = Disables f<br>GCEN: Gene<br>1 = Enables<br>reception<br>0 = General 0<br>STREN: SCL                   | port mode is dia<br>Slave Address<br>is a 10-bit slav<br>is a 7-bit slave<br>able Slew Rate<br>control disable<br>control enable<br>is Input Levels<br>(O pin threshold<br>the SMBus input<br>ral Call Enable<br>interrupt when<br>()<br>call address dis<br>1 Clock Stretch                    | sabled<br>ing bit<br>e address<br>address<br>Control bit<br>d<br>d<br>bit<br>ds compliant wit<br>ut thresholds<br>bit (when opera<br>a general call a<br>sabled<br>Enable bit (wh | th the SMBus s<br>ating as I <sup>2</sup> C sla<br>address is rece                    | pecification<br>ve)<br>ived in the I2C | 1RSR (module      | is enabled fo  |  |  |  |  |