Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | M8C                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 24MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, IrDA, SPI, UART/USART                                     |

| Peripherals                | LVD, POR, PWM, WDT                                                          |

| Number of I/O              | 24                                                                          |

| Program Memory Size        | 16KB (16K x 8)                                                              |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 1K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.25V                                                                  |

| Data Converters            | A/D 4x14b; D/A 4x9b                                                         |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                                              |

| Supplier Device Package    | 28-SSOP                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/cy8c28403-24pvxi |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **PSoC Functional Overview**

The PSoC family consists of many devices with On-Chip Controllers. These devices are designed to replace multiple traditional MCU based system components with one low cost single chip programmable component. A PSoC device includes configurable analog blocks, digital blocks, and interconnections. This architecture enables the user to create customized peripheral configurations to match the requirements of each individual application. In addition, a fast CPU, Flash program memory, SRAM data memory, and configurable I/O are included in a range of convenient pinouts and packages.

The CY8C28xxx group of PSoC devices described in this datasheet have multiple resource configuration options available. Therefore, not every resource mentioned in this datasheet is available for each CY8C28xxx subgroup. The CY8C28x45 subgroup has a full feature set of all resources described. There are six more segmented subgroups that allow designers to use a device with only the resources and functionality necessary for a specific application. See Table 2 on page 9 to determine the resources available for each CY8C28xxx subgroup. The same information is also presented in more detail in the Ordering Information section.

The architecture for this specific PSoC device family, as shown in the Logic Block Diagram on page 1, consists of four main areas: PSoC Core, Digital System, Analog System, and System Resources. The configurable global bus system allows all the device resources to be combined into a complete custom system. PSoC CY8C28xxx family devices have up to six I/O ports that connect to the global digital and analog interconnects, providing access to up to 12 digital blocks and up to 16 analog blocks.

### The PSoC Core

The PSoC Core is a powerful engine that supports a rich feature set. The core includes a CPU, memory, clocks, and configurable general Purpose I/O (GPIO). The M8C CPU core is a powerful processor with speeds up to 24 MHz, providing a four MIPS 8-bit Harvard architecture microcontroller.

Memory encompasses 16K bytes of Flash for program storage, 1K bytes of SRAM for data storage. The PSoC device incorporates flexible internal clock generators, including a 24 MHz internal main oscillator (IMO) accurate to 2.5% over temperature and voltage. A low power 32 kHz internal low speed oscillator (ILO) is provided for the sleep timer and watch dog timer (WDT). The 32.768 kHz external crystal oscillator (ECO) is available for use as a real time clock (RTC) and can optionally generate a crystal-accurate 24 MHz system clock using a PLL.

PSoC GPIOs provide connections to the CPU, and digital and analog resources. Each pin's drive mode may be selected from 8 options, which allows great flexibility in external interfacing. Every pin also has the capability to generate a system interrupt on high level, low level, and change from last read.

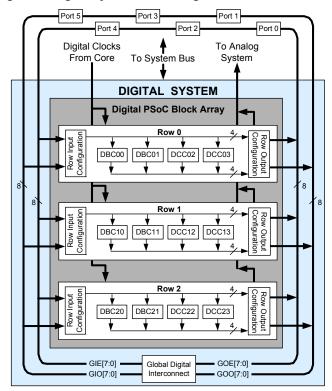

### The Digital System

The Digital System is composed of up to 12 configurable digital PSoC blocks. Each block is an 8-bit resource that can be used alone or combined with other blocks to create 8, 16, 24, and

32-bit peripherals, which are called user modules. The digital blocks can be connected to any GPIO through a series of global buses that can route any signal to any pin.

Figure 2. Digital System Block Diagram<sup>[1]</sup>

Digital peripheral configurations include:

- PWMs (8- and 16-bit, One-shot and Multi-shot capability)

- PWMs with Dead band/Kill (8- and 16-bit)

- Counters (8 to 32 bit)

- Timers (8 to 32 bit)

- Full-duplex 8-bit UARTs (up to 3) with selectable parity

- Half-duplex 8-bit UARTs (up to 6) with selectable parity

- Variable length SPI slave and master

Up to 6 total slaves and masters (8-bit)

Supports 8 to 16 bit operation

- I<sup>2</sup>C slave, master, or multi-master (up to 2 available as System Resources)

- IrDA (up to 3)

- Pseudo Random Sequence Generators (8 to 32 bit)

- Cyclical Redundancy Checker/Generator (16 bit)

- Shift Register (2 to 32 bit)

#### Note

1. CY8C28x52 devices do not have digital block row 2. They have two digital rows with eight total digital blocks.

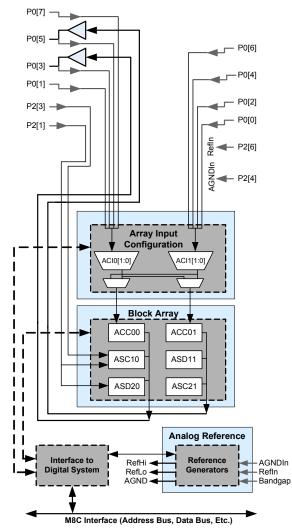

Figure 6. Analog System Block Diagram for CY8C28x23 Devices

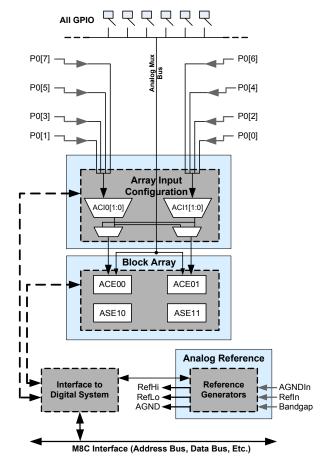

Figure 7. Analog System Block Diagram for CY8C28x13 Devices

The devices covered by this datasheet all have the same architecture, specifications, and ratings. However, the amount of some hardware resources varies from device to device within the group. The following table lists resources available for the specific device subgroups covered by this datasheet.

| Table 2. | CY8C28xxx Device Characteristics |  |

|----------|----------------------------------|--|

|----------|----------------------------------|--|

| PSoC Part<br>Number | CapSense | Digital<br>Blocks | Regular<br>Analog<br>Blocks | Limited<br>Analog<br>Blocks | HW I <sup>2</sup> C | Decimators | Digital<br>I/O | Analog<br>Inputs | Analog<br>Outputs | Analog<br>Mux<br>Buses |

|---------------------|----------|-------------------|-----------------------------|-----------------------------|---------------------|------------|----------------|------------------|-------------------|------------------------|

| CY8C28x03           | Ν        | 12                | 0                           | 0                           | 2                   | 0          | up to 24       | up to 8          | 0                 | 0                      |

| CY8C28x13           | Y        | 12                | 0                           | 4                           | 1                   | 2          | up to 40       | up to 40         | 0                 | 2                      |

| CY8C28x23           | Ν        | 12                | 6                           | 0                           | 2                   | 2          | up to 44       | up to 10         | 2                 | 0                      |

| CY8C28x33           | Y        | 12                | 6                           | 4                           | 1                   | 4          | up to 40       | up to 40         | 2                 | 2                      |

| CY8C28x43           | Ν        | 12                | 12                          | 0                           | 2                   | 4          | up to 44       | up to 44         | 4                 | 2                      |

| CY8C28x45           | Y        | 12                | 12                          | 4                           | 2                   | 4          | up to 44       | up to 44         | 4                 | 2                      |

| CY8C28x52           | Y        | 8                 | 12                          | 4                           | 1                   | 4          | up to 24       | up to 24         | 4                 | 2                      |

## **Register Reference**

This section lists the registers of the CY8C28xxx PSoC devices. For detailed register information, reference the *PSoC Technical Reference Manual* for CY8C28xxx PSoC devices.

### **Register Conventions**

The register conventions specific to this section are listed in the following table.

| Convention | Description                  |  |  |  |  |  |  |

|------------|------------------------------|--|--|--|--|--|--|

| R          | Read register or bit(s)      |  |  |  |  |  |  |

| W          | Write register or bit(s)     |  |  |  |  |  |  |

| L          | Logical register or bit(s)   |  |  |  |  |  |  |

| С          | Clearable register or bit(s) |  |  |  |  |  |  |

| #          | Access is bit specific       |  |  |  |  |  |  |

### **Register Mapping Tables**

CY8C28xxx PSoC devices have a total register address space of 512 bytes. The register space is referred to as I/O space and is divided into two banks. The XIO bit in the Flag register (CPU\_F) determines which bank of registers CPU instructions access. When the XIO bit is set the registers in Bank 1 are accessed by CPU instructions. When the XIO bit is cleared the registers in Bank 0 are accessed by CPU instructions.

**Note** In the following register mapping tables, blank fields are reserved and should not be accessed.

#### Table 10. CY8C28x13 Register Map Bank 0 Table: User Space

|                                  | CY8C28X13 R  |          |                      |              |        |                    |              | -        |                      |              | -      |

|----------------------------------|--------------|----------|----------------------|--------------|--------|--------------------|--------------|----------|----------------------|--------------|--------|

| Name                             | Addr (0,Hex) |          | Name                 | Addr (0,Hex) | Access | Name               | Addr (0,Hex) | Access   | Name                 | Addr (0,Hex) | Access |

| PRT0DR<br>PRT0IE                 | 00           | RW<br>RW | DBC20DR0<br>DBC20DR1 | 40           | #<br>W |                    | 80<br>81     |          | RDI2RI<br>RDI2SYN    | C0<br>C1     | RW     |

|                                  |              |          |                      | 41           |        |                    |              |          |                      |              |        |

| PRTOGS                           | 02           | RW       | DBC20DR2             | 42           | RW     |                    | 82           |          | RDI2IS               | C2           | RW     |

| PRT0DM2                          | 03           | RW       | DBC20CR0             | 43           | #      |                    | 83           |          | RDI2LT0              | C3           |        |

| PRT1DR                           | 04           | RW       | DBC21DR0             | 44           | #      |                    | 84           |          | RDI2LT1              | C4           | RW     |

| PRT1IE                           | 05           | RW       | DBC21DR1             | 45           | W      | -                  | 85           |          | RDI2RO0              | C5           | RW     |

| PRT1GS                           | 06           | RW       | DBC21DR2             | 46           | RW     | -                  | 86           |          | RDI2RO1              | C6           | RW     |

| PRT1DM2                          | 07           | RW       | DBC21CR0             | 47           | #      |                    | 87           |          | RDI2DSM              | C7           | RW     |

| PRT2DR                           | 08           | RW       | DCC22DR0             | 48           | #      |                    | 88           |          |                      | C8           |        |

| PRT2IE                           | 09           | RW       | DCC22DR1             | 49           | W      |                    | 89           |          |                      | C9           |        |

| PRT2GS                           | 0A           | RW       | DCC22DR2             | 4A           | RW     |                    | 8A           |          |                      | CA           | !      |

| PRT2DM2                          | 0B           | RW       | DCC22CR0             | 4B           | #      |                    | 8B           |          |                      | CB           | '      |

| PRT3DR                           | 0C           | RW       | DCC23DR0             | 4C           | #      |                    | 8C           |          |                      | CC           |        |

| PRT3IE                           | 0D           | RW       | DCC23DR1             | 4D           | W      |                    | 8D           |          |                      | CD           |        |

| PRT3GS                           | 0E           | RW       | DCC23DR2             | 4E           | RW     |                    | 8E           |          |                      | CE           |        |

| PRT3DM2                          | 0F           | RW       | DCC23CR0             | 4F           | #      |                    | 8F           |          |                      | CF           |        |

| PRT4DR                           | 10           | RW       |                      | 50           |        |                    | 90           |          | CUR_PP               | D0           | RW     |

| PRT4IE                           | 11           | RW       |                      | 51           |        |                    | 91           |          | STK_PP               | D1           | RW     |

| PRT4GS                           | 12           | RW       |                      | 52           |        |                    | 92           |          |                      | D2           |        |

| PRT4DM2                          | 13           | RW       |                      | 53           |        |                    | 93           |          | IDX_PP               | D3           | RW     |

| PRT5DR                           | 14           | RW       |                      | 54           |        |                    | 94           |          | MVR_PP               | D4           | RW     |

| PRT5IE                           | 15           | RW       |                      | 55           |        |                    | 95           |          | MVW_PP               | D5           | RW     |

| PRT5GS                           | 16           | RW       |                      | 56           |        |                    | 96           |          | I2C0_CFG             | D6           | RW     |

| PRT5DM2                          | 17           | RW       |                      | 57           |        |                    | 97           |          | I2C0_SCR             | D7           | #      |

|                                  | 18           |          |                      | 58           |        |                    | 98           |          | 12C0_DR              | D8           | RW     |

|                                  | 19           |          |                      | 59           |        |                    | 99           |          | I2C0_MSCR            | D9           | #      |

|                                  | 1A           |          |                      | 5A           |        |                    | 9A           |          | INT_CLR0             | DA           | RW     |

|                                  | 1B           |          |                      | 5B           |        |                    | 9B           |          | INT_CLR1             | DB           | RW     |

|                                  | 1C           |          |                      | 5C           |        |                    | 9C           |          | INT_CLR2             | DC           | RW     |

|                                  | 1D           |          |                      | 5D           |        |                    | 9D           |          | INT_CLR3             | DD           | RW     |

|                                  | 1E           |          |                      | 5E           |        |                    | 9E           |          | INT_MSK3             | DE           | RW     |

|                                  | 1F           |          |                      | 5F           |        |                    | 9F           |          | INT_MSK2             | DF           | RW     |

| DBC00DR0                         | 20           | #        |                      | 60           |        | DEC0_DH            | A0           | RC       | INT_MSK0             | E0           | RW     |

| DBC00DR1                         | 21           | W        | AMUX_CFG             | 61           | RW     | DEC0_DL            | A1           | RC       | INT_MSK1             | E1           | RW     |

| DBC00DR2                         | 22           | RW       |                      | 62           |        | DEC1_DH            | A2           | RC       | INT_VC               | E2           | RC     |

| DBC00CR0                         | 23           | #        |                      | 63           |        | DEC1_DL            | A3           | RC       | RES_WDT              | E3           | W      |

| DBC01DR0                         | 24           | #        |                      | 64           |        |                    | A4           |          |                      | E4           |        |

| DBC01DR1                         | 25           | W        |                      | 65           |        |                    | A5           |          |                      | E5           |        |

| DBC01DR2                         | 26           | RW       |                      | 66           |        |                    | A6           |          | DEC_CR0*             | E6           | RW     |

| DBC01CR0                         | 27           | #        |                      | 67           |        |                    | A7           |          | DEC_CR1*             | E7           | RW     |

| DCC02DR0                         | 28           | #        |                      | 68           |        | MUL1_X             | A8           | W        | MUL0_X               | E8           | W      |

| DCC02DR1                         | 29           | W        |                      | 69           |        | MUL1_Y             | A9           | W        | MUL0_Y               | E9           | W      |

| DCC02DR2                         | 2A           | RW       | SADC_DH              | 6A           | RW     | MUL1_DH            | AA           | R        | MUL0_DH              | EA           | R      |

| DCC02CR0                         | 2B           | #        | SADC_DL              | 6B           | RW     | MUL1_DL            | AB           | R        | MUL0_DL              | EB           | R      |

| DCC03DR0                         | 2C           | #        | TMP_DR0              | 6C           | RW     | ACC1_DR1           | AC           | RW       | ACC0_DR1             | EC           | RW     |

| DCC03DR1                         | 2D           | W        | TMP_DR1              | 6D           | RW     | ACC1_DR0           | AD           | RW       | ACC0_DR0             | ED           | RW     |

| DCC03DR2                         | 2E           | RW       | TMP_DR2              | 6E           | RW     | ACC1_DR3           | AE           | RW       | ACC0_DR3             | EE           | RW     |

| DCC03CR0                         | 2F           | #        | TMP_DR3              | 6F           | RW     | ACC1_DR2           | AF           | RW       | ACC0_DR2             | EF           | RW     |

| DBC10DR0                         | 30           | #        |                      | 70           |        | RDI0RI             | B0           | RW       |                      | F0           |        |

| DBC10DR1                         | 31           | W        |                      | 71           |        | RDI0SYN            | B1           | RW       |                      | F1           |        |

| DBC10DR2                         | 32           | RW       |                      | 72           |        | RDI0IS             | B2           | RW       |                      | F2           |        |

| DBC10CR0                         | 33           | #        |                      | 73           |        | RDI0LT0            | B3           | RW       |                      | F3           |        |

| DBC11DR0                         | 34           | #        |                      | 74           |        | RDI0LT1            | B4           | RW       |                      | F4           |        |

| DBC11DR1                         | 35           | W        |                      | 75           |        | RDI0RO0            | B5           | RW       |                      | F5           |        |

| DBC11DR2                         | 36           | RW       |                      | 76           |        | RDI0RO1            | B6           | RW       |                      | F6           |        |

| DBC11CR0                         | 37           | #        |                      | 77           | 1      | RDI0DSM            | B7           | RW       | CPU_F                | F7           | RL     |

| DCC12DR0                         | 38           | #        |                      | 78           | 1      | RDI1RI             | B8           | RW       |                      | F8           | 1      |

| DCC12DR1                         | 39           | W        |                      | 79           |        | RDI1SYN            | B9           | RW       |                      | F9           |        |

| DCC12DR2                         | 3A           | RW       |                      | 7A           |        | RDI1IS             | BA           | RW       |                      | FA           | 1      |

| DCC12CR0                         | 3B           | #        |                      | 7B           |        | RDI1LT0            | BB           | RW       |                      | FB           | +      |

| DCC13DR0                         | 3C           | #        |                      | 7D<br>7C     |        | RDI1LT1            | BC           | RW       | DAC1 D               | FC           | RW     |

|                                  | 30<br>3D     | #<br>W   |                      | 70<br>7D     |        | RDI1R00            | BD           | RW       | DACI_D<br>DAC0 D     | FD           | RW     |

| DCC13DR1                         | 50           | ~~       |                      |              |        |                    |              |          |                      |              |        |

| DCC13DR1<br>DCC13DR2             | 3E           | RW/      |                      | 7E           |        | RDI1RO1            | RF           | R\//     | CPU SCR1             | FF           |        |

| DCC13DR1<br>DCC13DR2<br>DCC13CR0 | 3E<br>3F     | RW<br>#  |                      | 7E<br>7F     |        | RDI1RO1<br>RDI1DSM | BE<br>BF     | RW<br>RW | CPU_SCR1<br>CPU_SCR0 | FE<br>FF     | #      |

### Table 13. CY8C28x23 Register Map Bank 1 Table: Configuration Space

|                     |              |              | мар валк 1         |                    |              |             |                    |        |                    |                    |              |

|---------------------|--------------|--------------|--------------------|--------------------|--------------|-------------|--------------------|--------|--------------------|--------------------|--------------|

| Name<br>PRT0DM0     | Addr (1,Hex) | Access<br>RW | Name<br>DBC20FN    | Addr (1,Hex)<br>40 | Access<br>RW | Name        | Addr (1,Hex)<br>80 | Access | Name<br>RDI2RI     | Addr (1,Hex)<br>C0 | Access<br>RW |

| PRT0DM0             | 00           | RW           | DBC20FN<br>DBC20IN | 40                 | RW           |             | 81                 |        | RDI2RI<br>RDI2SYN  | C0<br>C1           | RW           |

| PRTODMI             | 01           | RW           | DBC200U            |                    | RW           |             | 82                 |        | RDI2STN            | C1<br>C2           | RW           |

|                     |              |              |                    | 42                 |              |             |                    |        |                    |                    |              |

| PRT0IC1<br>PRT1DM0  | 03           | RW           | DBC20CR1           | 43                 | RW           |             | 83                 |        | RDI2LT0            | C3                 | RW           |

|                     | 04           | RW           | DBC21FN            | 44                 | RW           |             | 84                 |        | RDI2LT1<br>RDI2RO0 | C4                 | RW           |

| PRT1DM1             | 05           | RW           | DBC21IN            | 45                 | RW           |             | 85                 |        |                    | C5                 | RW           |

| PRT1IC0             | 06           | RW           | DBC21OU            | 46                 | RW           |             | 86                 |        | RDI2RO1            | C6                 | RW           |

| PRT1IC1             | 07           | RW           | DBC21CR1           | 47                 | RW           |             | 87                 |        | RDI2DSM            | C7                 | RW           |

| PRT2DM0             | 08           | RW           | DCC22FN            | 48                 | RW           |             | 88                 |        |                    | C8                 |              |

| PRT2DM1             | 09           | RW           | DCC22IN            | 49                 | RW           |             | 89                 |        |                    | C9                 |              |

| PRT2IC0             | 0A           | RW           | DCC22OU            | 4A                 | RW           |             | 8A                 |        |                    | CA                 |              |

| PRT2IC1             | 0B           | RW           | DCC22CR1           | 4B                 | RW           |             | 8B                 |        |                    | СВ                 |              |

| PRT3DM0             | 00           | RW           | DCC23FN            | 4C                 | RW           |             | 8C                 |        |                    | CC                 |              |

| PRT3DM1             | 0D           | RW           | DCC23IN            | 4D                 | RW           |             | 8D                 |        |                    | CD                 |              |

| PRT3IC0             | 0E           | RW           | DCC23OU            | 4E                 | RW           |             | 8E                 |        |                    | CE                 |              |

| PRT3IC1             | 0F           | RW           | DCC23CR1           | 4F                 | RW           |             | 8F                 |        |                    | CF                 |              |

| PRT4DM0             | 10           | RW           |                    | 50                 |              |             | 90                 |        | GDI_O_IN           | D0                 | RW           |

| PRT4DM1             | 11           | RW           |                    | 51                 |              | DEC0_CR0    | 91                 | RW     | GDI_E_IN           | D1                 | RW           |

| PRT4IC0             | 12           | RW           |                    | 52                 |              | DEC_CR3     | 92                 | RW     | GDI_O_OU           | D2                 | RW           |

| PRT4IC1             | 13           | RW           |                    | 53                 |              |             | 93                 | RW     | GDI_E_OU           | D3                 | RW           |

| PRT5DM0             | 14           | RW           |                    | 54                 |              |             | 94                 | RW     | DEC0_CR            | D4                 | RW           |

| PRT5DM1             | 15           | RW           |                    | 55                 |              | DEC1_CR0    | 95                 | RW     | DEC1_CR            | D5                 | RW           |

| PRT5IC0             | 16           | RW           |                    | 56                 |              |             | 96                 |        |                    | D6                 |              |

| PRT5IC1             | 17           | RW           |                    | 57                 |              |             | 97                 |        |                    | D7                 |              |

|                     | 18           |              |                    | 58                 |              |             | 98                 |        |                    | D8                 |              |

|                     | 19           |              |                    | 59                 |              |             | 99                 |        |                    | D9                 |              |

|                     | 1A           |              |                    | 5A                 |              | DEC_CR5     | 9A                 | RW     |                    | DA                 |              |

|                     | 1B           |              |                    | 5B                 |              |             | 9B                 |        |                    | DB                 |              |

|                     | 1C           |              |                    | 5C                 |              |             | 9C                 |        |                    | DC                 |              |

|                     | 1D           |              |                    | 5D                 |              |             | 9D                 |        | OSC_GO_EN          | DD                 | RW           |

|                     | 1E           |              |                    | 5E                 |              |             | 9E                 |        | OSC_CR4            | DE                 | RW           |

|                     | 1F           |              |                    | 5F                 |              |             | 9F                 |        | OSC_CR3            | DF                 | RW           |

| DBC00FN             | 20           | RW           | CLK_CR0            | 60                 | RW           | GDI_O_IN_CR | A0                 | RW     | OSC_CR0            | E0                 | RW           |

| DBC00IN             | 21           | RW           | CLK_CR1            | 61                 | RW           | GDI_E_IN_CR | A1                 | RW     | OSC_CR1            | E1                 | RW           |

| DBC00OU             | 22           | RW           | ABF_CR0            | 62                 | RW           | GDI_O_OU_CR | A2                 | RW     | OSC_CR2            | E2                 | RW           |

| DBC00CR1            | 23           | RW           | AMD_CR0            | 63                 | RW           | GDI_E_OU_CR | A3                 | RW     | VLT_CR             | E3                 | RW           |

| DBC01FN             | 24           | RW           | CMP_GO_EN          | 64                 | RW           | RTC_H       | A4                 | RW     | VLT_CMP            | E4                 | RW           |

| DBC01IN             | 25           | RW           |                    | 65                 |              | RTC_M       | A5                 | RW     |                    | E5                 |              |

| DBC01OU             | 26           | RW           | AMD_CR1            | 66                 | RW           | RTC_S       | A6                 | RW     |                    | E6                 |              |

| DBC01CR1            | 27           | RW           | ALT_CR0            | 67                 | RW           | RTC_CR      | A7                 | RW     |                    | E7                 |              |

| DCC02FN             | 28           | RW           |                    | 68                 |              |             | A8                 |        | IMO_TR             | E8                 | RW           |

| DCC02IN             | 29           | RW           | CLK_CR2            | 69                 | RW           |             | A9                 |        | ILO_TR             | E9                 | RW           |

| DCC02OU             | 2A           | RW           |                    | 6A                 |              |             | AA                 |        | BDG_TR             | EA                 | RW           |

| DCC02CR1            | 2B           | RW           | I2C1_CFG           | 6B                 | RW           |             | AB                 |        | ECO_TR             | EB                 | RW           |

| DCC03FN             | 2C           | RW           | TMP_DR0            | 6C                 | RW           |             | AC                 |        |                    | EC                 |              |

| DCC03IN             | 2D           | RW           | TMP_DR1            | 6D                 | RW           | I2C0_ADDR   | AD                 | RW     |                    | ED                 |              |

| DCC03OU             | 2E           | RW           | TMP_DR2            | 6E                 | RW           | I2C1_ADDR   | AE                 | RW     |                    | EE                 |              |

| DCC03CR1            | 2F           | RW           | TMP_DR3            | 6F                 | RW           | AMUX_CLK    | AF                 | RW     |                    | EF                 |              |

| DBC10FN             | 30           | RW           |                    | 70                 |              | RDIORI      | B0                 | RW     |                    | F0                 |              |

| DBC10IN             | 31           | RW           |                    | 71                 |              | RDI0SYN     | B1                 | RW     |                    | F1                 |              |

| DBC10OU             | 32           | RW           |                    | 72                 |              | RDI0IS      | B2                 | RW     |                    | F2                 |              |

| DBC10CR1            | 33           | RW           |                    | 73                 |              | RDI0LT0     | B3                 | RW     |                    | F3                 |              |

| DBC11FN             | 34           | RW           |                    | 74                 |              | RDI0LT1     | B4                 | RW     |                    | F4                 |              |

| DBC11IN             | 35           | RW           |                    | 75                 |              | RDI0RO0     | B5                 | RW     |                    | F5                 |              |

| DBC110U             | 36           | RW           |                    | 76                 |              | RDI0RO1     | B6                 | RW     |                    | F6                 |              |

| DBC11CR1            | 37           | RW           |                    | 77                 |              | RDIODSM     | B7                 | RW     | CPU_F              | F7                 | RL           |

| DCC12FN             | 38           | RW           | ľ                  | 78                 |              | RDI1RI      | B8                 | RW     |                    | F8                 |              |

| DCC12IN             | 39           | RW           |                    | 79                 |              | RDI1SYN     | В9                 | RW     |                    | F9                 |              |

| DCC12OU             | 3A           | RW           |                    | 7A                 |              | RDI1IS      | BA                 | RW     | FLS_PR1            | FA                 | RW           |

| DCC12CR1            | 3B           | RW           |                    | 7B                 |              | RDI1LT0     | BB                 | RW     |                    | FB                 |              |

| DCC13FN             | 3C           | RW           | l                  | 7C                 |              | RDI1LT1     | BC                 | RW     |                    | FC                 |              |

| DCC13IN             | 3D           | RW           |                    | 7D                 |              | RDI1RO0     | BD                 | RW     |                    | FD                 |              |

|                     | 35<br>3E     | RW           |                    | 76<br>7E           |              | RDI1R01     | BE                 | RW     | CPU SCR1           | FE                 | #            |

| DCC13CU             |              |              | 8                  |                    | ļ            |             |                    |        |                    |                    |              |

| DCC13OU<br>DCC13CR1 | 3F           | RW           |                    | 7F                 |              | RDI1DSM     | BF                 | RW     | CPU SCR0           | FF                 | #            |

#### Table 16. CY8C28x43 Register Map Bank 0 Table: User Space

|                      | C10C20X43 K                 |     |                      |                       |    |          |              | _      |                                  |              |          |

|----------------------|-----------------------------|-----|----------------------|-----------------------|----|----------|--------------|--------|----------------------------------|--------------|----------|

| Name                 | Addr (0,Hex)                |     | Name                 | Addr (0,Hex)          |    | Name     | Addr (0,Hex) | Access | Name                             | Addr (0,Hex) |          |

| PRT0DR               | 00                          | RW  | DBC20DR0             | 40                    | #  | ASC10CR0 | 80           | RW     | RDI2RI                           | C0           | RW       |

| PRTOIE               | 01                          | RW  | DBC20DR1             | 41                    | W  | ASC10CR1 | 81           | RW     | RDI2SYN                          | C1           | RW       |

| PRT0GS               | 02                          | RW  | DBC20DR2             | 42                    | RW | ASC10CR2 | 82           | RW     | RDI2IS                           | C2           | RW       |

| PRT0DM2              | 03                          | RW  | DBC20CR0             | 43                    | #  | ASC10CR3 | 83           | RW     | RDI2LT0                          | C3           | RW       |

| PRT1DR               | 04                          | RW  | DBC21DR0             | 44                    | #  | ASD11CR0 | 84           | RW     | RDI2LT1                          | C4           | RW       |

| PRT1IE               | 05                          | RW  | DBC21DR1             | 45                    | W  | ASD11CR1 | 85           | RW     | RDI2RO0                          | C5           | RW       |

| PRT1GS               | 06                          | RW  | DBC21DR2             | 46                    | RW | ASD11CR2 | 86           | RW     | RDI2RO1                          | C6           | RW       |

| PRT1DM2              | 07                          | RW  | DBC21CR0             | 47                    | #  | ASD11CR3 | 87           | RW     | RDI2DSM                          | C7           | RW       |

| PRT2DR               | 08                          | RW  | DCC22DR0             | 48                    | #  | ASC12CR0 | 88           | RW     |                                  | C8           |          |

| PRT2IE               | 09                          | RW  | DCC22DR1             | 49                    | W  | ASC12CR1 | 89           | RW     |                                  | C9           |          |

| PRT2GS               | 0A                          | RW  | DCC22DR2             | 4A                    | RW | ASC12CR2 | 8A           | RW     |                                  | CA           |          |

| PRT2DM2              | 0B                          | RW  | DCC22CR0             | 4B                    | #  | ASC12CR3 | 8B           | RW     |                                  | CB           |          |

| PRT3DR               | 0C                          | RW  | DCC23DR0             | 4C                    | #  | ASD13CR0 | 8C           | RW     |                                  | CC           |          |

| PRT3IE               | 0D                          | RW  | DCC23DR1             | 4D                    | W  | ASD13CR1 | 8D           | RW     |                                  | CD           |          |

| PRT3GS               | 0E                          | RW  | DCC23DR2             | 4E                    | RW | ASD13CR2 | 8E           | RW     |                                  | CE           |          |

| PRT3DM2              | 0F                          | RW  | DCC23CR0             | 4F                    | #  | ASD13CR3 | 8F           | RW     |                                  | CF           |          |

| PRT4DR               | 10                          | RW  |                      | 50                    |    | ASD20CR0 | 90           | RW     | CUR_PP                           | D0           | RW       |

| PRT4IE               | 11                          | RW  |                      | 51                    |    | ASD20CR1 | 91           | RW     | STK_PP                           | D1           | RW       |

| PRT4GS               | 12                          | RW  |                      | 52                    |    | ASD20CR2 | 92           | RW     |                                  | D2           |          |

| PRT4DM2              | 13                          | RW  |                      | 53                    |    | ASD20CR3 | 93           | RW     | IDX_PP                           | D3           | RW       |

| PRT5DR               | 14                          | RW  |                      | 54                    |    | ASC21CR0 | 94           | RW     | MVR_PP                           | D4           | RW       |

| PRT5IE               | 15                          | RW  |                      | 55                    |    | ASC21CR1 | 95           | RW     | MVW_PP                           | D5           | RW       |

| PRT5GS               | 16                          | RW  |                      | 56                    |    | ASC21CR2 | 96           | RW     | I2C0_CFG                         | D6           | RW       |

| PRT5DM2              | 17                          | RW  |                      | 57                    |    | ASC21CR3 | 97           | RW     | I2C0_SCR                         | D7           | #        |

|                      | 18                          |     |                      | 58                    |    | ASD22CR0 | 98           | RW     | I2C0_DR                          | D8           | RW       |

|                      | 19                          |     |                      | 59                    |    | ASD22CR1 | 99           | RW     | I2C0_MSCR                        | D9           | #        |

|                      | 1A                          |     |                      | 5A                    |    | ASD22CR2 | 9A           | RW     | INT_CLR0                         | DA           | RW       |

|                      | 1B                          |     |                      | 5B                    |    | ASD22CR3 | 9B           | RW     | INT_CLR1                         | DB           | RW       |

|                      | 1C                          |     |                      | 5C                    |    | ASC23CR0 | 9C           | RW     | INT_CLR2                         | DC           | RW       |

|                      | 1D                          |     |                      | 5D                    |    | ASC23CR1 | 9D           | RW     | INT_CLR3                         | DD           | RW       |

|                      | 1E                          |     |                      | 5E                    |    | ASC23CR2 | 9E           | RW     | INT_MSK3                         | DE           | RW       |

|                      | 1F                          |     |                      | 5F                    |    | ASC23CR3 | 9F           | RW     | INT_MSK2                         | DF           | RW       |

| DBC00DR0             | 20                          | #   | AMX_IN               | 60                    | RW | DEC0_DH  | A0           | RC     | INT_MSK0                         | E0           | RW       |

| DBC00DR1             | 21                          | W   | AMUX CFG             | 61                    | RW | DEC0 DL  | A1           | RC     | INT MSK1                         | E1           | RW       |

| DBC00DR2             | 22                          | RW  | CLK CR3              | 62                    | RW | DEC1 DH  | A2           | RC     | INT VC                           | E2           | RC       |

| DBC00CR0             | 23                          | #   | ARF CR               | 63                    | RW | DEC1 DL  | A3           | RC     | RES WDT                          | E3           | W        |

| DBC01DR0             | 24                          | #   | CMP_CR0              | 64                    | #  | DEC2 DH  | A4           | RC     | I2C1 SCR                         | E4           | #        |

| DBC01DR1             | 25                          | W   | ASY CR               | 65                    | #  | DEC2 DL  | A5           | RC     | I2C1 MSCR                        | E5           | #        |

| DBC01DR2             | 26                          | RW  | CMP CR1              | 66                    | RW | DEC3 DH  | A6           | RC     | DEC CR0*                         | E6           | RW       |

| DBC01CR0             | 27                          | #   | I2C1 DR              | 67                    | RW | DEC3 DL  | A7           | RC     | DEC CR1*                         | E7           | RW       |

| DCC02DR0             | 28                          | #   |                      | 68                    |    | MUL1 X   | A8           | W      | MUL0 X                           | E8           | W        |

| DCC02DR1             | 29                          | W   |                      | 69                    |    | MUL1 Y   | A9           | W      | MULO Y                           | E9           | W        |

| DCC02DR2             | 20<br>2A                    | RW  | SADC DH              | 6A                    | RW | MUL1 DH  | AA           | R      | MUL0 DH                          | EA           | R        |

| DCC02CR0             | 2B                          | #   | SADC DL              | 6B                    | RW | MUL1 DL  | AB           | R      | MULO DL                          | EB           | R        |

| DCC03DR0             | 20                          | #   | TMP DR0              | 6C                    | RW | ACC1 DR1 | AC           | RW     | ACC0 DR1                         | EC           | RW       |

| DCC03DR1             | 20<br>2D                    | W   | TMP_DR1              | 6D                    | RW | ACC1 DR0 | AD           | RW     | ACC0 DR0                         | ED           | RW       |

| DCC03DR2             | 25<br>2E                    | RW  | TMP_DR2              | 6E                    | RW | ACC1_DR3 | AE           |        | ACC0_DR3                         | EE           | RW       |

| DCC03DR2             | 2E<br>2F                    | #   | TMP_DR3              | 6F                    | RW | ACC1_DR3 | AL           | RW     | ACC0_DR2                         | EF           | RW       |

| DBC10DR0             | 30                          | #   | ACB00CR3             | 70                    | RW | RDIORI   | B0           | RW     | A000_DI12                        | F0           | 1.00     |

| DBC10DR0             | 31                          | W W | ACB00CR0             | 70                    | RW | RDIOSYN  | B1           | RW     |                                  | F1           |          |

| DBC10DR1             | 32                          | RW  | ACB00CR0             | 71                    | RW | RDIOIS   | B1<br>B2     | RW     |                                  | F2           | ┼────    |

| DBC10DR2<br>DBC10CR0 | 33                          | #   | ACB00CR1<br>ACB00CR2 | 72                    | RW | RDI0LT0  | B2<br>B3     | RW     |                                  | F2<br>F3     |          |

| DBC10CR0<br>DBC11DR0 | 33                          | #   | ACB00CR2<br>ACB01CR3 | 73                    | RW | RDI0LT1  | B3<br>B4     | RW     |                                  | F3<br>F4     |          |

|                      |                             |     |                      |                       |    |          |              |        |                                  |              |          |

| DBC11DR1             | 35                          | W   | ACB01CR0             | 75                    | RW | RDI0RO0  | B5           | RW     |                                  | F5           | ┨─────   |

| DBC11DR2             | 36                          | RW  | ACB01CR1             | 76                    | RW | RDIORO1  | B6           | RW     | CDU E                            | F6           |          |

| DBC11CR0             | 37                          | #   | ACB01CR2             | 77                    | RW | RDIODSM  | B7           | RW     | CPU_F                            | F7           | RL       |

| DCC12DR0             | 38                          | #   | ACB02CR3             | 78                    | RW | RDI1RI   | B8           | RW     |                                  | F8           | ───      |

| DCC12DR1             | 39                          | W   | ACB02CR0             | 79                    | RW | RDI1SYN  | B9           | RW     |                                  | F9           | ───      |

| DCC12DR2             | 3A                          | RW  | ACB02CR1             | 7A                    | RW | RDI1IS   | BA           | RW     |                                  | FA           | ───      |

| DCC12CR0             | 3B                          | #   | ACB02CR2             | 7B                    | RW | RDI1LT0  | BB           | RW     |                                  | FB           | ───      |

| DCC13DR0             | 3C                          | #   | ACB03CR3             | 7C                    | RW | RDI1LT1  | BC           | RW     |                                  | FC           | <u> </u> |

| DCC13DR1             | 3D                          | W   | ACB03CR0             | 7D                    | RW | RDI1RO0  | BD           | RW     |                                  | FD           |          |

| DCC13DR2             | 3E                          | RW  | ACB03CR1             | 7E                    | RW | RDI1RO1  | BE           | RW     | CPU_SCR1                         | FE           | #        |

|                      |                             |     |                      |                       |    |          |              |        |                                  |              |          |

| DCC13CR0             | 3F<br>e Reserved and should | #   | ACB03CR2             | 7F<br># Access is bit | RW | RDI1DSM  | BF           | RW     | CPU_SCR0<br>ceptions" on page 25 | FF           | #        |

### DC Operational Amplifier Specifications

The following tables list guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and -40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only. The Operational Amplifiers covered by these specifications are components of both the Analog Continuous Time PSoC blocks and the Analog Switched Cap PSoC blocks. The guaranteed specifications are measured in the Analog Continuous Time PSoC block.

| Symbol               | Description                                                                                                                                                                                                                                                           | Min                                                                  | Тур                                       | Max                                         | Units                      | Notes                                                                                                                                                                                                     |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|-------------------------------------------|---------------------------------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OSOACT</sub>  | Input Offset Voltage CT Block (absolute value)<br>Power = Low, Opamp bias = High<br>Power = Medium, Opamp bias = High<br>Power = High, Opamp bias = High                                                                                                              |                                                                      | 1.6<br>1.3<br>1.2                         | 8<br>8<br>8                                 | mV<br>mV<br>mV             |                                                                                                                                                                                                           |

| V <sub>OSOA</sub>    | Input Offset Voltage SC and AGND Opamps (absolute value)                                                                                                                                                                                                              | -                                                                    | 1                                         | 6                                           | mV                         | Applies to High and Low Opamp bias.                                                                                                                                                                       |

| TCV <sub>OSOA</sub>  | Average Input Offset Voltage Drift                                                                                                                                                                                                                                    | -                                                                    | 7.0                                       | 35.0                                        | μV/°C                      |                                                                                                                                                                                                           |

| I <sub>EBOA</sub>    | Input Leakage Current (Port 0 Analog Pins)                                                                                                                                                                                                                            | -                                                                    | 200                                       | -                                           | pА                         | Gross tested to 1 µA.                                                                                                                                                                                     |

| C <sub>INOA</sub>    | Input Capacitance (Port 0 Analog Pins)                                                                                                                                                                                                                                | -                                                                    | 4.5                                       | 9.5                                         | pF                         | Package and pin dependent.<br>Temp = 25 °C.                                                                                                                                                               |

| V <sub>CMOA</sub>    | Common Mode Voltage Range<br>Common Mode Voltage Range (high power or<br>high Opamp bias)                                                                                                                                                                             | 0.0<br>0.5                                                           |                                           | V <sub>DD</sub><br>V <sub>DD</sub> –<br>0.5 | V<br>V                     | The common-mode input<br>voltage range is measured<br>through an analog output buffer.<br>The specification includes the<br>limitations imposed by the<br>characteristics of the analog<br>output buffer. |

| CMRR <sub>OA</sub>   | Common Mode Rejection Ratio<br>Power = Low<br>Power = Medium<br>Power = High                                                                                                                                                                                          | 60<br>60<br>60                                                       |                                           | -<br>-<br>-                                 | dB<br>dB<br>dB             |                                                                                                                                                                                                           |

| G <sub>OLOA</sub>    | Open Loop Gain<br>Power = Low<br>Power = Medium<br>Power = High                                                                                                                                                                                                       | 60<br>60<br>80                                                       |                                           | -<br>-<br>-                                 | dB<br>dB<br>dB             |                                                                                                                                                                                                           |

| V <sub>OHIGHOA</sub> | High Output Voltage Swing (internal signals)<br>Power = Low<br>Power = Medium<br>Power = High                                                                                                                                                                         | V <sub>DD</sub> -0.2<br>V <sub>DD</sub> -0.2<br>V <sub>DD</sub> -0.5 | -<br>-                                    | _<br>_<br>_                                 | V<br>V<br>V                |                                                                                                                                                                                                           |

| V <sub>OLOWOA</sub>  | Low Output Voltage Swing (internal signals)<br>Power = Low<br>Power = Medium<br>Power = High                                                                                                                                                                          |                                                                      | -<br>-                                    | 0.2<br>0.2<br>0.5                           | V<br>V<br>V                |                                                                                                                                                                                                           |

| I <sub>SOA</sub>     | Supply Current (including associated AGND<br>buffer)<br>Power = Low, Opamp bias = Low<br>Power = Low, Opamp bias = High<br>Power = Medium, Opamp bias = Low<br>Power = Medium, Opamp bias = High<br>Power = High, Opamp bias = Low<br>Power = High, Opamp bias = High | -<br>-<br>-<br>-<br>-                                                | 200<br>400<br>700<br>1400<br>2400<br>4600 | 300<br>600<br>1100<br>2000<br>3600<br>7700  | μΑ<br>μΑ<br>μΑ<br>μΑ<br>μΑ |                                                                                                                                                                                                           |

| PSRR <sub>OA</sub>   | Supply Voltage Rejection Ratio                                                                                                                                                                                                                                        | 60                                                                   | _                                         | _                                           | dB                         |                                                                                                                                                                                                           |

#### Table 26. 5 V DC Operational Amplifier Specifications

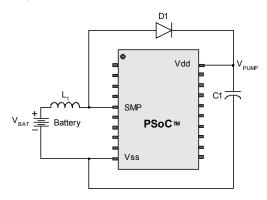

### DC Switch Mode Pump Specifications

The following table lists guaranteed maximum and minimum specifications for the voltage and temperature ranges: 4.75 V to 5.25 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, or 3.0 V to 3.6 V and –40 °C  $\leq$  T<sub>A</sub>  $\leq$  85 °C, respectively. Typical parameters apply to 5 V and 3.3 V at 25 °C and are for design guidance only.

| Table 33. | DC Switch | Mode | Pump | (SMP) | Specifications |

|-----------|-----------|------|------|-------|----------------|

|           |           |      |      |       | opooniounono   |

| Symbol                     | Description                                                                                                                             | Min    | Тур  | Max  | Units           | Notes                                                                                                                                                                              |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--------|------|------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>PUMP</sub> 5 V      | 5 V output voltage                                                                                                                      | 4.75   | 5.0  | 5.25 | V               | Configuration of footnote. <sup>[14]</sup> Average,<br>neglecting ripple. SMP trip voltage is set<br>to 5.0 V.                                                                     |

| V <sub>PUMP</sub> 3 V      | 3 V output voltage                                                                                                                      | 3.00   | 3.25 | 3.60 | V               | Configuration of footnote. <sup>[14]</sup> Average,<br>neglecting ripple. SMP trip voltage is set<br>to 3.25 V.                                                                    |

| I <sub>PUMP</sub>          | Available output current<br>V <sub>BAT</sub> = 1.5 V, V <sub>PUMP</sub> = 3.25 V<br>V <sub>BAT</sub> = 1.8 V, V <sub>PUMP</sub> = 5.0 V | 8<br>5 |      |      | mA<br>mA        | Configuration of footnote. <sup>[14]</sup><br>SMP trip voltage is set to 3.25 V.<br>SMP trip voltage is set to 5.0 V.                                                              |

| V <sub>BAT</sub> 5 V       | Input voltage range from battery                                                                                                        | 1.8    | -    | 5.0  | V               | Configuration of footnote. <sup>[14]</sup> SMP trip voltage is set to 5.0 V.                                                                                                       |

| V <sub>BAT</sub> 3 V       | Input voltage range from battery                                                                                                        | 1.5    | -    | 3.3  | V               | Configuration of footnote. <sup>[14]</sup> SMP trip voltage is set to 3.25 V.                                                                                                      |

| VBATSTART                  | Minimum input voltage from battery to start pump                                                                                        | 2.6    | -    | _    | V               | Configuration of footnote. <sup>[14]</sup>                                                                                                                                         |

| $\Delta V_{PUMP}_{Line}$   | Line regulation (over V <sub>BAT</sub> range)                                                                                           | _      | 5    | _    | %V <sub>O</sub> | Configuration of footnote. <sup>[14]</sup> $V_0$ is the " $V_{DD}$ Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 40 on page 52. |

| $\Delta V_{PUMP\_Load}$    | Load regulation                                                                                                                         | _      | 5    | _    | %V <sub>O</sub> | Configuration of footnote. <sup>[14]</sup> $V_O$ is the " $V_{DD}$ Value for PUMP Trip" specified by the VM[2:0] setting in the DC POR and LVD Specification, Table 40 on page 52. |

| $\Delta V_{PUMP}_{Ripple}$ | Output voltage ripple (depends on capacitor/load)                                                                                       | -      | 100  | -    | mVpp            | Configuration of footnote. <sup>[14]</sup> Load is 5mA.                                                                                                                            |

| E <sub>3</sub>             | Efficiency                                                                                                                              | 35     | 50   | -    | %               | Configuration of footnote. <sup>[14]</sup> Load is 5 mA. SMP trip voltage is set to 3.25 V.                                                                                        |

| F <sub>PUMP</sub>          | Switching frequency                                                                                                                     | _      | 1.3  | _    | MHz             |                                                                                                                                                                                    |

| DC <sub>PUMP</sub>         | Switching duty cycle                                                                                                                    | -      | 50   | _    | %               |                                                                                                                                                                                    |

### Figure 9. Basic Switch Mode Pump Circuit

#### Note 14. L<sub>1</sub> = 2 $\mu$ H inductor, C<sub>1</sub> = 10 $\mu$ F capacitor, D<sub>1</sub> = Schottky diode. See Figure 9.

### Table 35. 3.3-V DC Analog Reference Specifications (continued)

| Reference<br>ARF_CR<br>[5:3] | Reference Power<br>Settings                      | Symbol             | Reference | Description                                                | Min                        | Тур                        | Max                           | Units |

|------------------------------|--------------------------------------------------|--------------------|-----------|------------------------------------------------------------|----------------------------|----------------------------|-------------------------------|-------|

| 0b001                        | RefPower = High<br>Opamp bias = High             | V <sub>REFHI</sub> | Ref high  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.045   | P2[4] + P2[6] –<br>0.017   | P2[4]+P2[6]+<br>0.016         | V     |

|                              |                                                  | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                         | -     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.019   | P2[4] – P2[6] +<br>0.004   | P2[4]-P2[6]+<br>0.023         | V     |

|                              | RefPower = High<br>Opamp bias = Low              | V <sub>REFHI</sub> | Ref high  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.036   | P2[4] + P2[6] –<br>0.012   | P2[4]+P2[6]+<br>0.013         | V     |

| 1                            |                                                  | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                         | _     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.021   | P2[4] – P2[6] –<br>0.001   | P2[4]-P2[6]+<br>0.021         | V     |

|                              | RefPower =<br>Medium                             | V <sub>REFHI</sub> | Ref high  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.034   | P2[4] + P2[6] –<br>0.011   | P2[4]+P2[6]+<br>0.013         | V     |

|                              | Opamp bias = High                                | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                         | -     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.023   | P2[4] – P2[6] –<br>0.002   | P2[4]-P2[6]+<br>0.016         | V     |

|                              | RefPower =<br>Medium<br>Opamp bias = Low         | V <sub>REFHI</sub> | Ref high  | P2[4]+P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] + P2[6] -<br>0.033   | P2[4] + P2[6] -<br>0.009   | P2[4]+P2[6]+<br>0.014         | V     |

|                              |                                                  | V <sub>AGND</sub>  | AGND      | P2[4]                                                      | P2[4]                      | P2[4]                      | P2[4]                         | -     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | P2[4]–P2[6] (P2[4] =<br>V <sub>DD</sub> /2, P2[6] = 0.5 V) | P2[4] – P2[6] –<br>0.024   | P2[4] – P2[6] –<br>0.003   | P2[4]-P2[6]+<br>0.020         | V     |

| 0b010                        | RefPower = High<br>Opamp bias = High             | V <sub>REFHI</sub> | Ref high  | V <sub>DD</sub>                                            | V <sub>DD</sub> - 0.042    | V <sub>DD</sub> – 0.008    | V <sub>DD</sub>               | V     |

|                              |                                                  | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.035 | V <sub>DD</sub> /2 – 0.001 | V <sub>DD</sub> /2 + 0.031    | V     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.003    | V <sub>SS</sub> + 0.0165<br>V | V     |

|                              | RefPower = High                                  | V <sub>REFHI</sub> | Ref high  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.035    | V <sub>DD</sub> – 0.005    | V <sub>DD</sub>               | V     |

|                              | Opamp bias = Low                                 | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.031 | $V_{DD}/2 - 0.001$         | $V_{DD}/2 + 0.028$            | V     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.012       | V     |

|                              | RefPower =                                       | V <sub>REFHI</sub> | Ref high  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.044    | V <sub>DD</sub> – 0.005    | V <sub>DD</sub>               | V     |

|                              | Medium<br>Opamp bias = High                      | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.052 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.046$            | V     |

|                              |                                                  | V <sub>REFLO</sub> | Ref low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.002    | V <sub>SS</sub> + 0.014       | V     |

|                              | RefPower =                                       | V <sub>REFHI</sub> | Ref high  | V <sub>DD</sub>                                            | V <sub>DD</sub> – 0.036    | V <sub>DD</sub> – 0.004    | V <sub>DD</sub>               | V     |

|                              | Medium<br>Opamp bias = Low                       | V <sub>AGND</sub>  | AGND      | V <sub>DD</sub> /2                                         | V <sub>DD</sub> /2 – 0.032 | V <sub>DD</sub> /2         | $V_{DD}/2 + 0.029$            | V     |

|                              | · ·                                              | V <sub>REFLO</sub> | Ref low   | V <sub>SS</sub>                                            | V <sub>SS</sub>            | V <sub>SS</sub> + 0.001    | V <sub>SS</sub> + 0.012       | V     |